Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Betans                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 38                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

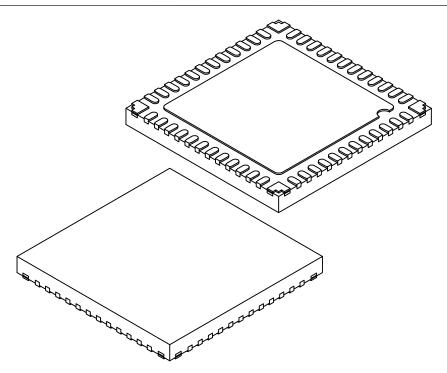

| Package / Case             | 48-TQFP Exposed Pad                                                              |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0256gpm048-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | U-0                        | U-0 U-0           |                   | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        |                            | _                 | -                 | _                 | _                    | _                 | _                | _                |  |  |  |  |  |  |

| 00.40        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |  |  |

| 15:8         |                            |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | S-0 S-0                    |                   | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 7:0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | _                |  |  |  |  |  |  |

### REGISTER 8-8: DCHxECON: DMA CHANNEL x EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and sets the CHTAIF flag                                     |

|           | •                                                                                                                          |

|           | •                                                                                                                          |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and sets the CHTAIF flag                                       |

|           | 00000000 = Interrupt 0 will abort any transfers in progress and sets the CHTAIF flag                                       |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                      |

|           | •                                                                                                                          |

|           | •                                                                                                                          |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer                                                                        |

|           | 0000000 = Interrupt 0 will initiate a DMA transfer                                                                         |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                            |

|           | 1 = A DMA transfer is forced to begin when this bit is written to a '1'                                                    |

|           | 0 = This bit always reads '0'                                                                                              |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                             |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul> |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                              |

| DIL D     | 1 = Aborts transfer and clears CHEN on pattern match                                                                       |

|           | 0 = Pattern match is disabled                                                                                              |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                       |

|           | 1 = Starts channel cell transfer if an interrupt matching CHSIRQx occurs                                                   |

|           | 0 = Interrupt number CHSIRQx is ignored and does not start a transfer                                                      |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                       |

|           | 1 = Channel transfer is aborted if an interrupt matching CHAIRQx occurs                                                    |

|           | 0 = Interrupt number CHAIRQx is ignored and does not terminate a transfer                                                  |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                 |

|           |                                                                                                                            |

Note 1: See Table 7-2 for the list of available interrupt IRQ sources.

# PIC32MM0256GPM064 FAMILY

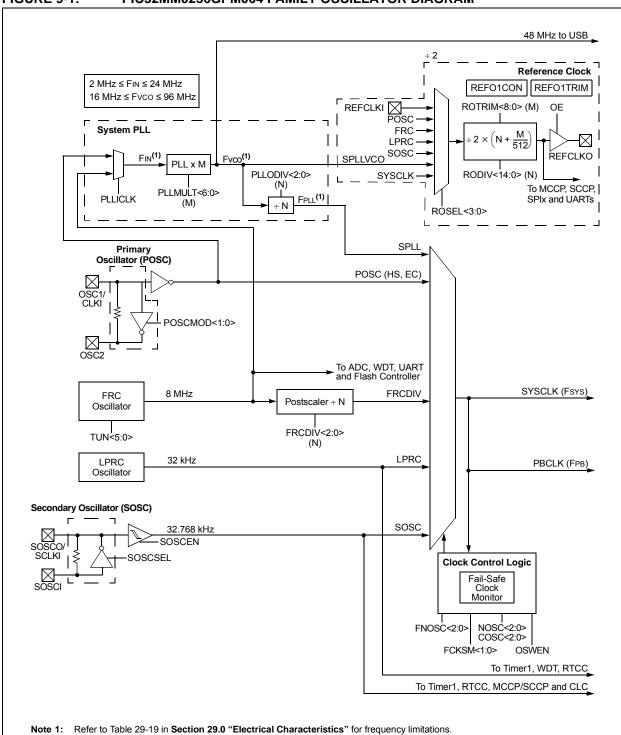

# 9.4 Oscillator Control Registers

| DS60001387C-page |

|------------------|

| € 102            |

## TABLE 9-1: OSCILLATOR CONFIGURATION REGISTER MAP

| ess                         |                                 |           |       |       | 30/14       29/13       28/12       27/11       26/10       25/9       24/8       23/7       22/6       21/5       20/4       19/3       18/2       17/1       16/0       2         -       -       -       -       -       -       -       -       -       -       0 |       |            |       |         |         |            |        |              |         |            |         |          |        | ÷                         |

|-----------------------------|---------------------------------|-----------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|---------|---------|------------|--------|--------------|---------|------------|---------|----------|--------|---------------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(2)</sup> | Bit Range | 31/15 | 30/14 | 29/13                                                                                                                                                                                                                                                                 | 28/12 | 27/11      | 26/10 | 25/9    | 24/8    | 23/7       | 22/6   | 21/5         | 20/4    | 19/3       | 18/2    | 17/1     | 16/0   | All Resets <sup>(1)</sup> |

| 2680                        | OSCCON                          | 31:16     | _     | _     |                                                                                                                                                                                                                                                                       |       |            |       |         |         |            |        |              | —       | _          | —       | _        |        | 0000                      |

| 2000                        | USCCON                          | 15:0      | _     |       | COSC<2:0> — NOSC<2:0> CLKI                                                                                                                                                                                                                                            |       |            |       |         |         |            |        |              | SLPEN   | CF         | _       | SOSCEN   | OSWEN  | xx0x                      |

| 2040                        |                                 | 31:16     | —     | —     | PLLODIV<2:0>                                                                                                                                                                                                                                                          |       |            |       |         |         |            |        | PLLMULT<6:0> |         |            |         |          | 0001   |                           |

| 26A0                        | SPLLCON                         | 15:0      |       |       |                                                                                                                                                                                                                                                                       |       |            | _     | _       | PLLICLK | r          | _      | _            | _       | _          | _       | _        | 0000   |                           |

| 2720                        | REFO1CON                        | 31:16     | _     |       |                                                                                                                                                                                                                                                                       |       |            |       |         | R       | ODIV<14:0> | •      |              |         |            |         |          |        | 0000                      |

| 2720                        | REFUICON                        | 15:0      | ON    | —     | SIDL                                                                                                                                                                                                                                                                  | OE    | RSLP       |       | DIVSWEN | ACTIVE  | -          | _      | -            | _       | ROSEL<3:0> |         |          |        | 0000                      |

| 2720                        | REF01TRIM                       | 31:16     |       |       |                                                                                                                                                                                                                                                                       | F     | ROTRIM<8:0 | >     |         |         |            | —      | -            | —       | —          | -       | -        |        | 0000                      |

| 2730                        | REFUTIRIN                       | 15:0      | _     | _     | _                                                                                                                                                                                                                                                                     | _     | _          |       | _       | _       |            | _      |              | _       | _          | _       | _        |        | 0000                      |

| 2770                        |                                 | 31:16     | _     | _     | _                                                                                                                                                                                                                                                                     |       |            |       | _       | —       |            | _      |              | _       | _          | _       |          |        | 0000                      |

| 2770                        | CLKSTAT                         | 15:0      | _     | _     | _                                                                                                                                                                                                                                                                     | _     | _          | _     | _       | r       | SPLLRDY    | USBRDY | LPRCRDY      | SOSCRDY | r          | POSCRDY | SPDIVRDY | FRCRDY | 0000                      |

| 2880                        | OSCTUN                          | 31:16     | _     | _     | _                                                                                                                                                                                                                                                                     | _     | _          |       | _       | _       |            | _      |              | _       | _          | _       | _        |        | 0000                      |

| 2080                        | USCIUN                          | 15:0      | ON    | r     | SIDL                                                                                                                                                                                                                                                                  | SRC   | LOCK       | POL   | ORNG    | ORPOL   |            | _      |              |         | TUN        | I<5:0>  |          |        | 0000                      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'; r = reserved bit. Reset values are shown in hexadecimal.

Note 1: Reset values are dependent on the FOSCSEL Configuration bits and the type of Reset.

2: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# 12.0 TIMER2 AND TIMER3

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

This family of PIC32 devices features four synchronous 16-bit timers (default) that can operate as a freerunning interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous Internal 16-Bit Timer

- Synchronous Internal 16-Bit Gated Timer

- Synchronous External 16-Bit Timer

**FIGURE 12-1:**

A single 32-bit synchronous timer is available by combining Timer2 with Timer3. The resulting 32-bit timer can operate in three modes:

- · Synchronous Internal 32-Bit Timer

- · Synchronous Internal 32-Bit Gated Timer

- Synchronous External 32-Bit

## 12.1 Additional Supported Features

- Selectable Clock Prescaler

- Timers Operational during CPU Idle

- ADC Event Trigger (only Timer3)

- Fast Bit Manipulation using CLR, SET and INV Registers

Sync TMRx 44 ADC Event Comparator x 16 Trigger<sup>(1)</sup> Equal 介 PRx Reset 0 TxIF Event Flag 1 Q TGATE (TxCON<7>) Q TCS (TxCON<1>) TGATE (TxCON<7>) ON (TxCON<15>) TxCK x 1 Prescaler Gate 1, 2, 4, 8, 16, Sync 1 0 32, 64, 256 PBCLK 0 0 <u>3</u> TCKPS (TxCON<6:4>) Note 1: ADC Event Trigger is only available on Timer3.

TIMER2 AND TIMER3 BLOCK DIAGRAM (TYPE A, 16-BIT)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0             | U-0               | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-1            |  |  |  |  |  |

| 31:24        | OENSYNC           |                   | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN            |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | U-0                  | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |  |  |  |  |

| 23:16        | ICGSM             | 1<1:0>            | —                    | AUXOL                | JT<1:0>              | ICS<2:0>             |                      |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | U-0                  | R/W-0                | U-0                  | U-0                  | U-0                  | U-0              |  |  |  |  |  |

| 15:8         | PWMRSEN           | ASDGM             | —                    | SSDG                 | —                    | —                    | -                    | -                |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |  |  |  |  |

| 7:0          | ASDG<7:0>         |                   |                      |                      |                      |                      |                      |                  |  |  |  |  |  |

## REGISTER 14-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31 **OENSYNC:** Output Enable Synchronization bit

- 1 = Update by output enable bits occurs on the next Time Base Reset or rollover

- 0 = Update by output enable bits occurs immediately

- bit 30 Unimplemented: Read as '0'

#### bit 29-24 OC<F:A>EN: Output Enable/Steering Control bits<sup>(1)</sup>

- 1 = OCx pin is controlled by the CCPx module and produces an output compare or PWM signal

- 0 = OCx pin is not controlled by the CCPx module; the pin is available to the port logic or another peripheral multiplexed on the pin

#### bit 23-22 ICGSM<1:0>: Input Capture Gating Source Mode Control bits

- 11 = Reserved

- 10 = One-Shot mode: Falling edge from gating source disables future capture events (ICDIS = 1)

- 01 = One-Shot mode: Rising edge from gating source enables future capture events (ICDIS = 0)

- 00 = Level-Sensitive mode: A high level from gating source will enable future capture events; a low level will disable future capture events

- bit 21 Unimplemented: Read as '0'

#### bit 20-19 AUXOUT<1:0>: Auxiliary Output Signal on Event Selection bits

- 11 = Input capture or output compare event; no signal in Timer mode

- 10 = Signal output depends on module operating mode

- 01 = Time base rollover event (all modes)

- 00 = Disabled

- bit 18-16 ICS<2:0>: Input Capture Source Select bits

- 111 = CLC4 output

- 110 = CLC3 output

- 101 = CLC2 output

- 100 = CLC1 output

- 011 = Comparator 3 output

- 010 = Comparator 2 output

- 001 = Comparator 1 output

- 000 = ICMx pin<sup>(2)</sup>

- bit 15 PWMRSEN: CCPx PWM Restart Enable bit

- 1 = ASEVT bit clears automatically at the beginning of the next PWM period, after the shutdown input has ended

- 0 = ASEVT must be cleared in software to resume PWM activity on output pins

- Note 1: OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

- **2:** This pin is remappable from SCCP modules.

NOTES:

# TABLE 16-1: I2C1, I2C2 AND I2C3 REGISTER MAP (CONTINUED)

| ess                         |                                 |           |         |        |        |        |        |       |        | Bi         | ts          |       |            |             |              |       |      |      |            |

|-----------------------------|---------------------------------|-----------|---------|--------|--------|--------|--------|-------|--------|------------|-------------|-------|------------|-------------|--------------|-------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14  | 29/13  | 28/12  | 27/11  | 26/10 | 25/9   | 24/8       | 23/7        | 22/6  | 21/5       | 20/4        | 19/3         | 18/2  | 17/1 | 16/0 | All Resets |

| 1700                        |                                 | 31:16     | —       | _      | —      | —      | _      | -     | -      | —          | -           | PCIE  | SCIE       | BOEN        | SDAHT        | SBCDE | r    | r    | 0000       |

| 1700                        | I2C3CON                         | 15:0      | ON      |        | SIDL   | SCLREL | STRICT | A10M  | DISSLW | SMEN       | GCEN        | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN | SEN  | 1000       |

| 1710                        | I2C3STAT                        | 31:16     | —       |        | _      |        | —      |       | —      |            |             | _     |            | _           | _            | _     |      | _    | 0000       |

| 1710                        | 12035 IAI                       | 15:0      | ACKSTAT | TRSTAT | ACKTIM |        | —      | BCL   | GCSTAT | ADD10      | IWCOL       | I2COV | D/A        | Р           | S            | R/W   | RBF  | TBF  | 0000       |

| 1720                        | I2C3ADD                         | 31:16     | —       | _      | —      | —      | —      | _     | —      | —          | -           | —     | —          | —           | —            | —     | —    | —    | 0000       |

| 1720                        | 1203ADD                         | 15:0      | —       | _      | —      | —      | —      | _     |        |            |             |       | I2C2 Addre | ss Register |              |       |      |      | 0000       |

| 1730                        | I2C3MSK                         | 31:16     | —       | —      | —      | —      | —      | _     | —      | —          | —           |       | —          | _           | —            | _     | —    | —    | 0000       |

| 1750                        | 120010101                       | 15:0      | —       | —      | —      | —      | —      | _     |        |            |             | 120   | 2 Address  | Mask Regis  | ster         |       |      | -    | 0000       |

| 1740                        | I2C3BRG                         | 31:16     | _       | —      |        | —      | —      | —     | —      | —          | —           |       | —          | _           | —            | _     | —    | —    | 0000       |

| 1740                        | IZCOBING                        | 15:0      |         |        |        |        |        |       | Baud   | d Rate Gen | erator Regi | ster  |            |             |              |       |      | -    | 0000       |

| 1750                        | I2C3TRN                         | 31:16     | —       | _      | —      | —      | —      | _     | —      | —          | -           | —     | —          | —           | —            | —     | —    | —    | 0000       |

| 1750                        | 12031 RN                        | 15:0      | —       |        | _      |        | —      |       | —      |            |             |       | I          | 2C2 Transn  | nit Register |       |      |      | 0000       |

| 1760                        | I2C3RCV                         | 31:16     | —       |        | _      | _      | —      |       | _      |            | _           | _     | _          | _           | _            | _     | _    | _    | 0000       |

| 1700                        | 1205RUV                         | 15:0      | _       |        | —      | _      | _      |       | —      | -          |             |       |            | 2C2 Receiv  | ve Register  |       |      |      | 0000       |

**Legend:** — = unimplemented, read as '0'; r = reserved bit. Reset values are shown in hexadecimal.

Note 1: All registers in this table, except I2CxRCV, have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        | MASK<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |  |  |  |  |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |  |  |  |  |

| 7:0          | URXISE            | :L<1:0>           | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |  |  |  |  |

#### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

- bit 31-24 MASK<7:0>: UARTx Address Match Mask bits

- Used to mask the ADDR<7:0> bits.

- For MASK<x>:

- 1 = ADDR<x> is used to detect the address match

- 0 = ADDR<x> is not used to detect the address match

- bit 23-16 ADDR<7:0>: UARTx Automatic Address Mask bits

When the ADDEN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: UARTx TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

#### bit 13 UTXINV: UARTx Transmit Polarity Inversion bit

- If IrDA mode is Disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

- If IrDA mode is Enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA<sup>®</sup> encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: UARTx Receiver Enable bit

- 1 = UARTx receiver is enabled, UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled, UxRX pin is ignored by the UARTx module

#### bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Break on next transmission; Start bit, followed by twelve '0' bits, followed by Stop bit, cleared by hardware upon completion

- 0 = Break transmission is disabled or has completed

- bit 10 UTXEN: UARTx Transmit Enable bit

- 1 = UARTx transmitter is enabled, UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled, any pending transmission is aborted and the buffer is reset

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 **TRMT:** Transmit Shift Register (TSR) is Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued in the transmit buffer

## TABLE 18-1: USB OTG REGISTER MAP (CONTINUED)

| ess                         |                                 | C)        |       |       |       |       |       |       |      |      | Bits  |          |       |             |        |        |           |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|-------------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4        | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 0070                        | U1BDTP1                         | 31:16     | _     | —     | —     | _     | _     | —     | —    | _    | _     | —        | _     | _           |        | —      | _         | _        | 0000       |

| 8670                        | UIBDIPI                         | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    |       |          | В     | DTPTRL<7:1> |        |        |           | _        | 0000       |

| 0000                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | _           | _      | _      | _         | -        | 0000       |

| 8680                        | UTFRIML                         | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    |       |          |       | FRML<       | 7:0>   |        |           |          | 0000       |

| 0000                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | —     | —        | _     | _           | _      | _      | _         | _        | 0000       |

| 8690                        | UTERMH                          | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _     | —        | _     | _           | _      |        | FRMH<2:0> |          | 0000       |

| 9640                        | U1TOK                           | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _     | —        | _     | _           | _      | _      | _         | _        | 0000       |

| 86A0                        | UTIOK                           | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    |       | PID<     | <3:0> |             |        | EP     | <3:0>     |          | 0000       |

| 0000                        | U1SOF                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | _           | _      | _      | _         | _        | 0000       |

| 86B0                        | UISOF                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | CNT<7       | /:0>   |        |           |          | 0000       |

| 0000                        |                                 | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | —     | —        | _     | _           | _      | _      | _         | _        | 0000       |

| 86C0                        | U1BDTP2                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |       |          |       | BDTPTR      | H<7:0> |        |           |          | 0000       |

| 86D0                        | U1BDTP3                         | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _     | —        | _     | _           | _      | _      | _         | _        | 0000       |

| 80DU                        | UIBD1P3                         | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    |       |          |       | BDTPTRI     | J<7:0> |        |           |          | 0000       |

| 86E0                        | U1CNFG1                         | 31:16     | _     | _     | _     | -     | -     | —     | _    | _    | -     | —        | _     | _           | -      | —      | _         | _        | 0000       |

| 80EU                        | UTCNFGT                         | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | UTEYE | UOEMON   | _     | USBSIDL     | LSDEV  | _      | _         | UASUSPND | 0001       |

| 8700                        | U1EP0                           | 31:16     | _     | _     | —     | _     |       | _     | _    | _    |       | —        | _     | _           |        | _      | _         | _        | 0000       |

| 8700                        | UIEPU                           | 15:0      | _     | _     | _     | -     | -     | —     | _    | _    | LSPD  | RETRYDIS | _     | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9710                        | U1EP1                           | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _     | —        | _     | _           | _      | _      | _         | _        | 0000       |

| 8710                        | UIEPI                           | 15:0      | _     | _     | —     | _     |       | _     | _    | _    |       | —        | _     | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 0700                        | U1EP2                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | _           | _      | _      | _         | -        | 0000       |

| 8720                        | UTEP2                           | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _     | —        | _     | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9720                        | U1EP3                           | 31:16     | _     | _     | —     | _     |       | _     | _    | _    |       | —        | _     | _           |        | _      | _         | _        | 0000       |

| 8730                        | UTEP3                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9740                        |                                 | 31:16     | _     | —     | —     | —     | _     | —     | —    | —    | _     | —        | _     | _           | _      | —      | _         | _        | 0000       |

| 8740                        | U1EP4                           | 15:0      | _     | _     | _     | —     | _     | —     | _    | _    | _     | —        | _     | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9750                        |                                 | 31:16     | _     | —     | —     | _     | _     | —     | _    | _    | _     | —        | _     | _           | _      | —      | _         | _        | 0000       |

| 8750                        | U1EP5                           | 15:0      |       | _     |       | —     | _     | —     |      |      | _     | —        | _     | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 0700                        |                                 | 31:16     | —     | —     | —     | _     | _     | —     | —    | _    | _     | —        | _     | —           | —      | —      | _         | _        | 0000       |

| 8760                        | U1EP6                           | 15:0      | _     | _     | _     | _     |       | _     | _    | _    | _     | _        | _     | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 10.1 "CLR, SET and INV Registers" for more information.

**2**: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for these bits is undefined.

# PIC32MM0256GPM064 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 24.24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31:24        | —                 | _                       | _                       | _                 | —                    | _                 | _                     | _                       |

| 00.40        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23:16        | —                 | —                       | —                       | —                 | —                    | _                 | _                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

|              |                   | —                       | _                       | _                 | —                    | _                 | _                     | _                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | STALLIF           |                         | RESUMEIR /              | IDLEIF            |                      | SOLL              | UERRIFY /             | DETACHIF <sup>(6)</sup> |

## REGISTER 18-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to Clear bit | HS = Hardware Settable bit              |

|-------------------|-----------------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 STALLIF: Stall Handshake Interrupt bit

- I = In Host mode, a Stall handshake was received during the handshake phase of the transaction; in Device mode, a Stall handshake was transmitted during the handshake phase of the transaction

- 0 = Stall handshake has not been sent

- bit 6 ATTACHIF: Peripheral Attach Interrupt bit<sup>(1)</sup>

- 1 = Peripheral attachment was detected by the USB module

- 0 = Peripheral attachment was not detected

- bit 5 **RESUMEIF:** Resume Interrupt bit<sup>(2)</sup>

- 1 = K-State is observed on the D+ or D- pin for 2.5 µs

- 0 = K-State is not observed

- bit 4 IDLEIF: Idle Detect Interrupt bit

- 1 = Idle condition detected (constant Idle state of 3 ms or more)

- 0 = No Idle condition detected

- bit 3 TRNIF: Token Processing Complete Interrupt bit<sup>(3)</sup>

- 1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information

- 0 = Processing of current token not complete

- bit 2 SOFIF: SOF Token Interrupt bit

- 1 = SOF token received by the peripheral or the SOF threshold reached by the host

- 0 = SOF token was not received nor threshold reached

- bit 1 **UERRIF**: USB Error Condition Interrupt bit<sup>(4)</sup>

- 1 = Unmasked error condition has occurred

- 0 = Unmasked error condition has not occurred

- **Note 1:** This bit is only valid if the HOSTEN bit is set (see Register 18-11), there is no activity on the USB for 2.5 μs and the current bus state is not SE0.

- 2: When not in Suspend mode, this interrupt should be disabled.

- 3: Clearing this bit will cause the STAT FIFO to advance.

- 4: Only error conditions enabled through the U1EIE register will set this bit.

- 5: Device mode.

- 6: Host mode.

## REGISTER 18-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Resets all Even/Odd Buffer Pointers to the Even buffer descriptor banks

- 0 = Even/Odd Buffer Pointers are not reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry are enabled

- 0 = USB module and supporting circuitry are disabled

SOFEN: SOF Enable bit(5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 18-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the Resume signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

NOTES:

| Bit<br>Range       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24              | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 31:24 USERID<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40              | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 23:16              | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0               | R/P               | R/P               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |

| 15:8               | FVBUSIO           | FUSBIDIO          | _                 | —                 | —                 | _                 |                  | _                |  |  |

| 7.0                | r-1               | r-1               | r-1               | R/P               | R/P               | r-1               | r-1              | r-1              |  |  |

| 7:0                |                   |                   |                   | ALTI2C            | SOSCHP            |                   | _                |                  |  |  |

#### REGISTER 26-1: FDEVOPT/AFDEVOPT: DEVICE OPTIONS CONFIGURATION REGISTER

| Legend: r = Reserved bit |                   | r = Reserved bit                                    | P = Programmable bit                    |  |  |  |

|--------------------------|-------------------|-----------------------------------------------------|-----------------------------------------|--|--|--|

|                          | R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                                         |  |  |  |

|                          | -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared x = Bit is unknown |  |  |  |

bit 31-16 USERID<15:0>: User ID bits (2 bytes which can programmed to any value)

- bit 15 FVBUSIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 14 FUSBIDIO: USB USBID Selection bit

- 1 = USBID pin is controlled by the USB module

- 0 = USBID pin is controlled by the port function

- bit 13-5 **Reserved:** Program as '1'

- bit 4 ALTI2C: Alternate I2C1 Location Select bit

- 1 = SDA1 and SCL1 are on pins, RB8 and RB9

- 0 = SDA1 and SCL1 are moved to alternate I<sup>2</sup>C locations, RB5 and RC9

- SOSCHP: Secondary Oscillator (SOSC) High-Power Enable bit

- 1 = SOSC operates in normal power mode

- 0 = SOSC operates in High-Power mode

- bit 2-0 Reserved: Program as '1'

bit 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |

| 31:24        | —                 | _                 | -                 | —                 | -                 | _                 | _                | —                |  |  |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |  |

| 23:16        | —                 | _                 | -                 | —                 |                   | _                 | —                | —                |  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 15:8         | FWDTEN            | RCLKSEL<1:0>      |                   | RWDTPS<4:0>       |                   |                   |                  |                  |  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |

| 7:0          | WINDIS            | FWDTWI            | NSZ<1:0>          |                   | SWDTPS<4:0>       |                   |                  |                  |  |  |

## REGISTER 26-4: FWDT/AFWDT: WATCHDOG TIMER CONFIGURATION REGISTER

| Legend:           | r = Reserved bit | P = Programmable bit                    |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-16 Reserved: Program as '1'

- bit 15 **FWDTEN:** Watchdog Timer Enable bit

- 1 = WDT is enabled

- 0 = WDT is disabled

## bit 14-13 RCLKSEL<1:0>: Run Mode Watchdog Timer Clock Source Selection bits

- 11 = Clock source is the LPRC oscillator (same as for Sleep mode)

- 10 = Clock source is the FRC oscillator

- 01 = Reserved

- 00 = Clock source is the system clock

## bit 12-8 RWDTPS<4:0>: Run Mode Watchdog Timer Postscale Select bits

## From 10100 to 11111 = 1:1048576.

| 10011 | = | 1:524288 |

|-------|---|----------|

|       |   | 1:262144 |

| 10001 | = | 1:131072 |

| 10000 | = | 1:65536  |

| 01111 | = | 1:32768  |

| 01110 | = | 1:16384  |

| 01101 | = | 1:8192   |

| 01100 | = | 1:4096   |

| 01011 | = | 1:2048   |

| 01010 | = | 1:1024   |

| 01001 | = | 1:512    |

| 01000 | = | 1:256    |

| 00111 | = | 1:128    |

| 00110 | = | 1:64     |

| 00101 | = | 1:32     |

| 00100 | = | 1:16     |

| 00011 | = | 1:8      |

| 00010 | = | 1:4      |

| 00001 | _ | 1.0      |

00001 = 1:2

00000 = 1:1

bit 7 WINDIS: Windowed Watchdog Timer Disable bit

- 1 = Windowed mode is disabled

- 0 = Windowed mode is enabled

| TABLE 29-3: OPERATING VOLTAGE SPECIFICATIONS | TABLE 29-3: | OPERATING VOLTAGE SPECIFICATIONS |

|----------------------------------------------|-------------|----------------------------------|

|----------------------------------------------|-------------|----------------------------------|

| DC CH        | ARACTER              | ISTICS                                                                      | Operating Conditions: 2.0V < VDD < 3.6V, -40°C < TA < +85°C<br>(unless otherwise stated) |     |       |       |                                     |

|--------------|----------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----|-------|-------|-------------------------------------|

| Param<br>No. | Symbol               | Characteristic                                                              | Min                                                                                      | Тур | Max   | Units | Conditions                          |

| DC10         | Vdd                  | Supply Voltage                                                              | 2.0                                                                                      | _   | 3.6   | V     |                                     |

| DC16         | V <sub>POR</sub> (1) | <b>VDD Start Voltage</b><br>to Ensure Internal<br>Power-on Reset Signal     | Vss                                                                                      | —   | 100   | mV    |                                     |

| DC17A        | SVDD <sup>(1)</sup>  | Recommended<br>Vod Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal | 0.05                                                                                     | _   |       | V/ms  | 0-3.3V in 66 ms,<br>0-2.0V in 40 ms |

| DC17B        | Vbor                 | Brown-out Reset<br>Voltage on VDD<br>Transition, High-to-Low                | 2.0                                                                                      | _   | 2.083 | V     |                                     |

**Note 1:** If the VPOR or SVDD parameters are not met, or the application experiences slow power-down VDD ramp rates, it is recommended to enable and use BOR.

## TABLE 29-4: OPERATING CURRENT (IDD)<sup>(2)</sup>

| DC CHARAG        | DC CHARACTERISTICS     |      |                |                          |               |                 |  |  |  |  |

|------------------|------------------------|------|----------------|--------------------------|---------------|-----------------|--|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Max  | Units          | Operating<br>Temperature |               | Conditions      |  |  |  |  |

| DC19             | .72                    | .96  | mA             | -40°C to +85°C           | 2.0V          | Fsys = 1 MHz    |  |  |  |  |

|                  |                        | .96  | mA             | -40°C to +85°C           | 3.3V          |                 |  |  |  |  |

| DC23             | 2.5                    | 3.7  | mA             | -40°C to +85°C           | 2.0V          | Fsys = 8 MHz    |  |  |  |  |

|                  | 2.5                    | 3.7  | mA             | -40°C to +85°C           | 3.3V          |                 |  |  |  |  |

| DC24             | 7.9                    | 10.2 | mA             | -40°C to +85°C           | 2.0V          | Fsys = 25 MHz   |  |  |  |  |

|                  | 7.9                    | 10.2 | mA             | -40°C to +85°C           | 3.3V          | 1313 - 23 MI 12 |  |  |  |  |

| DC25             | .4                     | .8   | μA             | -40°C to +85°C           | 2.0V          | LPRC,           |  |  |  |  |

|                  | .4 .8 μA -40°C to +85  |      | -40°C to +85°C | 3.3V                     | Fsys = 32 kHz |                 |  |  |  |  |

Note 1: Typical parameters are for design guidance only and are not tested.

**2:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

- Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC Clock Overshoot/Undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as outputs and driving low

- MCLR = VDD; WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

- · CPU executing:

```

while(1)

{

NOP();

}

```

3: JTAG is disabled

| DC CHARA         | CTERISTIC              | S   |              |                          |      |                                                                                   |  |

|------------------|------------------------|-----|--------------|--------------------------|------|-----------------------------------------------------------------------------------|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Max | Units        | Operating<br>Temperature | Vdd  | Conditions                                                                        |  |

| DC60             |                        |     |              |                          |      |                                                                                   |  |

|                  | 130                    | 255 | μA           | +25°C                    | 2.0V |                                                                                   |  |

|                  | 145                    | 265 | μA           | +85°C                    |      | Sleep with active main Voltage Regulator                                          |  |

|                  | 130                    | 255 | μA           | -40°C                    |      | <pre>(VREGS (PWRCON&lt;0&gt;) bit = 1,<br/>RETEN (PWRCON&lt;1&gt;) bit = 0)</pre> |  |

|                  | 130                    | 265 | μA           | +25°C                    | 3.3V |                                                                                   |  |

|                  | 145 275 μA +85°C       |     |              |                          |      |                                                                                   |  |

| DC61             | 3.5                    | 12  | μA           | -40°C                    |      |                                                                                   |  |

|                  | 4.5                    | 22  | μA           | +25°C                    | 2.0V | Sleep with main Voltage Regulator in                                              |  |

|                  | 15 35 μA +85°C         |     | Standby mode |                          |      |                                                                                   |  |

|                  | 4                      | 17  | μA           | -40°C                    | 3.3V | (VREGS (PWRCON<0>) bit = 0,                                                       |  |

|                  | 5                      | 30  | μA           | +25°C                    |      | RETEN (PWRCON<1>) bit = 0)                                                        |  |

|                  | 18                     | 38  | μA           | +85°C                    |      |                                                                                   |  |

| DC62             | 4.3                    | _   | μA           | -40°C                    |      |                                                                                   |  |

|                  | 5                      | _   | μA           | +25°C                    | 2.0V | Sleep with enabled Retention                                                      |  |

|                  | 10                     | _   | μA           | +85°C                    |      | Voltage Regulator                                                                 |  |

|                  | 5                      | _   | μA           | -40°C                    |      | (RETEN (PWRCON<1>) bit = 1,                                                       |  |

|                  | 5.6                    | _   | μA           | +25°C                    | 3.3V | RETVR (FPOR<2>) bit = 0)                                                          |  |

|                  | 12                     | _   | μA           | +85°C                    |      |                                                                                   |  |

| DC63             | .3                     | _   | μA           | -40°C                    |      |                                                                                   |  |

|                  | .4                     | _   | μA           | +25°C                    | 2.0V | Sleep with enabled Retention                                                      |  |

|                  | 3.5                    |     | μA           | +85°C                    |      | Voltage Regulator<br>- (VREGS (PWRCON<0>) bit = 0,                                |  |

|                  | 0.35                   |     | μA           | -40°C                    |      | = (VREGS(PWRCON<0>) bit = 0,<br>RETEN (PWRCON<1>) bit = 1,                        |  |

|                  | 0.45                   |     | μA           | +25°C                    | 3.3V | RETVR(FPOR<2>)  bit = 0)                                                          |  |

|                  | 4.5                    |     | μA           | +85°C                    |      |                                                                                   |  |

# TABLE 29-6:POWER-DOWN CURRENT (IPD)<sup>(2)</sup>

Note 1: Parameters are for design guidance only and are not tested.

2: Base IPD is measured with:

- Oscillator is configured in FRC mode without PLL (FNOSC<2:0> (FOSCSEL<2:0>) = 000)

- OSC1 pin is driven with external square wave from rail-to-rail (EC Clock Overshoot/Undershoot < 250 mV required)

- OSC2 is configured as an I/O in Configuration Words (OSCIOFNC (FOSCSEL<10>) = 1)

- FSCM is disabled (FCKSM<1:0> (FOSCSEL<15:14>) = 00)

- Secondary Oscillator circuits are disabled (SOSCEN (FOSCSEL<6>) = 0 and SOSCSEL (FOSCSEL<12>) = 0)

- Main and low-power BOR circuits are disabled (BOREN<1:0> (FPOR<1:0>) = 00 and LPBOREN (FPOR<3>) = 0)

- Watchdog Timer is disabled (FWDTEN (FWDT<15>) = 0)

- All I/O pins (excepting OSC1) are configured as outputs and driven low

- No peripheral modules are operating or being clocked (defined PMDx bits are all ones)

# 29.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC32MM0256GPM064 family AC characteristics and timing parameters.

## TABLE 29-16: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)          |

|--------------------|--------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$                   |

|                    | Operating voltage VDD range as described in Section 29.1 "DC Characteristics". |

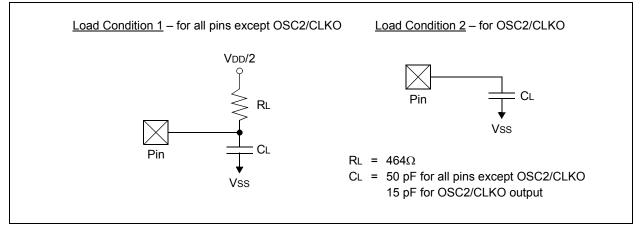

## FIGURE 29-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

## TABLE 29-17: CAPACITIVE LOADING CONDITIONS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                              |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|-------------------------------------------------------------------------|

| DO50         | Cosco  | OSC2/CLKO Pin         | _   | —                  | TBD |       | In XT and HS modes when<br>external clock is used to drive<br>OSC1/CLKI |

| DO56         | Сю     | All I/O Pins and OSC2 | —   | —                  | TBD | pF    | EC mode                                                                 |

| DO58         | Св     | SCLx, SDAx            | _   | _                  | TBD | pF    | In I <sup>2</sup> C mode                                                |

**Legend:** TBD = To Be Determined

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

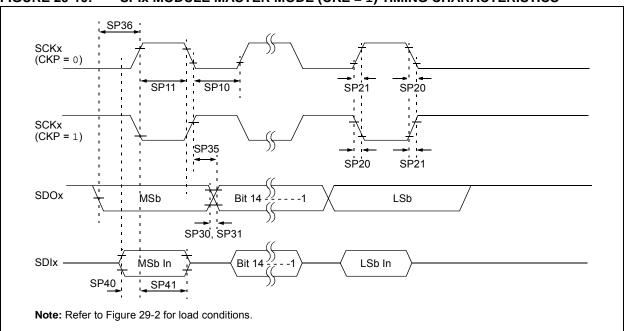

# FIGURE 29-10: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 29-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |                     |      |       |                    |  |  |

|--------------------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|--|

| Param<br>No.       | Symbol                | Characteristics <sup>(1)</sup>                | Min.                                                                                                                             | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP10               | TscL                  | SCKx Output Low Time <sup>(3)</sup>           | Tsck/2                                                                                                                           | —                   | _    | ns    |                    |  |  |

| SP11               | TscH                  | SCKx Output High Time <sup>(3)</sup>          | Tsck/2                                                                                                                           |                     | _    | ns    |                    |  |  |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(4)</sup>          |                                                                                                                                  |                     | _    | ns    | See Parameter DO32 |  |  |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(4)</sup>          | _                                                                                                                                | _                   | _    | ns    | See Parameter DO31 |  |  |

| SP30               | TDOF                  | SDOx Data Output Fall<br>Time <sup>(4)</sup>  | —                                                                                                                                | —                   | _    | ns    | See Parameter DO32 |  |  |

| SP31               | TDOR                  | SDOx Data Output Rise<br>Time <sup>(4)</sup>  | —                                                                                                                                | —                   | _    | ns    | See Parameter DO31 |  |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid<br>after SCKx Edge     | _                                                                                                                                |                     | 7    | ns    | VDD > 2.0V         |  |  |

|                    |                       |                                               |                                                                                                                                  |                     | 10   | ns    | VDD < 2.0V         |  |  |

| SP36               | TDOV2sc,<br>TDOV2scL  | SDOx Data Output Setup<br>to First SCKx Edge  | 7                                                                                                                                | —                   | _    | ns    |                    |  |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data<br>Input to SCKx Edge | 7                                                                                                                                |                     | _    | ns    | VDD > 2.0V         |  |  |

|                    |                       |                                               | 10                                                                                                                               | _                   | _    | ns    | VDD < 2.0V         |  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data<br>Input to SCKx Edge  | 7                                                                                                                                |                     | _    | ns    | VDD > 2.0V         |  |  |

|                    |                       |                                               | 10                                                                                                                               |                     | _    | ns    | VDD < 2.0V         |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in the "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 10 pF load on all SPIx pins.

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-105C Sheet 1 of 2

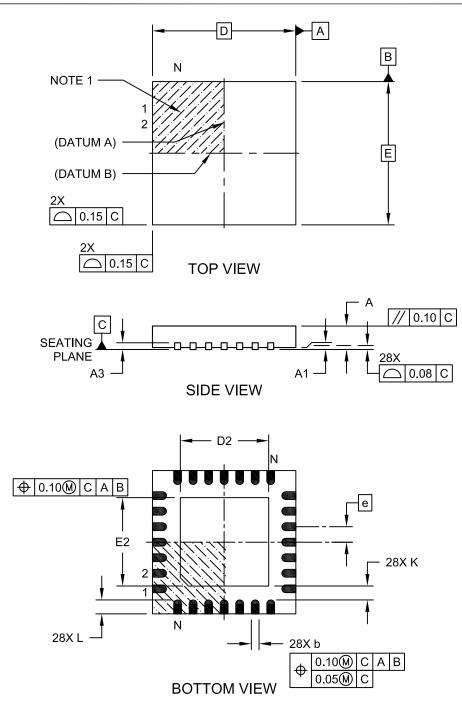

# 48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M4) - 6x6 mm Body [UQFN] With Corner Anchors and 4.6x4.6 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                                    | MILLIMETERS |          |      |      |  |  |

|------------------------------------|-------------|----------|------|------|--|--|

| Dimension                          | MIN         | NOM      | MAX  |      |  |  |

| Number of Terminals                | N           | 48       |      |      |  |  |

| Pitch                              | е           | 0.40 BSC |      |      |  |  |

| Overall Height                     | Α           | 0.50     | 0.55 | 0.60 |  |  |

| Standoff                           | A1          | 0.00     | 0.02 | 0.05 |  |  |

| Terminal Thickness                 | A3          | 0.15 REF |      |      |  |  |

| Overall Length                     | D           | 6.00 BSC |      |      |  |  |

| Exposed Pad Length                 | D2          | 4.50     | 4.60 | 4.70 |  |  |

| Overall Width                      | E           | 6.00 BSC |      |      |  |  |

| Exposed Pad Width                  | E2          | 4.50     | 4.60 | 4.70 |  |  |

| Terminal Width                     | b           | 0.15     | 0.20 | 0.25 |  |  |

| Corner Anchor Pad                  | b1          | 0.45 REF |      |      |  |  |

| Corner Anchor Pad, Metal-free Zone | b2          | 0.23 REF |      |      |  |  |

| Terminal Length                    | L           | 0.35     | 0.40 | 0.45 |  |  |

| Terminal-to-Exposed-Pad            | K           | 0.30 REF |      |      |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-442A-M4 Sheet 2 of 2