Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Data ila                   |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Details                    |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 26                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-TQFP                                                                  |

| Supplier Device Package    | 64-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c601-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.4 PCL, PCLATH and PCLATU

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21-bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register may be performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSb of the PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

The contents of PCLATH and PCLATU will be transferred to the program counter by an operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (See Section 4.8.1).

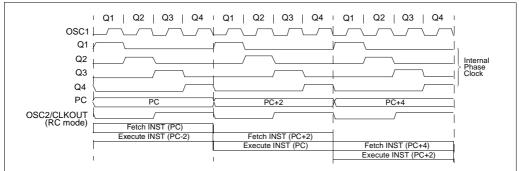

# 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1 or PLL output) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 4-6.

| FIGURE 4-9: | CDECIAL | FUNCTION | REGISTER MAP |

|-------------|---------|----------|--------------|

| FIGURE 4-9: | SPECIAL | FUNCTION | REGISTER WAP |

| FFFh | TOSU     | FDFh | INDF2    | FBFh | CCPR1H   | F9Fh | IPR1   |

|------|----------|------|----------|------|----------|------|--------|

| FFEh | TOSH     | FDEh | POSTINC2 | FBEh | CCPR1L   | F9Eh | PIR1   |

| FFDh | TOSL     | FDDh | POSTDEC2 | FBDh | CCP1CON  | F9Dh | PIE1   |

| FFCh | STKPTR   | FDCh | PREINC2  | FBCh | CCPR2H   | F9Ch | MEMCON |

| FFBh | PCLATU   | FDBh | PLUSW2   | FBBh | CCPR2L   | F9Bh | _      |

| FFAh | PCLATH   | FDAh | FSR2H    | FBAh | CCP2CON  | F9Ah | TRISJ  |

| FF9h | PCL      | FD9h | FSR2L    | FB9h | Reserved | F99h | TRISH  |

| FF8h | TBLPTRU  | FD8h | STATUS   | FB8h | Reserved | F98h | TRISG  |

| FF7h | TBLPTRH  | FD7h | TMR0H    | FB7h | Reserved | F97h | TRISF  |

| FF6h | TBLPTRL  | FD6h | TMR0L    | FB6h | _        | F96h | TRISE  |

| FF5h | TABLAT   | FD5h | T0CON    | FB5h | _        | F95h | TRISD  |

| FF4h | PRODH    | FD4h | Reserved | FB4h | _        | F94h | TRISC  |

| FF3h | PRODL    | FD3h | OSCCON   | FB3h | TMR3H    | F93h | TRISB  |

| FF2h | INTCON   | FD2h | LVDCON   | FB2h | TMR3L    | F92h | TRISA  |

| FF1h | INTCON2  | FD1h | WDTCON   | FB1h | T3CON    | F91h | LATJ   |

| FF0h | INTCON3  | FD0h | RCON     | FB0h | PSPCON   | F90h | LATH   |

| FEFh | INDF0    | FCFh | TMR1H    | FAFh | SPBRG    | F8Fh | LATG   |

| FEEh | POSTINC0 | FCEh | TMR1L    | FAEh | RCREG    | F8Eh | LATF   |

| FEDh | POSTDEC0 | FCDh | T1CON    | FADh | TXREG    | F8Dh | LATE   |

| FECh | PREINC0  | FCCh | TMR2     | FACh | TXSTA    | F8Ch | LATD   |

| FEBh | PLUSW0   | FCBh | PR2      | FABh | RCSTA    | F8Bh | LATC   |

| FEAh | FSR0H    | FCAh | T2CON    | FAAh | _        | F8Ah | LATB   |

| FE9h | FSR0L    | FC9h | SSPBUF   | FA9h | _        | F89h | LATA   |

| FE8h | WREG     | FC8h | SSPADD   | FA8h | _        | F88h | PORTJ  |

| FE7h | INDF1    | FC7h | SSPSTAT  | FA7h | CSEL2    | F87h | PORTH  |

| FE6h | POSTINC1 | FC6h | SSPCON1  | FA6h | CSELIO   | F86h | PORTG  |

| FE5h | POSTDEC1 | FC5h | SSPCON2  | FA5h | _        | F85h | PORTF  |

| FE4h | PREINC1  | FC4h | ADRESH   | FA4h | _        | F84h | PORTE  |

| FE3h | PLUSW1   | FC3h | ADRESL   | FA3h | _        | F83h | PORTD  |

| FE2h | FSR1H    | FC2h | ADCON0   | FA2h | IPR2     | F82h | PORTC  |

| FE1h | FSR1L    | FC1h | ADCON1   | FA1h | PIR2     | F81h | PORTB  |

| FE0h | BSR      | FC0h | ADCON2   | FA0h | PIE2     | F80h | PORTA  |

|      |          |      |          |      |          |      |        |

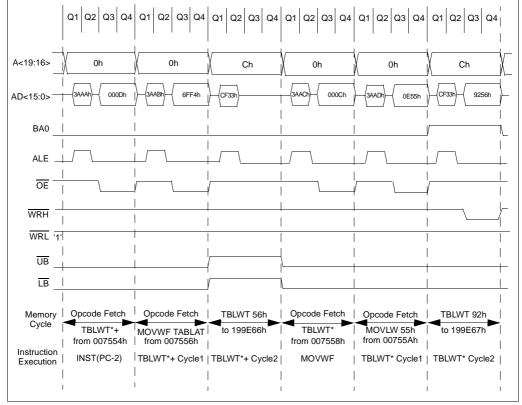

### 6.3 Table Write

Table Write operations store data from the data memory space into external program memory.

PIC18C601/801devices perform Table Writes one byte at a time. Table Writes to external memory are two-cycle instructions, unless wait states are enabled. The last cycle writes the data to the external memory location.

16-bit interface Table Writes depend on the type of external device that is connected and the WM<1:0> bits in the MEMCON register (See Figure 5-2).

Example 6-2 describes how to use TBLWT.

#### **EXAMPLE 6-2: TABLE WRITE CODE EXAMPLE**

```

; Write a byte to location 0020h

CLRF TBLPTRU ; clear upper 5 bits of TBLPTR

CLRF TBLPTRH ; clear higher 8 bits of TBLPTR

MOVLW 20h ; Load 20h into

MOVWF TBLPTRL ; TBLPTRL

MOVLW 55h ; Load 55h into

MOVWF TBLAT ; TBLAT

TBLWT* ; Write it

```

## 6.3.3 EXTERNAL TABLE WRITE IN 16-BIT WORD WRITE MODE

This mode allows Table Writes to any type of word-wide external memories.

This method makes a distinction between TBLWT cycles to even or odd addresses.

During a TBLWT cycle to an even address, where TBLPTR<0> = 0, the TABLAT data is transferred to a holding latch and the external address data bus is tristated for the data portion of the bus cycle. No write signals are activated.

During a TBLWT cycle to an odd address, where TBLPTR<0> = 1, the TABLAT data is presented on the upper byte of the AD<15:0> bus. The contents of the holding latch are presented on the lower byte of the AD<15:0> bus. The  $\overline{WRH}$  line is strobed for each write cycle and the  $\overline{WRL}$  line is unused. The BAO line indicates the LSb of TBLPTR, but it is unnecessary. The  $\overline{UB}$  and  $\overline{LB}$  lines are active to select both bytes.

The obvious limitation to this method is that the TBLWT must be done in pairs on a specific word boundary to correctly write a word location.

Figure 6-9 shows the timing associated with this mode.

#### **REGISTER 8-3: INTCON3 REGISTER**

| R/W-1  | R/W-1  | U-0 | R/W-0  | R/W-0  | U-0 | R/W-0  | R/W-0  |

|--------|--------|-----|--------|--------|-----|--------|--------|

| INT2IP | INT1IP | _   | INT2IE | INT1IE |     | INT2IF | INT1IF |

| bit 7  | •      |     | •      |        |     |        | hit 0  |

bit 7 INT2IP: INT2 External Interrupt Priority bit

1 = High priority

0 = Low priority

bit 6 INT1IP: INT1 External Interrupt Priority bit

1 = High priority

0 = Low priority

bit 5 Unimplemented: Read as '0'

bit 4 INT2IE: INT2 External Interrupt Enable bit

1 = Enables the INT2 external interrupt

0 = Disables the INT2 external interrupt

bit 3 INT1IE: INT1 External Interrupt Enable bit

1 = Enables the INT1 external interrupt

0 = Disables the INT1 external interrupt

bit 2 Unimplemented: Read as '0'

bit 1 INT2IF: INT2 External Interrupt Flag bit

1 = The INT2 external interrupt occurred (must be cleared in software)

0 = The INT2 external interrupt did not occur

bit 0 INT1IF: INT1 External Interrupt Flag bit

1 = The INT1 external interrupt occurred (must be cleared in software)

0 = The INT1 external interrupt did not occur

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

#### **REGISTER 8-7: PIE1 REGISTER**

bit 4

bit 3

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|-------|--------|--------|--------|

| _     | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |       |        |        | bit 0  |

bit 7 Unimplemented: Read as '0'

bit 6 ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D interrupt

0 = Disables the A/D interrupt

bit 5 RCIE: USART Receive Interrupt Enable bit

1 = Enables the USART receive interrupt

0 =Disables the USART receive interrupt

**TXIE**: USART Transmit Interrupt Enable bit 1 = Enables the USART transmit interrupt

0 = Disables the USART transmit interrupt

SSPIE: Master Synchronous Serial Port Interrupt Enable bit

1 = Enables the MSSP interrupt

0 = Disables the MSSP interrupt

bit 2 CCP1IE: CCP1 Interrupt Enable bit

1 = Enables the CCP1 interrupt

0 = Disables the CCP1 interrupt

bit 1 TMR2IE: TMR2 to PR2 Match Interrupt Enable bit

1 = Enables the TMR2 to PR2 match interrupt

0 = Disables the TMR2 to PR2 match interrupt

bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit

1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

NOTES:

TABLE 9-11: PORTF FUNCTIONS

| Name                       | Bit#            | Buffer Type | Function                                                             |  |  |  |

|----------------------------|-----------------|-------------|----------------------------------------------------------------------|--|--|--|

| RF0/AN5                    | bit0            | ST          | Input/output port pin or analog input                                |  |  |  |

| RF1/AN6                    | bit1            | ST          | Input/output port pin or analog input                                |  |  |  |

| RF2/AN7                    | RF2/AN7 bit2 ST |             | Input/output port pin or analog input                                |  |  |  |

| RF3/CSIO                   | bit3            | ST          | Input/output port pin or I/O chip select                             |  |  |  |

| RF4/A16/CS2 <sup>(1)</sup> | bit4            | ST          | Input/output port pin or chip select 2 or address bit 16             |  |  |  |

| RF5/CS1                    | bit5            | ST          | Input/output port pin or chip select 1                               |  |  |  |

| RF6/LB                     | bit6            | ST          | Input/output port pin or low byte select signal for external memory  |  |  |  |

| RF7/UB                     | bit7            | ST          | Input/output port pin or high byte select signal for external memory |  |  |  |

Legend: ST = Schmitt Trigger input

Note 1: CS2 is available only on PIC18C801.

TABLE 9-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTF

| Name   | Bit 7                                 | Bit 6       | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|---------------------------------------|-------------|-----------|-----------|-----------|-----------|-------|-------|--------------------------|---------------------------------|

| TRISF  | PORTF D                               | ata Directi | ion Contr |           | 1111 1111 | 1111 1111 |       |       |                          |                                 |

| PORTF  | Read PO                               | RTF pin/W   | rite POR  | TF Data I | _atch     |           |       |       | xxxx xxxx                | uuuu uuuu                       |

| LATF   | Read PO                               | RTF Data    | Latch/Wr  | ite PORT  | F Data La | atch      |       |       | 0000 0000                | uuuu uuuu                       |

| ADCON1 | - VCFG1 VCFG0 PCFG3 PCFG2 PCFG1 PCFG0 |             |           |           |           |           |       | PCFG0 | 00 0000                  | 00 0000                         |

| MEMCON | EBDIS                                 | PGRM        | WAIT1     | WAIT0     | _         | _         | WM1   | WMO   | 000000                   | 000000                          |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTF.

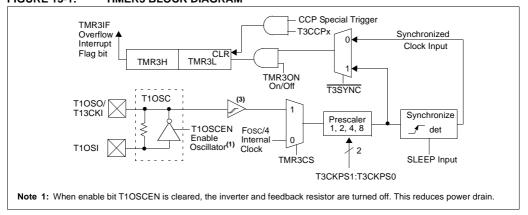

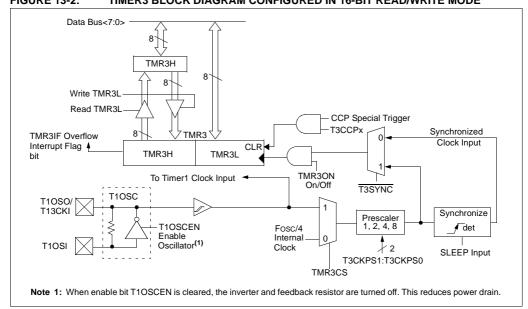

#### 13.1 Timer3 Operation

Timer3 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON register).

When TMR3CS = 0, Timer3 increments every instruction cycle. When TMR3CS = 1, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer3 also has an internal "RESET input". This RESET can be generated by the CCP module (Section 13.0).

### FIGURE 13-1: TIMER3 BLOCK DIAGRAM

FIGURE 13-2: TIMER3 BLOCK DIAGRAM CONFIGURED IN 16-BIT READ/WRITE MODE

TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

| Name    | Bit 7        | Bit 6         | Bit 5          | Bit 4         | Bit 3         | Bit 2        | Bit 1       | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|--------------|---------------|----------------|---------------|---------------|--------------|-------------|--------|-------------------------|---------------------------------|

| INTCON  | GIE/<br>GIEH | PEIE/<br>GIEL | TMR0IE         | INT0IE        | RBIE          | TMR0IF       | INT0IF      | RBIF   | 0000 000x               | 0000 000u                       |

| PIR1    | _            | ADIF          | RCIF           | TXIF          | SSPIF         | CCP1IF       | TMR2IF      | TMR1IF | -000 0000               | -000 0000                       |

| PIE1    | _            | ADIE          | RCIE           | TXIE          | SSPIE         | CCP1IE       | TMR2IE      | TMR1IE | -000 0000               | -000 0000                       |

| IPR1    | _            | ADIP          | RCIP           | TXIP          | SSPIP         | CCP1IP       | TMR2IP      | TMR1IP | -000 0000               | -000 0000                       |

| TRISC   | PORTC D      | ata Directio  | n Register     |               |               |              |             |        | 1111 1111               | 1111 1111                       |

| TMR1L   | Holding re   | gister for th | ne Least Sig   | nificant Byte | of the 16-bi  | t TMR1 Reç   | gister      |        | xxxx xxxx               | uuuu uuuu                       |

| TMR1H   | Holding re   | gister for th | ne Most Sigr   | nificant Byte | of the 16-bit | TMR1 Reg     | ister       |        | xxxx xxxx               | uuuu uuuu                       |

| T1CON   | RD16         | _             | T1CKPS1        | T1CKPS0       | T10SCEN       | T1SYNC       | TMR1CS      | TMR10N | 0-00 0000               | u-uu uuuu                       |

| CCPR1L  | Capture/C    | ompare/PV     | VM Register    | 1 (LSB)       |               |              | •           |        | xxxx xxxx               | uuuu uuuu                       |

| CCPR1H  | Capture/C    | ompare/PV     | VM Register    | 1 (MSB)       |               |              |             |        | xxxx xxxx               | uuuu uuuu                       |

| CCP1CON | _            | _             | DC1B1          | DC1B0         | CCP1M3        | CCP1M2       | CCP1M1      | CCP1M0 | 00 0000                 | 00 0000                         |

| CCPR2L  | Capture/C    | ompare/PV     | VM Register    | 2 (LSB)       |               |              |             |        | xxxx xxxx               | uuuu uuuu                       |

| CCPR2H  | Capture/C    | ompare/PV     | VM Register    | 2 (MSB)       |               |              |             |        | xxxx xxxx               | uuuu uuuu                       |

| CCP2CON | _            | _             | DC2B1          | DC2B0         | CCP2M3        | CCP2M2       | CCP2M1      | CCP2M0 | 00 0000                 | 00 0000                         |

| PIR2    | _            | _             | _              | _             | BCLIF         | LVDIF        | TMR3IF      | CCP2IF | 0000                    | 0000                            |

| PIE2    | _            | _             | _              | _             | BCLIE         | LVDIE        | TMR3IE      | CCP2IE | 0000                    | 0000                            |

| IPR2    | _            | _             | _              | _             | BCLIP         | LVDIP        | TMR3IP      | CCP2IP | 0000                    | 0000                            |

| TMR3L   | Н            | lolding regi  | ster for the I | Least Signifi | cant Byte of  | the 16-bit T | MR3 regist  | er     | xxxx xxxx               | uuuu uuuu                       |

| TMR3H   | H            | lolding reg   | ister for the  | Most Signific | cant Byte of  | the 16-bit T | MR3 registe | er     | xxxx xxxx               | uuuu uuuu                       |

| T3CON   | RD16         | T3CCP2        | T3CKPS1        | T3CKPS0       | T3CCP1        | T3SYNC       | TMR3CS      | TMR3ON | 0000 0000               | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

The MSSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR. until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit, BF (SSPSTAT register), and the interrupt flag bit, SSPIF (PIR registers), are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON1 register), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. The buffer full (BF) bit (SSPSTAT register) indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 15-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP status register (SSPSTAT register) indicates the various status conditions.

#### 15.3.2 ENABLING SPI I/O

To enable the serial port, SSP enable bit, SSPEN (SSPCON1 register), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers, and then set the SSPEN bit. This configures the SDI, SDO, SCK, and  $\overline{\text{SS}}$  pins as serial port pins. For the pins to behave as the serial port function, corresponding pins must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- · SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- RA5 must be configured as digital I/O using ADCON1 register

- SS must have TRISA<5> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### EXAMPLE 15-1: LOADING THE SSPBUF (SSPSR) REGISTER

| LOOP BTFSS SSPSTAT, BF<br>BRA LOOP | ;Has data been received (transmit complete)? ;No                        |

|------------------------------------|-------------------------------------------------------------------------|

| MOVF SSPBUF, W MOVWF RXDATA        | ;WREG reg = contents of SSPBUF ;Save in user RAM, if data is meaningful |

| MOVF TXDATA, W MOVWF SSPBUF        | ;W reg = contents of TXDATA ;New data to xmit                           |

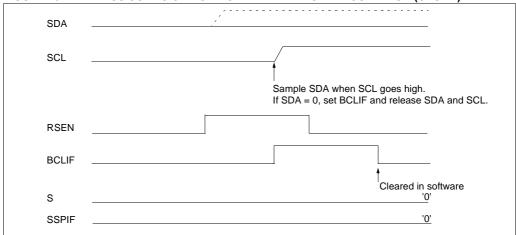

### 15.4.16.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 15-24). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time

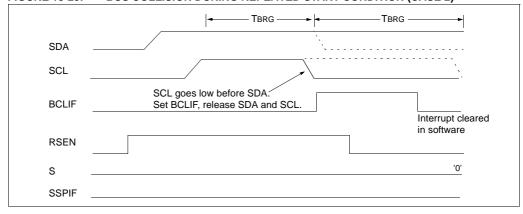

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition (Figure 15-25).

If, at the end of the BRG time-out both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete.

FIGURE 15-24: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 15-25: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### 16.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode, in that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA register).

## 16.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will be set.

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

When setting up a Synchronous Slave Transmission, follow these steps:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- Enable the transmission by setting enable bit TXFN

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

### 16.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register, and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector.

When setting up a Synchronous Slave Reception, follow these steps:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete. An interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

| TADI E 16 10. | REGISTERS ASSOCIATE | A WITH CANCHDUNGING C | I AVE TO ANGMISSION |

|---------------|---------------------|-----------------------|---------------------|

| TABLE 10-10:  | KEGISTEKS ASSUCIATE | J WITH STNURKUNUUS S  | LAVE IKANSINISSIUN  |

| Name   | Bit 7     | Bit 6         | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-----------|---------------|---------|-----------|-----------|--------|--------|--------|-------------------------|---------------------------------|

| INTCON | GIE/GIEH  | PEIE/GIEL     | TMR0IE  | INT0IE    | RBIE      | TMR0IF | INT0IF | RBIF   | 0000 000x               | 0000 000u                       |

| PIR1   | _         | ADIF          | RCIF    | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | -000 0000               | -000 0000                       |

| PIE1   | _         | ADIE          | RCIE    | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | -000 0000               | -000 0000                       |

| IPR1   | _         | ADIP          | RCIP    | TXIP      | SSPIP     | CCP1IP | TMR2IP | TMR1IP | -000 0000               | -000 0000                       |

| RCSTA  | SPEN      | RX9           | SREN    | CREN      | _         | FERR   | OERR   | RX9D   | 0000 -00x               | 0000 -00x                       |

| TXREG  | USART Tra | ansmit Regist |         | 0000 0000 | 0000 0000 |        |        |        |                         |                                 |

| TXSTA  | CSRC      | TX9           | TXEN    | SYNC      | ADDEN     | BRGH   | TRMT   | TX9D   | 0000 0010               | 0000 0010                       |

| SPBRG  | Baud Rate | Generator R   | egister |           |           |        |        |        | 0000 0000               | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

### 17.0 10-BIT ANALOG-TO-DIGITAL **CONVERTER (A/D) MODULE**

The analog-to-digital (A/D) converter module has 8 inputs for the PIC18C601 devices and 12 for the PIC18C801 devices. This module has the ADCON0, ADCON1, and ADCON2 registers.

The A/D allows conversion of an analog input signal to a corresponding 10-bit digital number.

The A/D module has five registers:

- · A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- · A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 17-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 17-2, configures the functions of the port pins. The ADCON2, shown in Register 16-3, configures the A/D clock source and justification.

#### REGISTER 17-1: ADCON0 REGISTER

|   | U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|---|-------|-----|-------|-------|-------|-------|---------|-------|

|   | _     | _   | CHS3  | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| b | oit 7 | •   | ,     | •     | •     | •     |         | bit 0 |

#### bit 7-6 Unimplemented: Read as '0'

#### bit 5-2 CHS3:CHS0: Analog Channel Select bits

0000 = channel 00. (AN0)

0001 = channel 01, (AN1)

0010 = channel 02, (AN2)

0011 = channel 03, (AN3)

0100 = channel 04, (AN4)

0101 = channel 05, (AN5)

0110 = channel 06, (AN6)

0111 = channel 07, (AN7)

1000 = channel 08, (AN8)(1)

1001 = channel 09, (AN9)(1)

1010 = channel 10, (AN10)<sup>(1)</sup>

1011 = channel 11, (AN11)<sup>(1)</sup>

1100 = Reserved

1101 = Reserved

1110 = Reserved

1111 = Reserved

These channels are not available on the PIC18C601 devices.

#### GO/DONE: A/D Conversion Status bit bit 1

#### When ADON = 1:

1 = A/D conversion in progress. Setting this bit starts an A/D conversion cycle. This bit is automatically cleared by hardware when the A/D conversion is complete.

0 = A/D conversion not in progress

#### bit 0 ADON: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shut-off and consumes no operating current

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| AND                                                                                                                                                                                    | )WF          | AND WRE                                             | G with                                              | f                                            |                                                    |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|-----------------------------------------------------|----------------------------------------------|----------------------------------------------------|------|

| Synt                                                                                                                                                                                   | ax:          | [ label ] ANDWF f [,d [,a]]                         |                                                     |                                              |                                                    |      |

| Ope                                                                                                                                                                                    | rands:       | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ |                                                     |                                              |                                                    |      |

| Ope                                                                                                                                                                                    | ration:      | (WREG)                                              | AND. (f)                                            | $\rightarrow$ de                             | est                                                |      |

| Statu                                                                                                                                                                                  | us Affected: | N,Z                                                 |                                                     |                                              |                                                    |      |

| Enco                                                                                                                                                                                   | oding:       | 0001 01da ffff fff                                  |                                                     |                                              |                                                    | ffff |

| Description:  The contents of WRE with register 'f'. If 'd' is stored in WREG. If 'd' is stored back in regis If 'a' is 0, the Access selected. If 'a' is 1, the selected as per the E |              |                                                     | d' is 0,<br>f 'd' is<br>egister<br>ess Ba<br>I, the | the re<br>1, the<br>'f' (de<br>ank w<br>bank | esult is<br>result<br>fault).<br>ill be<br>will be |      |

| Wor                                                                                                                                                                                    | ds:          | 1                                                   |                                                     |                                              |                                                    |      |

| Cycles:                                                                                                                                                                                |              | 1                                                   |                                                     |                                              |                                                    |      |

| Q Cycle Activity:                                                                                                                                                                      |              |                                                     |                                                     |                                              |                                                    |      |

|                                                                                                                                                                                        | Q1           | Q2                                                  | Q3                                                  | 3                                            | C                                                  | Q4   |

|                                                                                                                                                                                        | Decode       | Read<br>register 'f'                                | Proce<br>Data                                       |                                              | Writ<br>destir                                     |      |

| Example: | ANDWF | REG, | W |

|----------|-------|------|---|

Before Instruction

WREG = 17h REG = 0C2h N = ? Z = ?

After Instruction

WREG = 02h REG = 0C2h N = 0 Z = 0

| вс                            | Branch if Carry                                                                                                                                                                                         |      |      |      |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|

| Syntax:                       | [label] BC n                                                                                                                                                                                            |      |      |      |  |

| Operands:                     | -128 ≤ n ≤ 127                                                                                                                                                                                          |      |      |      |  |

| Operation:                    | if carry bit is '1' $(PC) + 2 + 2n \rightarrow PC$                                                                                                                                                      |      |      |      |  |

| Status Affected:              | None                                                                                                                                                                                                    |      |      |      |  |

| Encoding:                     | 1110                                                                                                                                                                                                    | 0010 | nnnn | nnnn |  |

| Description:                  | If the Carry bit is '1', then the pr                                                                                                                                                                    |      |      |      |  |

|                               | The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC+2+2n. This instruction is then a two-cycle instruction. |      |      |      |  |

| Words:                        | 1                                                                                                                                                                                                       |      |      |      |  |

| Cycles:                       | 1(2)                                                                                                                                                                                                    |      |      |      |  |

| Q Cycle Activity:<br>If Jump: |                                                                                                                                                                                                         |      |      |      |  |

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | 'n'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | 'n'          | Data    | operation |

Example: HERE BC 5

Before Instruction

PC = address (HERE)

After Instruction

If Carry

$\begin{array}{lll} \mbox{If Carry} & = & 1; \\ \mbox{PC} & = & \mbox{address (HERE+12)} \\ \mbox{If Carry} & = & 0; \end{array}$

PC = address (HERE+2)

|--|

[label] BRA n Syntax: Operands:  $\textbf{-}1024 \leq n \leq 1023$ Operation:  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1101 nnnn nnnn Description:

Add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC+2+2n. This instruction is a twocycle instruction.

Words:

2 Cycles:

Q Cycle Activity:

| Q1        | Q2           | Q3        | Q4          |

|-----------|--------------|-----------|-------------|

| Decode    | Read literal | Process   | Write to PC |

|           | 'n'          | Data      |             |

| No        | No           | No        | No          |

| operation | operation    | operation | operation   |

Example: HERE BRA Jump

Before Instruction

PC address (HERE)

After Instruction

PC address (Jump) **BSF** Bit Set f

Syntax: [label] BSF f, b [,a]

Operands:  $0 \le f \le 255$  $0 \le b \le 7$

$a \in [0,1]$

Operation:  $1 \rightarrow f < b >$

Status Affected: None

Encoding: 1000 bbba ffff ffff Description: Bit 'b' in register 'f' is set. If 'a' is 0

Access Bank will be selected, overriding the BSR value. If 'a' is 1, the Bank will be selected as per the BSR

value (default).

Words: Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: BSF FLAG REG, 7

Before Instruction

FLAG\_REG 0Ah

After Instruction

FLAG\_REG 8Ah

| GOTO                                                | Unconditional Branch                                          |                             |                            |                                        |  |

|-----------------------------------------------------|---------------------------------------------------------------|-----------------------------|----------------------------|----------------------------------------|--|

| Syntax:                                             | [ label ]                                                     | GOTO                        | k                          |                                        |  |

| Operands:                                           | $0 \le k \le 10$                                              | 048575                      |                            |                                        |  |

| Operation:                                          | $k \rightarrow PC <$                                          | 20:1>                       |                            |                                        |  |

| Status Affected:                                    | None                                                          |                             |                            |                                        |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                  | 1111<br>k <sub>19</sub> kkk | k <sub>7</sub> kkk<br>kkkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |  |

| Description:                                        | GOTO allows an unconditional branch anywhere within entire 2M |                             |                            |                                        |  |

by the memory range. The 20-bit value 'k' is loaded into PC<20:1>. GOTO is always a two-cycle

instruction.

Words: 2

Cycles: 2

Q Cycle Activity:

| Q1        | Q2           | Q3        | Q4           |

|-----------|--------------|-----------|--------------|

| Decode    | Read literal | No        | Read literal |

|           | 'k'<7:0>,    | operation | 'k'<19:8>,   |

|           |              |           | Write to PC  |

| No        | No           | No        | No           |

| operation | operation    | operation | operation    |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INCF              | Increme                                            | nt f                                                                            |                                                                                     |                                                         |

|-------------------|----------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------|

| Syntax:           | [ label ]                                          | INCF f                                                                          | [,d [,a]]                                                                           |                                                         |

| Operands:         | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$ | 55                                                                              |                                                                                     |                                                         |

| Operation:        | (f) + 1 $\rightarrow$                              | dest                                                                            |                                                                                     |                                                         |

| Status Affected:  | C,DC,N,                                            | OV,Z                                                                            |                                                                                     |                                                         |

| Encoding:         | 0010                                               | 10da                                                                            | ffff                                                                                | ffff                                                    |

| Description:      | in WREG<br>placed ba<br>'a' is 0, th<br>selected,  | f 'd' is 0, t<br>i. If 'd' is<br>ack in reg<br>ae Acces<br>overridir<br>the Ban | he result i<br>1, the res<br>ister 'f' (de<br>s Bank w<br>ng the BSI<br>k will be s | s placed<br>ult is<br>efault). If<br>ill be<br>R value. |

| Words:            | 1                                                  |                                                                                 |                                                                                     |                                                         |

| Cycles:           | 1                                                  |                                                                                 |                                                                                     |                                                         |

| Q Cycle Activity: |                                                    |                                                                                 |                                                                                     |                                                         |

| Q1                | Q2                                                 | Q3                                                                              | 3                                                                                   | Q4                                                      |

| Decode      |       | Read<br>register 'f' | Process<br>Data | Write to destination |  |  |

|-------------|-------|----------------------|-----------------|----------------------|--|--|

| <u>Exar</u> | nple: | INCF                 | CNT             |                      |  |  |

Before Instruction CNT 0FFh Z 0 С ? DC ? After Instruction CNT 00h Z 1 С 1

DC

| SLEEP            | Enter SLEEP mode                                                                                                                                                                                  |      |      |      |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                   |      |      |      |  |

| Operands:        | None                                                                                                                                                                                              |      |      |      |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ postscaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                             |      |      |      |  |

| Status Affected: | TO, PD                                                                                                                                                                                            |      |      |      |  |

| Encoding:        | 0000                                                                                                                                                                                              | 0000 | 0000 | 0011 |  |

| Description:     | The power-down status bit (PD) is cleared. The time-out status bit (TO) is set. Watchdog Timer and its postscaler are cleared.  The processor is put into SLEEP mode with the oscillator stopped. |      |      |      |  |

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2        | Q3      | Q4    |  |

|--------|-----------|---------|-------|--|

| Decode | No        | Process | Go to |  |

|        | operation | Data    | sleep |  |

Example: SLEEP

$Befo\underline{re}\ Instruction$

$\frac{\overline{\text{TO}}}{\overline{\text{PD}}} = ?$

After Instruction

$\frac{\overline{\text{TO}}}{\text{PD}} = 0$

† If WDT causes wake-up, this bit is cleared.

| SUBFWB         | Subtract f                                                                                              | Subtract f from WREG with borrow                                                                                                                                                                                                                                                                                               |                      |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:        | [label] S                                                                                               | [ label ] SUBFWB f [,d [,a]]                                                                                                                                                                                                                                                                                                   |                      |  |  |  |

| Operands:      | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                     |                                                                                                                                                                                                                                                                                                                                |                      |  |  |  |

| Operation:     | (WREG) -                                                                                                | $(WREG) - (f) - (\overline{C}) \rightarrow dest$                                                                                                                                                                                                                                                                               |                      |  |  |  |

| Status Affecte | d: N,OV, C, [                                                                                           | OC, Z                                                                                                                                                                                                                                                                                                                          |                      |  |  |  |

| Encoding:      | 0101                                                                                                    | 01da ff                                                                                                                                                                                                                                                                                                                        | ff ffff              |  |  |  |

| Description:   | (borrow) fr<br>ment meth<br>stored in V<br>is stored ir<br>is 0, the A<br>selected, o<br>If 'a' is 1, t | Subtract register 'f' and carry flag (borrow) from WREG (2's complement method). If 'd' is 0, the result is stored in WREG. If 'd' is 1, the result is stored in register 'f' (default). If 'a' is 0, the Access Bank will be selected, overriding the BSR value. If 'a' is 1, the Bank will be selected as per the BSR value. |                      |  |  |  |

| Words:         | 1                                                                                                       | 1                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Cycles:        | 1                                                                                                       | 1                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Q Cycle Activi | ty:                                                                                                     |                                                                                                                                                                                                                                                                                                                                |                      |  |  |  |

| Q1             | Q2                                                                                                      | Q3                                                                                                                                                                                                                                                                                                                             | Q4                   |  |  |  |

| Decode         | Read<br>register 'f'                                                                                    | Process<br>Data                                                                                                                                                                                                                                                                                                                | Write to destination |  |  |  |

TOCKI

TO

### TABLE 22-10: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Symbol                     | Characteristic                                          |                 |                         | Min                      | Max      | Units                | Conditions         |

|--------------|----------------------------|---------------------------------------------------------|-----------------|-------------------------|--------------------------|----------|----------------------|--------------------|

| 40           | Tt0H                       | T0CKI High Pulse Width                                  |                 | No Prescaler            | 0.5Tcy + 20              | _        | ns                   |                    |

|              |                            |                                                         |                 | With Prescaler          | 10                       | _        | ns                   |                    |

| 41           | Tt0L                       | T0CKI L                                                 | ow Pulse Width  | No Prescaler            | 0.5Tcy + 20              | _        | _ns `                | 7                  |

|              |                            |                                                         |                 | With Prescaler          | 10                       | _/       | ns )                 |                    |

| 42           | Tt0P                       | T0CKI F                                                 | Period          | No Prescaler            | Tcy + 10                 | _/ \     | ns                   |                    |

|              |                            | İ                                                       |                 | With Prescaler          | Greater of:              | <u> </u> | ns `                 | W≧ prescale value  |

|              |                            |                                                         |                 |                         | 20 ns or TCY + 40 N      |          | $\backslash \rangle$ | (1, 2, 4,, 256)    |

| 45           | Tt1H                       | T1CKI                                                   | Synchronous, no | o prescaler             | (0.5Tey + 20             | ( - ·    | ns                   |                    |

|              |                            | High<br>Time                                            | Synchronous,    | PIC18C601/801           | / / Jtb /                | _        | ns                   |                    |

|              |                            |                                                         | with prescaler  | PIC18 <b>LC</b> 601/801 | \ \ \25 \                | _        | ns                   |                    |

|              |                            |                                                         | Asynchronous    | PIC18C601/801           | / \ 30                   | _        | ns                   |                    |

|              |                            |                                                         | <               | P(C18LC601/801          | 50                       | _        | ns                   |                    |

| 46           | Tt1L                       | T1CKI                                                   | Synchronous, no | o prescaler             | 0.5Tcy + 5               | _        | ns                   |                    |

|              |                            | Low                                                     | Synchronous,    | PIC18C601/801           | 10                       | _        | ns                   |                    |

|              |                            | Time                                                    | with prescaler  | PIC18LC601/801          | 25                       | _        | ns                   |                    |

|              |                            |                                                         | Asynchronous    | PIC18C601/801           | 30                       | _        | ns                   |                    |

|              | /                          |                                                         |                 | PIC18 <b>LC</b> 601/801 | TBD                      | TBD      | ns                   |                    |

| 47           | Tt1P 🤇 <                   | T1CKL                                                   | Synchronous     |                         | Greater of:              | _        | ns                   | N = prescale value |

|              |                            | input \                                                 |                 |                         | 20 ns or <u>Tcy + 40</u> |          |                      | (1, 2, 4, 8)       |

|              | $\langle \rangle \rangle $ | period                                                  |                 |                         | N                        |          |                      |                    |

|              | <u> </u>                   | $\vee$                                                  | Asynchronous    |                         | 60                       | _        | ns                   |                    |

|              | \Ft'\                      | T1CKI oscillator input frequency range                  |                 |                         | DC                       | 50       | kHz                  |                    |

| 48           | Toke2tmrl                  | Delay from external T1CKI clock edge to timer increment |                 |                         | 2Tosc                    | 7Tosc    | _                    |                    |

NOTES: