Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 26                                                                        |

| Program Memory Size        | -                                                                         |

| Program Memory Type        | ROMIess                                                                   |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c601t-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    |          |      | Pin N       | umber    |          |             |                |                                      |  |  |

|--------------------|----------|------|-------------|----------|----------|-------------|----------------|--------------------------------------|--|--|

| Pin Na             | ime      | PIC1 | BC601       | PIC1     | 8C801    | Pin<br>Type | Buffer<br>Type |                                      |  |  |

|                    |          | TQFP | PLCC        | TQFP     | PLCC     | туре        | Type           | Description                          |  |  |

|                    |          |      |             |          |          |             |                | PORTF is a bi-directional I/O port.  |  |  |

| RF0/AN5            |          | 18   | 28          | 24       | 36       |             |                |                                      |  |  |

| RF0                |          |      |             |          |          | I/O         | ST             | Digital I/O.                         |  |  |

| AN5                |          |      |             |          |          | 1           | Analog         | Analog input 5.                      |  |  |

| RF1/AN6            |          | 17   | 27          | 23       | 35       |             |                |                                      |  |  |

| BF1                |          |      |             |          |          | I/O         | ST             | Digital I/O.                         |  |  |

| AN6                |          |      |             |          |          | 1           | Analog         | Analog input 6.                      |  |  |

| RF2/AN7            |          | 16   | 26          | 18       | 30       |             |                |                                      |  |  |

| RF2                |          | 10   | 20          | 10       | 50       | I/O         | ST             | Digital I/O.                         |  |  |

| AN7                |          |      |             |          |          | 1/0         | Analog         | Analog input 7.                      |  |  |

| RF3/CSIO           |          | 15   | 25          | 17       | 29       |             | / indiog       | , malog mpar / .                     |  |  |

| RF3                |          | 15   | 25          | 17       | 29       | I/O         | ST             | Digital I/O.                         |  |  |

| CSIO               |          |      |             |          |          | 1/O         | ST             | System bus chip select I/O.          |  |  |

|                    |          |      | 0.4         |          |          | 1/0         | 31             | System bus chip select i/O.          |  |  |

| RF4/A16<br>RF4/CS2 |          | 14   | 24          | 16       | 28       |             |                |                                      |  |  |

| RF4/052<br>RF4     |          | _    | _           | 10       | 28       | I/O         | ST             | Digital I/O.                         |  |  |

| A16                |          |      |             |          |          | 1/O<br>1/O  | TTL            | External memory address 16.          |  |  |

| CS2                |          |      |             |          |          | 0           | TTL            | Chip select 2.                       |  |  |

|                    |          | 10   |             | 45       | 07       | 0           | 116            | Chip select 2.                       |  |  |

| RF5/CS1            |          | 13   | 23          | 15       | 27       | 1/0         | OT             | Distribut 1/O                        |  |  |

| RF5<br>CS1         |          |      |             |          |          | 1/O<br>O    | ST<br>TTL      | Digital I/O.                         |  |  |

|                    |          |      |             |          |          | 0           | IIL            | Chip select 1.                       |  |  |

| RF6/LB             |          | 12   | 22          | 14       | 26       |             |                |                                      |  |  |

| RF6                |          |      |             |          |          | I/O         | ST             | Digital I/O.                         |  |  |

| LB                 |          |      |             |          |          | 0           | TTL            | Low byte select signal for external  |  |  |

|                    |          |      |             |          |          |             |                | memory interface.                    |  |  |

| RF7/UB             |          | 11   | 21          | 13       | 25       |             |                |                                      |  |  |

| RF7                |          |      |             |          |          | I/O         | ST             | Digital I/O.                         |  |  |

| UB                 |          |      |             |          |          | 0           | TTL            | High byte select signal for external |  |  |

|                    |          |      |             |          |          |             |                | memory interface.                    |  |  |

|                    | TL = TTL |      |             |          |          |             |                | OS compatible input or output        |  |  |

| S                  | ST = Sch |      | ger input v | with CMC | S levels |             | alog = Ana     | 0 1                                  |  |  |

| I                  | = Inpi   | ut   |             |          |          | 0           | = Out          | tput                                 |  |  |

# TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

P = Power

OD = Open Drain (no P diode to VDD)

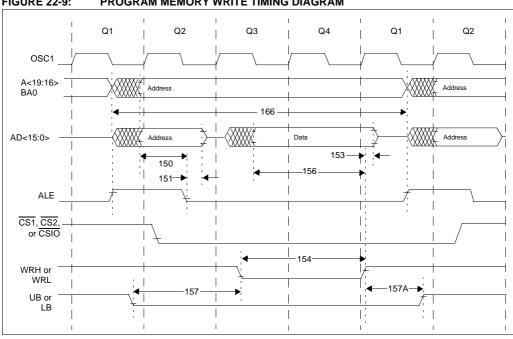

#### 6.3.4 16-BIT EXTERNAL TABLE WRITE (BYTE SELECT MODE)

This mode allows Table Writes to word-wide external memories that have byte selection capabilities. This generally includes word-wide FLASH devices and word-wide static RAM devices.

During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The WRH line is strobed for each write cycle and the  $\overline{\text{WRL}}$  line is unused. The BA0 or  $\overline{\text{UB}}$  or  $\overline{\text{UL}}$  lines are used to select the byte to be written, based on the LSb of the TBLPTR.

JEDEC standard flash memories will require a I/O port line to become a BYTE/WORD input signal and will use the BA0 signal as a byte address. JEDEC standard static RAM memories will use the UB or UL signals to select the byte.

Figure 6-10 shows the timing associated with this mode.

Q1 Q2 Q3 Q4 Q2 Q3 Q4 Q1 A<19:16> 0h 0h Ch 0h 0h Ch 000Dh AAB 6FF4h 000Ch 9292h AD<15:0> 5656h AAC 3440 0E55h CF33 CE33 BA0 ALE OE WRH WRL '1' UB LB **Opcode Fetch** Memory Opcode Fetch TBLWT 56h Opcode Fetch Opcode Fetch TBLWT 92h Cycle TBLWT\*+ MOVWE TABLAT to 199E66h TBI WT\* MOVLW 55h to 199E67h from 00755Ah from 007554h from 007556h from 007558h Instruction INST(PC-2) TBLWT\*+ Cycle1 | TBLWT\*+ Cycle2 | MOVWF TBLWT\* Cycle1 | TBLWT\* Cycle2 Execution

#### TABLE 9-7: PORTD FUNCTIONS

| Name                      | Bit# | Buffer Type           | Function                                  |

|---------------------------|------|-----------------------|-------------------------------------------|

| RD0/AD0/A0 <sup>(2)</sup> | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 0 |

| RD1/AD1/A1 <sup>(2)</sup> | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 1 |

| RD2/AD2/A2 <sup>(2)</sup> | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 2 |

| RD3/AD3/A3 <sup>(2)</sup> | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 3 |

| RD4/AD4/A4 <sup>(3)</sup> | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 4 |

| RD5/AD5/A5 <sup>(2)</sup> | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 5 |

| RD6/AD6/A6 <sup>(2)</sup> | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 6 |

| RD7/AD7/A7 <sup>(2)</sup> | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or system bus bit 7 |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in System Bus mode.

2: RDx is used as a multiplexed address/data bus for PIC18C601 and PIC18C801 in 16-bit mode, and as an address only for PIC18C801 in 8-bit mode.

| IADLE 9-0: SUMIMART OF REGISTERS ASSOCIATED WITH PORTU | TABLE 9-8: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTD |

|--------------------------------------------------------|------------|--------------------------------------------|

|--------------------------------------------------------|------------|--------------------------------------------|

| Name   | Bit 7                         | Bit 6      | Bit 5 | Bit 4     | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-------------------------------|------------|-------|-----------|-----------|-------|-------|-------|-------------------------|---------------------------------|

| PORTD  | RD7                           | RD6        | RD5   | RD4       | RD3       | RD2   | RD1   | RD0   | xxxx xxxx               | uuuu uuuu                       |

| LATD   | LATD Data                     | a Output R |       | XXXX XXXX | uuuu uuuu |       |       |       |                         |                                 |

| TRISD  | PORTD Data Direction Register |            |       |           |           |       |       |       | 1111 1111               | 1111 1111                       |

| MEMCON | EBDIS                         | PGRM       | WAIT1 | WAIT0     |           |       | WM1   | WM0   | 000000                  | 000000                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTD.

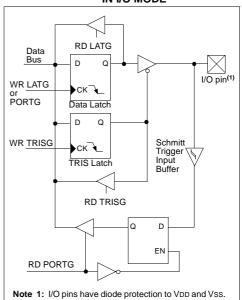

### 9.7 PORTG, LATG, and TRISG Registers

PORTG is a 5-bit wide, bi-directional port. The corresponding data direction register is TRISG. Setting a TRISG bit (= 1) will make the corresponding PORTG pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISG bit (= 0) will make the corresponding PORTG pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATG register read and write the latched output value for PORTG.

PORTG is multiplexed with system bus control signals ALE, OE, WRH, WRL and BA0. The WRH signal is the only signal that is disabled and configured as a port pin (RG3) during external program execution in 8-bit mode. All other pins are by default, system bus control signals. PORTG can be configured as an I/O port by setting EBDIS bit in the MEMCON register and when execution is taking place in internal program RAM.

| Note: | On Power-on Reset, PORTG defaults to |  |  |  |  |  |  |  |

|-------|--------------------------------------|--|--|--|--|--|--|--|

|       | system bus signals.                  |  |  |  |  |  |  |  |

#### EXAMPLE 9-8: INITIALIZING PORTG

| CLRF  | PORTG | ; Initialize PORTG by    |

|-------|-------|--------------------------|

|       |       | ; clearing output        |

|       |       | ; data latches           |

| CLRF  | LATG  | ; Alternate method       |

|       |       | ; to clear output        |

|       |       | ; data latches           |

| MOVLW | 04h   | ; Value used to          |

|       |       | ; initialize data        |

|       |       | ; direction              |

| MOVWF | TRISG | ; Set RG1:RG0 as outputs |

|       |       | ; RG2 as input           |

|       |       | ; RG4:RG3 as outputs     |

|       |       | _                        |

#### FIGURE 9-14: PORTG BLOCK DIAGRAM IN I/O MODE

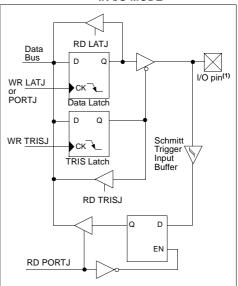

### 9.9 PORTJ, LATJ, and TRISJ Registers

| Note: | PORTJ is | available | only | on | PIC18C801 |

|-------|----------|-----------|------|----|-----------|

|       | devices. |           |      |    |           |

PORTJ is an 8-bit wide, bi-directional I/O port. The corresponding data direction register is TRISJ. Setting a TRISJ bit (= 1) will make the corresponding PORTJ pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISJ bit (= 0) will make the corresponding PORTJ pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATJ register read and write the latched output value for PORTJ.

PORTJ is multiplexed with de-multiplexed system data bus D7:D0, when device is configured in 8-bit execution mode. Register MEMCON configures PORTJ as I/O or system bus pins.

| Note: | On Power-on Reset, PORTJ defaults to |  |  |  |  |  |  |  |  |

|-------|--------------------------------------|--|--|--|--|--|--|--|--|

|       | system bus signals.                  |  |  |  |  |  |  |  |  |

#### EXAMPLE 9-10: INITIALIZING PORTJ

| CLRF  | PORTJ | ; Initialize PORTJ by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATJ  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0CFh  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISJ | ; Set RJ3:RJ0 as inputs |

|       |       | ; RJ5:RJ4 as outputs    |

|       |       | ; RJ7:RJ6 as inputs     |

|       |       | -                       |

#### FIGURE 9-19: PORTJ BLOCK DIAGRAM IN I/O MODE

#### TABLE 9-17: PORTJ FUNCTIONS

| Name                  | Bit# | Buffer Type | Function                                                          |

|-----------------------|------|-------------|-------------------------------------------------------------------|

| RJ0/D0 <sup>(1)</sup> | bit0 | ST/TTL      | Input/output port pin or Data bit 0 for external memory interface |

| RJ1/D1 <sup>(1)</sup> | bit1 | ST/TTL      | Input/output port pin or Data bit 1 for external memory interface |

| RJ2/D2 <sup>(1)</sup> | bit2 | ST/TTL      | Input/output port pin or Data bit 2 for external memory interface |

| RJ3/D3 <sup>(1)</sup> | bit3 | ST/TTL      | Input/output port pin or Data bit 3 for external memory interface |

| RJ4/D4 <sup>(1)</sup> | bit4 | ST/TTL      | Input/output port pin or Data bit 4 for external memory interface |

| RJ5/D5 <sup>(1)</sup> | bit5 | ST/TTL      | Input/output port pin or Data bit 5 for external memory interface |

| RJ6/D6 <sup>(1)</sup> | bit6 | ST/TTL      | Input/output port pin or Data bit 6 for external memory interface |

| RJ7/D7 <sup>(1)</sup> | bit7 | ST/TTL      | Input/output port pin or Data bit 7 for external memory interface |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: PORTJ is available only on PIC18C801 devices.

#### TABLE 9-18: SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ

| Name   | Bit 7                                           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| TRISJ  | PORTJ Data Direction Control Register           |       |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| PORTJ  | Read PORTJ pin/Write PORTJ Data Latch           |       |       |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                       |

| LATJ   | TJ Read PORTJ Data Latch/Write PORTJ Data Latch |       |       |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                       |

| MEMCON | EBDIS                                           | PGRM  | WAIT1 | WAIT0 | _     | —     | WM1   | WM0   | 000000                   | 000000                          |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTJ.

# 11.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers: TMR1H and TMR1L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- RESET from CCP module special event trigger

Register 11-1 shows the Timer1 Control register. This register controls the operating mode of the Timer1 module as well as contains the Timer1 oscillator enable bit (T10SCEN). Timer1 can be enabled/disabled by setting/clearing control bit TMR10N (T1CON register).

Figure 11-1 is a simplified block diagram of the Timer1 module.

Note: Timer1 is disabled on POR.

### REGISTER 11-1: T1CON REGISTER

|         | R/W-0                                                    | U-0                                               | R/W-0                           | R/W-0              | R/W-0                           | R/W-0         | R/W-0        | R/W-0  |

|---------|----------------------------------------------------------|---------------------------------------------------|---------------------------------|--------------------|---------------------------------|---------------|--------------|--------|

|         | RD16                                                     | —                                                 | T1CKPS1                         | T1CKPS0            | T1OSCEN                         | T1SYNC        | TMR1CS       | TMR10N |

|         | bit 7                                                    |                                                   |                                 |                    |                                 |               |              | bit 0  |

| bit 7   | RD16: 16-                                                | oit Read/W                                        | /rite Mode E                    | nable bit          |                                 |               |              |        |

|         |                                                          | •                                                 |                                 |                    | one 16-bit ope<br>wo 8-bit oper |               |              |        |

| bit 6   | Unimplem                                                 | ented: Re                                         | ad as '0'                       |                    |                                 |               |              |        |

| bit 5-4 | T1CKPS1:                                                 | T1CKPS0                                           | : Timer1 Inp                    | ut Clock Pres      | scale Select b                  | oits          |              |        |

|         | 11 = 1:8 Pr<br>10 = 1:4 Pr<br>01 = 1:2 Pr<br>00 = 1:1 Pr | rescale va<br>rescale va                          | lue<br>lue                      |                    |                                 |               |              |        |

| bit 3   | T1OSCEN                                                  | : Timer1 C                                        | scillator Ena                   | able bit           |                                 |               |              |        |

|         | 1 = Timer1<br>0 = Timer1<br>The os                       | Oscillator                                        | is shut-off                     | dback resist       | or are turned                   | off to elimin | ate power d  | rain.  |

| bit 2   | T1SYNC:                                                  | Fimer1 Ext                                        | ernal Clock                     | Input Synchr       | onization Sele                  | ect bit       |              |        |

|         | When TMF<br>1 = Do not<br>0 = Synchr<br>When TMF         | R1CS = 1:<br>synchroni<br>onize exte<br>R1CS = 0: | ze external o<br>ernal clock in | clock input<br>put | ock when TMI                    |               |              |        |

| bit 1   | TMR1CS:                                                  | Timer1 Clo                                        | ock Source S                    | Select bit         |                                 |               |              |        |

|         | 1 = Externa<br>0 = Interna                               |                                                   | •                               | T1OSO/T130         | CKI (on the ris                 | ing edge)     |              |        |

| bit 0   | TMR10N:                                                  | Timer1 Or                                         | n bit                           |                    |                                 |               |              |        |

|         | 1 = Enable<br>0 = Stops ⊺                                |                                                   |                                 |                    |                                 |               |              |        |

|         | Legend:                                                  |                                                   |                                 |                    |                                 |               |              |        |

|         | R = Reada                                                | ble bit                                           | W =                             | Writable bit       | U = Unim                        | plemented     | bit, read as | '0'    |

'1' = Bit is set

- n = Value at POR

'0' = Bit is cleared

x = Bit is unknown

bit

bit

bit

bit

bit

bit

bit

bit

- n = Value at POR

#### REGISTER 15-3: SSPCON2 REGISTER

| R/W-0                                 | R/W-0                                                                          | R/W-0                                 | R/W-0        | R/W-0       | R/W-0       | R/W-0        | R/W-0     |

|---------------------------------------|--------------------------------------------------------------------------------|---------------------------------------|--------------|-------------|-------------|--------------|-----------|

| GCEN                                  | ACKSTAT                                                                        | ACKDT                                 | ACKEN        | RCEN        | PEN         | RSEN         | SEN       |

| bit 7                                 |                                                                                |                                       |              |             |             |              | bit 0     |

| 1 = Enable                            | neral Call Ena<br>interrupt whe<br>al call address                             | en a general                          |              |             | eceived in  | the SSPSR    | 1         |

| In Master 7                           | Acknowledge<br>ransmit mode<br>vledge was ne<br>vledge was re                  | <u>ə:</u><br>ot received f            | rom slave    | r mode only | ()          |              |           |

| In Master F                           |                                                                                | <u>.</u>                              |              | • •         | quence at   | the end of a | a receive |

| In Master F<br>1 = Initiate<br>Automa | cknowledge S<br>Receive mode<br>Acknowledge<br>atically cleare<br>vledge seque | <u>:</u><br>sequence o<br>d by hardwa | on SDA and S |             |             |              | ta bit.   |

|                                       | ceive Enable<br>s Receive mo<br>e idle                                         |                                       | laster mode  | only)       |             |              |           |

| SCK releas                            | P Condition E<br>se control<br>STOP conditi<br>condition idle                  |                                       |              | • •         | ally cleare | d by hardwa  | are.      |

| 1 = Initiate<br>by hard               | Deated STAR<br>Repeated ST<br>dware.<br>ted START co                           | ART conditi                           |              |             |             |              | d         |

| SEN: STAR<br>1 = Initiate             | RT Condition<br>START condi<br>condition idle                                  | Enabled bit (<br>ition on SDA         |              |             |             | ed by hardv  | vare.     |

| I                                     | For bits ACKI<br>mode, this bit<br>writes to the S                             | may not be                            | set (no spoo |             |             |              |           |

| Legend:                               |                                                                                |                                       |              |             |             |              |           |

| R = Reada                             | ble bit                                                                        | W = Wr                                | itable bit   | U = Unimp   | lemented I  | oit, read as | '0'       |

|                                       |                                                                                |                                       |              |             |             |              |           |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

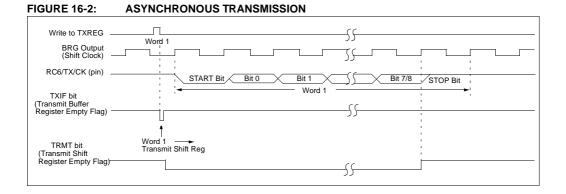

#### FIGURE 16-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 16-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Value on<br>all other<br>RESETS | DR,                  | Value on<br>POR,<br>BOR             | Bit 0          | Bit 1          | Bit 2                  | Bit 3               | Bit 4                | Bit 5                                    | Bit 6                              | Bit 7                          | Name                            |

|---------------------------------|----------------------|-------------------------------------|----------------|----------------|------------------------|---------------------|----------------------|------------------------------------------|------------------------------------|--------------------------------|---------------------------------|

| 0000 000u                       | 000x                 | 0000 000x                           | RBIF           | <b>INT0IF</b>  | TMR0IF                 | RBIE                | INT0IE               | TMR0IE                                   | PEIE/GIEL                          | GIE/GIEH                       | INTCON                          |

| 000 0000                        | 0000                 | -000 0000                           | TMR1IF         | TMR2IF         | CCP1IF                 | SSPIF               | TXIF                 | RCIF                                     | ADIF                               | —                              | PIR1                            |

| 000 0000                        | 0000                 | -000 0000                           | TMR1IE         | TMR2IE         | CCP1IE                 | SSPIE               | TXIE                 | RCIE                                     | ADIE                               | —                              | PIE1                            |

| 000 0000                        | 0000                 | -000 0000                           | TMR1IP         | TMR2IP         | CCP1IP                 | SSPIP               | TXIP                 | RCIP                                     | ADIP                               | —                              | IPR1                            |

| 0000 -00x                       | -00x                 | 0000 -00x                           | RX9D           | OERR           | FERR                   | —                   | CREN                 | SREN                                     | RX9                                | SPEN                           | RCSTA                           |

| 0000 0000                       | 0000                 | 0000 0000                           |                |                |                        |                     |                      | ster                                     | ansmit Regis                       | USART Tra                      | TXREG                           |

| 0000 0010                       | 0010                 | 0000 0010                           | TX9D           | TRMT           | BRGH                   | ADDEN               | SYNC                 | TXEN                                     | TX9                                | CSRC                           | TXSTA                           |

| 0000 0000                       | 0000                 | 0000 0000                           |                |                |                        |                     |                      | Register                                 | Generator I                        | Baud Rate                      | SPBRG                           |

|                                 | -00x<br>0000<br>0010 | 0000 -00x<br>0000 0000<br>0000 0010 | TMR1IP<br>RX9D | TMR2IP<br>OERR | CCP1IP<br>FERR<br>BRGH | SSPIP<br>—<br>ADDEN | TXIP<br>CREN<br>SYNC | RCIP<br>SREN<br>ster<br>TXEN<br>Register | ADIP<br>RX9<br>ansmit Regis<br>TX9 | USART Tra<br>CSRC<br>Baud Rate | IPR1<br>RCSTA<br>TXREG<br>TXSTA |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

#### **REGISTER 17-2: ADCON1 REGISTER**

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-4 VCFG1:VCFG0: Voltage Reference Configuration bits

|     | A/D VREF+      | A/D VREF-      |

|-----|----------------|----------------|

| 0 0 | Avdd           | Avss           |

| 01  | External VREF+ | Avss           |

| 10  | Avdd           | External VREF- |

| 11  | External VREF+ | External VREF- |

bit 3-0 PCFG3:PCFG0: A/D Port Configuration Control bits

|      | AN11 | AN10 | AN9 | AN8 | AN7 | AN6 | AN5 | AN4 | AN3 | AN2 | AN1 | AN0 |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000 | Α    | А    | А   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0001 | А    | А    | А   | А   | А   | А   | А   | Α   | Α   | А   | А   | А   |

| 0010 | А    | А    | А   | А   | А   | А   | А   | Α   | Α   | А   | А   | А   |

| 0011 | А    | А    | А   | А   | А   | А   | А   | А   | А   | А   | А   | А   |

| 0100 | D    | А    | А   | А   | А   | Α   | А   | Α   | Α   | А   | А   | Α   |

| 0101 | D    | D    | А   | А   | А   | А   | А   | А   | А   | А   | А   | А   |

| 0110 | D    | D    | D   | Α   | А   | Α   | А   | Α   | Α   | А   | Α   | А   |

| 0111 | D    | D    | D   | D   | А   | А   | А   | А   | А   | А   | А   | А   |

| 1000 | D    | D    | D   | D   | D   | А   | А   | А   | А   | А   | А   | А   |

| 1001 | D    | D    | D   | D   | D   | D   | А   | Α   | Α   | А   | А   | А   |

| 1010 | D    | D    | D   | D   | D   | D   | D   | А   | А   | А   | А   | А   |

| 1011 | D    | D    | D   | D   | D   | D   | D   | D   | Α   | Α   | Α   | А   |

| 1100 | D    | D    | D   | D   | D   | D   | D   | D   | D   | А   | А   | А   |

| 1101 | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | А   | А   |

| 1110 | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | А   |

| 1111 | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

A = Analog input D = Digital I/O

Shaded cells = Additional A/D channels available on PIC18C801 devices.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 17.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 12 TAD per 10-bit conversion. The source of the A/D conversion clock is software selectable. There are seven possible options for TAD:

- 2Tosc

- 4Tosc

- 8Tosc

- 16Tosc

- 32Tosc

- 64Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 17-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

### 17.3 Configuring Analog Port Pins

The ADCON1, TRISA, TRISF and TRISH registers control the operation of the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume current out of the device's specification limits.

| AD Clock S | ource (TAD) | Maximum Device Frequency |                               |  |  |  |

|------------|-------------|--------------------------|-------------------------------|--|--|--|

| Operation  | ADCS2:ADCS0 | PIC18C601/801            | PIC18LC601/801 <sup>(5)</sup> |  |  |  |

| 2Tosc      | 000         | 1.25 MHz                 | 666 kHz                       |  |  |  |

| 4Tosc      | 100         | 2.50 MHz                 | 1.33 MHz                      |  |  |  |

| 8Tosc      | 001         | 5.00 MHz                 | 2.67 MHz                      |  |  |  |

| 16Tosc     | 101         | 10.0 MHz                 | 5.33 MHz                      |  |  |  |

| 32Tosc     | 010         | 20.0 MHz                 | 10.67 MHz                     |  |  |  |

| 64Tosc     | 110         | —                        | _                             |  |  |  |

| RC         | x11         | —                        | _                             |  |  |  |

#### TABLE 17-1: TAD VS. DEVICE OPERATING FREQUENCIES

Note 1: The RC source has a typical TAD time of 4 µs.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: For device frequencies above 1 MHz, the device must be in SLEEP for the entire conversion or the A/D accuracy may be out of specification.

5: This column is for the LC devices only.

### 19.0 SPECIAL FEATURES OF THE CPU

There are several features intended to maximize system reliability, minimize cost through elimination of external components and provide power saving operating modes:

- OSC Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- ID Locations

PIC18C601/801 devices have a Watchdog Timer, which can be permanently enabled/disabled via the configuration bits, or it can be software controlled. By default, the Watchdog Timer is disabled to allow software control. It runs off its own RC oscillator for cost reduction. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Powerup Timer (PWRT), which provides a fixed delay on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up or through an interrupt. Several oscillator options are also available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. By default, HS oscillator mode is selected. There are two main modes of operations for external memory interface: 8-bit and 16-bit (default). A set of configuration bits are used to select various options.

### 19.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h - 3FFFFh), which can only be accessed using table reads and table writes.

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|----------|-------|-------|-------|-------|--------|--------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H | -     | —     |       | -     | —      | —      | FOSC1  | FOSC0  | 11                                |

| 300002h | CONFIG2L | _     | BW    | _     | _     | —      | —      | _      | PWRTEN | -11                               |

| 300003h | CONFIG2H | _     | —     | _     | _     | WDTPS2 | WDTPS1 | WDTPS0 | WDTEN  | 1110                              |

| 300006h | CONFIG4L | r     | _     | _     | _     | —      | —      | _      | STVREN | 11                                |

| 3FFFFEh | DEVID1   | DEV2  | DEV1  | DEV0  | REV4  | REV3   | REV2   | REV1   | REV0   | 0000 0000                         |

| 3FFFFFh | DEVID2   | DEV10 | DEV9  | DEV8  | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | 0000 0000                         |

#### TABLE 19-1: CONFIGURATION BITS AND DEVICE IDs

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, maintain '1'. Shaded cells are unimplemented, read as '0'.

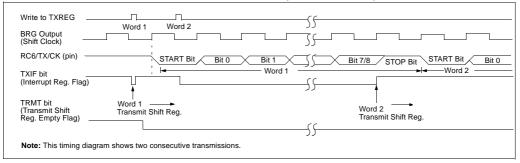

- 3: TOST = 1024TOSC (drawing not to scale). This delay will not occur for RC and EC osc modes.

- 4: CLKOUT is not available in these oscillator modes, but shown here for timing reference.

# 20.0 INSTRUCTION SET SUMMARY

The PIC18C601/801 instruction set adds many enhancements to the previous  $PIC^{\otimes}$  MCU instruction sets, while maintaining an easy migration path from them.

With few exceptions, instructions are a single program memory word (16-bits). Each single word instruction is divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

The PIC18C601/801 instruction set summary in Table 20-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 20-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- The file register (represented by 'f')

The destination of the result

- (represented by 'd')

- 3. The accessed memory (represented by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction.

The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- The file register (represented by 'f')

The bit in the file register

- (represented by 'b')

- The accessed memory (represented by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located.

The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (represented by 'k')

- The desired FSR register to load the literal value into (represented by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (represented by 'n')

- The mode of the Call or Return instructions (represented by 's')

- The mode of the Table Read and Table Write instructions (represented by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double word instructions. These four instructions were made double word instructions so that all the required information is available in these 32 bits. In the second word, the 4 MSbs are 1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. The double word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two word branch instructions (if true) would take 3  $\mu$ s.

Figure 20-1 shows the general formats that the instructions can have. All examples use the format `nnh' to represent a hexadecimal number, where `h' signifies a hexadecimal digit.

The Instruction Set Summary, shown in Table 20-2, lists the instructions recognized by the Microchip assembler (MPASM<sup>TM</sup>).

Section 20.1 provides a description of each instruction.

| BNC                                | Branch in                                                    | Not Carry                                       |                                                                                    | BN         | N                                                       | Branch if                                                          | Not Negativ                                               | ve                                                                                                |

|------------------------------------|--------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------|------------|---------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Syntax:                            | [ <i>label</i> ] E                                           | 3NC n                                           |                                                                                    | Syn        | tax:                                                    | [label] B                                                          | NN n                                                      |                                                                                                   |

| Operands:                          | -128 ≤ n :                                                   | ≤ 127                                           |                                                                                    | Оре        | rands:                                                  | -128 ≤ n ≤                                                         | 127                                                       |                                                                                                   |

| Operation:                         | if carry bi<br>(PC) + 2                                      | t is '0'<br>+ 2n → PC                           |                                                                                    | Оре        | eration:                                                | if negative<br>(PC) + 2 +                                          |                                                           |                                                                                                   |

| Status Affecte                     | d: None                                                      |                                                 |                                                                                    | Stat       | us Affected:                                            | None                                                               |                                                           |                                                                                                   |

| Encoding:                          | 1110                                                         | 0011 nn                                         | nn nnnn                                                                            | Enc        | oding:                                                  | 1110                                                               | 0111 nn                                                   | nn nnnn                                                                                           |

| Description:                       | program<br>The 2's c<br>added to<br>have incr<br>instruction | the PC. Since<br>emented to fe<br>n, the new ad | umber '2n' is<br>the PC will<br>etch the next<br>ldress will be<br>ttion is then a | Des        | cription:                                               | program w<br>The 2's co<br>added to t<br>have incre<br>instruction | mplement n<br>he PC. Sinc<br>mented to fe<br>, the new ac | ', then the<br>umber '2n' is<br>the PC will<br>etch the next<br>ldress will be<br>ttion is then a |

|                                    | two-cycle                                                    | instruction.                                    |                                                                                    |            |                                                         | two-cycle                                                          | instruction.                                              |                                                                                                   |

| Words:                             | 1                                                            |                                                 |                                                                                    | Wor        | ds:                                                     | 1                                                                  |                                                           |                                                                                                   |

| Cycles:                            | 1(2)                                                         |                                                 |                                                                                    | Сус        | les:                                                    | 1(2)                                                               |                                                           |                                                                                                   |

| Q Cycle Activ<br>If Jump:          | ity:                                                         |                                                 |                                                                                    |            | ycle Activity:<br>imp:                                  |                                                                    |                                                           |                                                                                                   |

| Q1                                 | Q2                                                           | Q3                                              | Q4                                                                                 |            | Q1                                                      | Q2                                                                 | Q3                                                        | Q4                                                                                                |

| Decode                             | Read literal<br>'n'                                          | Process<br>Data                                 | Write to PC                                                                        |            | Decode                                                  | Read literal<br>'n'                                                | Process<br>Data                                           | Write to PC                                                                                       |

| No                                 | No                                                           | No                                              | No                                                                                 |            | No                                                      | No                                                                 | No                                                        | No                                                                                                |

| operation<br>If No Jump:           | n operation                                                  | operation                                       | operation                                                                          | lf N       | operation                                               | operation                                                          | operation                                                 | operation                                                                                         |

| Q1                                 | Q2                                                           | Q3                                              | Q4                                                                                 |            | Q1                                                      | Q2                                                                 | Q3                                                        | Q4                                                                                                |

| Decode                             | Read literal<br>'n'                                          | Process<br>Data                                 | No<br>operation                                                                    |            | Decode                                                  | Read literal<br>'n'                                                | Process<br>Data                                           | No<br>operation                                                                                   |

| Example:                           | HERE                                                         | BNC Jump                                        |                                                                                    | <u>Exa</u> | mple:                                                   | HERE                                                               | BNN Jump                                                  | )                                                                                                 |

| Before Ir                          |                                                              |                                                 |                                                                                    |            | Before Instr                                            |                                                                    |                                                           |                                                                                                   |

| PC<br>After Inst<br>If Ca<br>If Ca | ruction<br>ry = 0;<br>PC = ac<br>ry = 1;                     | ddress (Jump)                                   |                                                                                    |            | PC<br>After Instruc<br>If Negat<br>PC<br>If Negat<br>PC | tion<br>ive = 0;<br>= ad<br>ive = 1;                               | dress (HERE)<br>dress (Jump)<br>dress (HERE+              |                                                                                                   |

| тэт        | FSZ             | Test f, ski                                                                        | ip if 0                                                                             |                                                                           |

|------------|-----------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Synt       | ax:             | [label] T                                                                          | "STFSZ f[,a                                                                         | 1]                                                                        |

| Ope        | rands:          | $0 \le f \le 255$                                                                  | 5                                                                                   |                                                                           |

|            |                 | a ∈ [0,1]                                                                          |                                                                                     |                                                                           |

| Ope        | ration:         | skip if f = 0                                                                      | C                                                                                   |                                                                           |

| State      | us Affected:    | None                                                                               |                                                                                     |                                                                           |

| Enco       | oding:          | 0110                                                                               | 011a ff                                                                             | ff ffff                                                                   |

| Des        | cription:       | during the<br>cution, is o<br>executed,<br>instruction<br>Bank will b<br>BSR value | current instr<br>discarded an<br>making this<br>a. If 'a' is 0, t<br>be selected, c | d a NOP is<br>a two-cycle<br>he Access<br>overriding the<br>the Bank will |

| Wor        | ds:             | 1                                                                                  |                                                                                     |                                                                           |

| Cycl       | es:             |                                                                                    | ycles if skip<br>a 2-word ins                                                       | and followed<br>truction                                                  |

| QC         | vcle Activity:  |                                                                                    |                                                                                     |                                                                           |

|            | Q1              | Q2                                                                                 | Q3                                                                                  | Q4                                                                        |

|            | Decode          | Read                                                                               | Process                                                                             | No                                                                        |

| lf sk      | in:             | register 'f'                                                                       | Data                                                                                | operation                                                                 |

| 11 54      | ip.<br>Q1       | Q2                                                                                 | Q3                                                                                  | Q4                                                                        |

|            | No              | No                                                                                 | No                                                                                  | No                                                                        |

|            | operation       | operation                                                                          | operation                                                                           | operation                                                                 |

| lf sk      | ip and followe  |                                                                                    |                                                                                     |                                                                           |

|            | Q1              | Q2                                                                                 | Q3                                                                                  | Q4                                                                        |

|            | No<br>operation | No<br>operation                                                                    | No<br>operation                                                                     | No<br>operation                                                           |

|            | No              | No                                                                                 | No                                                                                  | No                                                                        |

|            | operation       | operation                                                                          | operation                                                                           | operation                                                                 |

| <u>Exa</u> | <u>mple</u> :   | NZERO                                                                              | ISTFSZ CNI<br>:<br>:                                                                | ſ                                                                         |

|            | Before Instru   | iction                                                                             |                                                                                     |                                                                           |

|            | PC              | = Ad                                                                               | dress (HERE)                                                                        |                                                                           |

|            | After Instruct  | ion<br>= 00                                                                        | h,                                                                                  |                                                                           |

|            | PC              |                                                                                    | dress (ZERO)                                                                        |                                                                           |

|            | If CNT<br>PC    | ≠ 00<br>= Ad                                                                       | h,<br> dress (NZERC                                                                 | ))                                                                        |

|            | FU              | - Au                                                                               | UICOO (NZERO                                                                        | ,                                                                         |

| [ <i>label</i> ]<br>0 ≤ k ≤ 2<br>(WREG)<br>N,Z | 55                                                          |                                                                                                   | ∃G                                                  |

|------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| (WREG)<br>N,Z                                  |                                                             | $\rightarrow$ WRI                                                                                 | ΞG                                                  |

| N,Z                                            | .XOR. k                                                     | $\rightarrow$ WRI                                                                                 | EG                                                  |

|                                                |                                                             |                                                                                                   |                                                     |

| 0000                                           |                                                             |                                                                                                   |                                                     |

| 0000                                           | 1010                                                        | kkkk                                                                                              | kkkk                                                |

| XOR'ed                                         | with the 8                                                  | -bit liter                                                                                        | al 'k'. The                                         |

| 1                                              |                                                             |                                                                                                   |                                                     |

| 1                                              |                                                             |                                                                                                   |                                                     |

|                                                |                                                             |                                                                                                   |                                                     |

| 2                                              | Q3                                                          | Q                                                                                                 | 4                                                   |

| Read<br>literal 'k'                            |                                                             |                                                                                                   | Write to<br>WREG                                    |

|                                                | XOR'ed'<br>result is<br>1<br>1<br>22<br>Read<br>literal 'k' | XOR'ed with the 8<br>result is placed in<br>1<br>1<br>22<br>Q3<br>Read Proces<br>literal 'k' Data | 1<br>12 Q3 Q4<br>Read Process 1<br>literal 'k' Data |

| Before Instruction    |           |          |

|-----------------------|-----------|----------|

| WREG                  | =         | 0B5h     |

| Ν                     | =         | ?        |

| Z                     | =         | ?        |

| After Instruction     |           |          |

| After Instruc         | tion      |          |

| After Instruc<br>WREG | tion<br>= | 1Ah      |

|                       |           | 1Ah<br>0 |

| WREG                  | =         |          |

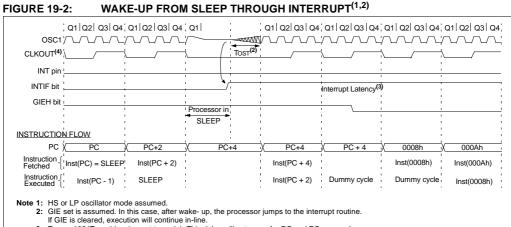

#### FIGURE 22-9: **PROGRAM MEMORY WRITE TIMING DIAGRAM**

Operating Conditions: 2.0V <Vcc <5.5V, -40°C <TA <125°C unless otherwise stated.

| TABLE 22-8: | PROGRAM MEMORY WRITE TIMING REQUIREMENTS |

|-------------|------------------------------------------|

| IADLE 22-0: | PROGRAM MEMORI WRITE HIMING REQUIREMENTS |

| Param<br>No. | Symbol   | Characteristics                                                    | Min        | Тур     | Max | Units |

|--------------|----------|--------------------------------------------------------------------|------------|---------|-----|-------|

| 150          | TadV2alL | Address out valid to ALE $\downarrow$ (address setup time)         | 0.25TCY-10 | _       |     | ns    |

| 151          | TalL2adl | ALE $\downarrow$ to address out invalid (address hold time)        | 5          | _       | _   | ns    |

| 153          | TwrH2adl | WRn 1 to data out invalid (data hold time)                         | 5          |         |     | ns    |

| 154          | TwrL     | WRn pulse width                                                    | 0.5Tcy-5   | 0.5Tcy  | _   | ns    |

| 156          | TadV2wrH | Data valid before WRN 1 (data setup time)                          | 0.5Tcy-10  | _       | _   | ns    |

| 157          | TbsV2wrL | Byte select valid before WRn $\downarrow$ (byte select setup time) | 0.25Tcy    | _       | _   | ns    |

| 157A         | TwrH2bsl | WRn $\uparrow$ to byte select invalid (byte select hold time)      | 0.125Tcy-5 | _       | _   | ns    |

| 166          | TalH2alH | ALE↑ to ALE↑ (cycle time)                                          | —          | 0.25Tcy | _   | ns    |

| 36           | TIVRST   | Time for Internal Reference Voltage to become stable               | —          | 20      | 50  | μs    |

# 23.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

Graphs and Tables are not available at this time.

### 24.0 PACKAGING INFORMATION

### 24.1 Package Marking Information

68-Lead PLCC

#### Example

80-Lead TQFP

Example

| Legenc | I: XXX<br>YY<br>WW<br>NNN | Customer specific information*<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code                  |

|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carried                | nt the full Microchip part number cannot be marked on one line, it will<br>over to the next line thus limiting the number of available characters<br>er specific information. |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

### APPENDIX E: DEVELOPMENT TOOL VERSION REQUIREMENTS

This lists the minimum requirements (software/ firmware) of the specified development tool to support the devices listed in this data sheet.

| MPLAB <sup>®</sup> IDE: | TBD |

|-------------------------|-----|

|-------------------------|-----|

MPLAB® SIMULATOR: TBD

#### MPLAB® ICE 3000:

| PIC18C601/801 Proc<br>Part Number -                                                      | essor Module:<br>TBD                                          |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| PIC18C601/801 Devi<br>Socket<br>64-pin TQFP<br>68-pin PLCC<br>80-pin TQFP<br>84-pin PLCC | ce Adapter:<br>Part Number<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD |

| MPLAB <sup>®</sup> ICD:                                                                  | TBD                                                           |

| PRO MATE <sup>®</sup> II:                                                                | TBD                                                           |

| PICSTART <sup>®</sup> Plus:                                                              | TBD                                                           |

| MPASM <sup>™</sup> Assembler:                                                            | TBD                                                           |

| MPLAB <sup>®</sup> C18 C Compiler:                                                       | TBD                                                           |

|                                                                                          |                                                               |

| Note: | Please read all associated README.TXT       |

|-------|---------------------------------------------|

|       | files that are supplied with the develop-   |

|       | ment tools. These "read me" files will dis- |

|       | cuss product support and any known          |

|       | limitations.                                |