Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                |                                                                          |

| RAM Size                   | 1.5К х 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 80-TQFP                                                                  |

| Supplier Device Package    | 80-TQFP (12x12)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18c801-i-pt |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |      | Pin N | umber |       |                                         |                                         |                                                                                                                      |

|----------|------|-------|-------|-------|-----------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name | PIC1 | BC601 | PIC1  | 8C801 | Pin<br>Type                             | Buffer<br>Type                          |                                                                                                                      |

|          | TQFP | PLCC  | TQFP  | PLCC  | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Description                                                                                                          |

|          |      |       |       |       |                                         |                                         | PORTB is a bi-directional I/O port. PORTE<br>can be software programmed for internal<br>weak pull-ups on all inputs. |

| RB0/INT0 | 48   | 60    | 58    | 72    |                                         |                                         |                                                                                                                      |

| RB0      |      |       |       |       | I/O                                     | TTL                                     | Digital I/O.                                                                                                         |

| INT0     |      |       |       |       | I                                       | ST                                      | External interrupt 0.                                                                                                |

| RB1/INT1 | 47   | 59    | 57    | 71    |                                         |                                         |                                                                                                                      |

| RB1      |      |       |       |       | I/O                                     | TTL                                     | Digital I/O.                                                                                                         |

| INT1     |      |       |       |       | I                                       | ST                                      | External interrupt 1.                                                                                                |

| RB2/INT2 | 46   | 58    | 56    | 70    |                                         |                                         |                                                                                                                      |

| RB2      |      |       |       |       | I/O                                     | TTL                                     | Digital I/O.                                                                                                         |

| INT2     |      |       |       |       | I                                       | ST                                      | External interrupt 2.                                                                                                |

| RB3/CCP2 | 45   | 57    | 55    | 69    |                                         |                                         |                                                                                                                      |

| RB3      |      |       |       |       | I/O                                     | TTL                                     | Digital I/O.                                                                                                         |

| CCP2     |      |       |       |       | I/O                                     | ST                                      | Capture2 input, Compare2 output,<br>PWM2 output.                                                                     |

| RB4      | 44   | 56    | 54    | 68    | I/O                                     | TTL                                     | Digital I/O, Interrupt-on-change pin.                                                                                |

| RB5      | 43   | 55    | 53    | 67    | I/O                                     | TTL                                     | Digital I/O, Interrupt-on-change pin.                                                                                |

| RB6      | 42   | 54    | 52    | 66    | I/O                                     | TTL                                     | Digital I/O, Interrupt-on-change pin.                                                                                |

|          |      |       |       |       | I                                       | ST                                      | ICSP programming clock.                                                                                              |

| RB7      | 37   | 48    | 47    | 60    | I/O                                     | TTL                                     | Digital I/O, Interrupt-on-change pin.                                                                                |

|          |      |       |       |       | I/O                                     | ST                                      | ICSP programming data.                                                                                               |

## TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

I = Input

P = Power

CMOS = CMOS compatible input or output Analog = Analog input

O = Output

OD = Open Drain (no P diode to VDD)

|           |           |         | Pin N     | umber |       |                                         |                                         |                                                                                                              |

|-----------|-----------|---------|-----------|-------|-------|-----------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Pin Na    | ame       | PIC18   | BC601     | PIC18 | BC801 | Pin<br>Type                             | Buffer<br>Type                          |                                                                                                              |

|           |           | TQFP    | PLCC      | TQFP  | PLCC  | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Description                                                                                                  |

|           |           |         |           |       |       |                                         |                                         | PORTD is a bi-directional I/O port. These<br>pins have TTL input buffers when external<br>memory is enabled. |

| RD0/AD0   |           | 58      | 3         | 72    | 3     |                                         |                                         |                                                                                                              |

| RD0       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD0       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 0.                                                                              |

| RD1/AD1   |           | 55      | 67        | 69    | 83    |                                         |                                         |                                                                                                              |

| RD1       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD1       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 1.                                                                              |

| RD2/AD2   |           | 54      | 66        | 68    | 82    |                                         |                                         |                                                                                                              |

| RD2       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD2       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 2.                                                                              |

| RD3/AD3   |           | 53      | 65        | 67    | 81    |                                         |                                         |                                                                                                              |

| RD3       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD3       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 3.                                                                              |

| RD4/AD4   |           | 52      | 64        | 66    | 80    |                                         |                                         |                                                                                                              |

| RD4       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD4       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 4.                                                                              |

| RD5/AD5   |           | 51      | 63        | 65    | 79    |                                         |                                         |                                                                                                              |

| RD5       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD5       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 5.                                                                              |

| RD6/AD6   |           | 50      | 62        | 64    | 78    |                                         |                                         |                                                                                                              |

| RD6       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD6       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 6.                                                                              |

| RD7/AD7   |           | 49      | 61        | 63    | 77    |                                         |                                         |                                                                                                              |

| RD7       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD7       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 7.                                                                              |

| Legend: 1 | TTL = TTL | compati | ble input |       |       | CI                                      | MOS = CM                                | OS compatible input or output                                                                                |

#### **TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)**

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

OD = Open Drain (no P diode to VDD)

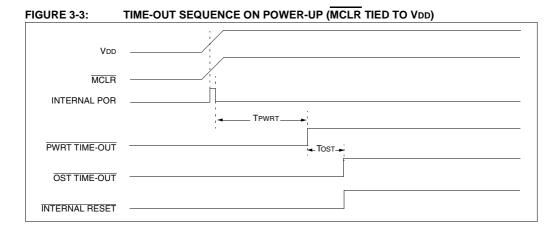

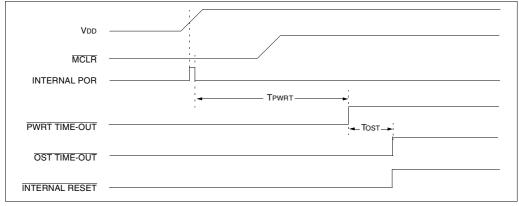

## FIGURE 3-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

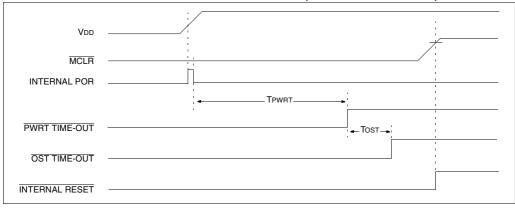

## FIGURE 3-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

| TADLE 3-3.                    |     | Inalization conditions for all registers |                |                                                                            |                                 |  |  |  |  |  |  |

|-------------------------------|-----|------------------------------------------|----------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|

| Register Applicabl<br>Devices |     |                                          | Power-on Reset | MCLR Reset<br>WDT Reset<br>Reset Instruction<br>Stack Over/Underflow Reset | Wake-up via WDT or<br>Interrupt |  |  |  |  |  |  |

| TOSU                          | 601 | 801                                      | 0 0000         | 0 0000                                                                     | u uuuu <b>(3)</b>               |  |  |  |  |  |  |

| TOSH                          | 601 | 801                                      | 0000 0000      | 0000 0000                                                                  | uuuu uuuu <b>(3)</b>            |  |  |  |  |  |  |

| TOSL                          | 601 | 801                                      | 0000 0000      | 0000 0000                                                                  | uuuu uuuu <b>(3)</b>            |  |  |  |  |  |  |

| STKPTR                        | 601 | 801                                      | 00-0 0000      | 00-0 0000                                                                  | uu-u uuuu <b>(3)</b>            |  |  |  |  |  |  |

| PCLATU                        | 601 | 801                                      | 0 0000         | 0 0000                                                                     | u uuuu                          |  |  |  |  |  |  |

| PCLATH                        | 601 | 801                                      | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| PCL                           | 601 | 801                                      | 0000 0000      | 0000 0000                                                                  | PC + 2 <sup>(2)</sup>           |  |  |  |  |  |  |

| TBLPTRU                       | 601 | 801                                      | 00 0000        | 00 0000                                                                    | uu uuuu                         |  |  |  |  |  |  |

| TBLPTRH                       | 601 | 801                                      | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| TBLPTRL                       | 601 | 801                                      | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| TABLAT                        | 601 | 801                                      | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| PRODH                         | 601 | 801                                      | xxxx xxxx      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| PRODL                         | 601 | 801                                      | xxxx xxxx      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| INTCON                        | 601 | 801                                      | 0000 000x      | 0000 000u                                                                  | սսսս սսսս <b>(1)</b>            |  |  |  |  |  |  |

| INTCON2                       | 601 | 801                                      | 1111 -1-1      | 1111 -1-1                                                                  | uuuu -u-u <b>(1)</b>            |  |  |  |  |  |  |

| INTCON3                       | 601 | 801                                      | 11-0 0-00      | 11-0 0-00                                                                  | uu-u u-uu <b>(1)</b>            |  |  |  |  |  |  |

| INDF0                         | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| POSTINC0                      | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| POSTDEC0                      | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| PREINC0                       | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| PLUSW0                        | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| FSR0H                         | 601 | 801                                      | 0000           | 0000                                                                       | uuuu                            |  |  |  |  |  |  |

| FSR0L                         | 601 | 801                                      | xxxx xxxx      | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| WREG                          | 601 | 801                                      | xxxx xxxx      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |  |

| INDF1                         | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| POSTINC1                      | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| POSTDEC1                      | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| PREINC1                       | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| PLUSW1                        | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

| FSR1H                         | 601 | 801                                      | 0000           | 0000                                                                       | uuuu                            |  |  |  |  |  |  |

| FSR1L                         | 601 | 801                                      | XXXX XXXX      | սսսս սսսս                                                                  | սսսս սսսս                       |  |  |  |  |  |  |

| BSR                           | 601 | 801                                      | 0000           | 0000                                                                       | uuuu                            |  |  |  |  |  |  |

| INDF2                         | 601 | 801                                      | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |  |  |  |  |

## TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0',  $\, q$  = value depends on condition, r = reserved, maintain '0'

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (00008h or 00018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH, and TOSL are updated with the current value of the PC. The SKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- **5:** This is not a physical register. It is an indirect pointer that addresses another register. The contents returned is the value contained in the addressed register.

| Fi             | File Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bi |                                      |                 |                          |             |            | Bit 0         | Value on<br>POR           | Value or<br>all other |           |          |

|----------------|--------------------------------------------------------|--------------------------------------|-----------------|--------------------------|-------------|------------|---------------|---------------------------|-----------------------|-----------|----------|

|                | 1                                                      |                                      |                 |                          |             |            |               |                           |                       |           | RESETS(  |

| FD7h           | TMR0H                                                  |                                      | ster High Byte  |                          |             |            |               |                           |                       | 0000 0000 | 0000 000 |

| FD6h           | TMR0L                                                  | -                                    | ster Low Byte   | 1                        | 1           | i          | i             | i                         | 1                     | XXXX XXXX | uuuu uuu |

| FD5h           | T0CON                                                  | TMR0ON                               | 16BIT           | TOCS                     | TOSE        | T0PS3      | T0PS2         | T0PS1                     | T0PS0                 | 1111 1111 | 1111 111 |

| FD4h           | Reserved                                               |                                      |                 |                          |             | 1          |               |                           | r                     | rrrr rrrr | rrrr rri |

| FD3h           | OSCCON <sup>(2)</sup>                                  | -                                    | —               | —                        | -           | LOCK       | PLLEN         | SCS1                      | SCS0                  | 0000      | uuu      |

| FD2h           | LVDCON <sup>(2)</sup>                                  | -                                    | —               | IRVST                    | LVDEN       | LVV3       | LVV2          | LVV1                      | LVV0                  | 00 0101   | 00 010   |

| FD1h           | WDTCON <sup>(2)</sup>                                  | —                                    | —               | —                        | -           | WDPS2      | WDPS1         | WDPS0                     | SWDTEN                | 0000      | xx>      |

| FD0h           | RCON                                                   | IPEN                                 | r               | —                        | RI          | TO         | PD            | POR                       | r                     | 00-1 11qq | 00-q qqu |

| FCFh           | TMR1H                                                  | Timer1 Regi                          | ster High Byte  | )                        |             |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FCEh           | TMR1L                                                  | Timer1 Regi                          | ster Low Byte   |                          | •           |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FCDh           | T1CON                                                  | RD16                                 | _               | T1CKPS1                  | T1CKPS0     | T1OSCEN    | T1SYNC        | TMR1CS                    | TMR1ON                | 0-00 0000 | u-uu uuu |

| FCCh           | TMR2                                                   | Timer2 Regi                          | ster            |                          |             |            |               |                           |                       | 0000 0000 | 0000 000 |

| FCBh           | PR2                                                    | Timer2 Peric                         | od Register     |                          |             |            |               |                           |                       | 1111 1111 | 1111 111 |

| FCAh           | T2CON                                                  | _                                    | TOUTPS3         | TOUTPS2                  | TOUTPS1     | TOUTPS0    | TMR2ON        | T2CKPS1                   | T2CKPS0               | -000 0000 | -000 000 |

| FC9h           | SSPBUF                                                 | SSP Receive Buffer/Transmit Register |                 |                          |             |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FC8h           | SSPADD                                                 | SSP Addres                           | s Register in I | <sup>2</sup> C Slave Mod | e. SSP Baud | Rate Reloa | d Register in | I <sup>2</sup> C Master M | lode                  | 0000 0000 | 0000 000 |

| FC7h           | SSPSTAT                                                | SMP                                  | CKE             | D/A                      | Р           | S          | R/W           | UA                        | BF                    | 0000 0000 | 0000 000 |

| FC6h           | SSPCON1                                                | WCOL                                 | SSPOV           | SSPEN                    | СКР         | SSPM3      | SSPM2         | SSPM1                     | SSPM0                 | 0000 0000 | 0000 000 |

| FC5h           | SSPCON2                                                | GCEN                                 | ACKSTAT         | ACKDT                    | ACKEN       | RCEN       | PEN           | RSEN                      | SEN                   | 0000 0000 | 0000 000 |

| FC4h           | ADRESH                                                 | A/D Result F                         | Register High   | Byte                     |             |            |               |                           | 1                     | XXXX XXXX | uuuu uuu |

| FC3h           | ADRESL                                                 | A/D Result F                         | Register Low E  | Byte                     |             |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FC2h           | ADCON0                                                 | _                                    | _               | CHS3                     | CHS2        | CHS1       | CHS0          | GO/DONE                   | ADON                  | 00 0000   | 00 000   |

| FC1h           | ADCON1                                                 | _                                    | _               | VCFG1                    | VCFG0       | PCFG3      | PCFG2         | PCFG1                     | PCFG0                 | 00 0000   | 00 000   |

| FC0h           | ADCON2                                                 | ADFM                                 | _               | _                        | _           | _          | ADCS2         | ADCS1                     | ADCS0                 | 0000      | 000      |

| FBFh           | CCPR1H                                                 | Capture/Con                          | npare/PWM R     | tegister1 High           | Byte        |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FBEh           | CCPR1L                                                 | Capture/Con                          | npare/PWM R     | legister1 Low            | Byte        |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FBDh           | CCP1CON                                                | _                                    | _               | DC1B1                    | DC1B0       | CCP1M3     | CCP1M2        | CCP1M1                    | CCP1M0                | 00 0000   | 00 000   |

| FBCh           | CCPR2H                                                 | Capture/Con                          | npare/PWM R     | tegister2 High           | Byte        |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FBBh           | CCPR2L                                                 |                                      |                 | egister2 Low             |             |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FBAh           | CCP2CON                                                | _                                    | _               | DC2B1                    | DC2B0       | CCP2M3     | CCP2M2        | CCP2M1                    | CCP2M0                | 00 0000   | uu uuu   |

| FB9h           | Reserved                                               |                                      |                 |                          |             |            |               |                           |                       | rrrr rrrr | rrrr rri |

| FB8h           | Reserved                                               |                                      |                 |                          |             |            |               |                           |                       | rrrr rrrr | rrrr rri |

| FB7h           | Reserved                                               |                                      |                 |                          |             |            |               |                           |                       | rrrr rrrr | rrrr rri |

| FB6h           |                                                        |                                      |                 |                          |             |            |               |                           |                       |           |          |

| FB5h           |                                                        |                                      |                 |                          |             |            |               |                           |                       |           |          |

| FB4h           |                                                        |                                      |                 |                          |             |            |               |                           |                       |           |          |

| FB3h           | TMR3H                                                  | Timer3 Regi                          | ster High Byte  | <b>,</b>                 |             |            |               |                           |                       | xxxx xxxx | uuuu uuu |

| FB2h           | TMR3L                                                  |                                      | ster Low Byte   |                          |             |            |               |                           |                       |           | uuuu uuu |

|                |                                                        | -                                    |                 |                          | TACKDOO     | T20004     | TODALO        | TMP200                    | TMDOON                | xxxx xxxx |          |

| FB1h<br>Legend | T3CON                                                  | RD16                                 | T3CCP2          | T3CKPS1<br>mplemented, o | T3CKPS0     | T3CCP1     | T3SYNC        | TMR3CS                    | TMR3ON                | 0000 0000 | uuuu uuu |

|  | TABLE 4-2: | <b>REGISTER FILE SUMMARY - PIC18C601/801</b> | (CONTINUED) |

|--|------------|----------------------------------------------|-------------|

|--|------------|----------------------------------------------|-------------|

Note 1: Other (non-power-up) RESETS include external RESET through MCLR and Watchdog Timer Reset.

2: These registers can only be modified when the Combination Lock is open.

3: These registers are available on PIC18C801 only.

## 6.3.1 8-BIT EXTERNAL TABLE WRITES

When the external bus is 8-bit, the byte-wide Table Write exactly corresponds to the bus length and there are no special considerations required.

The  $\overline{WRL}$  signal is used as the active write signal.

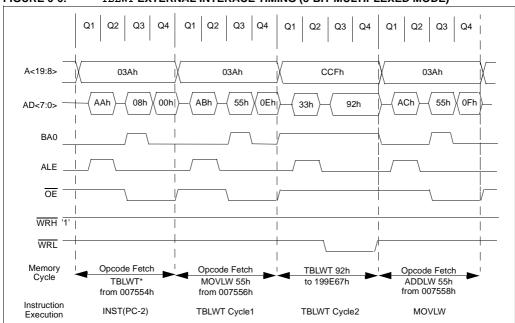

Figure 6-6 and Figure 6-7 show the timings associated with the 8-bit modes.

## FIGURE 6-6: TBLWT EXTERNAL INTERACE TIMING (8-BIT MULTIPLEXED MODE)

## 6.3.4 16-BIT EXTERNAL TABLE WRITE (BYTE SELECT MODE)

This mode allows Table Writes to word-wide external memories that have byte selection capabilities. This generally includes word-wide FLASH devices and word-wide static RAM devices.

During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The WRH line is strobed for each write cycle and the  $\overline{\text{WRL}}$  line is unused. The BA0 or  $\overline{\text{UB}}$  or  $\overline{\text{UL}}$  lines are used to select the byte to be written, based on the LSb of the TBLPTR.

JEDEC standard flash memories will require a I/O port line to become a BYTE/WORD input signal and will use the BA0 signal as a byte address. JEDEC standard static RAM memories will use the UB or UL signals to select the byte.

Figure 6-10 shows the timing associated with this mode.

Q1 Q2 Q3 Q4 Q2 Q3 Q4 Q1 A<19:16> 0h 0h Ch 0h 0h Ch 000Dh AAB 6FF4h 000Ch 9292h AD<15:0> 5656h AAC 3440 0E55h CF33 CE33 BA0 ALE OE WRH WRL '1' UB LB **Opcode Fetch** Memory Opcode Fetch TBLWT 56h Opcode Fetch Opcode Fetch TBLWT 92h Cycle TBLWT\*+ MOVWE TABLAT to 199E66h TBI WT\* MOVLW 55h to 199E67h from 00755Ah from 007554h from 007556h from 007558h Instruction INST(PC-2) TBLWT\*+ Cycle1 | TBLWT\*+ Cycle2 | MOVWF TBLWT\* Cycle1 | TBLWT\* Cycle2 Execution

## REGISTER 8-5: PIR1 REGISTER

| FIKT KEG                     | ISTER                                                                        |               |                |              |            |              |        |  |  |  |

|------------------------------|------------------------------------------------------------------------------|---------------|----------------|--------------|------------|--------------|--------|--|--|--|

| U-0                          | R/W-0                                                                        | R-0           | R-0            | R/W-0        | R/W-0      | R/W-0        | R/W-0  |  |  |  |

| —                            | ADIF                                                                         | RCIF          | TXIF           | SSPIF        | CCP1IF     | TMR2IF       | TMR1IF |  |  |  |

| bit 7                        |                                                                              |               |                |              |            |              | bit 0  |  |  |  |

| Unimplem                     | ented: Read                                                                  | as '0'        |                |              |            |              |        |  |  |  |

| ADIF: A/D                    | Converter Inte                                                               | errupt Flag b | pit            |              |            |              |        |  |  |  |

|                              | conversion c                                                                 | •             |                |              |            |              |        |  |  |  |

| 0 = The A/                   | D conversion                                                                 | is not comp   | lete           |              |            |              |        |  |  |  |

| RCIF: USA                    | RT Receive I                                                                 | nterrupt Flag | g bit          |              |            |              |        |  |  |  |

|                              | 1 = The USART receive buffer, RCREG, is full<br>(cleared when RCREG is read) |               |                |              |            |              |        |  |  |  |

| 0 = The US                   | SART receive                                                                 | buffer is em  | pty            |              |            |              |        |  |  |  |

| TXIF: USA                    | RT Transmit I                                                                | nterrupt Flag | g bit          |              |            |              |        |  |  |  |

|                              | SART transmit<br>d when TXRE                                                 |               |                | /            |            |              |        |  |  |  |

| 0 = The US                   | SART transmit                                                                | buffer is ful | 1              |              |            |              |        |  |  |  |

| SSPIF: Ma                    | ster Synchror                                                                | ous Serial F  | Port Interrupt | Flag bit     |            |              |        |  |  |  |

|                              | nsmission/rec<br>be cleared in s                                             | •             | mplete         |              |            |              |        |  |  |  |

| 0 = Waiting                  | g to transmit/re                                                             | eceive        |                |              |            |              |        |  |  |  |

| CCP1IF: C                    | CP1 Interrupt                                                                | Flag bit      |                |              |            |              |        |  |  |  |

| Capture me                   | ode:                                                                         |               |                |              |            |              |        |  |  |  |

|                              | 1 register cap<br>be cleared in s                                            |               | ed             |              |            |              |        |  |  |  |

| 0 = No TM                    | R1 register ca                                                               | pture occur   | red            |              |            |              |        |  |  |  |

| Compare n                    | node:                                                                        |               |                |              |            |              |        |  |  |  |

|                              | 1 register con<br>be cleared in s                                            |               | occurred       |              |            |              |        |  |  |  |

| 0 = No TM                    | R1 register co                                                               | mpare mato    | ch occurred    |              |            |              |        |  |  |  |

| <u>PWM mode</u><br>Unused in | -                                                                            |               |                |              |            |              |        |  |  |  |

| TMR2IF: ⊺                    | MR2 to PR2 I                                                                 | Match Interro | upt Flag bit   |              |            |              |        |  |  |  |

| (must b                      | to PR2 match<br>be cleared in s                                              | software)     |                |              |            |              |        |  |  |  |

| 0 = No TM                    | R2 to PR2 ma                                                                 | atch occurre  | d              |              |            |              |        |  |  |  |

| TMR1IF: ⊺                    | MR1 Overflov                                                                 | v Interrupt F | lag bit        |              |            |              |        |  |  |  |

|                              | register overfl                                                              |               |                |              |            |              |        |  |  |  |

|                              | be cleared in s                                                              | ,             |                |              |            |              |        |  |  |  |

| 0 = IMR1                     | register did no                                                              | ot overflow   |                |              |            |              |        |  |  |  |

| Legend:                      |                                                                              |               |                |              |            |              |        |  |  |  |

| R = Reada                    | ble bit                                                                      | W = Wr        | itable bit     | U = Unimp    | lemented b | oit, read as | 0'     |  |  |  |

| - n = Value                  | at POR                                                                       | '1' = Bit     | is set         | '0' = Bit is | cleared    | x = Bit is u | nknown |  |  |  |

## REGISTER 8-8: PIE2 REGISTER

- n = Value at POR

|         | U-0                                                                                                            | U-0                                                                                                                         | U-0           | U-0        | R/W-0     | R/W-0      | R/W-0          | R/W-0  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------|------------|-----------|------------|----------------|--------|--|--|--|--|

|         | —                                                                                                              | _                                                                                                                           | —             | —          | BCLIE     | LVDIE      | TMR3IE         | CCP2IE |  |  |  |  |

|         | bit 7                                                                                                          |                                                                                                                             |               |            |           |            |                | bit 0  |  |  |  |  |

| bit 7-4 | Unimplem                                                                                                       | ented: Read                                                                                                                 | as '0'        |            |           |            |                |        |  |  |  |  |

| bit 3   | 1 = Enable                                                                                                     | BCLIE: Bus Collision Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled<br>I VDIE: Low Voltage Detect Interrupt Enable bit |               |            |           |            |                |        |  |  |  |  |

| bit 2   | LVDIE: Low Voltage Detect Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled                                  |                                                                                                                             |               |            |           |            |                |        |  |  |  |  |

| bit 1   | 1 = Enables                                                                                                    | MR3 Overflo<br>s the TMR3 o<br>s the TMR3                                                                                   | overflow inte | rrupt      |           |            |                |        |  |  |  |  |

| bit 0   | <b>CCP2IE</b> : CCP2 Interrupt Enable bit<br>1 = Enables the CCP2 interrupt<br>0 = Disables the CCP2 interrupt |                                                                                                                             |               |            |           |            |                |        |  |  |  |  |

|         | Legend:                                                                                                        |                                                                                                                             |               |            |           |            |                |        |  |  |  |  |

|         | R = Readat                                                                                                     | ole bit                                                                                                                     | W = Wr        | itable bit | U = Unimp | lemented b | oit, read as ' | 0'     |  |  |  |  |

'0' = Bit is cleared

x = Bit is unknown

'1' = Bit is set

## TABLE 9-17: PORTJ FUNCTIONS

| Name                  | Bit# | Buffer Type | Function                                                          |

|-----------------------|------|-------------|-------------------------------------------------------------------|

| RJ0/D0 <sup>(1)</sup> | bit0 | ST/TTL      | Input/output port pin or Data bit 0 for external memory interface |

| RJ1/D1 <sup>(1)</sup> | bit1 | ST/TTL      | Input/output port pin or Data bit 1 for external memory interface |

| RJ2/D2 <sup>(1)</sup> | bit2 | ST/TTL      | Input/output port pin or Data bit 2 for external memory interface |

| RJ3/D3 <sup>(1)</sup> | bit3 | ST/TTL      | Input/output port pin or Data bit 3 for external memory interface |

| RJ4/D4 <sup>(1)</sup> | bit4 | ST/TTL      | Input/output port pin or Data bit 4 for external memory interface |

| RJ5/D5 <sup>(1)</sup> | bit5 | ST/TTL      | Input/output port pin or Data bit 5 for external memory interface |

| RJ6/D6 <sup>(1)</sup> | bit6 | ST/TTL      | Input/output port pin or Data bit 6 for external memory interface |

| RJ7/D7 <sup>(1)</sup> | bit7 | ST/TTL      | Input/output port pin or Data bit 7 for external memory interface |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: PORTJ is available only on PIC18C801 devices.

## TABLE 9-18: SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ

| Name   | Bit 7                                        | Bit 6     | Bit 5    | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|----------------------------------------------|-----------|----------|-------|-----------|-----------|-------|-------|--------------------------|---------------------------------|

| TRISJ  | CJ PORTJ Data Direction Control Register     |           |          |       |           |           |       |       |                          | 1111 1111                       |

| PORTJ  | Read PC                                      | ORTJ pin/ | Write PO |       | xxxx xxxx | uuuu uuuu |       |       |                          |                                 |

| LATJ   | Read PORTJ Data Latch/Write PORTJ Data Latch |           |          |       |           |           |       |       | xxxx xxxx                | uuuu uuuu                       |

| MEMCON | EBDIS                                        | PGRM      | WAIT1    | WAIT0 | _         | —         | WM1   | WM0   | 000000                   | 000000                          |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTJ.

## 14.0 CAPTURE/COMPARE/PWM (CCP) MODULES

REGISTER 14-1:

Each CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a 16-bit capture register, as a 16-bit compare register, or as a PWM Duty Cycle register. Table 14-1 shows the timer resources of the CCP module modes.

CCP1CON REGISTER

CCP2CON REGISTER

The operation of CCP1 is identical to that of CCP2, with the exception of the special event trigger. Therefore, operation of a CCP module in the following sections is described, with respect to CCP1.

Table 14-2 shows the interaction of the CCP modules.

Register 14-1 shows the CCPx Control registers (CCPxCON). For the CCP1 module, the register is called CCP1CON and for the CCP2 module, the register is called CCP2CON.

#### R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 CCP1CON \_\_\_\_ DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 bit 7 bit 0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 CCP2CON DC2B1 DC2B0 CCP2M3 CCP2M2 CCP2M1 CCP2M0 bit 7 bit 0 bit 7-6 Unimplemented: Read as '0' bit 5-4 DCxB1:DCxB0: PWM Duty Cycle bit1 and bit0 Capture mode: Unused Compare mode: Unused PWM mode: These bits are the two LSbs (bit1 and bit0) of the 10-bit PWM duty cycle. The upper eight bits (DCx9:DCx2) of the duty cycle are found in CCPRxL. bit 3-0 CCPxM3:CCPxM0: CCPx Mode Select bits 0000 = Capture/Compare/PWM off (resets CCPx module) 0001 = Reserved 0010 = Compare mode, toggle output on match (CCPxIF bit is set) 0011 = Reserved 0100 = Capture mode, every falling edge 0101 = Capture mode, every rising edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, Initialize CCP pin Low, on compare match force CCP pin High (CCPIF bit is set) 1001 = Compare mode, Initialize CCP pin High, on compare match force CCP pin Low (CCPIF bit is set) 1010 = Compare mode, Generate software interrupt on compare match (CCPIF bit is set, CCP pin is unaffected) 1011 = Compare mode, Trigger special event (CCPIF bit is set, reset TMR1 or TMR3) 11xx = PWM mode Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 15.4.8 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full bit, BF, and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one baud rate generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF bit is cleared and the master releases SDA, allowing the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurs, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 15-15).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL, until all seven address bits and the R/W bit, are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2 register). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF bit is cleared and the baud rate generator is turned off, until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

## 15.4.8.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT register) is set when the CPU writes to SSPBUF, and is cleared when all eight bits are shifted out.

## 15.4.8.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

15.4.8.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2 register) is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ), and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

## 15.4.9 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2 register).

# Note: The MSSP module must be in an IDLE state before the RCEN bit is set, or the RCEN bit will be disregarded.

The baud rate generator begins counting and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the RCEN bit is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF bit is set, the SSPIF flag bit is set and the baud rate generator is suspended from counting, holding SCL low. The MSSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge Sequence Enable bit ACKEN (SSPCON2 register).

## 15.4.9.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

## 15.4.9.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when eight bits are received into the SSPSR and the BF bit is already set from a previous reception.

## 15.4.9.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

## 18.1 Control Register

The Low Voltage Detect Control register (Register 18-1) controls the operation of the Low Voltage Detect circuitry.

## REGISTER 18-1: LVDCON REGISTER

|         | U-0                                                                                 | U-0          | R-0                        | R/W-0          | R/W-0         | R/W-1        | R/W-0          | R/W-1        |  |  |  |

|---------|-------------------------------------------------------------------------------------|--------------|----------------------------|----------------|---------------|--------------|----------------|--------------|--|--|--|

|         | _                                                                                   | _            | IRVST                      | LVDEN          | LVDL3         | LVDL2        | LVDL1          | LVDL0        |  |  |  |

|         | bit 7                                                                               |              |                            |                |               |              |                | bit 0        |  |  |  |

|         |                                                                                     |              |                            |                |               |              |                |              |  |  |  |

| bit 7-6 | Unimplem                                                                            | ented: Read  | d as '0'                   |                |               |              |                |              |  |  |  |

| bit 5   | IRVST: Inte                                                                         | rnal Refere  | nce Voltage                | Stable Flag I  | oit           |              |                |              |  |  |  |

|         | 1 = Indicate<br>voltage                                                             |              | ow Voltage                 | Detect logic   | will generate | the interrup | ot flag at the | e specified  |  |  |  |

|         |                                                                                     |              | •                          | Detect logic   | •             |              |                | t the        |  |  |  |

| bit 4   | LVDEN: Low Voltage Detect Power Enable bit                                          |              |                            |                |               |              |                |              |  |  |  |

|         | 1 = Enables LVD, powers up LVD circuit<br>0 = Disables LVD, powers down LVD circuit |              |                            |                |               |              |                |              |  |  |  |

| bit 3-0 | LVDL3:LVDL0: Low Voltage Detection Limit bits                                       |              |                            |                |               |              |                |              |  |  |  |

|         | 1111 = Ext                                                                          | ernal analog | g input is use             | ed (input con  | nes from the  | LVDIN pin)   |                |              |  |  |  |

|         | 1110 = 4.5                                                                          | -            |                            |                |               |              |                |              |  |  |  |

|         | 1101 = 4.2                                                                          | -            |                            |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180<br>d on PIC180 |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                |                |               |              |                |              |  |  |  |

|         | 0111 = 3.0                                                                          | V - Reserve  | d on PIC180                | 2601/801       |               |              |                |              |  |  |  |

|         | 0110 = 2.8                                                                          | V - Reserve  | d on PIC180                | C601/801       |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                |                |               |              |                |              |  |  |  |

|         |                                                                                     |              | d on PIC180                | 01 and PIC1    | 81 C 801/601  |              |                |              |  |  |  |

|         |                                                                                     |              |                            |                |               |              | a voltogo o    | f the device |  |  |  |

|         | are not test                                                                        |              | men result i               | n a trip point |               | and operatin | y voltage o    |              |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 19.2 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run, even if the clock on the OSC1/CLKI and OSC2/CLKO pins of the device has been stopped; for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the RCON register will be cleared upon a WDT time-out.

By default, the Watchdog Timer is disabled by configuration to allow software control over Watchdog Timer operation. If the WDT is enabled by configuration, software execution may not disable this function. When the Watchdog Timer is disabled by configuration, the SWDTEN bit in the WDTCON register enables/ disables the operation of the WDT. The WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT postscaler may be assigned by using configuration bits WDPS<3:1> in CONFIG2H register. If the Watchdog Timer is disabled by configuration, values for the WDT postscaler may be assigned using the SWDPS bits in the WDTCON register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

## 19.2.1 CONTROL REGISTER

Register 19-5 shows the WDTCON register. This is a readable and writable register. It contains control bits to control the Watchdog Timer from user software. If the Watchdog Timer is enabled by configuration, this register setting is ignored.

## REGISTER 19-5: WDTCON REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|--------|--------|--------|--------|

| —     |     |     | —   | SWDPS2 | SWDPS1 | SWDPS0 | SWDTEN |

| bit 7 |     |     |     |        |        |        | bit 0  |

### bit 7-4 Unimplemented: Read as '0'

bit 3-1 SWDPS0: Software Watchdog Timer Postscale Select bits

| 111 = 1.128                                            |

|--------------------------------------------------------|

| 110 = 1:64                                             |

| 101 = 1:32                                             |

| 100 = 1:16                                             |

| 011 = 1:8                                              |

| 010 = 1:4                                              |

| 001 = 1:2                                              |

| 000 = 1:1                                              |

| SWDTEN: Software Controlled Watchdog Timer Enable bit  |

| 1 = Watchdog Timer is on                               |

| 0 = Watchdog Timer is turned off if it is not disabled |

|                                                        |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 0

| Mnemonic,<br>Operands |       | Description                    | Qualas | 16-Bit Instruction Word |      |      | Vord | Status    | Natas |

|-----------------------|-------|--------------------------------|--------|-------------------------|------|------|------|-----------|-------|

|                       |       | Description                    | Cycles | MSb                     |      |      | LSb  | Affected  | Notes |

| CONTROL               | OPERA | TIONS                          |        |                         |      |      |      |           |       |

| BC                    | n     | Branch if Carry                | 1 (2)  | 1110                    | 0010 | nnnn | nnnn | None      |       |

| BN                    | n     | Branch if Negative             | 1 (2)  | 1110                    | 0110 | nnnn | nnnn | None      |       |

| BNC                   | n     | Branch if Not Carry            | 1 (2)  | 1110                    | 0011 | nnnn | nnnn | None      |       |

| BNN                   | n     | Branch if Not Negative         | 1 (2)  | 1110                    | 0111 | nnnn | nnnn | None      |       |

| BNOV                  | n     | Branch if Not Overflow         | 1 (2)  | 1110                    | 0101 | nnnn | nnnn | None      |       |

| BNZ                   | n     | Branch if Not Zero             | 2      | 1110                    | 0001 | nnnn | nnnn | None      |       |

| BOV                   | n     | Branch if Overflow             | 1 (2)  | 1110                    | 0100 | nnnn | nnnn | None      |       |

| BRA                   | n     | Branch Unconditionally         | 1 (2)  | 1101                    | 0nnn | nnnn | nnnn | None      |       |

| BZ                    | n     | Branch if Zero                 | 1 (2)  | 1110                    | 0000 | nnnn | nnnn | None      |       |

| CALL                  | n, s  | Call subroutine1st word        | 2      | 1110                    | 110s | kkkk | kkkk | None      |       |

|                       |       | 2nd word                       |        | 1111                    | kkkk | kkkk | kkkk |           |       |

| CLRWDT                | _     | Clear Watchdog Timer           | 1      | 0000                    | 0000 | 0000 | 0100 | TO, PD    |       |

| DAW                   | _     | Decimal Adjust WREG            | 1      | 0000                    | 0000 | 0000 | 0111 | С         |       |

| GOTO                  | n     | Go to address1st word          | 2      | 1110                    | 1111 | kkkk | kkkk | None      |       |

|                       |       | 2nd word                       |        | 1111                    | kkkk | kkkk | kkkk |           |       |

| NOP                   | _     | No Operation                   | 1      | 0000                    | 0000 | 0000 | 0000 | None      |       |

| NOP                   | _     | No Operation (Note 4)          | 1      | 1111                    | xxxx | xxxx | xxxx | None      |       |

| POP                   | _     | Pop top of return stack (TOS)  | 1      | 0000                    | 0000 | 0000 | 0110 | None      |       |

| PUSH                  | _     | Push top of return stack (TOS) | 1      | 0000                    | 0000 | 0000 | 0101 | None      |       |

| RCALL                 | n     | Relative Call                  | 2      | 1101                    | 1nnn | nnnn | nnnn | None      |       |

| RESET                 |       | Software device RESET          | 1      | 0000                    | 0000 | 1111 | 1111 | All       |       |

| RETFIE                | S     | Return from interrupt enable   | 2      | 0000                    | 0000 | 0001 | 000s | GIE/GIEH, |       |

|                       |       |                                |        |                         |      |      |      | PEIE/GIEL |       |

| RETLW                 | k     | Return with literal in WREG    | 2      | 0000                    | 1100 | kkkk | kkkk | None      |       |

| RETURN                | s     | Return from Subroutine         | 2      | 0000                    | 0000 | 0001 | 001s | None      |       |

| SLEEP                 | _     | Go into Standby mode           | 1      | 0000                    | 0000 | 0000 | 0011 | TO, PD    |       |

| TABLE 20-2: | PIC18C601/801 | INSTRUCTION SET | (CONTINUED) |

|-------------|---------------|-----------------|-------------|

|             |               |                 |             |

Note 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTE, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

6: Microchip's MPASM<sup>™</sup> Assembler automatically defaults destination bit 'd' to '1', while access bit 'a' defaults to '1' or '0', according to address of register being used.

|                                                                                                                                                                                                                 | 6                                                           | Bit Toggle                                                    | ə f                   |              |                        |  |  |