Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 26                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

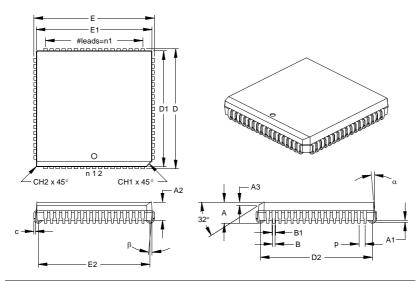

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 68-LCC (J-Lead)                                                          |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc601-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

|                   |           | Pin N     | umber     |           |      |                |                                        |

|-------------------|-----------|-----------|-----------|-----------|------|----------------|----------------------------------------|

| Pin Name          | PIC1      | PIC18C601 |           | PIC18C801 |      | Buffer<br>Type |                                        |

|                   | TQFP PLCC |           | TQFP PLCC |           | Туре | 1960           | Description                            |

|                   |           |           |           |           |      |                | PORTA is a bi-directional I/O port.    |

| RA0/AN0           | 24        | 34        | 30        | 42        |      |                |                                        |

| RA0               |           |           |           |           | I/O  | TTL            | Digital I/O.                           |

| AN0               |           |           |           |           | 1    | Analog         | Analog input 0.                        |

| RA1/AN1           | 23        | 33        | 29        | 41        |      | 0              |                                        |

| RA1               |           |           |           |           | I/O  | TTL            | Digital I/O.                           |

| AN1               |           |           |           |           | 1    | Analog         | Analog input 1.                        |

| RA2/AN2/VREF-     | 22        | 32        | 28        | 40        |      |                |                                        |

| RA2               |           | 02        | 20        | 10        | I/O  | TTL            | Digital I/O.                           |

| AN2               |           |           |           |           | ., C | Analog         | Analog input 2.                        |

| VREF-             |           |           |           |           | i    | Analog         | A/D reference voltage (Low) input.     |

| RA3/AN3/VREF+     | 21        | 31        | 27        | 39        |      | J              | ····································   |

| RA3               | 21        | 01        | 21        | 00        | I/O  | TTL            | Digital I/O.                           |

| AN3               |           |           |           |           | .″Ŭ  | Analog         | Analog input 3.                        |

| VREF+             |           |           |           |           | i    | Analog         | A/D reference voltage (High) input.    |

| RA4/T0CKI         | 28        | 39        | 34        | 47        |      | J              | ······································ |

| RA4               | 20        | 03        | 04        | 77        | I/O  | ST/OD          | Digital I/O – Open drain when          |

|                   |           |           |           |           | "    | 01/00          | configured as output.                  |

| TOCKI             |           |           |           |           | 1    | ST             | Timer0 external clock input.           |

| RA5/AN4/SS/LVDIN  | 27        | 38        | 33        | 46        |      |                |                                        |

| RA5               |           | 00        | 00        | -0        | I/O  | TTL            | Digital I/O.                           |

| AN4               |           |           |           |           |      | Analog         | Analog input 4.                        |

| SS                |           |           |           |           |      | ST             | SPI slave select input.                |

| LVDIN             |           |           |           |           | i    | Analog         | Low voltage detect input.              |

| Legend: TTL = TTL | compati   | hle innut | 1         | I         | CI   | v              | OS compatible input or output          |

| TABLE 1-2: PINOUT I/O | DESCRIPTIONS | (CONTINUED) |

|-----------------------|--------------|-------------|

|-----------------------|--------------|-------------|

ST = Schmitt Trigger input with CMOS levels

- = Input L

- P = Power

Analog = Analog input

0 = Output

= Open Drain (no P diode to VDD) OD

|           |           |         | Pin N     | umber |       |                                         |                                         |                                                                                                              |

|-----------|-----------|---------|-----------|-------|-------|-----------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Pin Na    | ame       | PIC18   | BC601     | PIC18 | BC801 | Pin<br>Type                             | Buffer<br>Type                          |                                                                                                              |

|           |           | TQFP    | PLCC      | TQFP  | PLCC  | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Description                                                                                                  |

|           |           |         |           |       |       |                                         |                                         | PORTD is a bi-directional I/O port. These<br>pins have TTL input buffers when external<br>memory is enabled. |

| RD0/AD0   |           | 58      | 3         | 72    | 3     |                                         |                                         |                                                                                                              |

| RD0       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD0       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 0.                                                                              |

| RD1/AD1   |           | 55      | 67        | 69    | 83    |                                         |                                         |                                                                                                              |

| RD1       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD1       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 1.                                                                              |

| RD2/AD2   |           | 54      | 66        | 68    | 82    |                                         |                                         |                                                                                                              |

| RD2       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD2       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 2.                                                                              |

| RD3/AD3   |           | 53      | 65        | 67    | 81    |                                         |                                         |                                                                                                              |

| RD3       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD3       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 3.                                                                              |

| RD4/AD4   |           | 52      | 64        | 66    | 80    |                                         |                                         |                                                                                                              |

| RD4       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD4       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 4.                                                                              |

| RD5/AD5   |           | 51      | 63        | 65    | 79    |                                         |                                         |                                                                                                              |

| RD5       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD5       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 5.                                                                              |

| RD6/AD6   |           | 50      | 62        | 64    | 78    |                                         |                                         |                                                                                                              |

| RD6       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD6       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 6.                                                                              |

| RD7/AD7   |           | 49      | 61        | 63    | 77    |                                         |                                         |                                                                                                              |

| RD7       |           |         |           |       |       | I/O                                     | ST                                      | Digital I/O.                                                                                                 |

| AD7       |           |         |           |       |       | I/O                                     | TTL                                     | External memory address/data 7.                                                                              |

| Legend: 1 | TTL = TTL | compati | ble input |       |       | CI                                      | MOS = CM                                | OS compatible input or output                                                                                |

#### **TABLE 1-2: PINOUT I/O DESCRIPTIONS (CONTINUED)**

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

OD = Open Drain (no P diode to VDD)

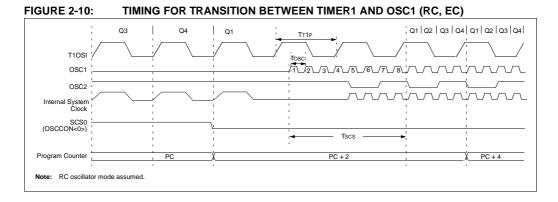

### 2.6.3 SCS0, SCS1 PRIORITY

If both SCS0 and SCS1 are set to '1' simultaneously, the SCS0 bit has priority over the SCS1 bit. This means that the low power option will take precedence over the PLL option. If both bits are cleared simultaneously, the system clock will come from OSC1, after a ToST time-out. If only the SCS0 bit is cleared, the system clock will come from the PLL output, following ToST and TPLL time.

TABLE 2-3: SCS0, SCS1 PRIORITY

| SCS1 | SCS0 | Clock Source        |

|------|------|---------------------|

| 0    | 0    | Ext Oscillator OSC1 |

| 0    | 1    | Timer1 Oscillator   |

| 1    | 0    | HS + PLL            |

| 1    | 1    | Timer1 Oscillator   |

# 2.7 Effects of SLEEP Mode on the On-Chip Oscillator

When the device executes a SLEEP instruction, the on-chip clocks and oscillator are turned off and the device is held at the beginning of an instruction cycle (Q1 state). With the oscillator off, the OSC1 and OSC2 signals will stop oscillating. Since all the transistor switching currents have been removed, SLEEP mode achieves the lowest current consumption of the device (only leakage currents). Enabling any on-chip feature that will operate during SLEEP, will increase the current consumed during SLEEP. The user can wake from SLEEP through external RESET, Watchdog Timer Reset, or through an interrupt.

# 2.8 Power-up Delays

Power-up delays are controlled by two timers, so that no external RESET circuitry is required for most applications. The delays ensure that the device is kept in RESET until the device power supply and clock are stable. For additional information on RESET operation, see Section 3.0 RESET.

The first timer is the Power-up Timer (PWRT), which optionally provides a fixed delay of TPWRT (parameter #33) on power-up only. The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable.

PIC18C601/801 devices provide a configuration bit, PWRTEN in CONFIG2L register, to enable or disable the Power-up Timer. By default, the Power-up Timer is enabled.

With the PLL enabled (HS4 oscillator mode), the time-out sequence following a Power-on Reset is different from other oscillator modes. The time-out sequence is as follows: the PWRT time-out is invoked after a POR time delay has expired, then, the Oscillator Start-up Timer (OST) is invoked. However, this is still not a sufficient amount of time to allow the PLL to lock at high frequencies. The PWRT timer is used to provide an additional time-out, called TPLL (parameter #7), to allow the PLL ample time to lock to the incoming clock frequency.

# TABLE 2-4: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| OSC Mode  | OSC1 Pin                                               | OSC2 Pin                                               |

|-----------|--------------------------------------------------------|--------------------------------------------------------|

| RC        | Floating, external resistor should pull high           | At logic low                                           |

| EC        | Floating                                               | At logic low                                           |

| LP and HS | Feedback inverter disabled, at quiescent voltage level | Feedback inverter disabled, at guiescent voltage level |

Note: See Table 3-1 in Section 3.0 RESET, for time-outs due to SLEEP and MCLR Reset.

# 4.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 4-8 shows the data memory organization for PIC18C601/801 devices.

The data memory map is divided into banks that contain 256 bytes each. The lower four bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper 4 bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFR's are used for control and status of the controller and peripheral functions, while GPR's are used for data storage and scratch pad operations in the user's application. The SFR's start at the last location of Bank 15 (0FFFh) and grow downwards. GPR's start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

GPR banks 4 and 5 serve as a Program Memory called "Boot RAM", when PGRM bit in MEMCON is set. When PGRM bit is set, any read from "Boot RAM" returns '0's, while any write to it is ignored.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSR). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing, or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access bank. Section 4.10 provides a detailed description of the Access bank.

#### 4.9.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly. Indirect addressing operates through the File Select Registers (FSR). The operation of indirect addressing is shown in Section 4.12.

PIC18C601/801 devices have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other RESETS.

Data RAM is available for use as GPR registers by all instructions. Bank 15 (0F80h to 0FFFh) contains SFR's. All other banks of data memory contain GPR registers starting with bank 0.

#### 4.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 4-2.

The SFR's can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations are unimplemented and read as '0's. See Table 4-2 for addresses for the SFRs.

### 4.9.3 SECURED ACCESS REGISTERS

PIC18C601/801 devices contain software programming options for safety critical peripherals. Because these safety critical peripherals can be programmed in software, registers used to control these peripherals are given limited access by the user code. This way, errant code will not accidentally change settings in peripherals that could cause catastrophic results.

The registers that are considered safety critical are the Watchdog Timer register (WDTCON), the External Memory Control register (MEMCON), the Oscillator Control register (OSCCON) and the Chip Select registers (CSSEL2 and CSELIO).

Two bits called Combination Lock (CMLK) bits, located in the lower two bits of the PSPCON register, must be set in sequence by user code to gain access to Secured Access registers.

# 6.3 Table Write

Table Write operations store data from the data memory space into external program memory.

PIC18C601/801devices perform Table Writes one byte at a time. Table Writes to external memory are two-cycle instructions, unless wait states are enabled. The last cycle writes the data to the external memory location.

16-bit interface Table Writes depend on the type of external device that is connected and the WM<1:0> bits in the MEMCON register (See Figure 5-2).

Example 6-2 describes how to use TBLWT.

#### EXAMPLE 6-2: TABLE WRITE CODE EXAMPLE

| : Write | a byte to | location 0020h                  |

|---------|-----------|---------------------------------|

| CLRF    | TBLPTRU   | ; clear upper 5 bits of TBLPTR  |

| CLRF    | TBLPTRH   | ; clear higher 8 bits of TBLPTR |

| MOVLW   | 20h       | : Load 20h into                 |

| MOVWF   | TBLPTRL   | : TBLPTRL                       |

| MOVLW   | 55h       | ; Load 55h into                 |

| MOVWF   | TBLAT     | : TBLAT                         |

| TBLWT*  |           | : Write it                      |

|         |           |                                 |

# 7.0 8 X 8 HARDWARE MULTIPLIER

An 8 x 8 hardware multiplier is included in the ALU of PIC18C601/801 devices. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored into the 16-bit product register pair (PRODH:PRODL). The multiplier does not affect any flags in the STATUS register.

Making the  $8 \times 8$  multiplier execute in a single cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in some applications previously reserved for Digital Signal Processors.

Table 7-1 shows a performance comparison between enhanced devices using the single cycle hardware multiply, and performing the same function without the hardware multiply.

|                  |                           | Program           | Cycles | Time     |          |          |  |

|------------------|---------------------------|-------------------|--------|----------|----------|----------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 25 MHz | @ 10 MHz | @ 4 MHz  |  |

| Q v Q uncigned   | Without hardware multiply | 13                | 69     | 11.0 μs  | 27.6 μs  | 69.0 μs  |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 160.0 ns | 400.0 ns | 1.0 μs   |  |

| 9 x 9 olanod     | Without hardware multiply | 33                | 91     | 14.6 μs  | 36.4 μs  | 91.0 μs  |  |

| 8 x 8 signed     | Hardware multiply         | 6                 | 6      | 960.0 ns | 2.4 μs   | 6.0 μs   |  |

| 16 x 16 unsigned | Without hardware multiply | 21                | 242    | 38.7 μs  | 96.8 μs  | 242.0 μs |  |

| 16 x 16 unsigned | Hardware multiply         | 24                | 24     | 3.8 μs   | 9.6 μs   | 24.0 μs  |  |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 40.6 μs  | 102.6 μs | 254.0 μs |  |

| TO A TO SIGNED   | Hardware multiply         | 36                | 36     | 5.8 μs   | 14.4 μs  | 36.0 μs  |  |

# TABLE 7-1: PERFORMANCE COMPARISON

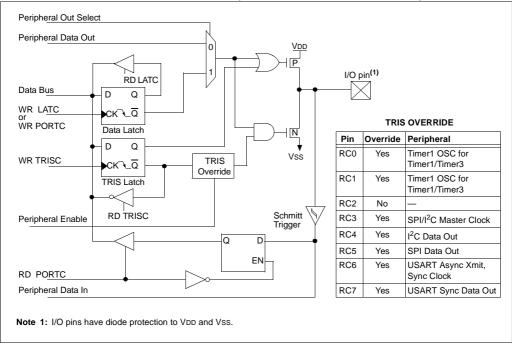

# 9.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATC register, read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 9-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

#### EXAMPLE 9-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0CFh  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC3:RC0 as inputs |

|       |       | ; RC5:RC4 as outputs    |

|       |       | ; RC7:RC6 as inputs     |

|       |       |                         |

# FIGURE 9-6: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

| Name                        | Bit# | Buffer Type           | Function                                     |

|-----------------------------|------|-----------------------|----------------------------------------------|

| RE0/AD8/A8 <sup>(2)</sup>   | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 8  |

| RE1/AD9/A9 <sup>(2)</sup>   | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 9  |

| RE2/AD10/A10 <sup>(2)</sup> | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 10 |

| RE3/AD11/A11 <sup>(2)</sup> | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 11 |

| RE4/AD12/A12 <sup>(2)</sup> | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 12 |

| RE5/AD13/A13 <sup>(2)</sup> | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 13 |

| RE6/AD14/A14 <sup>(2)</sup> | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 14 |

| RE7/AD15/A15 <sup>(2)</sup> | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or Address/Data bit 15 |

# TABLE 9-9: PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in System Bus mode.

2: REx is used as a multiplexed address/data bus for PIC18C601 and PIC18C801 in 16-bit mode, and as an

address only for PIC18C801 in 8-bit mode.

| TABLE 9-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Name   | Bit 7                                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|--------|----------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| TRISE  | PORTE Data Direction Control Register        |       |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| PORTE  | Read PORTE pin/Write PORTE Data Latch        |       |       |       |       |       |       |       | XXXX XXXX                | uuuu uuuu                       |

| LATE   | Read PORTE Data Latch/Write PORTE Data Latch |       |       |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                       |

| MEMCON | EBDIS                                        | PGRM  | WAIT1 | WAIT0 |       | —     | WM1   | WM0   | 000000                   | 000000                          |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTE.

| Name   | Bit 7                                                                           | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |

|--------|---------------------------------------------------------------------------------|---------------|---------|---------|---------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                                                                    | PEIE/<br>GIEL | TMR0IE  | INTOIE  | RBIE    | TMR0IF | INTOIF | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | —                                                                               | ADIF          | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF    | -000 0000            | -000 0000                       |

| PIE1   | —                                                                               | ADIE          | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE    | -000 0000            | -000 0000                       |

| IPR1   | —                                                                               | ADIP          | RCIP    | TXIP    | SSPIP   | CCP1IP | TMR2IP | TMR1IP    | -000 0000            | -000 0000                       |

| TMR1L  | R1L Holding register for the Least Significant Byte of the 16-bit TMR1 register |               |         |         |         |        |        | xxxx xxxx | uuuu uuuu            |                                 |

| TMR1H  | 1H Holding register for the Most Significant Byte of the 16-bit TMR1 register   |               |         |         |         |        |        |           | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | RD16                                                                            | —             | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N    | 0-00 0000            | u-uu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

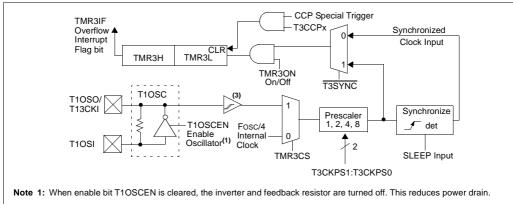

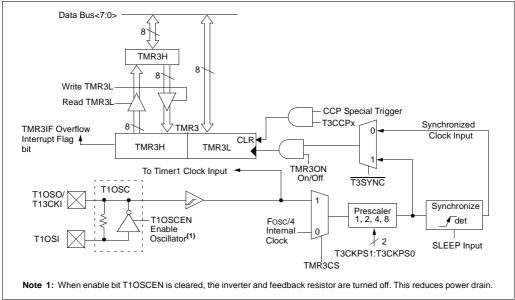

# 13.1 Timer3 Operation

Timer3 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON register).

When TMR3CS = 0, Timer3 increments every instruction cycle. When TMR3CS = 1, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer3 also has an internal "RESET input". This RESET can be generated by the CCP module (Section 13.0).

### FIGURE 13-1: TIMER3 BLOCK DIAGRAM

# FIGURE 13-2: TIMER3 BLOCK DIAGRAM CONFIGURED IN 16-BIT READ/WRITE MODE

# 15.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

# 15.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface<sup>™</sup> (SPI)

- Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The  $I^2C$  interface supports the following modes in hardware:

- · Master mode

- Multi-Master mode

- · Slave mode

# 15.2 Control Registers

The MSSP module has three associated registers. These include a status register and two control registers.

# REGISTER 15-1: SSPSTAT REGISTER

Register 15-1 shows the MSSP Status Register (SSPSTAT), Register 15-2 shows the MSSP Control Register 1 (SSPCON1), and Register 15-3 shows the MSSP Control Register 2 (SSPCON2).

|       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R-0                                                                       | R-0                                            | R-0                | R-0         | R-0            | R-0   |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|--------------------|-------------|----------------|-------|--|--|--|--|

|       | SMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D/A                                                                       | Р                                              | S                  | R/W         | UA             | BF    |  |  |  |  |

|       | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |                                                |                    |             |                | bit 0 |  |  |  |  |

| bit 7 | 0 = Input da <u>SPI Slave n</u> SMP must l <u>In I<sup>2</sup>C Mast</u> 1= Slew rat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>mode:</u><br>ata sampled at<br>ata sampled at                                                                                                                                                                                                                                                                                                                                                                                                                                                      | middle of dat<br>en SPI is used<br>ide:<br>iled for standa                | a output time<br>d in Slave mo<br>ard speed mo | ode<br>ode (100 kH | z and 1 MH: | z)             |       |  |  |  |  |

| bit 6 | CKE: SPI Clock Edge Select<br><u>CKP = 0:</u><br>1 = Data transmitted on rising edge of SCK<br>0 = Data transmitted on falling edge of SCK<br><u>CKP = 1:</u><br>1 = Data transmitted on falling edge of SCK<br>0 = Data transmitted on rising edge of SCK                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |                                                |                    |             |                |       |  |  |  |  |

| bit 5 | 1 = Indicate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D/A: Data/Address bit (I <sup>2</sup> C mode only)<br>1 = Indicates that the last byte received or transmitted was data<br>0 = Indicates that the last byte received or transmitted was address                                                                                                                                                                                                                                                                                                       |                                                                           |                                                |                    |             |                |       |  |  |  |  |

| bit 4 | <ul> <li>P: STOP bit</li> <li>(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)</li> <li>1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)</li> <li>0 = STOP bit was not detected last</li> </ul>                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |                                                |                    |             |                |       |  |  |  |  |

| bit 3 | 1 = Indicate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | oit<br>only. This bit is<br>es that a STAR<br>bit was not de                                                                                                                                                                                                                                                                                                                                                                                                                                          | T bit has beer                                                            |                                                |                    |             |                | ed.)  |  |  |  |  |

| bit 2 | <ul> <li>RW: Read/Write bit Information (I<sup>2</sup>C mode only)</li> <li>This bit holds the R/W bit information following the last add<u>ress</u> match. This bit is only valid from the address match to the next START bit, STOP bit, or not ACK bit.</li> <li>In I<sup>2</sup>C Slave mode:</li> <li>1 = Read</li> <li>0 = Write</li> <li>In I<sup>2</sup>C Master mode:</li> <li>1 = Transmit is in progress</li> <li>0 = Transmit is not in progress.</li> <li>OR-ing this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |                                                |                    |             |                |       |  |  |  |  |

| bit 1 | 1 = Indicate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e Address (10-l<br>es that the user<br>s does not nee                                                                                                                                                                                                                                                                                                                                                                                                                                                 | needs to upo                                                              | date the addr                                  | ess in the S       | SPADD reg   | ister          |       |  |  |  |  |

| bit 0 | $\frac{\text{Receive (SI}}{1 = \text{Receive}}$ $0 = \text{Receive}$ $\frac{\text{Transmit (I}^2}{1 = \text{Data tra}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>a Address does not need to be updated</li> <li>BF: Buffer Full Status bit<br/><u>Receive (SPI and I<sup>2</sup>C modes):</u> <ol> <li>Receive complete, SSPBUF is full</li> <li>Receive not complete, SSPBUF is empty</li> </ol> </li> <li>Transmit (I<sup>2</sup>C mode only): <ol> <li>Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full</li> <li>Data transmit complete (does not include the ACK and STOP bits), SSPBUF is empty</li> </ol> </li> </ul> |                                                                           |                                                |                    |             |                |       |  |  |  |  |

|       | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |                                                |                    |             |                |       |  |  |  |  |

|       | R = Readat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writa                                                                 | able bit                                       | U = Unimp          | lemented bi | t, read as '0' |       |  |  |  |  |

|       | - n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                                                |                    |             |                |       |  |  |  |  |

bit

bit

bit

bit

bit

bit

bit

bit

- n = Value at POR

#### REGISTER 15-3: SSPCON2 REGISTER

| R/W-0                                     | R/W-0                                                                                                                                                                                                                                                                  | R/W-0                         | R/W-0        | R/W-0        | R/W-0       | R/W-0        | R/W-0     |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|--------------|-------------|--------------|-----------|--|

| GCEN                                      | ACKSTAT                                                                                                                                                                                                                                                                | ACKDT                         | ACKEN        | RCEN         | PEN         | RSEN         | SEN       |  |

| bit 7                                     |                                                                                                                                                                                                                                                                        |                               |              |              |             |              | bit C     |  |

| 1 = Enable                                | eneral Call En<br>e interrupt whe<br>al call address                                                                                                                                                                                                                   | en a general                  |              |              | eceived in  | the SSPSR    | 1         |  |

| <u>In Master</u><br>1 = Ackno             | : Acknowledge<br>Transmit mode<br>wledge was ne<br>wledge was re                                                                                                                                                                                                       | <u>e:</u><br>ot received f    | rom slave    | er mode only | ()          |              |           |  |

| <u>In Master</u><br>Value tran            | cknowledge E<br><u>Receive mode</u><br>smitted when<br>cknowledge<br>wledge                                                                                                                                                                                            | <u>):</u>                     |              |              | quence at   | the end of a | a receive |  |

| <u>In Master</u><br>1 = Initiate<br>Autom | ACKEN: Acknowledge Sequence Enable bit (In I <sup>2</sup> C Master mode only)<br>In Master Receive mode:<br>1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit.<br>Automatically cleared by hardware.<br>0 = Acknowledge sequence idle |                               |              |              |             |              |           |  |

|                                           | eceive Enable<br>es Receive mo<br>/e idle                                                                                                                                                                                                                              |                               | laster mode  | only)        |             |              |           |  |

| SCK relea                                 | P Condition E<br>se control<br>STOP conditi<br>condition idle                                                                                                                                                                                                          |                               |              |              | ally cleare | d by hardwa  | are.      |  |

| 1 = Initiate<br>by har                    | peated STAR<br>Repeated ST<br>dware.<br>ated START co                                                                                                                                                                                                                  | ART conditi                   |              |              |             |              | d         |  |

| SEN: STA<br>1 = Initiate                  | RT Condition<br>START cond<br>Condition idle                                                                                                                                                                                                                           | Enabled bit (<br>ition on SDA |              |              |             | ed by hardv  | vare.     |  |

| Note:                                     | For bits ACKI<br>mode, this bit<br>writes to the S                                                                                                                                                                                                                     | may not be                    | set (no spoo |              |             |              |           |  |

| Legend:                                   |                                                                                                                                                                                                                                                                        |                               |              |              |             |              |           |  |

| R = Reada                                 | able bit                                                                                                                                                                                                                                                               | W = Wr                        | itable bit   | U = Unimp    | lemented l  | bit, read as | '0'       |  |

|                                           |                                                                                                                                                                                                                                                                        |                               |              |              |             |              |           |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

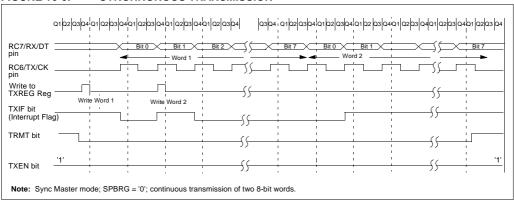

# FIGURE 16-6: SYNCHRONOUS TRANSMISSION

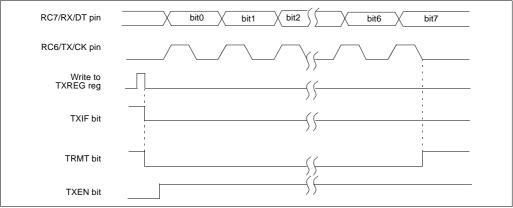

# FIGURE 16-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

The value in the ADRESH/ADRESL registers is not modified for a Power-on Reset. The ADRESH/ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 17.1. After this acquisition time has elapsed, the A/D conversion can be started. The following steps should be followed to do an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time.

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

- 5. Wait for A/D conversion to complete, by either:

- Polling for the GO/DONE bit to be cleared, OR

- Waiting for the A/D interrupt

- Read A/D Result registers (ADRESH:ADRESL); clear bit ADIF, if required.

- For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

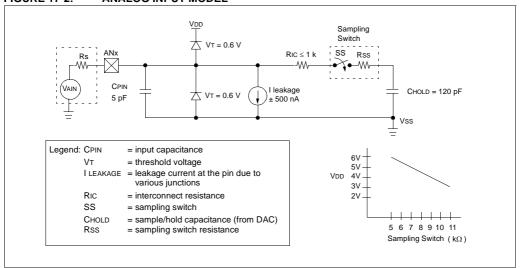

#### FIGURE 17-2: ANALOG INPUT MODEL

| BCF                      | Bit Clear                                                                         | f                                 |                        |                          |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------|-----------------------------------|------------------------|--------------------------|--|--|--|

| Syntax:                  | [label] E                                                                         | [ <i>label</i> ] BCF f, b [,a]    |                        |                          |  |  |  |

| Operands:                | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$ |                                   |                        |                          |  |  |  |

| Operation:               | $0 \rightarrow f < b >$                                                           |                                   |                        |                          |  |  |  |

| Status Affected:         | None                                                                              |                                   |                        |                          |  |  |  |

| Encoding:                | 1001                                                                              | bbba                              | ffff                   | ffff                     |  |  |  |

| Description:             | Bit 'b' in re<br>0, the Acc<br>overriding<br>the Bank<br>BSR valu                 | cess Ban<br>the BSI<br>will be se | k will be:<br>R value. | selected,<br>If 'a' = 1, |  |  |  |

| Words:                   | 1                                                                                 |                                   |                        |                          |  |  |  |

| Cycles:                  | 1                                                                                 | 1                                 |                        |                          |  |  |  |

| Q Cycle Activity:        |                                                                                   |                                   |                        |                          |  |  |  |

| Q1                       | Q2                                                                                | Q3                                | 3                      | Q4                       |  |  |  |

| Decode                   | Read<br>register 'f'                                                              | Proce<br>Data                     |                        | Write<br>gister 'f'      |  |  |  |

| Example:                 | BCF                                                                               | FLAG_RE                           | G, 7                   |                          |  |  |  |

| Before Instru<br>FLAG_R  | iction<br>EG = 0C7h                                                               |                                   |                        |                          |  |  |  |

| After Instruct<br>FLAG_R | tion<br>EG = 47h                                                                  |                                   |                        |                          |  |  |  |

|                          |                                                                                   |                                   |                        |                          |  |  |  |

| BN                                      | Branch if                                                            | Negati                                                                                                                                                                                                                                                         | ve   |                 |  |  |  |  |

|-----------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|--|--|--|--|

| Syntax:                                 | [ <i>label</i> ] B                                                   | [ <i>label</i> ] BN n                                                                                                                                                                                                                                          |      |                 |  |  |  |  |

| Operands:                               | -128 ≤ n ≤                                                           | 127                                                                                                                                                                                                                                                            |      |                 |  |  |  |  |

| Operation:                              | if negative<br>(PC) + 2 +                                            |                                                                                                                                                                                                                                                                |      |                 |  |  |  |  |

| Status Affected:                        | None                                                                 | None                                                                                                                                                                                                                                                           |      |                 |  |  |  |  |

| Encoding:                               | 1110                                                                 | 0110                                                                                                                                                                                                                                                           | nnnn | ı nnnn          |  |  |  |  |

| Description:                            | gram will t<br>The 2's co<br>added to t<br>have incre<br>instruction | If the Negative bit is '1', then the pro-<br>gram will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then a |      |                 |  |  |  |  |

| Words:                                  | 1                                                                    | IIISUUCU                                                                                                                                                                                                                                                       | 011. |                 |  |  |  |  |

| Cycles:                                 | 1(2)                                                                 | •                                                                                                                                                                                                                                                              |      |                 |  |  |  |  |

| Q Cycle Activity:<br>If Jump:           | 1(2)                                                                 |                                                                                                                                                                                                                                                                |      |                 |  |  |  |  |

| Q1                                      | Q2                                                                   | Q3                                                                                                                                                                                                                                                             | 3    | Q4              |  |  |  |  |

| Decode                                  | Read literal<br>'n'                                                  | Proce<br>Data                                                                                                                                                                                                                                                  |      | Write to PC     |  |  |  |  |

| No                                      | No                                                                   | No                                                                                                                                                                                                                                                             |      | No              |  |  |  |  |

| operation                               | operation                                                            | operat                                                                                                                                                                                                                                                         | ion  | operation       |  |  |  |  |

| If No Jump:                             |                                                                      |                                                                                                                                                                                                                                                                |      |                 |  |  |  |  |

| Q1                                      | Q2                                                                   | Q3                                                                                                                                                                                                                                                             |      | Q4              |  |  |  |  |

| Decode                                  | Read literal<br>'n'                                                  | Proce<br>Data                                                                                                                                                                                                                                                  |      | No<br>operation |  |  |  |  |

|                                         | HERE                                                                 | BN                                                                                                                                                                                                                                                             |      |                 |  |  |  |  |

| Example:                                | 11151(15                                                             | DIN                                                                                                                                                                                                                                                            | Jump |                 |  |  |  |  |

| Example:<br>Before Instru               |                                                                      | DIN                                                                                                                                                                                                                                                            | Jump |                 |  |  |  |  |

| <u>Example</u> :<br>Before Instru<br>PC | uction                                                               | dress (H                                                                                                                                                                                                                                                       | -    |                 |  |  |  |  |

=

0; =

address (HERE+2)

If Negative PC

| BRA                                                                                                      | ۱                                                                | Unconditi               | onal Branch             | า               | BSI                                      | F                           | Bit Set f                                                              |                 |                       |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------|-------------------------|-----------------|------------------------------------------|-----------------------------|------------------------------------------------------------------------|-----------------|-----------------------|

| Synt                                                                                                     | ax:                                                              | [ <i>label</i> ] B      | RA n                    |                 | Syn                                      | tax:                        | [label] B                                                              | SF f, b [,a]    |                       |