Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | EBI/EMI, I²C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | -                                                                          |

| Program Memory Type        | ROMIess                                                                    |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc601t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                   |         | Pin N     | umber |       |                                         |                |                                        |

|-------------------|---------|-----------|-------|-------|-----------------------------------------|----------------|----------------------------------------|

| Pin Name          | PIC1    | BC601     | PIC1  | 8C801 | Pin<br>Type                             | Buffer<br>Type |                                        |

|                   | TQFP    | PLCC      | TQFP  | PLCC  | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1960           | Description                            |

|                   |         |           |       |       |                                         |                | PORTA is a bi-directional I/O port.    |

| RA0/AN0           | 24      | 34        | 30    | 42    |                                         |                |                                        |

| RA0               |         |           |       |       | I/O                                     | TTL            | Digital I/O.                           |

| AN0               |         |           |       |       | 1                                       | Analog         | Analog input 0.                        |

| RA1/AN1           | 23      | 33        | 29    | 41    |                                         | 0              |                                        |

| RA1               |         |           |       |       | I/O                                     | TTL            | Digital I/O.                           |

| AN1               |         |           |       |       | 1                                       | Analog         | Analog input 1.                        |

| RA2/AN2/VREF-     | 22      | 32        | 28    | 40    |                                         |                |                                        |

| RA2               |         | 02        | 20    | 10    | I/O                                     | TTL            | Digital I/O.                           |

| AN2               |         |           |       |       | ., C                                    | Analog         | Analog input 2.                        |

| VREF-             |         |           |       |       | i                                       | Analog         | A/D reference voltage (Low) input.     |

| RA3/AN3/VREF+     | 21      | 31        | 27    | 39    |                                         | J              | ······g• (··/                          |

| RA3               | 21      | 01        | 21    | 00    | I/O                                     | TTL            | Digital I/O.                           |

| AN3               |         |           |       |       | .″Ŭ                                     | Analog         | Analog input 3.                        |

| VREF+             |         |           |       |       | i                                       | Analog         | A/D reference voltage (High) input.    |

| RA4/T0CKI         | 28      | 39        | 34    | 47    |                                         | J              | ······································ |

| RA4               | 20      | 03        | 04    | 77    | I/O                                     | ST/OD          | Digital I/O – Open drain when          |

|                   |         |           |       |       | "                                       | 01/00          | configured as output.                  |

| TOCKI             |         |           |       |       | 1                                       | ST             | Timer0 external clock input.           |

| RA5/AN4/SS/LVDIN  | 27      | 38        | 33    | 46    |                                         |                |                                        |

| RA5               |         | 00        | 00    | -0    | I/O                                     | TTL            | Digital I/O.                           |

| AN4               |         |           |       |       |                                         | Analog         | Analog input 4.                        |

| SS                |         |           |       |       |                                         | ST             | SPI slave select input.                |

| LVDIN             |         |           |       |       | i                                       | Analog         | Low voltage detect input.              |

| Legend: TTL = TTL | compati | hle innut | 1     | I     | CI                                      | v              | OS compatible input or output          |

| TABLE 1-2: PINOUT I/O | DESCRIPTIONS | (CONTINUED) |

|-----------------------|--------------|-------------|

|-----------------------|--------------|-------------|

ST = Schmitt Trigger input with CMOS levels

- = Input L

- P = Power

Analog = Analog input

0 = Output

= Open Drain (no P diode to VDD) OD

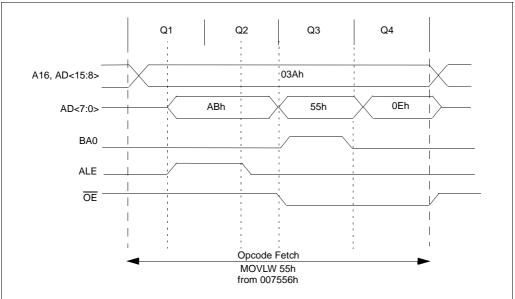

#### 5.2.2 8-BIT DE-MULTIPLEXED MODE

The 8-bit De-Multiplexed mode applies only to the PIC18C801. Data and address lines are available separately. External components are not necessary in this mode.

For 8-bit De-Multiplexed mode on the PIC18C801, the instructions are fetched as two 8-bit bytes on a dedicated data bus (PORTJ). The address will be presented for the entire duration of the fetch cycle on a separate address bus. The two instruction bytes are sequentially fetched within one instruction cycle (TcY). Therefore, the designer must choose external memory devices according to timing calculations, based on 1/2 TcY (2 times instruction rate). For proper memory speed selection, setup and hold times must be considered. The Address Latch Enable (ALE) pin is left unconnected, since glue logic is not necessary. The  $\overline{OE}$  output enable signal will enable one byte of program memory for a portion of the instruction cycle, then BA0 will change and the second byte will be enabled to form the 16-bit instruction word. The least significant bit of the address, BA0, must be connected to the memory devices in this mode. Figure 5-3 shows an example of 8-bit De-Multiplexed mode on the PIC18C801. The control signals used in 8-bit De-Multiplexed mode are outlined in Register 5-2. Register 5-4 describes 8-bit De-Multiplexed mode timing.

#### 6.3.3 EXTERNAL TABLE WRITE IN 16-BIT WORD WRITE MODE

This mode allows Table Writes to any type of word-wide external memories.

This method makes a distinction between TBLWT cycles to even or odd addresses.

During a TBLWT cycle to an even address, where TBLPTR<0> = 0, the TABLAT data is transferred to a holding latch and the external address data bus is tristated for the data portion of the bus cycle. No write signals are activated.

During a TBLWT cycle to an odd address, where TBLPTR<0> = 1, the TABLAT data is presented on the upper byte of the AD<15:0> bus. The contents of the holding latch are presented on the lower byte of the AD<15:0> bus. The WRH line is strobed for each write cycle and the WRL line is unused. The BAO line indicates the LSb of TBLPTR, but it is unnecessary. The UB and LB lines are active to select both bytes.

The obvious limitation to this method is that the TBLWT must be done in pairs on a specific word boundary to correctly write a word location.

Figure 6-9 shows the timing associated with this mode.

|                          | Q1 Q2 Q3 Q4             | Q1 Q2 Q3 Q4                  | Q1 Q2 Q3 Q4    | Q1 Q2 Q3 Q4            | Q1 Q2 Q3 Q4               | Q1 Q2 Q3 Q4     |

|--------------------------|-------------------------|------------------------------|----------------|------------------------|---------------------------|-----------------|

| A<19:16>                 | 0h                      | Oh                           | Ch             | Oh                     | Oh                        | Ch              |

| AD<15:0>                 | (3AAAh)-(000Dh          | AABh 6FF4h                   | CF33h          | (3AACh) 000Ch          | AADh OE55h                | CF33h)-(9256h)- |

| BA0                      |                         |                              |                |                        |                           | <br> N          |

| ALE                      | <br> _/\                |                              |                |                        |                           |                 |

| OE                       | <br>  \                 | /                            | 1              | <u> </u>               | \                         |                 |

| WRH                      |                         | <u> </u><br>                 |                |                        |                           |                 |

| WRL '1'                  | 1                       | 1                            |                |                        |                           |                 |

| UB                       |                         | <br>                         |                |                        |                           |                 |

| LB _                     |                         |                              | /              |                        |                           |                 |

| Memory                   | Opcode Fetch            | Opcode Fetch                 | TBLWT 56h      | Opcode Fetch           | Opcode Fetch              | TBLWT 92h       |

| Cycle                    | TBLWT*+<br>from 007554h | MOVWF TABLAT<br>from 007556h | to 199E66h     | TBLWT*<br>from 007558h | MOVLW 55h<br>from 00755Ah | to 199E67h      |

| Instruction<br>Execution | INST(PC-2)              | TBLWT*+ Cycle1               | TBLWT*+ Cycle2 | MOVWF                  | TBLWT* Cycle1             | TBLWT* Cycle2   |

|                          |                         | 1                            |                |                        |                           |                 |

## 8.1 Control Registers

This section contains the control and status registers.

### 8.1.1 INTCON REGISTERS

The INTCON Registers are readable and writable registers, which contain various enable, priority, and flag bits.

## REGISTER 8-1: INTCON REGISTER

| R/V   | /-0         | R/W-0                            | R/W-0           | R/W-0       | R/W-0        | R/W-0        | R/W-0          | R/W-:  |

|-------|-------------|----------------------------------|-----------------|-------------|--------------|--------------|----------------|--------|

| GIE/C | <b>H</b> EI | PEIE/GIEL                        | TMR0IE          | INT0IE      | RBIE         | TMR0IF       | INT0IF         | RBIF   |

| bit 7 |             |                                  |                 |             |              |              |                | b      |

| GIE/G | IEH:        | Global Interru                   | upt Enable b    | it          |              |              |                |        |

| When  |             |                                  |                 |             |              |              |                |        |

|       |             | s all unmaske<br>s all interrupt |                 |             |              |              |                |        |

| When  |             |                                  | 0               |             |              |              |                |        |

|       |             | s all high prio                  | rity interrupt  | S           |              |              |                |        |

| 0 = D | sable       | es all high prio                 | ority interrupt | s           |              |              |                |        |

|       |             | : Peripheral Ir                  | nterrupt Ena    | ble bit     |              |              |                |        |

| When  |             |                                  | d norinhara     | lintorrunto |              |              |                |        |

|       |             | s all unmaske<br>s all peripher  |                 | rinterrupts |              |              |                |        |

| When  |             | • •                              |                 |             |              |              |                |        |

| 1 = E | nable       | s all low priori                 |                 | •           |              |              |                |        |

|       |             | es all priority p                | •               |             |              |              |                |        |

|       |             | MR0 Overflov                     | •               |             |              |              |                |        |

|       |             | s the TMR0 o<br>es the TMR0 o    |                 | •           |              |              |                |        |

|       |             | T0 External In                   |                 |             |              |              |                |        |

| 1 = E | nables      | s the INT0 ex                    | ternal interru  | upt         |              |              |                |        |

|       |             | es the INT0 ex                   |                 | •           |              |              |                |        |

|       |             | Port Change I                    |                 |             |              |              |                |        |

|       |             | s the RB port<br>es the RB port  | •               | •           |              |              |                |        |

|       |             | MR0 Overflov                     | Ũ               | •           |              |              |                |        |

|       |             | register has o                   | •               | •           | ed in softwa | are)         |                |        |

| 0 = T | vlR0 r      | register did no                  | ot overflow     |             |              |              |                |        |

|       |             | T0 External In                   |                 |             |              |              |                |        |

|       |             | T0 external in<br>T0 external in | •               |             | e cleared in | sonware)     |                |        |

|       |             | Port Change I                    | •               |             |              |              |                |        |

|       |             | t one of the R                   |                 | <i>.</i>    | ate (must be | e cleared ir | n software)    |        |

| 0 = N | one o       | f the RB7:RB                     | 4 pins have     | changed sta | te           |              |                |        |

| Leger | nd:         |                                  |                 |             |              |              |                |        |

| R = R | eadal       | ble bit                          | W = Wri         | table bit   | U = Unimp    | lemented l   | bit, read as ' | 0'     |

| n - 1 | /alue       | at POR                           | '1' = Bit       | is set      | '0' = Bit is | cleared      | x = Bit is u   | aknown |

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

#### REGISTER 8-3: INTCON3 REGISTER

| R/W-1                                           | R/W-1                                              | U-0            | R/W-0        | R/W-0          | U-0       | R/W-0        | R/W-0  |

|-------------------------------------------------|----------------------------------------------------|----------------|--------------|----------------|-----------|--------------|--------|

| INT2IP                                          | INT1IP                                             | —              | INT2IE       | INT1IE         | —         | INT2IF       | INT1IF |

| bit 7                                           |                                                    |                |              |                |           |              | bit    |

| INT2IP: IN<br>1 = High pr<br>0 = Low pri        |                                                    | nterrupt Prior | ity bit      |                |           |              |        |

| <b>INT1IP:</b> IN<br>1 = High pr<br>0 = Low pri |                                                    | nterrupt Prior | ity bit      |                |           |              |        |

| Unimplem                                        | ented: Read                                        | as '0'         |              |                |           |              |        |

| 1 = Enable                                      | T2 External Ir<br>s the INT2 ex<br>es the INT2 e:  | ternal interru | ıpt          |                |           |              |        |

| 1 = Enable                                      | T1 External Ir<br>s the INT1 ex<br>s the INT1 e:   | ternal interru | ıpt          |                |           |              |        |

| Unimplem                                        | ented: Read                                        | as '0'         |              |                |           |              |        |

| 1 = The IN                                      | T2 External Ir<br>T2 external in<br>T2 external in | terrupt occu   | rred (must l | be cleared in  | software) |              |        |

| 1 = The IN                                      | T1 External Ir<br>T1 external in<br>T1 external in | terrupt occu   | rred (must b | e cleared in   | software) |              |        |

| Legend:                                         |                                                    |                |              |                |           |              |        |

| R = Reada                                       | ble bit                                            | W = Wri        | table bit    | U = Unimp      | lemented  | bit, read as | '0'    |

| - n = Value                                     | at POR                                             | '1' = Bit      | is set       | '0' = Bit is ( | cleared   | x = Bit is u | nknown |

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

| Name             | Bit# | Buffer Type | Function                                                                                                |

|------------------|------|-------------|---------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T13CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output or Timer1/Timer3 clock input.                         |

| RC1/T1OSI        | bit1 | ST          | Input/output port pin, Timer1 oscillator input.                                                         |

| RC2/CCP1         | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                                |

| RC3/SCK/SCL      | bit3 | ST          | Input/output port pin or synchronous serial clock for SPI/I <sup>2</sup> C.                             |

| RC4/SDI/SDA      | bit4 | ST          | Input/output port pin or SPI Data in (SPI mode) or Data I/O $(l^2C \text{ mode})$ .                     |

| RC5/SDO          | bit5 | ST          | Input/output port pin or Synchronous Serial Port Data output.                                           |

| RC6/TX/CK        | bit6 | ST          | Input/output port pin, Addressable USART Asynchronous Transmit, or Addressable USART Synchronous Clock. |

| RC7/RX/DT        | bit7 | ST          | Input/output port pin, Addressable USART Asynchronous Receive, or Addressable USART Synchronous Data.   |

#### TABLE 9-5: PORTC FUNCTIONS

Legend: ST = Schmitt Trigger input

### TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7  | Bit 6     | Bit 5       | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|-------|--------|-----------|-------------|--------|-------|-------|-------|-------|-------------------------|---------------------------------|

| PORTC | RC7    | RC6       | RC5         | RC4    | RC3   | RC2   | RC1   | RC0   | xxxx xxxx               | uuuu uuuu                       |

| LATC  | LATC D | ata Outpu | it Register |        |       |       |       |       | XXXX XXXX               | uuuu uuuu                       |

| TRISC | PORTC  | Data Dire | ection Reg  | jister |       |       |       |       | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged

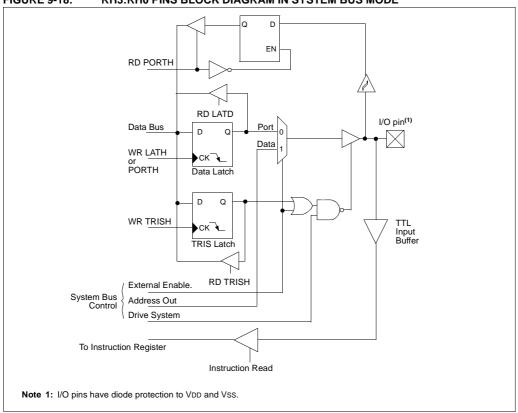

### FIGURE 9-18: RH3:RH0 PINS BLOCK DIAGRAM IN SYSTEM BUS MODE

## 13.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers: TMR3H and TMR3L)

- Readable and writable (both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- RESET from CCP module trigger

Figure 13-1 is a simplified block diagram of the Timer3 module.

Register 13-1 shows the Timer3 Control register. This register controls the operating mode of the Timer3 module and sets the CCP clock source.

Register 11-1 shows the Timer1 Control register. This register controls the operating mode of the Timer1 module, as well as contains the Timer1 oscillator enable bit (T1OSCEN), which can be a clock source for Timer3.

Note: Timer3 is disabled on POR.

|         | 13000                   | LOIOTEIX                       |                                 |                                                          |                            |              |                |         |

|---------|-------------------------|--------------------------------|---------------------------------|----------------------------------------------------------|----------------------------|--------------|----------------|---------|

|         | R/W-0                   | R/W-0                          | R/W-0                           | R/W-0                                                    | R/W-0                      | R/W-0        | R/W-0          | R/W-0   |

|         | RD16                    | T3CCP2                         | T3CKPS1                         | T3CKPS0                                                  | T3CCP1                     | T3SYNC       | TMR3CS         | TMR3ON  |

|         | bit 7                   |                                |                                 |                                                          |                            |              |                | bit 0   |

| bit 7   | RD16: 16-b              | oit Read/Wr                    | ite Mode Ena                    | able                                                     |                            |              |                |         |

|         |                         | •                              |                                 | Timer3 in on<br>Timer3 in two                            | •                          |              |                |         |

| bit 6,3 | T3CCP2:T                | 3CCP1: Tim                     | ner3 and Tim                    | er1 to CCPx                                              | Enable bits                |              |                |         |

|         | 01 = Timer<br>Timer     | 3 is the cloc<br>1 is the cloc | k source for<br>k source for    | compare/cap<br>compare/cap<br>compare/cap<br>compare/cap | ture of CCP<br>ture of CCP | 2,<br>1      |                |         |

| bit 5-4 | T3CKPS1:                | T3CKPS0:                       | Timer3 Input                    | Clock Presc                                              | ale Select b               | its          |                |         |

|         | 11 <b>= 1:8 P</b> I     | rescale valu                   | е                               |                                                          |                            |              |                |         |

|         |                         | rescale valu                   | -                               |                                                          |                            |              |                |         |

|         |                         | rescale valu<br>rescale valu   | -                               |                                                          |                            |              |                |         |

| bit 2   | (Not usable             | e if the syste                 |                                 | put Synchror<br>les from Time                            |                            | trol bit     |                |         |

|         |                         | t synchroniz                   | e external clo<br>nal clock inp | •                                                        |                            |              |                |         |

|         | When TMR                |                                |                                 |                                                          |                            |              |                |         |

|         | This bit is i           | gnored. Tim                    | er3 uses the                    | internal cloc                                            | k when TMF                 | R3CS = 0.    |                |         |

| bit 1   | TMR3CS:                 | Timer3 Cloc                    | k Source Se                     | lect bit                                                 |                            |              |                |         |

|         | falling                 | •                              |                                 | 1 oscillator o                                           | r T1CKI (on                | the rising e | dge after th   | e first |

| bit 0   | TMR3ON:                 | Timer3 On I                    | bit                             |                                                          |                            |              |                |         |

|         | 1 = Enable              |                                |                                 |                                                          |                            |              |                |         |

|         | $0 = \text{Stops}^{-1}$ | Timer3                         |                                 |                                                          |                            |              |                |         |

|         | Legend:                 |                                |                                 |                                                          |                            |              |                |         |

|         | R = Reada               | ble bit                        | W = W                           | ritable bit                                              | U = Unim                   | plemented I  | oit, read as ' | 0'      |

|         | - n = Value             | at POR                         | '1' = Bi                        | t is set                                                 | '0' = Bit is               | cleared      | x = Bit is u   | nknown  |

|         |                         |                                |                                 |                                                          |                            |              |                |         |

### REGISTER 13-1: T3CON REGISTER

## 15.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received, simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- · Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL/LVOIN

Additionally, a fourth pin may be used when in any Slave mode of operation:

Slave Select (SS) - RA5/SS/AN4

#### 15.3.1 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits SSPCON1<5:0> and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 15-1 shows the block diagram of the MSSP module, when in SPI mode.

## FIGURE 15-1: MSSP BLOCK DIAGRAM

#### (SPI MODE) Internal Data Bus Read Write SSPBUF reg SSPSR reg SDI bit0 Shift Clock SS Control $\ge$ Enable SS Edge Select 2 Clock Select SSPM3:SSPM0 SMP:CKE 4 MR2 Output ∤2 Edge Select $\mathbb{X}$ Prescaler Tosc SCK 4, 16, 64 Data to TX/RX in SSPSR TRIS bit Note: I/O pins have diode protection to VDD and VSS.

#### REGISTER 17-3: ADCON2 REGISTER

bit

bit bit

| R/W-0                                                                                   | U-0                                                       | U-0        | U-0                                            | U-0            | R/W-0     | R/W-0        | R/W-0  |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|------------|------------------------------------------------|----------------|-----------|--------------|--------|

| ADFM                                                                                    | —                                                         | _          | —                                              | —              | ADCS2     | ADCS1        | ADCS0  |

| bit 7                                                                                   |                                                           |            |                                                |                |           |              | bit 0  |

| <b>ADFM:</b> A/I<br>1 = Right ji<br>0 = Left jus                                        |                                                           | mat Select | bit                                            |                |           |              |        |

| Unimplem                                                                                | ented: Rea                                                | d as '0'   |                                                |                |           |              |        |

| 000 = Fos<br>001 = Fos<br>010 = Fos<br>011 = FRC<br>100 = Fos<br>101 = Fos<br>110 = Fos | C/2<br>C/8<br>C/32<br>(clock deriv<br>C/4<br>C/16<br>C/64 | ed from an | Clock Select<br>internal RC o<br>internal RC o | oscillator = 1 | ,         |              |        |

| Legend:                                                                                 |                                                           |            |                                                |                |           |              |        |

| R = Reada                                                                               | ble bit                                                   | W = W      | /ritable bit                                   | U = Unim       | plemented | bit, read as | '0'    |

| - n = Value                                                                             | at POR                                                    | '1' = B    | it is set                                      | '0' = Bit i    | s cleared | x = Bit is u | nknown |

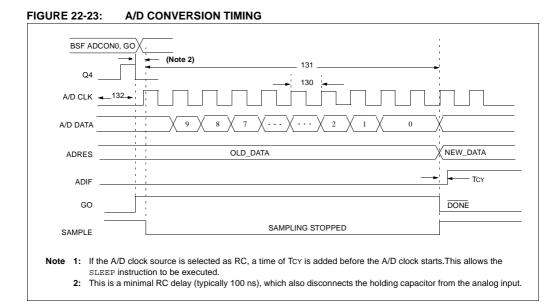

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and VSS), or the voltage level on the RA3/AN3/VREF+ pin and RA2/AN2/VREF-.

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in SLEEP, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off and any conversion is aborted.

Each port pin associated with the A/D converter can be configured as an analog input (RA3 can also be a voltage reference), or as a digital I/O.

The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0 register) is cleared, and A/D interrupt flag bit ADIF is set. The block diagram of the A/D module is shown in Figure 17-1.

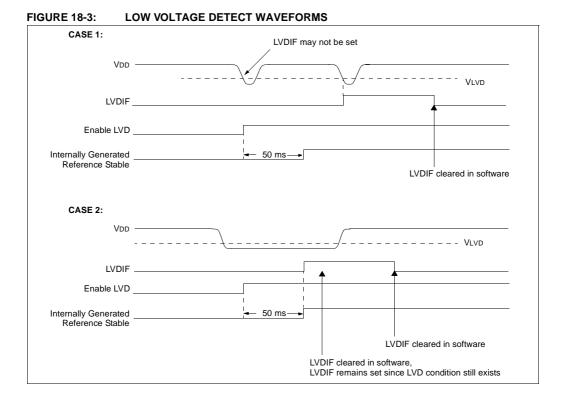

## 18.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease current consumption, the LVD circuitry only needs to be enabled for short periods, where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to setup the LVD module:

- 1. Write the value to the LVDL3:LVDL0 bits (LVDCON register), which selects the desired LVD trip point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- Clear the LVD interrupt flag, which may have falsely become set, until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 18-3 shows typical waveforms that the LVD module may be used to detect.

|             | 6                                                           | Bit Toggle                                                               | ə f                                        |                                       |                             |

|-------------|-------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|---------------------------------------|-----------------------------|

| Synt        | tax:                                                        | [ <i>label</i> ] B                                                       | TG f, b [,                                 | a]                                    |                             |

| Ope         | rands:                                                      | 0 ≤ f ≤ 255<br>0 ≤ b < 7<br>a ∈ [0,1]                                    | 5                                          |                                       |                             |

| Ope         | ration:                                                     | $(\overline{f} < b >) \to f$                                             | <b></b>                                    |                                       |                             |

| Statu       | us Affected:                                                | None                                                                     |                                            |                                       |                             |

| Enco        | oding:                                                      | 0111                                                                     | bbba                                       | ffff                                  | ffff                        |

| Des         | cription:                                                   | Bit 'b' in da<br>inverted.<br>will be sele<br>value. If 'a<br>selected a | lf 'a' is 0,<br>ected, ove<br>a' is 1, the | the Acce<br>erriding the<br>Bank with | ss Bank<br>ne BSR<br>ill be |

| Wor         | ds:                                                         | 1                                                                        |                                            |                                       |                             |

| Cycl        | es:                                                         | 1                                                                        |                                            |                                       |                             |

| QC          | ycle Activity:                                              |                                                                          |                                            |                                       |                             |

|             | <u></u>                                                     | 00                                                                       | 00                                         |                                       |                             |

|             | Q1                                                          | Q2                                                                       | Q3                                         | (                                     | Q4                          |

|             | Q1<br>Decode                                                | Q2<br>Read<br>register 'f'                                               | Q3<br>Process<br>Data                      | s W                                   | Q4<br>rite<br>ster 'f'      |

| <u>Exar</u> |                                                             | Read<br>register 'f'                                                     | Process<br>Data                            | s W                                   | rite                        |

|             | Decode                                                      | Read<br>register 'f'<br>BTG F                                            | Process<br>Data                            | s W<br>regis                          | rite                        |

|             | Decode<br>mple:<br>Before Instru                            | Read<br>register 'f'<br>BTG F<br>Inction:<br>= 0111 0<br>ion:            | Process<br>Data                            | s W<br>regis                          | rite                        |

|             | Decode<br>mple:<br>Before Instru<br>PORTC<br>After Instruct | Read<br>register 'f'<br>BTG F<br>Inction:<br>= 0111 0<br>ion:            | Process<br>Data                            | s W<br>regis                          | rite                        |

| Syntax:                                                                                          | [ <i>label</i> ] B                                                         | OV n                                                  |                                |                                            |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------|--------------------------------------------|

| Operands:                                                                                        | -128 ≤ n ≤                                                                 | 127                                                   |                                |                                            |

| Operation:                                                                                       | if overflow<br>(PC) + 2 +                                                  |                                                       |                                |                                            |

| Status Affected:                                                                                 | None                                                                       |                                                       |                                |                                            |

| Encoding:                                                                                        | 1110                                                                       | 0100                                                  | nnnn                           | nnnn                                       |

| Description:                                                                                     | If the Over<br>gram will I<br>The 2's co                                   | oranch.                                               |                                | •                                          |

|                                                                                                  | added to t<br>have incre<br>instruction<br>PC+2+2n.<br>two-cycle           | emented<br>, the ne<br>This in:                       | to fetc<br>w addre<br>structio | h the nex<br>ess will b                    |

| Words:                                                                                           | 1                                                                          |                                                       |                                |                                            |

|                                                                                                  |                                                                            |                                                       |                                |                                            |

|                                                                                                  | 1(2)                                                                       |                                                       |                                |                                            |

| Cycles:<br>Q Cycle Activity:<br>If Jump:                                                         | •                                                                          |                                                       |                                |                                            |

| Cycles:<br>Q Cycle Activity:                                                                     | •                                                                          | Q3                                                    | ۰.<br>۱                        | Q4                                         |

| Cycles:<br>Q Cycle Activity:<br>If Jump:                                                         | 1(2)                                                                       | Q3<br>Proce<br>Data                                   | ss V                           |                                            |

| Cycles:<br>Q Cycle Activity:<br>If Jump:<br>Q1                                                   | 1(2)<br>Q2<br>Read literal                                                 | Proce                                                 | ss W                           |                                            |

| Cycles:<br>Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No                                   | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                    | Proce<br>Data<br>No                                   | ss W                           | /rite to PC                                |

| Cycles:<br>Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation                      | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                    | Proce<br>Data<br>No                                   | ss W<br>a<br>ion d             | /rite to PC                                |

| Cycles:<br>Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:       | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation                       | Proce<br>Data<br>No<br>operati                        | ss W<br>ion d<br>ss            | Vrite to PC                                |

| Cycles:<br>Q Cycle Activity:<br>If Jump:<br>Q1<br>Decode<br>No<br>operation<br>If No Jump:<br>Q1 | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal | Proce<br>Data<br>No<br>operati<br>Q3<br>Proce<br>Data | ss W<br>ion d<br>ss            | Vrite to PC<br>No<br>operation<br>Q4<br>No |

address (Jump)

address (HERE+2)

PC

PC

If Overflow

=

=

= 0;

| CPFSGT                                              | -                                                                                                                                                                                                                                                                                                                                       | Compare f with WREG,<br>skip if f > WREG                                                                                      |                 |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:                                             | [label] (                                                                                                                                                                                                                                                                                                                               | CPFSGT f[                                                                                                                     | ,a]             |  |  |  |  |  |

| Operands:                                           | • •                                                                                                                                                                                                                                                                                                                                     | $0 \le f \le 255$                                                                                                             |                 |  |  |  |  |  |

| Operation:                                          | (f) – (WRE<br>skip if (f) >                                                                                                                                                                                                                                                                                                             | (f) – (WREG),<br>skip if (f) > (WREG)<br>(unsigned comparison)                                                                |                 |  |  |  |  |  |

| Status Affected:                                    | None                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |                 |  |  |  |  |  |

| Encoding:                                           | 0110 010a ffff ffff                                                                                                                                                                                                                                                                                                                     |                                                                                                                               |                 |  |  |  |  |  |

| Description:                                        | memory lo                                                                                                                                                                                                                                                                                                                               | Compares the contents of data<br>memory location 'f' to the contents of<br>the WREG by performing an<br>unsigned subtraction. |                 |  |  |  |  |  |

|                                                     | If the contents of 'f' are greater than<br>the contents of , then the fetched<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. If 'a' is 0, the<br>Access Bank will be selected, over-<br>riding the BSR value. If 'a' is 1, the<br>Bank will be selected as per the BSR<br>value. |                                                                                                                               |                 |  |  |  |  |  |

| Words:                                              | 1                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |                 |  |  |  |  |  |

| Cycles:                                             |                                                                                                                                                                                                                                                                                                                                         | ycles if skip a<br>a 2-word inst                                                                                              |                 |  |  |  |  |  |

| Q Cycle Activity:                                   | 00                                                                                                                                                                                                                                                                                                                                      | 02                                                                                                                            | 04              |  |  |  |  |  |

| Q1                                                  | Q2                                                                                                                                                                                                                                                                                                                                      | Q3                                                                                                                            | Q4              |  |  |  |  |  |

| Decode                                              | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                    | Process<br>Data                                                                                                               | No<br>operation |  |  |  |  |  |

| If skip:                                            |                                                                                                                                                                                                                                                                                                                                         |                                                                                                                               | operander       |  |  |  |  |  |

| Q1                                                  | Q2                                                                                                                                                                                                                                                                                                                                      | Q3                                                                                                                            | Q4              |  |  |  |  |  |

| No                                                  | No                                                                                                                                                                                                                                                                                                                                      | No                                                                                                                            | No              |  |  |  |  |  |

| operation                                           | operation                                                                                                                                                                                                                                                                                                                               | operation                                                                                                                     | operation       |  |  |  |  |  |

| If skip and follow                                  | ed by 2-word                                                                                                                                                                                                                                                                                                                            | instruction:                                                                                                                  |                 |  |  |  |  |  |

| Q1                                                  | Q2                                                                                                                                                                                                                                                                                                                                      | Q3                                                                                                                            | Q4              |  |  |  |  |  |

| No                                                  | No                                                                                                                                                                                                                                                                                                                                      | No                                                                                                                            | No              |  |  |  |  |  |

| operation                                           | operation                                                                                                                                                                                                                                                                                                                               | operation                                                                                                                     | operation       |  |  |  |  |  |

| No<br>operation                                     | No<br>operation                                                                                                                                                                                                                                                                                                                         | No<br>operation                                                                                                               | No<br>operation |  |  |  |  |  |

| Example: HERE CPFSGT REG<br>NGREATER :<br>GREATER : |                                                                                                                                                                                                                                                                                                                                         |                                                                                                                               |                 |  |  |  |  |  |

| Before Instru                                       |                                                                                                                                                                                                                                                                                                                                         |                                                                                                                               |                 |  |  |  |  |  |

| PC<br>WREG<br>After Ins<br>If REG                   | = Ad<br>= ?<br>truction                                                                                                                                                                                                                                                                                                                 | ldress (HERE)<br>REG;                                                                                                         |                 |  |  |  |  |  |

| PC                                                  |                                                                                                                                                                                                                                                                                                                                         | Idress (GREAT                                                                                                                 | 'ER)            |  |  |  |  |  |

| If REG                                              |                                                                                                                                                                                                                                                                                                                                         | REG;                                                                                                                          | -,              |  |  |  |  |  |

| PC = Address (NGREATER)                             |                                                                                                                                                                                                                                                                                                                                         |                                                                                                                               |                 |  |  |  |  |  |

| CPFSL                          | т                                                                                         | Compare<br>skip if f <                                                                                                                                                                                                                                                                                                             | f with WREG<br>WREG                                             | З,              |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------|--|--|--|--|

| Syntax:                        |                                                                                           | [label]                                                                                                                                                                                                                                                                                                                            | CPFSLT f[,                                                      | a]              |  |  |  |  |

| Operan                         | ds:                                                                                       | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                           | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$ |                 |  |  |  |  |

| Operati                        | on:                                                                                       | (f) – (WRE<br>skip if (f) <<br>(unsigned                                                                                                                                                                                                                                                                                           |                                                                 | 1               |  |  |  |  |

| Status /                       | Affected:                                                                                 | None                                                                                                                                                                                                                                                                                                                               |                                                                 |                 |  |  |  |  |

| Encodir                        | ng:                                                                                       | 0110                                                                                                                                                                                                                                                                                                                               | 000a ffi                                                        | f ffff          |  |  |  |  |

| Descrip                        | tion:                                                                                     | Compares the contents of data<br>memory location 'f' to the contents<br>of WREG by performing an<br>unsigned subtraction.<br>If the contents of 'f' are less than the<br>contents of WREG, then the fetched<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. If 'a' is 0, the |                                                                 |                 |  |  |  |  |

|                                | Access Bank will be selected. If a<br>1, the Bank will be selected as p<br>the BSR value. |                                                                                                                                                                                                                                                                                                                                    |                                                                 |                 |  |  |  |  |

| Words:                         |                                                                                           | 1                                                                                                                                                                                                                                                                                                                                  |                                                                 |                 |  |  |  |  |

| Cycles:                        | Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.           |                                                                                                                                                                                                                                                                                                                                    |                                                                 |                 |  |  |  |  |

| Q Cycle                        | Activity:                                                                                 |                                                                                                                                                                                                                                                                                                                                    |                                                                 |                 |  |  |  |  |

|                                | Q1                                                                                        | Q2                                                                                                                                                                                                                                                                                                                                 | Q3                                                              | Q4              |  |  |  |  |

| [                              | Decode                                                                                    | Read<br>register 'f'                                                                                                                                                                                                                                                                                                               | Process<br>Data                                                 | No<br>operation |  |  |  |  |

| If skip:                       |                                                                                           | 0                                                                                                                                                                                                                                                                                                                                  |                                                                 |                 |  |  |  |  |

|                                | Q1                                                                                        | Q2                                                                                                                                                                                                                                                                                                                                 | Q3                                                              | Q4              |  |  |  |  |

|                                | No                                                                                        | No                                                                                                                                                                                                                                                                                                                                 | No                                                              | No              |  |  |  |  |

| ·                              | peration                                                                                  | operation                                                                                                                                                                                                                                                                                                                          | operation                                                       | operation       |  |  |  |  |

| If skip a                      |                                                                                           | ed by 2-word                                                                                                                                                                                                                                                                                                                       |                                                                 |                 |  |  |  |  |

| r                              | Q1                                                                                        | Q2                                                                                                                                                                                                                                                                                                                                 | Q3                                                              | Q4              |  |  |  |  |

| 0                              | No<br>peration                                                                            | No<br>operation                                                                                                                                                                                                                                                                                                                    | No<br>operation                                                 | No<br>operation |  |  |  |  |

| -                              | No                                                                                        | No                                                                                                                                                                                                                                                                                                                                 | No                                                              | No              |  |  |  |  |

| o                              | peration                                                                                  | operation                                                                                                                                                                                                                                                                                                                          | operation                                                       | operation       |  |  |  |  |

| <u>Exampl</u>                  | <u>e</u> :                                                                                | NLESS                                                                                                                                                                                                                                                                                                                              | CPFSLT REG<br>:                                                 |                 |  |  |  |  |