Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 25MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 37                                                                       |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | ROMIess                                                                  |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

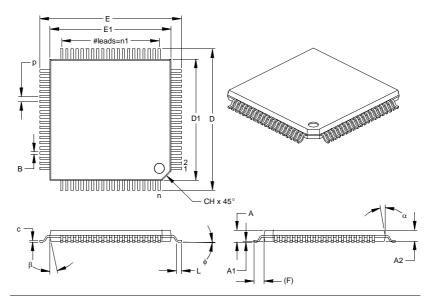

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 84-LCC (J-Lead)                                                          |

| Supplier Device Package    | 84-PLCC (29.31x29.31)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc801-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |            | Pin N     | umber     |      |                                         |                                         |                                     |

|----------|------------|-----------|-----------|------|-----------------------------------------|-----------------------------------------|-------------------------------------|

| Pin Name | PIC1       | BC601     | PIC18C801 |      | Pin<br>Type                             | Buffer<br>Type                          |                                     |

|          | TQFP       | PLCC      | TQFP      | PLCC | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Description                         |

|          |            |           |           |      |                                         |                                         | PORTE is a bi-directional I/O port. |

| RE0/AD8  | 2          | 11        | 4         | 15   |                                         |                                         |                                     |

| RE0      |            |           |           |      | I/O                                     | ST                                      | Digital I/O.                        |

| AD8      |            |           |           |      | I/O                                     | TTL                                     | External memory address/data 8.     |

| RE1/AD9  | 1          | 10        | 3         | 14   |                                         |                                         |                                     |

| RE1      |            |           |           |      | I/O                                     | ST                                      | Digital I/O.                        |

| AD9      |            |           |           |      | I/O                                     | TTL                                     | External memory address/data 9.     |

| RE2/AD10 | 64         | 9         | 78        | 9    |                                         |                                         | -                                   |

| RE2      |            |           | _         |      | I/O                                     | ST                                      | Digital I/O.                        |

| AD10     |            |           |           |      | I/O                                     | TTL                                     | External memory address/data 10.    |

| RE3/AD11 | 63         | 8         | 77        | 8    |                                         |                                         |                                     |

| RE3      |            |           |           |      | I/O                                     | ST                                      | Digital I/O.                        |

| AD11     |            |           |           |      | I/O                                     | TTL                                     | External memory address/data 11.    |

| RE4/AD12 | 62         | 7         | 76        | 7    |                                         |                                         | -                                   |

| RE4      |            |           |           |      | I/O                                     | ST                                      | Digital I/O.                        |

| AD12     |            |           |           |      | I/O                                     | TTL                                     | External memory address/data 12.    |

| RE5/AD13 | 61         | 6         | 75        | 6    |                                         |                                         | -                                   |

| RE5      |            | Ŭ         |           | č    | I/O                                     | ST                                      | Digital I/O.                        |

| AD13     |            |           |           |      | I/O                                     | TTL                                     | External memory address/data 13.    |

| RE6/AD14 | 60         | 5         | 74        | 5    |                                         |                                         | ,                                   |

| RE6      | 00         | 5         |           | 5    | I/O                                     | ST                                      | Digital I/O.                        |

| AD14     |            |           |           |      | 1/O                                     | TTL                                     | External memory address/data 14.    |

| RE7/AD15 | 59         | 4         | 73        | 4    |                                         |                                         | ,                                   |

| RE7      | 00         | •         |           | •    | I/O                                     | ST                                      | Digital I/O.                        |

| AD15     |            |           |           |      | 1/O                                     | ST                                      | External memory address/data 15.    |

| -        | TL compati | ble input | 1         |      |                                         | -                                       | IOS compatible input or output      |

| TABLE 1-2: | PINOUT I/O DESCRIPTIONS | (CONTINUED) |

|------------|-------------------------|-------------|

|            |                         |             |

ST = Schmitt Trigger input with CMOS levels

= Input I.

P = Power

Analog = Analog input

0 = Output

OD = Open Drain (no P diode to VDD)

| Register            | Applicable<br>Devices |     | Power-on Reset | MCLR Reset<br>WDT Reset<br>Reset Instruction<br>Stack Over/Underflow Reset | Wake-up via WDT or<br>Interrupt |  |  |

|---------------------|-----------------------|-----|----------------|----------------------------------------------------------------------------|---------------------------------|--|--|

| POSTINC2            | 601                   | 801 | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |

| POSTDEC2            | 601                   | 801 | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |

| PREINC2             | 601                   | 801 | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |

| PLUSW2              | 601                   | 801 | (Note 5)       | (Note 5)                                                                   | (Note 5)                        |  |  |

| FSR2H               | 601                   | 801 | 0000           | 0000                                                                       | uuuu                            |  |  |

| FSR2L               | 601                   | 801 | XXXX XXXX      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| STATUS              | 601                   | 801 | x xxxx         | u uuuu                                                                     | u uuuu                          |  |  |

| TMR0H               | 601                   | 801 | xxxx xxxx      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| TMR0L               | 601                   | 801 | xxxx xxxx      | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |

| T0CON               | 601                   | 801 | 1111 1111      | 1111 1111                                                                  | uuuu uuuu                       |  |  |

| OSCCON              | 601                   | 801 | 00 0-00        | uu u-u0                                                                    | uu u-uu                         |  |  |

| LVDCON              | 601                   | 801 | 00 0101        | 00 0101                                                                    | uu uuuu                         |  |  |

| WDTCON              | 601                   | 801 | 1111           | uuuu                                                                       | uuuu                            |  |  |

| RCON <sup>(4)</sup> | 601                   | 801 | 0r-1 11qr      | 0r-1 qqur                                                                  | ur-u qqur                       |  |  |

| TMR1H               | 601                   | 801 | XXXX XXXX      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| TMR1L               | 601                   | 801 | xxxx xxxx      | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |

| T1CON               | 601                   | 801 | 0-00 0000      | u-uu uuuu                                                                  | u-uu uuuu                       |  |  |

| TMR2                | 601                   | 801 | XXXX XXXX      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| PR2                 | 601                   | 801 | 1111 1111      | 1111 1111                                                                  | 1111 1111                       |  |  |

| T2CON               | 601                   | 801 | -000 0000      | -000 0000                                                                  | -uuu uuuu                       |  |  |

| SSPBUF              | 601                   | 801 | xxxx xxxx      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| SSPADD              | 601                   | 801 | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSPSTAT             | 601                   | 801 | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSPCON1             | 601                   | 801 | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSPCON2             | 601                   | 801 | 0000 0000      | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| ADRESH              | 601                   | 801 | xxxx xxxx      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| ADRESL              | 601                   | 801 | xxxx xxxx      | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |

| ADCON0              | 601                   | 801 | 00 0000        | 00 0000                                                                    | uu uuuu                         |  |  |

| ADCON1              | 601                   | 801 | -000 0000      | -000 0000                                                                  | -uuu uuuu                       |  |  |

| ADCON2              | 601                   | 801 | 0 0 0 0        | 0000                                                                       | uuuu                            |  |  |

| CCPR1H              | 601                   | 801 | xxxx xxxx      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| CCPR1L              | 601                   | 801 | XXXX XXXX      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| CCP1CON             | 601                   | 801 | 00 0000        | 00 0000                                                                    | uu uuuu                         |  |  |

### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', ~q = value depends on condition, r = reserved, maintain '0'

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (00008h or 00018h).

- **3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH, and TOSL are updated with the current value of the PC. The SKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: This is not a physical register. It is an indirect pointer that addresses another register. The contents returned is the value contained in the addressed register.

### 4.2.3 PUSH AND POP INSTRUCTIONS

Since the Top-of-Stack (TOS) is readable and writable, the ability to push values onto the stack and pop values off the stack, without disturbing normal program execution, is a desirable option. To push the current PC value onto the stack, a PUSH instruction can be executed. This will increment the stack pointer and load the current PC value onto the stack. TOSU, TOSH and TOSL can then be modified to place a return address on the stack.

The POP instruction discards the current TOS by decrementing the stack pointer. The previous value pushed onto the stack then becomes the TOS value.

#### 4.2.4 STACK FULL/UNDERFLOW RESETS

These RESETS are enabled/disabled by programming the STVREN configuration bit in CONFIG4L register.

When the STVREN bit is disabled, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a RESET. When the STVREN bit is enabled, a full or underflow will set the appropriate STKFUL or STKUNF bit and then cause a RESET. The STKFUL or STKUNF bits are only cleared by the user software or a POR.

### 4.3 Fast Register Stack

A "fast return" option is available for interrupts and calls. A fast register stack is provided for the STATUS, WREG and BSR registers, and is only one layer in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the fast register stack are then loaded back into the working registers, if the fast return instruction is used to return from the interrupt.

A low or high priority interrupt source will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably for low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten.

If high priority interrupts are not disabled during low priority interrupts, users must save the key registers in software during a low priority interrupt.

If no interrupts are used, the fast register stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a fast call instruction must be executed.

Example 4-1 shows a source code example that uses the fast register stack.

### EXAMPLE 4-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST       | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------------|---------------------------------------------------------|

| •<br>SUB1 •           |                                                         |

| •<br>•<br>RETURN FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

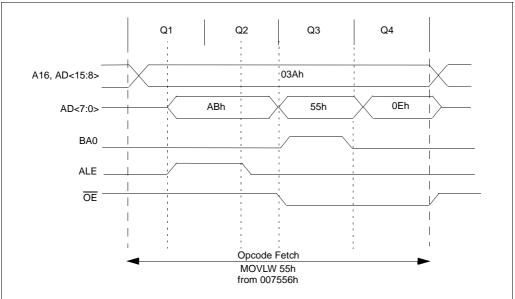

### 5.2.2 8-BIT DE-MULTIPLEXED MODE

The 8-bit De-Multiplexed mode applies only to the PIC18C801. Data and address lines are available separately. External components are not necessary in this mode.

For 8-bit De-Multiplexed mode on the PIC18C801, the instructions are fetched as two 8-bit bytes on a dedicated data bus (PORTJ). The address will be presented for the entire duration of the fetch cycle on a separate address bus. The two instruction bytes are sequentially fetched within one instruction cycle (TcY). Therefore, the designer must choose external memory devices according to timing calculations, based on 1/2 TcY (2 times instruction rate). For proper memory speed selection, setup and hold times must be considered. The Address Latch Enable (ALE) pin is left unconnected, since glue logic is not necessary. The  $\overline{OE}$  output enable signal will enable one byte of program memory for a portion of the instruction cycle, then BA0 will change and the second byte will be enabled to form the 16-bit instruction word. The least significant bit of the address, BA0, must be connected to the memory devices in this mode. Figure 5-3 shows an example of 8-bit De-Multiplexed mode on the PIC18C801. The control signals used in 8-bit De-Multiplexed mode are outlined in Register 5-2. Register 5-4 describes 8-bit De-Multiplexed mode timing.

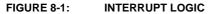

### 8.0 INTERRUPTS

PIC18C601/801 devices have 15 interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level, or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will override any low priority interrupts that may be in progress.

There are 10 registers that are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2

- PIE1, PIE2

- IPR1, IPR2

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- · Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON register). When interrupt priority is enabled, there are two bits that enable interrupts globally. Setting the GIEH bit (INTCON register) enables all interrupts that have the priority bit set. Setting the GIEL bit (INTCON register) enables all interrupts that have the priority bit cleared. When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority level. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. The PEIE bit (INTCON register) enables/disables all peripheral interrupt sources. The GIE bit (INTCON register) enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the Global Interrupt Enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (000008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts, to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

#### REGISTER 8-3: INTCON3 REGISTER

| R/W-1                                                                                                                             | R/W-1                                              | U-0            | R/W-0        | R/W-0          | U-0       | R/W-0        | R/W-0  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------|--------------|----------------|-----------|--------------|--------|--|--|--|

| INT2IP                                                                                                                            | INT1IP                                             | _              | INT2IE       | INT1IE         | —         | INT2IF       | INT1IF |  |  |  |

| bit 7                                                                                                                             |                                                    |                |              |                |           |              | bit    |  |  |  |

| INT2IP: IN<br>1 = High pr<br>0 = Low pri                                                                                          |                                                    | nterrupt Prior | ity bit      |                |           |              |        |  |  |  |

| <b>INT1IP:</b> IN<br>1 = High pr<br>0 = Low pri                                                                                   |                                                    | nterrupt Prior | ity bit      |                |           |              |        |  |  |  |

| Unimplem                                                                                                                          | ented: Read                                        | as '0'         |              |                |           |              |        |  |  |  |

| INT2IE: INT2 External Interrupt Enable bit<br>1 = Enables the INT2 external interrupt<br>0 = Disables the INT2 external interrupt |                                                    |                |              |                |           |              |        |  |  |  |

| 1 = Enable                                                                                                                        | T1 External Ir<br>s the INT1 ex<br>s the INT1 e:   | ternal interru | ıpt          |                |           |              |        |  |  |  |

| Unimplem                                                                                                                          | ented: Read                                        | as '0'         |              |                |           |              |        |  |  |  |

| 1 = The IN                                                                                                                        | T2 External Ir<br>T2 external in<br>T2 external in | terrupt occu   | rred (must l | be cleared in  | software) |              |        |  |  |  |

| 1 = The IN                                                                                                                        | T1 External Ir<br>T1 external in<br>T1 external in | terrupt occu   | rred (must b | e cleared in   | software) |              |        |  |  |  |

| Legend:                                                                                                                           |                                                    |                |              |                |           |              |        |  |  |  |

| R = Reada                                                                                                                         | ble bit                                            | W = Wri        | table bit    | U = Unimp      | lemented  | bit, read as | '0'    |  |  |  |

| - n = Value                                                                                                                       | at POR                                             | '1' = Bit      | is set       | '0' = Bit is ( | cleared   | x = Bit is u | nknown |  |  |  |

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

### REGISTER 8-8: PIE2 REGISTER

- n = Value at POR

|         | U-0                                     | U-0                                                                                                                                                                                      | U-0            | U-0        | R/W-0     | R/W-0      | R/W-0          | R/W-0  |  |  |  |  |  |

|---------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|-----------|------------|----------------|--------|--|--|--|--|--|

|         | —                                       | _                                                                                                                                                                                        | —              | —          | BCLIE     | LVDIE      | TMR3IE         | CCP2IE |  |  |  |  |  |

|         | bit 7                                   |                                                                                                                                                                                          |                |            |           |            |                | bit 0  |  |  |  |  |  |

| bit 7-4 | Unimplem                                | ented: Read                                                                                                                                                                              | as '0'         |            |           |            |                |        |  |  |  |  |  |

| bit 3   | 1 = Enable                              | BCLIE: Bus Collision Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled                                                                                                                 |                |            |           |            |                |        |  |  |  |  |  |

| bit 2   | LVDIE: Low<br>1 = Enable<br>0 = Disable |                                                                                                                                                                                          | tect Interrupt | Enable bit |           |            |                |        |  |  |  |  |  |

| bit 1   | 1 = Enables                             | MR3 Overflo<br>s the TMR3 o<br>s the TMR3                                                                                                                                                | overflow inte  | rrupt      |           |            |                |        |  |  |  |  |  |

| bit 0   | 1 = Enable:                             | <ul> <li>0 = Disables the TMR3 overflow interrupt</li> <li>CCP2IE: CCP2 Interrupt Enable bit</li> <li>1 = Enables the CCP2 interrupt</li> <li>0 = Disables the CCP2 interrupt</li> </ul> |                |            |           |            |                |        |  |  |  |  |  |

|         | Legend:                                 |                                                                                                                                                                                          |                |            |           |            |                |        |  |  |  |  |  |

|         | R = Readat                              | ole bit                                                                                                                                                                                  | W = Wr         | itable bit | U = Unimp | lemented b | oit, read as ' | 0'     |  |  |  |  |  |

'0' = Bit is cleared

x = Bit is unknown

'1' = Bit is set

#### **REGISTER 8-9: IPR1 REGISTER**

| U-0                                                                                                                                           | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                               | ADIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RCIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TXIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SSPIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CCP1IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TMR2IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TMR1IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| bit 7                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Unimplom                                                                                                                                      | ontod: Pood                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| •                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | h.:.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| ADIP: A/D Converter Interrupt Priority bit<br>1 = High priority<br>0 = Low priority                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |