Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

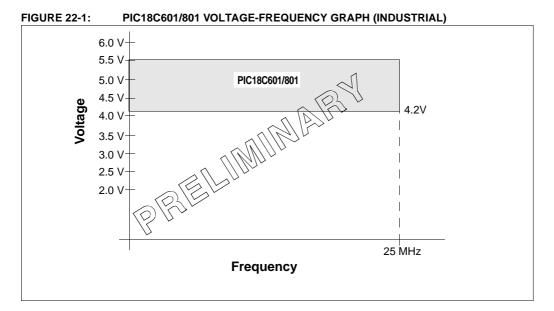

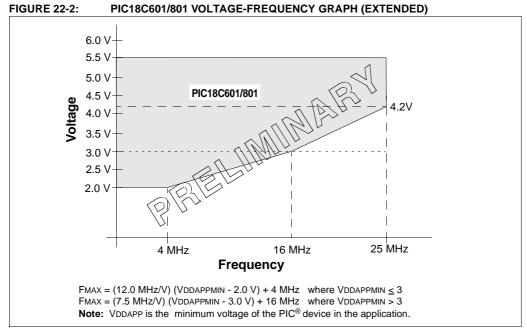

| Speed                      | 25MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 37                                                                        |

| Program Memory Size        | -                                                                         |

| Program Memory Type        | ROMIess                                                                   |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 1.5K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lc801-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

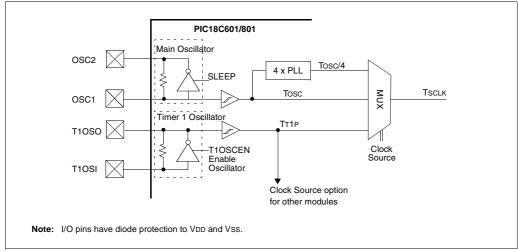

## 2.6 Oscillator Switching Feature

PIC18C601/801 devices include a feature that allows the system clock source to be switched from the main oscillator to an alternate low frequency clock source. For PIC18C601/801 devices, this alternate clock source is the Timer1 oscillator. If a low frequency crystal (32 kHz, for example) has been attached to the Timer1 oscillator pins and the Timer1 oscillator has been enabled, the device can switch to a low power execution mode. Figure 2-5 shows a block diagram of the system clock sources.

## 2.6.1 SYSTEM CLOCK SWITCH BIT

The system clock source switching is performed under software control. The system clock switch bit, SCS0 (OSCCON register), controls the clock switching. When the SCS0 bit is '0', the system clock source comes from the main oscillator, selected by the FOSC2:FOSC0 configuration bits in CONFIG1H register. When the SCS0 bit is set, the system clock source will come from the Timer1 oscillator. The SCS0 bit is cleared on all forms of RESET.

Note: The Timer1 oscillator must be enabled to switch the system clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 control register (T1CON). If the Timer1 oscillator is not enabled, any write to the SCS0 bit will be ignored (SCS0 bit forced cleared) and the main oscillator will continue to be the system clock source.

#### FIGURE 2-5: DEVICE CLOCK SOURCES

## 5.0 EXTERNAL MEMORY INTERFACE

The External Memory Interface is a feature of the PIC18C601/801 that allows the processor to access external memory devices, such as FLASH, EPROM, SRAM, etc. Memory mapped peripherals may also be accessed.

The External Memory Interface physical implementation includes up to 26 pins on the PIC18C601 and up to 38 pins on the PIC18C801. These pins are reserved for external address/data bus functions. These pins are multiplexed with I/O port pins, but the I/O functions are only enabled when program execution takes place in internal Boot RAM and the EBDIS bit in the MEMCON register is set (see Register 5-1).

## 5.1 Memory Control Register (MEMCON)

Register 5-1 shows the Memory Control Register (MEMCON). This register contains bits used to control the operation of the External Memory Interface.

## REGISTER 5-1: MEMCON REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 |  |

|-------|-------|-------|-------|-----|-----|-------|-------|--|

| EBDIS | PGRM  | WAIT1 | WAIT0 |     | —   | WM1   | WM0   |  |

| bit7  |       |       |       |     |     |       | bit0  |  |

| bit 7   | EBDIS: External Bus Disable                                                                                                                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = External system bus disabled, all external bus drivers are mapped as I/O ports</li> <li>0 = External system bus enabled, and I/O ports are disabled</li> </ul>                                                       |

| bit 6   | PGRM: Program RAM Enable                                                                                                                                                                                                          |

|         | 1 = 512 bytes of internal RAM enabled as internal program memory from location 1FFE00h to<br>1FFFFFh, external program memory at these locations is unused. Internal GPR memory<br>from 400h to 5FFh is disabled and returns 00h. |

|         | 0 = Internal RAM enabled as internal GPR memory from 400h to 5FFh. Program memory from location 1FFE00h to 1FFFFFh is configured as external program memory.                                                                      |

| bit 5-4 | WAIT<1:0>: Table Reads and Writes Bus Cycle Wait Count                                                                                                                                                                            |

|         | 11 = Table reads and writes will wait 0 TCY                                                                                                                                                                                       |

|         | 10 = Table reads and writes will wait 1 Tcy                                                                                                                                                                                       |

|         | 01 = Table reads and writes will wait 2 TCY<br>00 = Table reads and writes will wait 3 TCY                                                                                                                                        |

| bit 3-2 |                                                                                                                                                                                                                                   |

| DIL 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                        |

| bit 1-0 | WM<1:0>: TABLWT Operation with 16-bit Bus                                                                                                                                                                                         |

|         | $1X =$ Word Write mode: TABLAT0 and TABLAT1 word output, $\overline{WRH}$ active when TABLAT1 written                                                                                                                             |

|         | 01 = Byte Select mode: TABLAT data copied on both MS and LS Byte, $\overline{WRH}$ and $(\overline{UB} \text{ or } \overline{LB})$ will activate                                                                                  |

|         | 00 = Byte Write mode: TABLAT data copied on both MS and LS Byte, WRH or WRL will activate                                                                                                                                         |

|         |                                                                                                                                                                                                                                   |

|         | Legend:                                                                                                                                                                                                                           |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

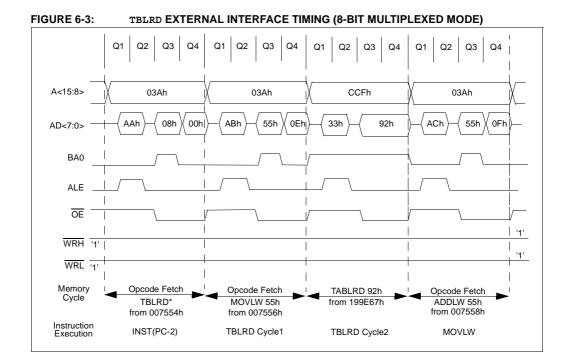

## 6.2 Table Read

The TBLRD instruction is used to retrieve data from external program memory and place it into data memory.

TBLPTR points to a byte address in external program memory space. Executing TBLRD places the byte into TABLAT. In addition, TBLPTR can be modified automatically for the next Table Read operation.

Table Reads from external program memory are performed one byte at a time. If the external interface is 8-bit, the bus interface circuitry in TABLAT will load the external value into TABLAT. If the external interface is 16-bit, interface circuitry in TABLAT will select either the high or low byte of the data from the 16-bit bus, based on the least significant bit of the address.

Example 6-1describes how to use TBLRD. Figure 6-3 and Figure 6-4 show Table Read timings for an 8-bit external interface, and Figure 6-5 describes Table Read timing for a 16-bit interface.

## EXAMPLE 6-1: TABLE READ CODE EXAMPLE

| ; Read | a byte from | location | 0020h                         |

|--------|-------------|----------|-------------------------------|

| CLRF   | TBLPTRU     | ;        | clear upper 5 bits of TBLPTR  |

| CLRF   | TBLPTRH     | ;        | clear higher 8 bits of TBLPTR |

| MOVLW  | 20h         | ;        | Load 20h into                 |

| MOVWF  | TBLPTRL     | ;        | TBLPTRL                       |

| TBLRD* |             | ;        | Data is in TABLAT             |

|        |             |          |                               |

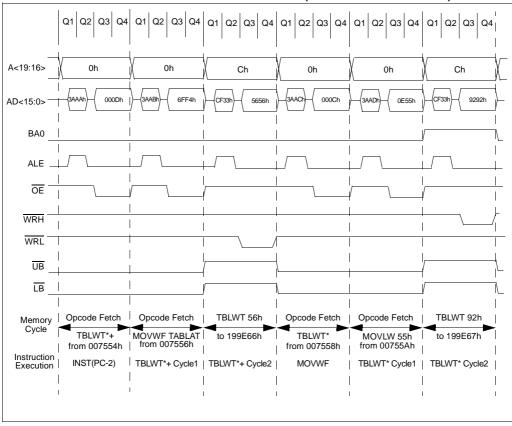

#### 6.3.2 16-BIT EXTERNAL TABLE WRITE (BYTE WRITE MODE)

This mode allows Table Writes to byte-wide external memories. During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The appropriate WRH or WRL line is strobed based on the LSb of the TBLPTR. Figure 6-8 shows the timing associated with this mode.

#### FIGURE 6-8: TBLWT EXTERNAL INTERFACE TIMING (16-BIT BYTE WRITE MODE)

## 7.1 Operation

Example 7-1 shows the sequence to perform an 8 x 8 unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 7-2 shows the sequence to do an 8 x 8 signed multiply. To account for the sign bits of the arguments, each argument's most significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 7-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

MOVFF ARG1, WREG ; MULWF ARG2 ; ARG1 \* ARG2 -> ; PRODH:PRODL

#### EXAMPLE 7-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVFF | ARG1, | WREG |   |                |

|-------|-------|------|---|----------------|

| MULWF | ARG2  |      | ; | ARG1 * ARG2 -> |

|       |       |      | ; | PRODH: PRODL   |

| BTFSC | ARG2, | SB   | ; | Test Sign Bit  |

| SUBWF | PRODH |      | ; | PRODH = PRODH  |

|       |       |      | ; | - ARG1         |

| MOVFF | ARG2, | WREG |   |                |

| BTFSC | ARG1, | SB   | ; | Test Sign Bit  |

| SUBWF | PRODH |      | ; | PRODH = PRODH  |

|       |       |      | ; | - ARG2         |

|       |       |      |   |                |

Example 7-3 shows the sequence to perform a 16 x 16 unsigned multiply. Equation 7-1 shows the algorithm that is used. The 32-bit result is stored in 4 registers RES3:RES0.

#### EQUATION 7-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L          |

|-----------|---|------------------------------------|

|           | = | (intolli intolli b ) ;             |

|           |   | (ARG1H • ARG2L • 2 <sup>8</sup> )+ |

|           |   | (ARG1L • ARG2H • 2 <sup>8</sup> )+ |

|           |   | (ARG1L • ARG2L)                    |

|           |   |                                    |

#### EXAMPLE 7-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   |        | ARG1L, |      |   |                  |

|---|--------|--------|------|---|------------------|

|   | MULWF  | ARG2L  |      | ; | ARG1L * ARG2L -> |

|   |        |        |      | ; | PRODH:PRODL      |

|   | MOVFF  | PRODH, | RES1 | ; |                  |

|   | MOVFF  | PRODL, | RES0 | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVFF  | ARG1H, | WREG |   |                  |

|   | MULWF  | ARG2H  |      | ; | ARG1H * ARG2H -> |

|   |        |        |      | ; | PRODH:PRODL      |

|   | MOVFF  | PRODH, | RES3 | ; |                  |

|   | MOVFF  | PRODL, | RES2 | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVFF  | ARG1L, | WREG |   |                  |

|   | MULWF  | ARG2H  |      | ; | ARG1L * ARG2H -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVF   | PRODL, | W    | ; |                  |

|   | ADDWF  | RES1   |      | ; | Add cross        |

|   | MOVF   | PRODH, | W    | ; | products         |

|   | ADDWFC | RES2   |      | ; | -                |

|   | CLRF   | WREG   |      | ; |                  |

|   | ADDWFC | RES3   |      | ; |                  |

| ; |        |        |      |   |                  |

|   | MOVFF  | ARG1H, | WREG | ; |                  |

|   | MULWF  | ARG2L  |      | ; | ARG1H * ARG2L -> |

|   |        |        |      | ; | PRODH: PRODL     |

|   | MOVF   | PRODL, | W    | ; |                  |

|   | ADDWF  |        |      |   | Add cross        |

|   | MOVF   | PRODH, | W    | ; | products         |

|   | ADDWFC |        |      | ; | -                |

|   | CLRF   | WREG   |      | ; |                  |

|   | ADDWFC | RES3   |      | ; |                  |

|   |        |        |      | , |                  |

|   |        |        |      |   |                  |

Example 7-4 shows the sequence to perform a 16 x 16 signed multiply. Equation 7-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs' most significant bit (MSb) is tested and the appropriate subtractions are done.

### EQUATION 7-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 |                                                  |   |  |  |  |  |

|-----------|--------------------------------------------------|---|--|--|--|--|

| =         | ARG1H:ARG1L • ARG2H:ARG2L                        |   |  |  |  |  |

| =         | (ARG1H • ARG2H • 2 <sup>16</sup> ) +             |   |  |  |  |  |

|           | (ARG1H • ARG2L • 2 <sup>8</sup> ) +              |   |  |  |  |  |

|           | (ARG1L • ARG2H • 2 <sup>8</sup> ) +              |   |  |  |  |  |

|           | (ARG1L • ARG2L) +                                |   |  |  |  |  |

|           | (-1 ● ARG2H<7> ● ARG1H:ARG1L ● 2 <sup>16</sup> ) | + |  |  |  |  |

|           | (-1 ● ARG1H<7> ● ARG2H:ARG2L ● 2 <sup>16</sup> ) |   |  |  |  |  |

|           |                                                  |   |  |  |  |  |

### REGISTER 8-10: IPR2 REGISTER

- n = Value at POR

|         | U-0                                                                                           | U-0         | U-0    | U-0        | R/W-1     | R/W-1      | R/W-1          | R/W-1  |

|---------|-----------------------------------------------------------------------------------------------|-------------|--------|------------|-----------|------------|----------------|--------|

|         | —                                                                                             |             | —      | _          | BCLIP     | LVDIP      | TMR3IP         | CCP2IP |

|         | bit 7                                                                                         |             |        |            |           |            |                | bit 0  |

| bit 7-4 | Unimplem                                                                                      | ented: Read | as '0' |            |           |            |                |        |

| bit 3   | BCLIP: Bus Collision Interrupt Priority bit<br>1 = High priority<br>0 = Low priority          |             |        |            |           |            |                |        |

| bit 2   | LVDIP: Low Voltage Detect Interrupt Priority bit<br>1 = High priority<br>0 = Low priority     |             |        |            |           |            |                |        |

| bit 1   | <b>TMR3IP</b> : TMR3 Overflow Interrupt Priority bit<br>1 = High priority<br>0 = Low priority |             |        |            |           |            |                |        |

| bit 0   | <b>CCP2IP</b> : CCP2 Interrupt Priority bit<br>1 = High priority<br>0 = Low priority          |             |        |            |           |            |                |        |

|         | Legend:                                                                                       |             |        |            |           |            |                |        |

|         | R = Readal                                                                                    | ole bit     | W = Wr | itable bit | U = Unimp | lemented b | oit, read as ' | 0'     |

'0' = Bit is cleared

x = Bit is unknown

'1' = Bit is set

### 8.1.6 INT INTERRUPTS

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxIF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxIE. Flag bit INTxIF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxIE was set prior to going into SLEEP. If the global interrupt enable bit GIE is set, the processor will branch to the interrupt vector following wake-up.

Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits INT1IP (INTCON3 register) and INT2IP (INTCON3 register). There is no priority bit associated with INT0; it is always a high priority interrupt source.

#### 8.1.7 TMR0 INTERRUPT

In 8-bit mode (which is the default), an overflow (0FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit TMR0IF. In 16-bit mode, an overflow (0FFFh  $\rightarrow$  0000h)

in the TMR0H:TMR0L registers will set flag bit TMR0IF. The interrupt can be enabled/disabled by setting/clearing enable bit TMR0IE (INTCON register). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2 register). See Section 10.0 for further details on the Timer0 module.

### 8.1.8 PORTB INTERRUPT-ON-CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON register). The interrupt can be enabled/ disabled by setting/clearing enable bit RBIE (INTCON register). Interrupt priority for PORTB interrupt-onchange is determined by the value contained in the interrupt priority bit RBIP (INTCON2 register).

## 8.2 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (See Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 8-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

#### EXAMPLE 8-1: SAVING STATUS, WREG AND BSR REGISTERS IN RAM

| MOVWF<br>MOVFF<br>MOVFF<br>; | W_TEMP<br>STATUS, STATUS_TEMP<br>BSR, BSR_TEMP | ; W_TEMP is in Low Access bank<br>; STATUS_TEMP located anywhere<br>; BSR located anywhere |

|------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------|

| ; USER                       | ISR CODE                                       |                                                                                            |

| ;                            |                                                |                                                                                            |

| MOVFF                        | BSR_TEMP, BSR                                  | ; Restore BSR                                                                              |

| MOVF                         | W_TEMP, W                                      | ; Restore WREG                                                                             |

| MOVFF                        | STATUS_TEMP, STATUS                            | ; Restore STATUS                                                                           |

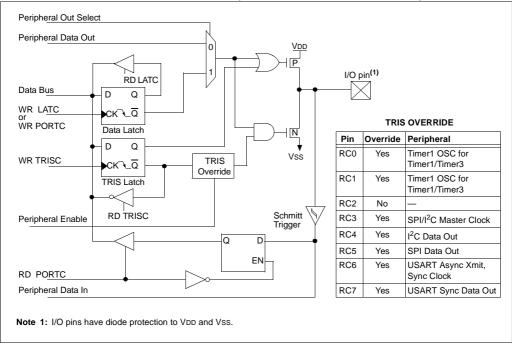

## 9.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATC register, read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 9-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

#### EXAMPLE 9-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0CFh  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC3:RC0 as inputs |

|       |       | ; RC5:RC4 as outputs    |

|       |       | ; RC7:RC6 as inputs     |

|       |       |                         |

## FIGURE 9-6: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

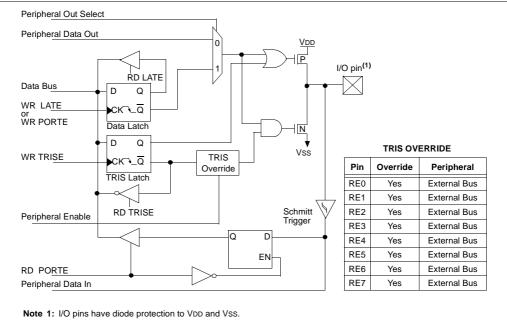

## 9.5 PORTE, TRISE and LATE Registers

PORTE is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATE register reads and writes the latched output value for PORTE.

PORTE is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. PORTE is multiplexed with several peripheral functions (Table 9-9).

PORTE is multiplexed with the system bus and is available only when the system bus is disabled, by setting EBDIS bit in register MEMCON. When operating as the system bus, PORTE is configured as the high order byte of the address/data bus (AD15:AD8), or as the high order address byte (A15:A8), if address and data buses are de-multiplexed.

| Note: | On Power-on Reset, PORTE defaults to |

|-------|--------------------------------------|

|       | the system bus.                      |

### EXAMPLE 9-5: INITIALIZING PORTE

| CLRF  | PORTE | ; | Initialize PORTE by   |

|-------|-------|---|-----------------------|

|       |       | ; | clearing output       |

|       |       | ; | data latches          |

| CLRF  | LATE  | ; | Alternate method      |

|       |       | ; | to clear output       |

|       |       | ; | data latches          |

| MOVLW | 03h   | ; | Value used to         |

|       |       | ; | initialize data       |

|       |       | ; | direction             |

| MOVWF | TRISE | ; | Set RE1:RE0 as inputs |

|       |       | ; | RE7:RE2 as outputs    |

|       |       |   |                       |

## FIGURE 9-9: PORTE BLOCK DIAGRAM IN I/O MODE

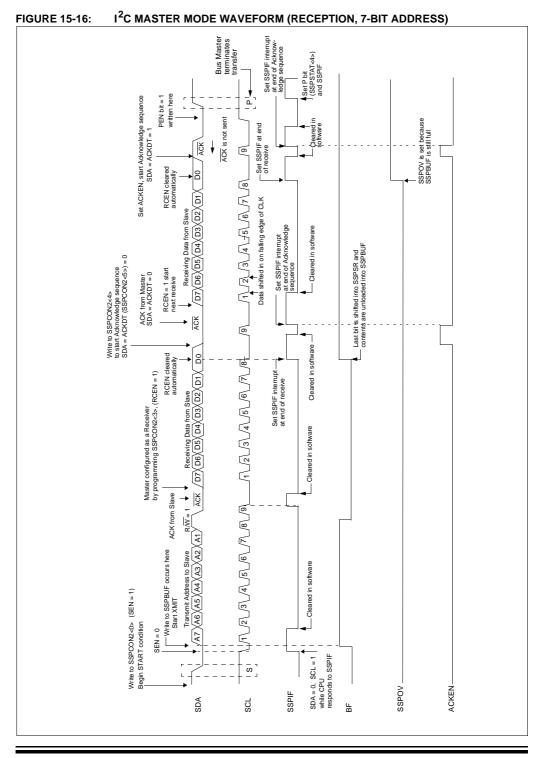

## 15.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

## 15.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface<sup>™</sup> (SPI)

- Inter-Integrated Circuit<sup>™</sup> (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The  $I^2C$  interface supports the following modes in hardware:

- · Master mode

- Multi-Master mode

- · Slave mode

#### REGISTER 16-2: RCSTA REGISTER

| IEK 10-2. | RC31A R                                | LOISTER                                                                   |                              |                 |                |               |              |       |

|-----------|----------------------------------------|---------------------------------------------------------------------------|------------------------------|-----------------|----------------|---------------|--------------|-------|

|           | R/W-0                                  | R/W-0                                                                     | R/W-0                        | R/W-0           | R/W-0          | R-0           | R-0          | R-x   |

|           | SPEN                                   | RX9                                                                       | SREN                         | CREN            | ADDEN          | FERR          | OERR         | RX9D  |

|           | bit 7                                  |                                                                           |                              |                 |                |               |              | bit 0 |

| bit 7     | 1 = Serial p                           | ial Port Enab<br>port enabled (<br>port disabled                          |                              | RX/DT and T     | X/CK pins a    | s serial po   | rt pins)     |       |

| bit 6     | 1 = Selects                            | Receive Enat<br>9-bit reception<br>8-bit reception                        | on                           |                 |                |               |              |       |

| bit 5     | SREN: Sing<br>Asynchrone<br>Don't care | gle Receive E<br>ous mode:                                                | Enable bit                   |                 |                |               |              |       |

|           | 1 = Enable<br>0 = Disable              | <u>us mode - Ma</u><br>s single recei<br>es single rece<br>leared after r | ve<br>ive                    | complete.       |                |               |              |       |

|           | Synchrono<br>Unused in                 | <u>us mode - Sla</u><br>this mode                                         | ave:                         |                 |                |               |              |       |

| bit 4     | Asynchrone<br>1 = Enable               | ntinuous Rece<br>ous mode:<br>s continuous<br>es continuous               | receive                      | bit             |                |               |              |       |

|           |                                        | <u>us mode:</u><br>s continuous<br>es continuous                          |                              | enable bit C    | REN is clea    | red (CREN     | l overrides  | SREN) |

| bit 3     | Asynchrone<br>1 = Enable<br>is set     | ddress Detec<br><u>ous mode 9-b</u><br>s address de                       | <u>tection, enablication</u> | ole interrupt a |                |               |              |       |

| bit 2     | FERR: Fra                              | es address de<br>ming Error bit<br>g error (Can I<br>ning error           |                              |                 |                |               |              | . ,   |

| bit 1     |                                        | errun Error bi<br>n error (Can I<br>rrun error                            |                              | y clearing bit  | CREN)          |               |              |       |

| bit 0     | RX9D: 9th                              | bit of Receive                                                            | ed Data. Car                 | h be Address    | /Data bit or a | a parity bit. |              |       |

|           | Legend:                                |                                                                           |                              |                 |                |               |              |       |

|           | R = Reada                              | ble bit                                                                   | W = Wr                       | itable bit      | U = Unimp      | lemented b    | oit, read as | 0'    |

'1' = Bit is set

- n = Value at POR

'0' = Bit is cleared

x = Bit is unknown

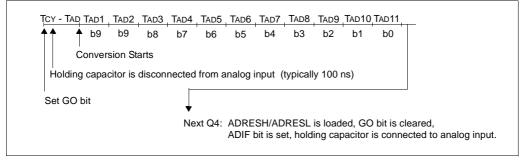

## 17.4 A/D Conversions

Figure 17-3 shows the operation of the A/D converter after the GO bit has been set. Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

## 17.5 Use of the CCP2 Trigger

An A/D conversion can be started by the "special event trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011, and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 (or Timer3) counter.

### FIGURE 17-3: A/D CONVERSION TAD CYCLES

| IOR        | LW             | In                  | clusive           | OR lite       | ral with   | WREG                  |  |  |

|------------|----------------|---------------------|-------------------|---------------|------------|-----------------------|--|--|

| Synt       | tax:           | [/                  | [label] IORLW k   |               |            |                       |  |  |

| Ope        | rands:         | 0                   | $0 \le k \le 255$ |               |            |                       |  |  |

| Ope        | ration:        | (V                  | VREG)             | .OR. k –      | → WREG     |                       |  |  |

| State      | us Affected:   | Ν                   | ,Z                |               |            |                       |  |  |

| Enco       | oding:         |                     | 0000              | 1001          | kkkk       | kkkk                  |  |  |

| Des        | cription:      | w                   | ith the e         |               | teral 'k'. | e OR'ed<br>The result |  |  |

| Wor        | ds:            | 1                   |                   |               |            |                       |  |  |

| Cycl       | es:            | 1                   |                   |               |            |                       |  |  |

| QC         | ycle Activity: |                     |                   |               |            |                       |  |  |

|            | Q1             |                     | Q2                | Q             | 3          | Q4                    |  |  |

|            | Decode         | Read<br>literal 'k' |                   | Proce<br>Data |            | Vrite to<br>WREG      |  |  |

| <u>Exa</u> | mple:          | I                   | ORLW              | 35h           |            |                       |  |  |

|            | Before Instru  | ictio               | n                 |               |            |                       |  |  |

|            | WREG           | =                   | 9Ah               |               |            |                       |  |  |

|            | N<br>Z         | =                   | ?<br>?            |               |            |                       |  |  |

|            | After Instruct |                     | :                 |               |            |                       |  |  |

|            | WREG           |                     | 0BFh              |               |            |                       |  |  |

|            | N              | =                   | 1                 |               |            |                       |  |  |

|            | Z              | =                   | 0                 |               |            |                       |  |  |

|            |                |                     |                   |               |            |                       |  |  |

|            |                |                     |                   |               |            |                       |  |  |

|            |                |                     |                   |               |            |                       |  |  |

| IORWF                                     | Inclusive                                                                                     | OR WREG                                                                                                                                                                                                                                                                                                      | with f               |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:                                   | [ label ]                                                                                     | IORWF f[,                                                                                                                                                                                                                                                                                                    | d [,a]]              |  |  |  |

| Operands:                                 | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                         | 5                                                                                                                                                                                                                                                                                                            |                      |  |  |  |

| Operation:                                | (WREG) .                                                                                      | $OR. (f) \to de$                                                                                                                                                                                                                                                                                             | st                   |  |  |  |

| Status Affected:                          | N,Z                                                                                           |                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Encoding:                                 | 0001                                                                                          | 00da ff                                                                                                                                                                                                                                                                                                      | ff ffff              |  |  |  |

| Description:                              | 'f'. If 'd' is (<br>WREG. If<br>placed bac<br>If 'a' is 0, t<br>selected, c<br>If 'a' is 1, t | Inclusive OR WREG with register<br>'f'. If 'd' is 0, the result is placed in<br>WREG. If 'd' is 1, the result is<br>placed back in register 'f' (default).<br>If 'a' is 0, the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' is 1, the Bank will be selected<br>as per the BSR value. |                      |  |  |  |

| Words:                                    | 1                                                                                             |                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Cycles:                                   | 1                                                                                             |                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Q Cycle Activity:                         |                                                                                               |                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Q1                                        | Q2                                                                                            | Q3                                                                                                                                                                                                                                                                                                           | Q4                   |  |  |  |

| Decode                                    | Read<br>register 'f'                                                                          | Process<br>Data                                                                                                                                                                                                                                                                                              | Write to destination |  |  |  |

| Example: IORWF RESULT, W                  |                                                                                               |                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| Before Instru<br>RESULT<br>WREG<br>N<br>Z | = 13h<br>= 91h<br>= ?<br>= ?                                                                  |                                                                                                                                                                                                                                                                                                              |                      |  |  |  |

| After Instruction |   |     |  |  |  |  |

|-------------------|---|-----|--|--|--|--|

| RESULT            | = | 13h |  |  |  |  |

| WREG              | = | 93h |  |  |  |  |

| N                 | = | 1   |  |  |  |  |

| Z                 | = | 0   |  |  |  |  |

N Z

| NEGF                                                                                                | Negate f                                                       |                                                                                                                                                                                                                                                               |        |                     |  |  |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|--|--|

| Syntax:                                                                                             | [label] N                                                      | IEGF                                                                                                                                                                                                                                                          | f [,a] |                     |  |  |

| Operands:                                                                                           | 0 ≤ f ≤ 25<br>a ∈ [0,1]                                        | 5                                                                                                                                                                                                                                                             |        |                     |  |  |

| Operation:                                                                                          | ( <del>f</del> ) + 1 →                                         | • f                                                                                                                                                                                                                                                           |        |                     |  |  |

| Status Affected:                                                                                    | N,OV, C,                                                       | DC, Z                                                                                                                                                                                                                                                         |        |                     |  |  |

| Encoding:                                                                                           | 0110                                                           | 110a                                                                                                                                                                                                                                                          | ffff   | ffff                |  |  |

| Description:                                                                                        | compleme<br>the data n<br>0, the Acc<br>overriding<br>the Bank | Location 'f' is negated using two's<br>complement. The result is placed in<br>the data memory location 'f'. If 'a' is<br>0, the Access Bank will be selected,<br>overriding the BSR value. If 'a' is 1,<br>the Bank will be selected as per the<br>BSR value. |        |                     |  |  |

| Words:                                                                                              | 1                                                              |                                                                                                                                                                                                                                                               |        |                     |  |  |

| Cycles:                                                                                             | 1                                                              |                                                                                                                                                                                                                                                               |        |                     |  |  |

| Q Cycle Activity:                                                                                   |                                                                |                                                                                                                                                                                                                                                               |        |                     |  |  |

| Q1                                                                                                  | Q2                                                             | Q3                                                                                                                                                                                                                                                            | 5      | Q4                  |  |  |

| Decode                                                                                              | Read<br>register 'f'                                           | Proce<br>Data                                                                                                                                                                                                                                                 |        | Write<br>gister 'f' |  |  |

| Example:                                                                                            | NEGF H                                                         | REG                                                                                                                                                                                                                                                           |        |                     |  |  |

| Before Instru<br>REG<br>N<br>OV<br>C<br>DC<br>Z<br>After Instruct<br>REG<br>N<br>OV<br>C<br>DC<br>Z | = 0011 :<br>= ?<br>= ?<br>= ?<br>= ?<br>= ?<br>ion             | 1010 <b>[3A</b><br>0110 <b>[0C</b>                                                                                                                                                                                                                            |        |                     |  |  |

| NOF       | )             |                               |       |     |    |      |

|-----------|---------------|-------------------------------|-------|-----|----|------|

| Synt      | ax:           | [ label ]                     | NOP   |     |    |      |

| Ope       | rands:        | None                          |       |     |    |      |

| Ope       | ration:       | No opera                      | tion  |     |    |      |

| Statu     | us Affected:  | None                          |       |     |    |      |

| Encoding: |               | 0000                          | 0000  | 000 | 0  | 0000 |

|           |               | 1111                          | XXXX  | XXX | x  | XXXX |

| Dese      | cription:     | No opera                      | tion. |     |    |      |

| Wor       | ds:           | 1                             |       |     |    |      |

| Cycl      | es:           | 1                             |       |     |    |      |

| QC        | cle Activity: |                               |       |     |    |      |

| Q1        |               | Q2                            | Q3    |     | Q4 |      |

|           | Decode        | No                            | No No |     |    | No   |

|           |               | operation operation operation |       |     |    |      |

#### Example:

None.

| SUBWFB            | Subtract<br>Borrow                                                                                                               | Subtract WREG from f with<br>Borrow                                                      |                                                                                          |                                                                                      |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Syntax:           | [label] S                                                                                                                        | [ label ] SUBWFB f [,d [,a]]                                                             |                                                                                          |                                                                                      |  |  |

| Operands:         | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                             |                                                                                          |                                                                                          |                                                                                      |  |  |

| Operation:        | (f) – (WR                                                                                                                        | EG) – (                                                                                  | $\overline{C}) \rightarrow de$                                                           | st                                                                                   |  |  |

| Status Affected:  | N,OV, C,                                                                                                                         | DC, Z                                                                                    |                                                                                          |                                                                                      |  |  |

| Encoding:         | 0101                                                                                                                             | 10da                                                                                     | ffff                                                                                     | ffff                                                                                 |  |  |

| Description:      | Subtract<br>(borrow)<br>plement to<br>result is s<br>the result<br>'f' (defaul<br>Bank will<br>the BSR v<br>will be se<br>value. | from reg<br>method).<br>tored in '<br>is stored<br>t). If 'a' i<br>be seled<br>value. If | ister 'f'<br>If 'd' is<br>WREG<br>back i<br>back i<br>is 0, the<br>cted, ov<br>'a' is 1, | (2's com-<br>0, the<br>If 'd' is 1,<br>n register<br>Access<br>rerriding<br>the Bank |  |  |

| Words:            | 1                                                                                                                                |                                                                                          |                                                                                          |                                                                                      |  |  |

| Cycles:           | 1                                                                                                                                | 1                                                                                        |                                                                                          |                                                                                      |  |  |

| Q Cycle Activity: |                                                                                                                                  |                                                                                          |                                                                                          |                                                                                      |  |  |

| Q1                | Q2                                                                                                                               | Q3                                                                                       |                                                                                          | Q4                                                                                   |  |  |

| Decode            | Read<br>register 'f'                                                                                                             | Proces<br>Data                                                                           |                                                                                          | Write to                                                                             |  |  |

## SUBWFB (Cont.)

| Example 1: SUBWFB REG     |                        |  |  |  |  |

|---------------------------|------------------------|--|--|--|--|

| Before Instruct           | ion                    |  |  |  |  |

| REG =                     | (****=****)            |  |  |  |  |

| WREG =                    | (0000 1101)            |  |  |  |  |

| C =                       | •                      |  |  |  |  |

| After Instructio          |                        |  |  |  |  |

| REG =<br>WREG =           | 0000 (00000 1011)      |  |  |  |  |

| C =                       |                        |  |  |  |  |

| _                         | · 0                    |  |  |  |  |

| N =                       | 0 ; result is positive |  |  |  |  |

| Example 2:                | SUBWFB REG, W          |  |  |  |  |

| Before Instruct           | ion                    |  |  |  |  |

| REG =                     | ()                     |  |  |  |  |

| WREG =                    | (0001 1010)            |  |  |  |  |

| C =                       | -                      |  |  |  |  |

| After Instructio<br>REG = |                        |  |  |  |  |

| WREG =                    |                        |  |  |  |  |

| C =                       | : 1                    |  |  |  |  |

| Z =                       | , recall to Ecre       |  |  |  |  |

| N =                       | • 0                    |  |  |  |  |

| Example 3:                | SUBWFB REG             |  |  |  |  |

| Before Instruct           | ion                    |  |  |  |  |

| REG =                     | ()                     |  |  |  |  |

| WREG =                    | ()                     |  |  |  |  |

| C =                       | ·                      |  |  |  |  |

| After Instructio          |                        |  |  |  |  |

| REG =<br>WREG =           | ······                 |  |  |  |  |

| C =                       | - (                    |  |  |  |  |

| Z =                       |                        |  |  |  |  |

| N =                       | 1 ; result is negative |  |  |  |  |

## 22.3 AC (Timing) Characteristics

#### 22.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                    | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|---------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                       | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                       |           |                                        |

| F                     | Frequency                             | Т         | Time                                   |

| Lowerca               | se letters (pp) and their meanings:   |           |                                        |

| рр                    |                                       |           |                                        |

| сс                    | CCP1                                  | osc       | OSC1                                   |

| ck                    | CLKO                                  | rd        | RD                                     |

| CS                    | CS                                    | rw        | RD or WR                               |

| di                    | SDI                                   | sc        | SCK                                    |

| do                    | SDO                                   | SS        | SS                                     |

| dt                    | Data-in                               | tO        | TOCKI                                  |

| io                    | I/O port                              | t1        | T1CKI                                  |

| mc                    | MCLR                                  | wr        | WR                                     |

| Upperca               | se letters and their meanings:        |           |                                        |

| S                     |                                       |           |                                        |

| F                     | Fall                                  | Р         | Period                                 |

| н                     | High                                  | R         | Rise                                   |

| 1                     | Invalid (Hi-impedance)                | V         | Valid                                  |

| L                     | Low                                   | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                       |           |                                        |

| AA                    | output access                         | High      | High                                   |

| BUF                   | Bus free                              | Low       | Low                                    |

| TCC:ST (              | I <sup>2</sup> C specifications only) | ·         |                                        |

| CC                    |                                       |           |                                        |

| HD                    | Hold                                  | SU        | Setup                                  |

| ST                    |                                       |           |                                        |

| DAT                   | DATA input hold                       | STO       | STOP condition                         |

| STA                   | START condition                       |           |                                        |

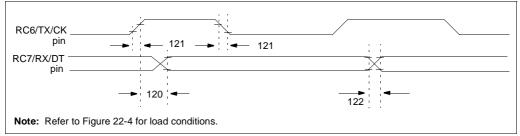

#### TABLE 22-20: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                    | E T                     | Min | Max | Units | Conditions |

|--------------|----------|-----------------------------------|-------------------------|-----|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (Master & Slave)        | n AD                    |     |     |       |            |

|              |          | Clock high to data-out valid      | RIG180601/801           | —   | 40  | ns    |            |

|              |          |                                   | PIC18LC601/801          | —   | 100 | ns    |            |

| 121          | Tckrf    | Clock out rise time and fall time | PIC18 <b>C</b> 601/801  |     | 20  | ns    |            |

|              |          | (Master mode)                     | PIC18LC601/801          |     | 50  | ns    |            |

| 122          | Tdtrf    | Data-out rise time and tall time  | PIC18 <b>C</b> 601/801  | _   | 20  | ns    |            |

|              |          |                                   | PIC18 <b>LC</b> 601/801 | _   | 50  | ns    |            |

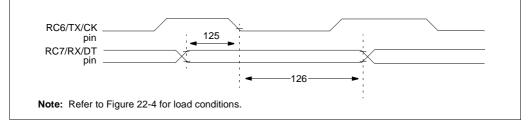

### FIGURE 22-22: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 22-21: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                     | Min | Max | Units | Conditions |

|--------------|----------|------------------------------------|-----|-----|-------|------------|

| 125          | TdtV2ckl | SYNC RCV (Master & Slave)          |     |     |       |            |

|              |          | Data-hold before CK ( ) hold time) | 10  | —   | ns    |            |

| 126          | TckL2dtl | Data-hold after EK (ADT hold time) | 15  | —   | ns    |            |

| PRI          |          |                                    |     |     |       |            |

## APPENDIX E: DEVELOPMENT TOOL VERSION REQUIREMENTS

This lists the minimum requirements (software/ firmware) of the specified development tool to support the devices listed in this data sheet.

| MPLAB <sup>®</sup> IDE: | TBD |

|-------------------------|-----|

|-------------------------|-----|

MPLAB® SIMULATOR: TBD

## MPLAB® ICE 3000:

| PIC18C601/801 Proc<br>Part Number -                                                      | essor Module:<br>TBD                                   |

|------------------------------------------------------------------------------------------|--------------------------------------------------------|

| PIC18C601/801 Devi<br>Socket<br>64-pin TQFP<br>68-pin PLCC<br>80-pin TQFP<br>84-pin PLCC | ce Adapter:<br>Part Number<br>TBD<br>TBD<br>TBD<br>TBD |

| MPLAB <sup>®</sup> ICD:                                                                  | TBD                                                    |

| PRO MATE <sup>®</sup> II:                                                                | TBD                                                    |

| PICSTART <sup>®</sup> Plus:                                                              | TBD                                                    |

| MPASM <sup>™</sup> Assembler:                                                            | TBD                                                    |

| MPLAB <sup>®</sup> C18 C Compiler:                                                       | TBD                                                    |

|                                                                                          |                                                        |

| Note: | Please read all associated README.TXT       |  |  |

|-------|---------------------------------------------|--|--|

|       | files that are supplied with the develop-   |  |  |

|       | ment tools. These "read me" files will dis- |  |  |

|       | cuss product support and any known          |  |  |

|       | limitations.                                |  |  |