Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | H8S/2000                                                                         |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SCI, SSU, UART/USART                             |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 69                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-LQFP                                                                          |

| Supplier Device Package    | 80-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r4f20203rdfd-v0 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2.8 Event Link Interrupt Control Status Register (ELCSR)

| Add         | dress: H'F         | F0528 | 3    |                     |         |                                                                                                          |                                               |              |              |                      |      |

|-------------|--------------------|-------|------|---------------------|---------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------|--------------|----------------------|------|

|             | Bit:               | b7    |      | b6                  | b       | 5                                                                                                        | b4                                            | b3           | b2           | b1                   | b0   |

|             |                    | _     |      | _                   | _       | -                                                                                                        | -                                             | ELIE2        | ELIE1        | ELF2                 | ELF1 |

| Value after | reset:             | 0     |      | 0                   | C       |                                                                                                          | 0                                             | 0            | 0            | 0                    | 0    |

| Bit         | Symb               | ool   | Bi   | t Name              | D       | escr                                                                                                     | iption                                        |              |              |                      | R/W  |

| 7 to 4      | _                  |       | Re   | eserved             | -       | hese<br>e 0.                                                                                             | bits are re                                   | ad as 0. Th  | ne write val | ue should            | —    |

| 3           | ELIE2              | 2     |      | .C interrupt        | 2 0     | ELF                                                                                                      | 2 interrupt                                   | s are disab  | led.         |                      | R/W  |

|             |                    |       | en   | able                | 1       | ELF                                                                                                      | 2 interrupt                                   | s are enab   | led.         |                      |      |

| 2           | ELIE1              | 1     |      | C interrupt         | 1 0     | ELF                                                                                                      | 1 interrupt                                   | s are disab  | led.         |                      | R/W  |

|             |                    |       | en   | able                | 1       | ELF                                                                                                      | 1 interrupt                                   | s are enab   | led.         |                      |      |

| 1           | ELF2 ELC interrupt |       | : [S | [Setting condition] |         |                                                                                                          |                                               |              |              |                      |      |

|             |                    |       | fla  | g 2                 | •       | • When the event selected by ELSR30 occurs* <sup>1</sup>                                                 |                                               |              |              |                      |      |

|             |                    |       |      |                     | [0      | [Clearing conditions]                                                                                    |                                               |              |              |                      |      |

|             |                    |       |      |                     | •       |                                                                                                          | hen 1 is rea<br>itten to the                  |              | bit and the  | en 0 is              |      |

|             |                    |       |      |                     | •       | int                                                                                                      | hen the DT<br>errupt, and<br>0.* <sup>2</sup> |              | •            | ELF2<br>3 of the DTC | 0    |

| 0           | ELF1               |       | FI   | .C interrupt        |         |                                                                                                          |                                               | 1            |              |                      | B/W  |

| 0           |                    |       | fla  | •                   | . [c    | [Setting condition]                                                                                      |                                               |              |              |                      |      |

|             |                    |       |      |                     | •<br>10 | <ul> <li>When the event selected by ELSR12 occurs*<sup>1</sup></li> <li>[Clearing conditions]</li> </ul> |                                               |              |              |                      |      |

|             |                    |       |      |                     | •       | W                                                                                                        | hen 1 is rea<br>itten to the                  | ad from this | bit and the  | en 0 is              |      |

|             |                    |       |      |                     | •       | int                                                                                                      | hen the DT<br>errupt, and<br>0.* <sup>2</sup> |              | -            | LF1<br>3 of the DTC  | 2    |

Notes: 1. For details, see section 12, Event Link Controller.

2. When the DTC is activated by an ELF1 or ELF2 interrupt, the event link source module is not affected.

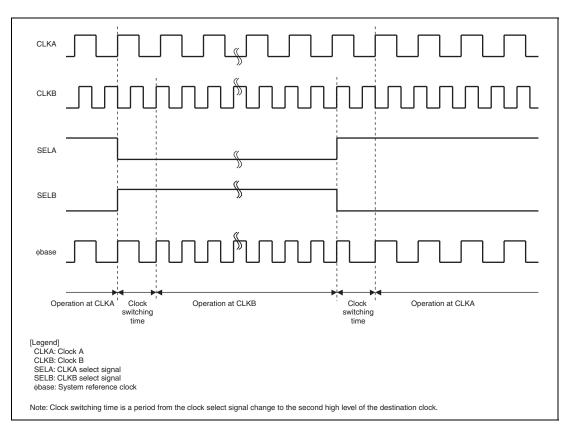

## (2) Switching System Reference Clock Source

Figures 5.8 and 5.9 show clock source switching timing charts for the system reference clock.

# Figure 5.8 Timing of Clock Source Switching (When the switching destination clock source is active)

PDR2 is a register that stores output data for port 2 R/W

the values stored in PDR2 are read. If PDR2 is read R/W while PCR2 bits are cleared to 0, the pin states are

pins. When PCR2 bits are set to 1, the values

read regardless of the value stored in PDR2.

When PDR2 is read while PCR2 bits are set to 1,

5

4

3

2

1

0

#### Port Data Register 2 (PDR2) 10.2.3

Port 25 data

Port 24 data

Port 23 data

Port 22 data

Port 21 data

Port 20 data

| Address. | H'FFFFE1 |

|----------|----------|

| Address. | HEFFEI   |

PDR25

PDR24

PDR23

PDR22

PDR21

PDR20

|         | Bit:         | b7    | b6        | b5        | b4    | b3    | b2    | b1    | b0    |   |

|---------|--------------|-------|-----------|-----------|-------|-------|-------|-------|-------|---|

|         |              | PDR27 | PDR26     | PDR25     | PDR24 | PDR23 | PDR22 | PDR21 | PDR20 |   |

| Value a | after reset: | 0     | 0         | 0         | 0     | 0     | 0     | 0     | 0     |   |

| Bit     | Symbol       | Bit   | Name      | Descrip   | tion  |       |       |       | R/W   |   |

| 7       | PDR27        | Port  | t 27 data | 0: Low le | evel  |       |       |       | R/W   | - |

| 6       | PDR26        | Port  | t 26 data | 1: High I | evel  |       |       |       | R/W   | - |

stored in PDR2 are output.

R/W

R/W

R/W

R/W

## 10.11.3 Port Pull-Up Control Register B (PUCRB)

| Bit:         b7         b6         b5         b4         b3         b2         b1         b0           PUCRB7         PUCRB6         PUCRB5         PUCRB4         PUCRB3         PUCRB2         PUCRB1         PUCRB4           Value after reset:         0         0         0         0         0         0         0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                           |

| Value after reset: 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                           |

| Bit Symbol Bit Name Description R/W                                                                                                                                                                                                                                                                                       |

| 7 PUCRB7 Port B7 pull-up 0: The pull-up MOS of corresponding pin is R/W control disabled.                                                                                                                                                                                                                                 |

| 6 PUCRB6 Port B6 pull-up 1: The pull-up MOS of corresponding pin is R/W control enabled.                                                                                                                                                                                                                                  |

| 5 PUCRB5 Port B5 pull-up control PUCRB is a register that controls the pull-up MOS R/W in bit units of the pins set as the input ports.                                                                                                                                                                                   |

| 4 PUCRB4 Port B4 pull-up R/W control                                                                                                                                                                                                                                                                                      |

| 3 PUCRB3 Port B3 pull-up<br>control R/W                                                                                                                                                                                                                                                                                   |

| 2 PUCRB2 Port B2 pull-up R/W control                                                                                                                                                                                                                                                                                      |

| 1 PUCRB1 Port B1 pull-up<br>control R/W                                                                                                                                                                                                                                                                                   |

| 0 PUCRB0 Port B0 pull-up R/W                                                                                                                                                                                                                                                                                              |

• PUCRB7 bit to PUCRB0 bit (port B7 to B0 pull-up control)

This function is valid only for the pin set as general input, and for the input pin with a function selected by the PMC. However, this setting is invalid for the analog input pin.

#### 10.11.4 Notes on Using Port B

- 1. The PB0 pin is initially set as general I/O pin. If using this pin as the analog input pin for the A/D converter, set the PMRA2 bit in PMRA to 1.

- 2. Pins PB7 and PB6 can be used as analog input pins for the A/D converter or analog output pins for the D/A converter. Do not set these pins as analog input pins and analog output pins at the same time.

## 11.2.8 DTC Vector Register (DTVECR)

| Bit<br>SWDTEb7b6b5b4b3b2b1b0Value after reset:0000000000Bit<br>7SWDDIBit NameDescriptionR/W7SWDTEDTC software<br>activation<br>enable0: Disables the DTC activation by software.<br>Setting this bit to 1 activates DTC.<br>[Clearing conditions]]R/W7SWDTEDTC software<br>activation<br>enable0: Disables the DTC activation by software.<br>Setting this bit to 1 activates DTC.<br>[Clearing conditions]]R/W8When the DISEL bit is 0 and the specified<br>number of data transfers has not ended.<br>• When the DISEL bit is 0 and the specified<br>number of data transfer end interrupt<br>(SWDTEND) request has been sent to the CPU.<br>When the DISEL bit is 1 and data transfer has ended<br>or when the specified number of data transfer has ended<br>or when the specified number of data transfer has ended<br>or when the specified number of DTC activation by software.<br>These bits specify a vector number for DTC<br>activation<br>vector 6 to 0R/W<br>R/W6DTVEC6<br>4DTVEC3<br>activation<br>vector 6 to 0These bits specify a vector number for DTC software<br>activation.<br>The vector address is expressed as H0400 + (vector<br>number × 2). For example, when DTVEC6 to<br>DTVEC6 to<br>DTVEC6 to<br>DTVEC0 = H10, the vector address is H0420.R/W<br>R/W<br>R/W                                                                                                                                                                                                    |       | Address:     | H'FF053D |            |                                         |               |             |              |              |        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|----------|------------|-----------------------------------------|---------------|-------------|--------------|--------------|--------|--|

| Value after reset:0000000000BitSymbolBit NameDescriptionR/W7SWDTEDTC software<br>activation<br>enable0: Disables the DTC activation by software.<br>Setting this bit to 1 activates DTC.<br>[Clearing conditions]]R/W1:Enables the DTC activation by software.<br>Setting this bit to 1 activates DTC.<br>[Clearing conditions]]R/W•When the DISEL bit is 0 and the specified<br>number of data transfers has not ended.<br>••When the DISEL bit after a<br>software-activated data transfer end interrupt<br>(SWDTEND) request has been sent to the CPU.<br>When the DISEL bit is 1 and data transfers has<br>ended, this bit will not be cleared.6DTVEC6<br>activation<br>vector 6 to 0These bits specify a vector number for DTC<br>activation.<br>These bits specify a vector number for DTC software<br>activation.R/W<br>R/W6DTVEC3<br>activation<br>vector 6 to 0These bits specify a vector number for DTC software<br>activation.<br>The vector address is expressed as H'0400 + (vector<br>number × 2). For example, when DTVEC6 to<br>DTVEC0 = H'10, the vector address is H'0420.R/W<br>R/W                                                                                                                                                                                                                                                                                                                                                                                         |       | Bit:         | b7       | b6         | b5                                      | b4            | b3          | b2           | b1           | b0     |  |

| Bit       Symbol       Bit Name       Description       R/W         7       SWDTE       DTC software activation enable       0: Disables the DTC activation by software.       R/W         7       SWDTE       DTC software activation enable       0: Disables the DTC activation by software.       R/W         7       SWDTE       DTC software activation enable       0: Disables the DTC activation by software.       R/W         7       SWDTE       DTC software activation enable       0: Disables the DTC activation by software.       R/W         7       SWDTE       DTC software activation enable       0: Disables the DTC activation by software.       R/W         9       When the DISEL bit is 0 and the specified number of data transfers has not ended.       When 0 is written to the DISEL bit after a software-activated data transfer end interrupt (SWDTEND) request has been sent to the CPU.         When the DISEL bit is 1 and data transfer has ended or when the specified number of data transfers has ended.       These bits specify a vector number for DTC activation by software.         5       DTVEC5       These bits specify a vector number for DTC software activation.       R/W         4       DTVEC3       The vector address is expressed as H'0400 + (vector number x 2). For example, when DTVEC6 to DTVEC6 to DTVEC0 = H'10, the vector address is H'0420.       R/W         1       DTVEC1       When the DISEL is 0. there bits mone |       |              | SWDTE    | DTVEC6     | DTVEC5                                  | DTVEC4        | DTVEC3      | DTVEC2       | DTVEC1       | DTVEC0 |  |

| 7       SWDTE       DTC software activation enable       0: Disables the DTC activation by software.       R/W         1: Enables the DTC activation by software. enable       1: Enables the DTC activation by software.       R/W         1: Enables the DTC activation by software. enable       Setting this bit to 1 activates DTC.       [Clearing conditions]         •       When the DISEL bit is 0 and the specified number of data transfers has not ended.       •       When 0 is written to the DISEL bit after a software-activated data transfer end interrupt (SWDTEND) request has been sent to the CPU.         When the DISEL bit is 1 and data transfer has ended or when the specified number of data transfers has ended, this bit will not be cleared.       R/W         6       DTVEC6       DTC software activation vector 6 to 0       These bits specify a vector number for DTC activation by software.       R/W         3       DTVEC3       The vector address is expressed as H'0400 + (vector number × 2). For example, when DTVEC6 to DTVEC6 to DTVEC0 = H'10, the vector address is H'0420.       R/W         1       DTVEC1       When the SWDTE is 0. there bits an ende written       R/W                                                                                                                                                                                                                                                                | Value | after reset: | 0        | 0          | 0                                       | 0             | 0           | 0            | 0            | 0      |  |

| activation<br>enable       1: Enables the DTC activation by software.<br>Setting this bit to 1 activates DTC.<br>[Clearing conditions]         • When the DISEL bit is 0 and the specified<br>number of data transfers has not ended.         • When 0 is written to the DISEL bit after a<br>software-activated data transfer end interrupt<br>(SWDTEND) request has been sent to the CPU.<br>When the DISEL bit is 1 and data transfer has ended<br>or when the specified number of data transfers has<br>ended, this bit will not be cleared.         6       DTVEC6         5       DTC software<br>activation<br>vector 6 to 0         4       DTVEC3         2       DTVEC2         1       DTVEC2         1       DTVEC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit   | Symbo        | ol Bit   | Name       | Descript                                | ion           |             |              |              | R/W    |  |

| enable       1: Enables the DTC activation by software.         enable       Setting this bit to 1 activates DTC.         [Clearing conditions]       .         When the DISEL bit is 0 and the specified<br>number of data transfers has not ended.         When 0 is written to the DISEL bit after a<br>software-activated data transfer end interrupt<br>(SWDTEND) request has been sent to the CPU.         When the DISEL bit is 1 and data transfer has ended<br>or when the Specified number of data transfers has<br>ended, this bit will not be cleared.         6       DTVEC6         5       DTVEC5         activation       These bits specify a vector number for DTC activation by software.         7       These bits specify a vector number for DTC software<br>activation.         3       DTVEC3         2       DTVEC2         1       DTVEC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7     | SWDT         |          |            | 0: Disable                              | es the DTC    | activation  | by softwar   | e.           | R/W    |  |

| Setting this bit to 1 activates DTC.       [Clearing conditions]         • When the DISEL bit is 0 and the specified number of data transfers has not ended.       • When 0 is written to the DISEL bit after a software-activated data transfer end interrupt (SWDTEND) request has been sent to the CPU.         When the DISEL bit is 1 and data transfer has ended or when the specified number of data transfers has ended, this bit will not be cleared.         6       DTVEC6         5       DTVEC5         4       DTVEC4         3       DTVEC3         2       DTVEC2         1       DTVEC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |              |          |            | 1: Enable                               | s the DTC     | activation  | by software  | e.           |        |  |

| <ul> <li>When the DISEL bit is 0 and the specified number of data transfers has not ended.</li> <li>When 0 is written to the DISEL bit after a software-activated data transfer end interrupt (SWDTEND) request has been sent to the CPU. When the DISEL bit is 1 and data transfer has ended or when the specified number of data transfers has ended, this bit will not be cleared.</li> <li><u>6</u> DTVEC6 DTC software activation vector 6 to 0</li> <li><u>4</u> DTVEC4 DTVEC3 DTVEC2 DTVEC2 I DTVEC2 = DTVEC2 H 10, the vector address is expressed as H'0400 + (vector R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |              | ona      | 510        | Setting th                              | is bit to 1 a | activates D | TC.          |              |        |  |

| number of data transfers has not ended.• When 0 is written to the DISEL bit after a<br>software-activated data transfer end interrupt<br>(SWDTEND) request has been sent to the CPU.When the DISEL bit is 1 and data transfer has ended<br>or when the Specified number of data transfers has<br>ended, this bit will not be cleared.6DTVEC6<br>activation<br>vector 6 to 0These bits specify a vector number for DTC<br>activation<br>vector 6 to 0R/W<br>R/W<br>R/W3DTVEC3<br>2DTVEC2<br>1The vector address is expressed as H'0400 + (vector<br>number × 2). For example, when DTVEC6 to<br>DTVEC0 = H'10, the vector address is H'0420.R/W<br>R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |              |          |            | [Clearing                               | conditions    | ]           |              |              |        |  |

| <ul> <li>When 0 is written to the DISEL bit after a software-activated data transfer end interrupt (SWDTEND) request has been sent to the CPU. When the DISEL bit is 1 and data transfer has ended or when the specified number of data transfers has ended, this bit will not be cleared.</li> <li><u>6</u> DTVEC6</li> <li><u>6</u> DTVEC5</li> <li><u>7</u> DTVEC4</li> <li><u>8</u> DTVEC3</li> <li><u>9</u> DTVEC2</li> <li><u>1</u> DTVEC1</li> <li>When the bit SWDTE is 0, these bits as how written</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |              |          |            | <ul> <li>When</li> </ul>                | ified         |             |              |              |        |  |

| software-activated data transfer end interrupt<br>(SWDTEND) request has been sent to the CPU.<br>When the DISEL bit is 1 and data transfer has ended<br>or when the specified number of data transfers has<br>ended, this bit will not be cleared.6DTVEC6DTC software<br>activation<br>vector 6 to 0R/W5DTVEC5<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |              |          |            | number of data transfers has not ended. |               |             |              |              |        |  |

| (SWDTEND) request has been sent to the CPU.When the DISEL bit is 1 and data transfer has ended<br>or when the specified number of data transfers has<br>ended, this bit will not be cleared.6DTVEC6DTC software<br>activation<br>vector 6 to 0These bits specify a vector number for DTC<br>activation by software.R/W<br>R/W5DTVEC5<br>activation<br>vector 6 to 0These bits specify a vector number for DTC software<br>activation.R/W<br>R/W3DTVEC3<br>2DTVEC2<br>1The vector address is expressed as H'0400 + (vector<br>number × 2). For example, when DTVEC6 to<br>DTVEC0 = H'10, the vector address is H'0420.R/W<br>R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |              |          |            |                                         |               |             |              |              |        |  |

| When the DISEL bit is 1 and data transfer has ended<br>or when the specified number of data transfers has<br>ended, this bit will not be cleared.6DTVEC6DTC software<br>activation<br>vector 6 to 0R/W5DTVEC5activation<br>vector 6 to 0These bits specify a vector number for DTC<br>activation.R/W4DTVEC4These bits specify a vector number for DTC software<br>activation.R/W3DTVEC3The vector address is expressed as H'0400 + (vector<br>number × 2). For example, when DTVEC6 to<br>DTVEC0 = H'10, the vector address is H'0420.R/W1DTVEC1When the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |              |          |            |                                         |               |             |              |              |        |  |

| or when the specified number of data transfers has<br>ended, this bit will not be cleared.6DTVEC6DTC software<br>activation<br>vector 6 to 0R/W5DTVEC5<br>activation<br>vector 6 to 0These bits specify a vector number for DTC<br>activation by software.R/W4DTVEC4<br>3DTVEC3<br>2These bits specify a vector number for DTC software<br>activation.R/W3DTVEC3<br>2The vector address is expressed as H'0400 + (vector<br>number × 2). For example, when DTVEC6 to<br>DTVEC0 = H'10, the vector address is H'0420.R/W1DTVEC1When the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |              |          |            | •                                       | ,             |             |              |              |        |  |

| 5DTVEC5<br>ector 6 to 0activation<br>vector 6 to 0activation by software.R/W4DTVEC4These bits specify a vector number for DTC softwareR/W3DTVEC3The vector address is expressed as H'0400 + (vector<br>number × 2). For example, when DTVEC6 to<br>DTVEC0 = H'10, the vector address is H'0420.R/W1DTVEC1When the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |              |          |            | or when t                               | he specifie   | d number    | of data trar |              |        |  |

| 3       DTVEC3       Vector 6 to 0       These bits specify a vector number for DTC software activation.       R/W         3       DTVEC3       The vector address is expressed as H'0400 + (vector number × 2). For example, when DTVEC6 to DTVEC0 = H'10, the vector address is H'0420.       R/W         1       DTVEC1       When the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6     | DTVE         | C6 DTC   | C software |                                         |               |             | nber for D   | ГС           | R/W    |  |

| 4DTVEC4R/W3DTVEC3These bits specify a vector number for DTC software<br>activation.R/W2DTVEC2The vector address is expressed as H'0400 + (vector<br>number $\times$ 2). For example, when DTVEC6 to<br>DTVEC0 = H'10, the vector address is H'0420.R/W1DTVEC1When the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5     | DTVE         | 5        |            | activation                              | by softwa     | re.         |              |              | R/W    |  |

| 3       DTVEC3         2       DTVEC2         1       DTVEC1    When the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4     | DTVE         |          |            |                                         |               | vector nur  | nber for D   | TC software  | R/W    |  |

| 2DTVEC2number $\times$ 2). For example, when DTVEC6 toR/W1DTVEC1DTVEC0 = H'10, the vector address is H'0420.R/WWhen the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3     | DTVE         | C3       |            |                                         | -             | is express  | ed as H'04(  | 00 + (vector | R/W    |  |

| When the bit SWDTE is 0, these bits can be written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2     | DTVE         | C2       |            | number ×                                | 2). For ex    | ample, whe  | en DTVEC     | 6 to         |        |  |

| 0 DTVEC0 When the bit SWDTE is 0, these bits can be written. R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1     | DTVE         | C1       |            | DTVEC0                                  | = H'10, the   | e vector ad | dress is H'  | 0420.        | R/W    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0     | DTVE         | C0       |            | When the                                | bit SWDT      | E is 0, the | se bits can  | be written.  | R/W    |  |

DTVECR enables or disables DTC activation by software, and sets a vector number for the software activation interrupt.

## 12.2.12 Event-Generation Timer Interval Setting Register B (ELTMSB)

| Address:           | H'FF06BA |     |         |    |    |       |       |    |

|--------------------|----------|-----|---------|----|----|-------|-------|----|

| Bit:               | b7       | b6  | b5      | b4 | b3 | b2    | b1    | b0 |

|                    |          | C3C | LS[3:0] |    |    | C2CLS | [3:0] |    |

| Value after reset: |          | 0   | 0       |    |    |       |       |    |

| Bit    | Symbol      | Bit Name             | Description                                       | R/W |

|--------|-------------|----------------------|---------------------------------------------------|-----|

| 7 to 4 | C3CLS[3:0]* | Channel 3            | 0000: Clock source<br>\$\$\phiELC/1\$\$           | R/W |

|        |             | event-<br>generation | 0001: Clock source<br>\$\$\phiELC/2\$\$           |     |

|        |             | interval select      | 0010: Clock source<br>\$\$\phiELC/4\$             |     |

|        |             |                      | 0011: Clock source                                |     |

|        |             |                      | 0100: Clock source                                |     |

|        |             |                      | 0101: Clock source                                |     |

|        |             |                      | 0110: Clock source                                |     |

|        |             |                      | 0111: Clock source                                |     |

|        |             |                      | 1000: Clock source $\phi$ ELC/256 (initial value) |     |

|        |             |                      | 1001: Clock source                                |     |

|        |             |                      | 1010: Clock source                                |     |

|        |             |                      | 1011: Clock source                                |     |

|        |             |                      | 1100: Clock source                                |     |

|        |             |                      | 1101: Clock source                                |     |

|        |             |                      | 1110: Clock source                                |     |

|        |             |                      | 1111: Clock source                                |     |

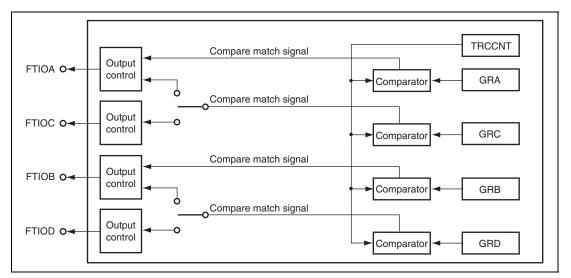

#### 15.3.6 Function of Changing Output Pins for GR

With the settings of bits IOC3 and IOD3 in TRCIOR1, pins for outputs of compare match signals for GRC and GRD can be changed from the FTIOC and FTIOD pins to the FTIOA and FTIOB pins. This means that the compare match A signal with the compare match C signal can be output on the FTIOA pin. The compare match B with the compare match D signal can be output on the FTIOB pin. Figure 15.24 is a block diagram of this function. Channel 0 and channel 1 can be set independently.

Figure 15.24 Block Diagram of Output Pins for GR

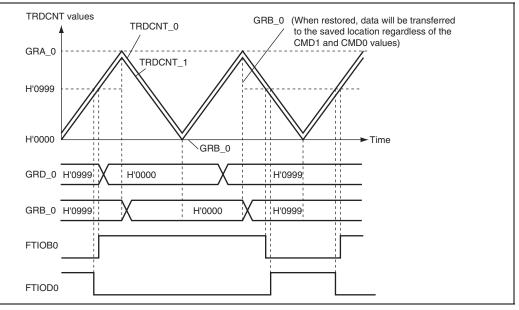

Figure 16.49 Buffer Operation (4) (Buffer Operation in Complementary PWM Mode CMD1 =1, CMD0 = 0)

## 16.3.14 Operation through an Event Link

Using the event link controller (ELC), timer RD unit 0 can be made to operate in the following ways in relation to events occurring in other modules. Each channel 0 and 1 can be specified independently.

### (1) Staring Counter Operation

The start of counting operations by timer RD can be selected by ELOPA and ELOPB of the ELC. When the event specified by ELSR3 and ELSR4 occur, the STR[1:0] bits in TRDSTR are set to 1, which stars counting by timer RD. However, if the specified event occurs when the STR bit has already been set to 1, the event is not effective.

#### (2) Counting Event

The counting of events by timer RD can be selected by ELOPA and ELOPB of the ELC. When the event specified in ELSR3 and ELSR4 occurs, event counter operation proceeds with that event as the source to drive counting, regardless of the setting of the TPSC[2:0] bits in TRDCR and the STR1, STR0 bits in TRDSTR. When the value of the counter is read, the value read out is the actual number of input events.

#### (3) Input Capture

Input capture operation of timer RD can be selected by ELOPA and ELOPB of the ELC. When the event specified in ELSR3 and ELSR4 occurs, GRD captures the value of TRDCNT. When input capture operation initiated by an event link is in use, set the IOD[3:0] bits = b'1101 in TRDIORC of timer RD, set the STR bit in TRDSTR to 1, and then start the counter. Since input on the FTIOD pin becomes valid at the same time, fix the input to the FTIOD pin or take other measures such as not allocating the FTIOD pin to the port in the PMC, etc.

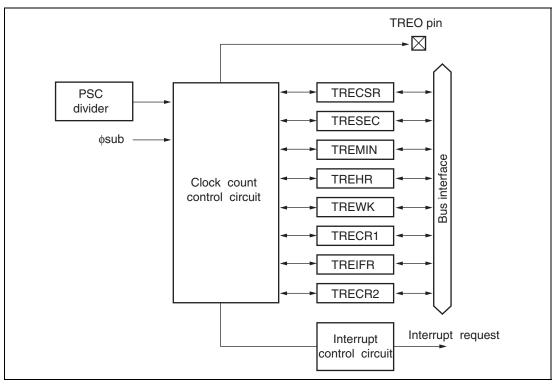

Figure 17.1 Block Diagram of Timer RE

Table 17.1 shows the timer RE input/output pin.

#### Table 17.1 Pin Configuration

| Pin Name | I/O    | Function                      |

|----------|--------|-------------------------------|

| TREO     | Output | Clock or compare-match output |

## 18.3.5 **Operation through an Event Link**

Using the event link controller (ELC), timer RG can be made to operate in the following ways in relation to events occurring in other modules.

## (1) Staring Counter Operation

The start of counting operations by timer RG can be selected by ELOPC of the ELC. When the event specified by ELSR8 occur, the STR bit in TRGMDR is set to 1, which starts counting by timer RG. However, if the specified event occurs when the STR bit has already been set to 1, the event is not effective.

## (2) Counting Event

The counting of events by timer RG can be selected by ELOPC of the ELC. When the event specified in ELSR8 occurs, event counter operation proceeds with that event as the source to drive counting, regardless of the setting of TPSC[2:0] bits in TRGCR and the STR bit in TRGMDR. When the value of the counter is read, the value read out is the actual number of input events.

## (3) Input Capture

Input capture operation of timer RG can be selected by ELOPC of the ELC. When the event specified in ELSR8 occurs, GRB captures the value of TRGCNT. When input capture operation initiated by an event link is in use, set IOB[2:0] = b'101 in the TRGIOR register of timer RG, set the STR bit in TRGMDR, and then start the counter. Since input on the TGIOB pin becomes valid at the same time, fix the input to the TGIOB pin or take other measures such as not allocating the TGIOB pin to the port in the PMC, etc.

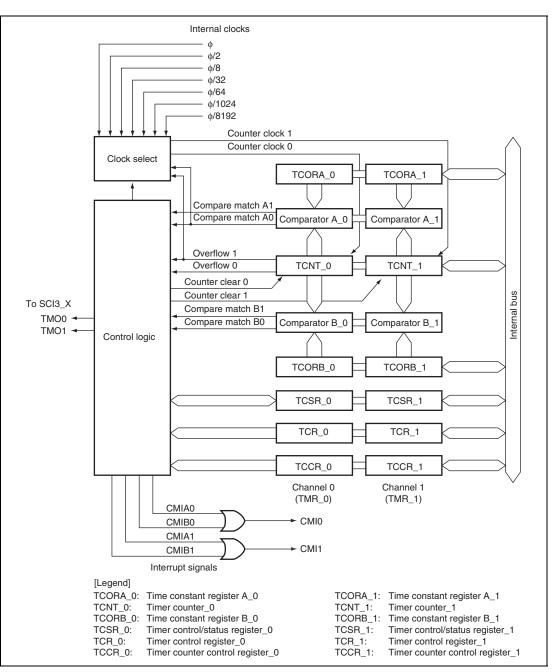

Figure 19.1 Block Diagram of 8-Bit Timer Module

## 21.2.6 Serial Control Register 3 (SCR3)

|         | Bit:         | b7        | b6                   | b5                                                             | b4                           | b3                                                                      | b2                                                    | b1       | b0  |

|---------|--------------|-----------|----------------------|----------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------|----------|-----|

|         | [            | TIE       | RIE                  | TE                                                             | RE                           | MPIE                                                                    | TEIE                                                  | CKE[1:0] |     |

| Value a | after reset: | 0         | 0                    | 0                                                              | 0                            | 0                                                                       | 0                                                     | 0        | 0   |

| Bit     | Symbo        | I Bit Nai | me                   | Descripti                                                      | ion                          |                                                                         |                                                       |          | R/W |

| 7       | TIE          | Transm    |                      | 0: The TX                                                      | (I interrupt                 | request is                                                              | disabled.                                             |          | R/W |

|         |              | interrup  | ot enable            | 1: The TX                                                      | (I interrupt                 | request is                                                              | enabled.                                              |          |     |

| 6       | RIE          |           |                      | 0: RXI an                                                      | d ERI inter                  | rupt reque                                                              | sts are disa                                          | abled.   | R/W |

|         |              | enable    |                      | 1: RXI an                                                      | d ERI inter                  | rupt reque                                                              | sts are ena                                           | bled.    |     |

| 5       | TE           | Transm    | nit enable           | 0: Transn                                                      | 0: Transmission is disabled. |                                                                         |                                                       |          |     |

|         |              |           |                      | 1: Transn                                                      | nission is e                 | nabled.                                                                 |                                                       |          |     |

| 4       | RE           | Receiv    | e enable             | 0: Recept                                                      | tion is disat                | oled.                                                                   |                                                       |          | R/W |

|         |              |           |                      | 1: Recept                                                      | ion is enab                  | oled.                                                                   |                                                       |          |     |

| 3       | MPIE         |           | ocessor<br>ot enable | •                                                              | only when<br>nous mode       |                                                                         | in SMR is                                             | 1 in     | R/W |

|         |              |           |                      | multiproce<br>RDRF, FR<br>On receiv<br>this bit is<br>resumed. | ring data in<br>automatica   | 0 is skippe<br>ER status f<br>which the<br>Illy cleared<br>s, see secti | ed, and set<br>lags in SSI<br>multiproce<br>and norma |          |     |

| 2       | TEIE         | Transm    |                      | 0: The TE                                                      | I interrupt                  | request is                                                              | disabled.                                             |          | R/W |

|         |              | interrup  | ot enable            | 1: The TE                                                      | El interrupt                 | request is                                                              | enabled.                                              |          |     |

Address: H'FF0552, H'FF055A, H'FF0562

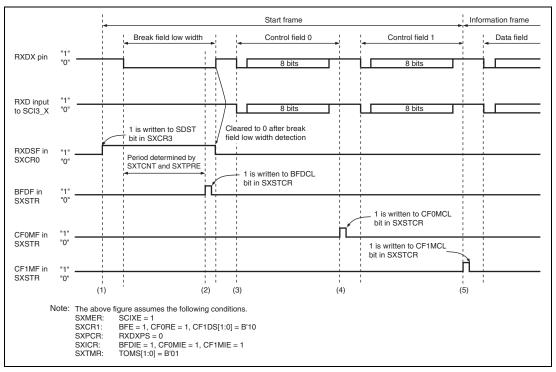

- 4. When the received control field 0 data agrees with the data set to SXCF0DR, the CF0MF bit in SXSTR is set to 1. Here, if the CF0MIE bit in SXICR is 1, an SCIX1 interrupt is generated. Then the control field 1 data begins to be received using the SCI3\_X. When the received control field 0 data does not agree with the data set to SXCF0DR, the SCIX returns to the state prior to break field low width detection.

- 5. When the received control field 1 data agrees with the data set to SXPCF1DR or SXSCF1DR, the CF1MF bit in SXSTR is set to 1. Here, if the CF1MIE bit in SXICR is 1, an SCIX1 interrupt is generated. Then the information frame is transmitted and received using the SCI3\_X. When the received control field 1 data does not agree with the data set to SXPCF1DR or SXSCF1DR, the SCIX returns to the state prior to break field low width detection.

The break field and control field 0 data should be omitted according to the start frame configuration.

Figure 22.8 Start Frame Reception Example

## (3) Receive Operation

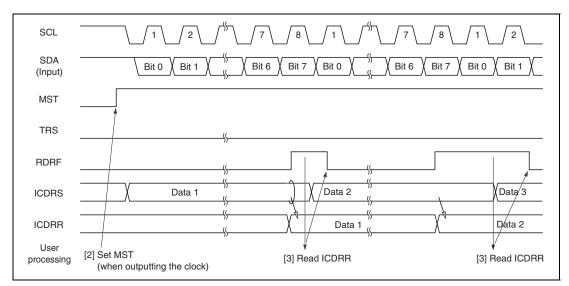

In receive mode, data is latched at the rise of the transfer clock. The transfer clock is output when MST in ICCR1 is 1 and is input when MST is 0. For receive mode operation timing, see figure 24.15. The reception procedure and operations in receive mode are described below.

- 1. Set the ICE bit in ICCR1 to 1. Set the MST and CKS[3:0] bits in ICCR1 to 1 (Initial setting).

- 2. When the transfer clock is output, set MST to 1 to start outputting the receive clock.

- 3. When the receive operation is completed, data is transferred from ICDRS to ICDRR and RDRF in ICSR is set. When MST = 1, the next byte can be received, so the clock is continually output. The continuous reception is performed by reading ICDRR every time RDRF is set. When the 8th clock is risen while RDRF is set to 1, the overrun is detected and AL/OVE in ICSR is set. At this time, the previous reception data is retained in ICDRR.

- 4. To stop receiving when MST = 1, read ICDRR after setting RCVD in ICCR1 to 1. Then, SCL is fixed high after receiving the next byte data.

Figure 24.15 Receive Mode Operation Timing

## Section 25 Synchronous Serial Communication Unit (SSU)

Note: In this section, the synchronous serial communication unit is abbreviated as SSU for convenience.

The synchronous serial communication unit (SSU) can handle clocked synchronous serial data communication.

Figure 25.1 shows a block diagram of the SSU.

Either the SSU or IIC2 incorporated in this LSI can be used at a time. Accordingly, when the SSU function is used, the IIC2 function is not available.

## 25.1 Features

- Can be operated in clocked synchronous communication mode or four-line bus communication mode (including bidirectional communication mode)

- Can be operated as a master or a slave device

- Choice of seven internal clocks (φ/256, φ/128, φ/64, φ/32, φ/16, φ/8, φ/4) and an external clock as a clock source

- Clock polarity and phase of SSCK can be selected

- Choice of data transfer direction (MSB-first or LSB-first)

- Receive error detection: overrun error

- Multimaster error detection: conflict error

- Five interrupt sources: transmit-end, transmit-data-empty, receive-data-full, overrun error, and conflict error. The DTC can be activated by the transmit-data-empty and receive-data-full interrupts.

- The transmitter and receiver with buffer structure allow continuous transmission and reception of serial data.

## 26.3.2 Slave Mode

Figure 26.5 shows the example of hardware LIN interface operation for receiving the header field in slave mode. Figures 26.6 to 26.8 show the flowcharts for header field reception.

The hardware LIN interface operates as follows for header field reception.

- 1. When 1 is written to the LSTART bit in LINCR register of the hardware LIN interface, Sync Break detection is enabled.

- 2. When a low level input is longer than the time set in timer RA, it is detected as Sync Break, thus setting the SBDCT flag in the LINST register to 1. In this case, if the SBIE bit in the LINCR register is set to 1, the timer RA/HW-LIN interrupt occurs. The hardware LIN interface then measures the Sync Field.

- 3. The hardware LIN interface receives the Sync Field (H'55). During reception, the hardware LIN interface measures the time from the start bit through bit 6. Here, the Sync Field input to the SCI3 RXD can be either enabled or disabled depending on the SBE bit setting in the LINCR register.

- 4. Completion of Sync Field measurement sets the SFDCT flag in the LINST register to 1. In this case, if the SFIE bit in the LINCR register is 1, the timer RA/HW-LIN interrupt occurs.

- 5. After completing Sync Field measurement, the hardware LIN interface calculates the transfer rate from the timer RA count value and sets the rate in SCI3\_1, and also updates the TRAPRE and TRATR registers in timer RA. Then the hardware LIN interface receives the ID field using SCI3\_1.

- 6. After completing ID field reception, the hardware LIN interface performs response field communications.

| Register Name                                  | Abbreviation | Number<br>of Bits | Address  | Module              | Data Bus<br>Width        | Number of<br>Access<br>States |

|------------------------------------------------|--------------|-------------------|----------|---------------------|--------------------------|-------------------------------|

| High-speed OCO trimming data register 3        | HOTRMDR3     | 8                 | H'FF062E | Clock<br>oscillator | 8                        | 2                             |

| High-speed OCO trimming data register 4        | HOTRMDR4     | 8                 | H'FF062F | _                   | 8                        | 2                             |

| 32-MHz high-speed OCO trimming data register 1 | HO32TRMDR1   | 8                 | H'FF063A | _                   | 8                        | 2                             |

| 32-MHz high-speed OCO trimming data register 2 | HO32TRMDR2   | 8                 | H'FF063B | -                   | 8                        | 2                             |

| 32-MHz high-speed OCO trimming data register 3 | HO32TRMDR3   | 8                 | H'FF063C | _                   | 8                        | 2                             |

| 32-MHz high-speed OCO trimming data register 4 | HO32TRMDR4   | 8                 | H'FF063D | _                   | 8                        | 2                             |

| Timer RG counter                               | TRGCNT       | 16                | H'FF0640 | Timer RG            | 16* <sup>4</sup>         | 2                             |

| General register A                             | GRA          | 16                | H'FF0642 | Timer RG            | <b>16</b> * <sup>4</sup> | 2                             |

| General register B                             | GRB          | 16                | H'FF0644 | Timer RG            | 16* <sup>4</sup>         | 2                             |

| Timer RG mode register                         | TRGMDR       | 8                 | H'FF0646 | Timer RG            | 8                        | 2                             |

| Timer RG counter control register              | TRGCNTCR     | 8                 | H'FF0647 | Timer RG            | 8                        | 2                             |

| Timer RG control register                      | TRGCR        | 8                 | H'FF0648 | Timer RG            | 8                        | 2                             |

| Timer RG I/O control register                  | TRGIOR       | 8                 | H'FF0649 | Timer RG            | 8                        | 2                             |

| Timer RG status register                       | TRGSR        | 8                 | H'FF064A | Timer RG            | 8                        | 2                             |

| Timer RG interrupt enable register             | TRGIER       | 8                 | H'FF064B | Timer RG            | 8                        | 2                             |

| GRA buffer register                            | BRA          | 16                | H'FF064C | Timer RG            | 16* <sup>4</sup>         | 2                             |

| GRB buffer register                            | BRB          | 16                | H'FF064E | Timer RG            | 16* <sup>4</sup>         | 2                             |

| Flash memory control register 1                | FLMCR1       | 8                 | H'FF0660 | FLASH               | 8                        | 2                             |

| Flash memory control register 2                | FLMCR2       | 8                 | H'FF0661 | FLASH               | 8                        | 2                             |

| Flash memory data flash protect register       | DFPR         | 8                 | H'FF0662 | FLASH               | 8                        | 2                             |

| Flash memory status register                   | FLMSTR       | 8                 | H'FF0663 | FLASH               | 8                        | 2                             |

| Event link setting register 0                  | ELSR0        | 8                 | H'FF0680 | ELC                 | 8                        | 2                             |

| Event link setting register 1                  | ELSR1        | 8                 | H'FF0681 | ELC                 | 8                        | 2                             |

| Event link setting register 2*7                | ELSR2        | 8                 | H'FF0682 | ELC                 | 8                        | 2                             |

| Event link setting register 3                  | ELSR3        | 8                 | H'FF0683 | ELC                 | 8                        | 2                             |

| Event link setting register 4                  | ELSR4        | 8                 | H'FF0684 | ELC                 | 8                        | 2                             |

| ApplicableTest ConditionMin.Typ.Max.UnitInput/output $  I_{L}  $ NMI, IRQ0 to IRQ7<br>TRAIO,TRGB,<br>Urrent $V_{IN} = 0.5 V to$ 1.0 $\mu A$ Input/output $  I_{L}  $ NMI, IRQ0 to IRQ7<br>TRAIO,TRGB,<br>FTCI, TRGC, FTIOA $V_{IN} = 0.5 V to$ 1.0 $\mu A$ Input/outputFTGI, TRGC, FTIOAFTIOE, FTIOC,<br>FTIOD, TRCOI,<br>FTIOD, TRCOI,<br>FTIOA, FTIOB0,<br>FTIOC1, FTIOD0,<br>FTIOC1, FTIOD11.0 $\mu A$ Imput/outputFTGI, TRGC, FTIOAFTIOE, FTIOC2,<br>FTIOA, FTIOB0,<br>FTIOC1, FTIOD11.0 $\mu A$ Imput/outputFTIOC, FTIOD0, FTIOA0, FTIOB0,<br>FTIOC1, FTIOD1FTIOC1, FTIOD11.0 $\mu A$ Imput/outputFTIOC, FTIOD0, FTIOA0, FTIOA0, FTIOA1, FTIOB1,<br>FTIOC2, FTIOD2FTIOA2, FTIOA2 </th <th></th> <th></th> |                       |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|

| Input output       TRAIO,TRGB,       (V <sub>oc</sub> - 0.5 V io)       Ito µX         leakage       TRAIO,TRGB,       (V <sub>oc</sub> - 0.5 V)         current       FTCI, TRGC, FTIOA         FTIOB, FTIOC,       FTIOD, TRCOI,         FTIOD, TRCOI,       FTIOD, TRIOBO,         FTIOO, FTIODO,       FTIOC, FTIODI,         FTIOC, FTIODI,       FTIOC1, FTIODI,         FTIOC1, FTIODI,       FTIOC2,         FTIO2, FTIOC2,       FTIO2         FTIO2, FTIO2       FTIOA3, FTIOB3,         FTIOC3, FTIOD3       TRDOI_T, TCLKA         TGIOB, SCK3       SCK3_2, SCK3_X         ADTRG1, ADTRG2       RXD, RXD_2,         RXD, RXD_2,       RXD_X, RXDX,         SCL, SDA       SCL, SDA                | tem                   | Notes |

| SSI, SSO, OSC1,         RES         P10 to P17         P20 to P27         P30 to P37         P40 to P47         P50 to P57         P60 to P67         P72 to P77         P80 to P87         P90 to P97         PA0 to PA7         PB0 to P87         P90 to P87         P90 to P87                                                                                                                                                                                                                                                                                                                                                                                                                             | nput/output<br>eakage | Notes |