Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                                |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3665axi-198t |

Table 4-1. Arithmetic Instructions

| Mnemonic      | Description                                          | Bytes | Cycles |

|---------------|------------------------------------------------------|-------|--------|

| ADD A,Rn      | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct  | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri     | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data   | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn     | Add register to accumulator with carry               | 1     | 1      |

| ADDC A,Direct | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri    | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data  | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn     | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A,Direct | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri    | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data  | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A         | Increment accumulator                                | 1     | 1      |

| INC Rn        | Increment register                                   | 1     | 2      |

| INC Direct    | Increment direct byte                                | 2     | 3      |

| INC @Ri       | Increment indirect RAM                               | 1     | 3      |

| DEC A         | Decrement accumulator                                | 1     | 1      |

| DEC Rn        | Decrement register                                   | 1     | 2      |

| DEC Direct    | Decrement direct byte                                | 2     | 3      |

| DEC @Ri       | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR      | Increment data pointer                               | 1     | 1      |

| MUL           | Multiply accumulator and B                           | 1     | 2      |

| DIV           | Divide accumulator by B                              | 1     | 6      |

| DAA           | Decimal adjust accumulator                           | 1     | 3      |

# 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 on page 15 shows the list of logical instructions and their description.

**Table 4-2. Logical Instructions**

|     | Mnemonic      | Description                       | Bytes | Cycles |

|-----|---------------|-----------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator       | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator    | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator   | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte    | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator        | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator     | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator    | 1     | 2      |

Document Number: 001-53413 Rev. \*Y Page 15 of 137

Table 4-3. Data Transfer Instructions (continued)

| Mnemonic          | Description                                            | Bytes | Cycles |

|-------------------|--------------------------------------------------------|-------|--------|

| MOV @Ri, Direct   | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV @Ri, #data    | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV DPTR, #data16 | Load data pointer with 16 bit constant                 | 3     | 3      |

| MOVC A, @A+DPTR   | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC A, @A + PC   | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX A,@Ri        | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX A, @DPTR     | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX @Ri, A       | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX @DPTR, A     | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH Direct       | Push direct byte onto stack                            | 2     | 3      |

| POP Direct        | Pop direct byte from stack                             | 2     | 2      |

| XCH A, Rn         | Exchange register with accumulator                     | 1     | 2      |

| XCH A, Direct     | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH A, @Ri        | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD A, @Ri       | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

Table 4-4. Boolean Instructions

| Mnemonic     | Description                             | Bytes | Cycles |

|--------------|-----------------------------------------|-------|--------|

| CLR C        | Clear carry                             | 1     | 1      |

| CLR bit      | Clear direct bit                        | 2     | 3      |

| SETB C       | Set carry                               | 1     | 1      |

| SETB bit     | Set direct bit                          | 2     | 3      |

| CPL C        | Complement carry                        | 1     | 1      |

| CPL bit      | Complement direct bit                   | 2     | 3      |

| ANL C, bit   | AND direct bit to carry                 | 2     | 2      |

| ANL C, /bit  | AND complement of direct bit to carry   | 2     | 2      |

| ORL C, bit   | OR direct bit to carry                  | 2     | 2      |

| ORL C, /bit  | OR complement of direct bit to carry    | 2     | 2      |

| MOV C, bit   | Move direct bit to carry                | 2     | 2      |

| MOV bit, C   | Move carry to direct bit                | 2     | 3      |

| JC rel       | Jump if carry is set                    | 2     | 3      |

| JNC rel      | Jump if no carry is set                 | 2     | 3      |

| JB bit, rel  | Jump if direct bit is set               | 3     | 5      |

| JNB bit, rel | Jump if direct bit is not set           | 3     | 5      |

| JBC bit, rel | Jump if direct bit is set and clear bit | 3     | 5      |

Document Number: 001-53413 Rev. \*Y Page 17 of 137

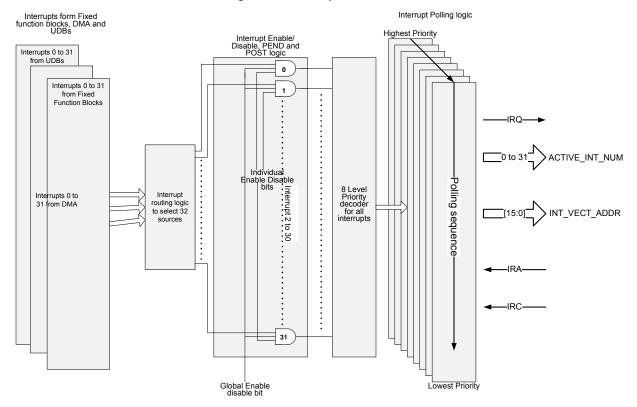

Figure 4-3. Interrupt Structure

Table 4-8. Interrupt Vector Table

| #  | Fixed Function         | DMA               | UDB          |

|----|------------------------|-------------------|--------------|

| 0  | LVD                    | phub_termout0[0]  | udb_intr[0]  |

| 1  | Cache/ECC              | phub_termout0[1]  | udb_intr[1]  |

| 2  | Reserved               | phub_termout0[2]  | udb_intr[2]  |

| 3  | Sleep (Pwr Mgr)        | phub_termout0[3]  | udb_intr[3]  |

| 4  | PICU[0]                | phub_termout0[4]  | udb_intr[4]  |

| 5  | PICU[1]                | phub_termout0[5]  | udb_intr[5]  |

| 6  | PICU[2]                | phub_termout0[6]  | udb_intr[6]  |

| 7  | PICU[3]                | phub_termout0[7]  | udb_intr[7]  |

| 8  | PICU[4]                | phub_termout0[8]  | udb_intr[8]  |

| 9  | PICU[5]                | phub_termout0[9]  | udb_intr[9]  |

| 10 | PICU[6]                | phub_termout0[10] | udb_intr[10] |

| 11 | PICU[12]               | phub_termout0[11] | udb_intr[11] |

| 12 | PICU[15]               | phub_termout0[12] | udb_intr[12] |

| 13 | Comparators Combined   | phub_termout0[13] | udb_intr[13] |

| 14 | Switched Caps Combined | phub_termout0[14] | udb_intr[14] |

| 15 | I <sup>2</sup> C       | phub_termout0[15] | udb_intr[15] |

| 16 | CAN                    | phub_termout1[0]  | udb_intr[16] |

| 17 | Timer/Counter0         | phub_termout1[1]  | udb_intr[17] |

| 18 | Timer/Counter1         | phub_termout1[2]  | udb_intr[18] |

| 19 | Timer/Counter2         | phub_termout1[3]  | udb_intr[19] |

| 20 | Timer/Counter3         | phub_termout1[4]  | udb_intr[20] |

| 21 | USB SOF Int            | phub_termout1[5]  | udb_intr[21] |

| 22 | USB Arb Int            | phub_termout1[6]  | udb_intr[22] |

Document Number: 001-53413 Rev. \*Y Page 22 of 137

### 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C36 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The factory default values of all EEPROM bytes are 0.

Because the EEPROM is mapped to the 8051 xdata space, the CPU cannot execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see Section 6.3.1) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. In addition, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

## 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2. Device Configuration NVL Register Map

| Register Address | 7             | 6         | 5                         | 4       | 3            | 2        | 1            | 0        |

|------------------|---------------|-----------|---------------------------|---------|--------------|----------|--------------|----------|

| 0x00             | PRT3RD        | DM[1:0]   | PRT2RDM[1:0] PRT1RDM[1:0] |         | DM[1:0]      | PRT0     | RDM[1:0]     |          |

| 0x01             | PRT12RDM[1:0] |           | PRT6R                     | DM[1:0] | PRT5RDM[1:0] |          | PRT4RDM[1:0] |          |

| 0x02             | XRESMEN       | DBGEN     |                           |         |              | PRT15    | SRDM[1:0]    |          |

| 0x03             |               | DIG_PHS_I | _DLY[3:0]                 |         | ECCEN        | DPS[1:0] |              | CFGSPEED |

The details for individual fields and their factory default settings are shown in Table 5-3.

Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                  | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port. See "Reset Configuration" on page 43. All pins of the port are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. See "Pin Descriptions" on page 12, XRES description.                   | 0 (default for 68-pin 72-pin, and 100-pin parts) - GPIO 1 (default for 48-pin parts) - external reset                         |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                 | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| CFGSPEED         | Controls the speed of the IMO-based clock during the device boot process, for faster boot or low-power operation                             | 0 (default) - 12 MHz IMO<br>1 - 48 MHz IMO                                                                                    |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug port. See "Programming, Debug Interfaces, Resources" on page 65.                            | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 23.             | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                       | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see "Nonvolatile Latches (NVL))" on page 110.

Document Number: 001-53413 Rev. \*Y Page 24 of 137

# 6. System Integration

## 6.1 Clocking System

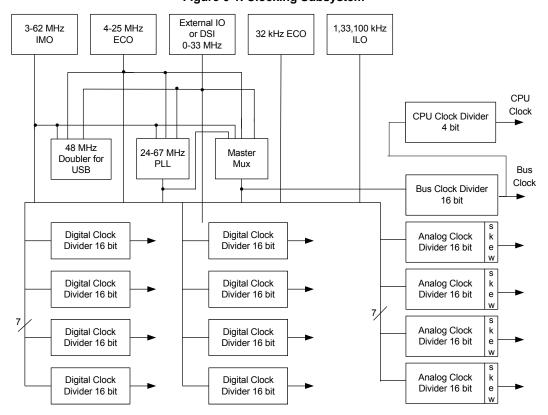

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 66 MHz clock, accurate to ±1% over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC.

Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 62-MHz IMO, ±1% at 3 MHz

- 4- to 25-MHz external crystal oscillator (MHzECO)

- □ Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 30.

- DSI signal from an external I/O pin or other logic

- □ 24- to 67-MHz fractional PLL sourced from IMO, MHzECO, or DSI

- □ 1-kHz, 33-kHz, 100-kHz ILO for WDT and sleep timer □ 32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB. (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

Figure 6-1. Clocking Subsystem

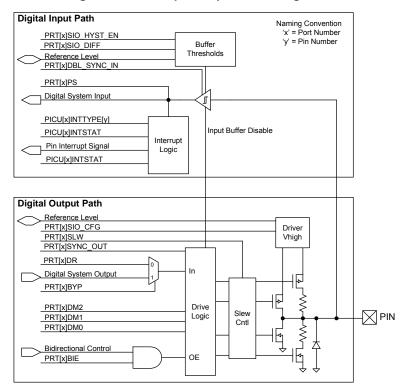

Figure 6-10. SIO Input/Output Block Diagram

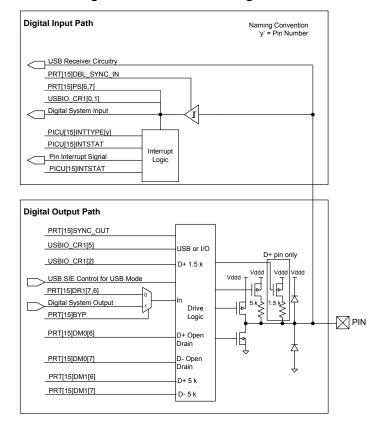

Figure 6-11. USBIO Block Diagram

# 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D- pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8 µs (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see *Section 5.5*), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

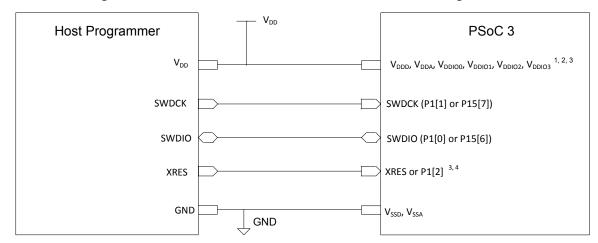

Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

- The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDIO1</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDIO1</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDIO1</sub>. So V<sub>DDIO1</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub> for Port 1 SWD programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDIO2</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

- <sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

Document Number: 001-53413 Rev. \*Y Page 67 of 137

### 9.3 Debug Features

Using the JTAG or SWD interface, the CY8C36 supports the following debug features:

- Halt and single-step the CPU

- View and change CPU and peripheral registers, and RAM addresses

- Eight program address breakpoints

- One memory access breakpoint—break on reading or writing any memory address and data value

- Break on a sequence of breakpoints (non recursive)

- Debugging at the full speed of the CPU

- Compatible with PSoC Creator and MiniProg3 programmer and debugger

- Standard JTAG programming and debugging interfaces make CY8C36 compatible with other popular third-party tools (for example, ARM / Keil)

### 9.4 Trace Features

The CY8C36 supports the following trace features when using JTAG or SWD:

- Trace the 8051 program counter (PC), accumulator register (ACC), and one SFR / 8051 core RAM register

- Trace depth up to 1000 instructions if all registers are traced, or 2000 instructions if only the PC is traced (on devices that include trace memory)

- Program address trigger to start tracing

- Trace windowing, that is, only trace when the PC is within a given range

- Two modes for handling trace buffer full: continuous (overwriting the oldest trace data) or break when trace buffer is full

### 9.5 Single Wire Viewer Interface

The SWV interface is closely associated with SWD but can also be used independently. SWV data is output on the JTAG interface's TDO pin. If using SWV, you must configure the device for SWD, not JTAG. SWV is not supported with the JTAG interface.

SWV is ideal for application debug where it is helpful for the firmware to output data similar to 'printf' debugging on PCs. The SWV is ideal for data monitoring, because it requires only a single pin and can output data in standard UART format or Manchester encoded format. For example, it can be used to tune a PID control loop in which the output and graphing of the three error terms greatly simplifies coefficient tuning.

The following features are supported in SWV:

- 32 virtual channels, each 32 bits long

- Simple, efficient packing and serializing protocol

- Supports standard UART format (N81)

### 9.6 Programming Features

The JTAG and SWD interfaces provide full programming support. The entire device can be erased, programmed, and verified. You can increase flash protection levels to protect firmware IP. Flash protection can only be reset after a full device erase. Individual flash blocks can be erased, programmed, and verified, if block security settings permit.

### 9.7 Device Security

PSoC 3 offers an advanced security feature called device security, which permanently disables all test, programming, and debug ports, protecting your application from external access. The device security is activated by programming a 32-bit key (0×50536F43) to a Write Once Latch (WOL).

The WOL is a type of nonvolatile latch (NVL). The cell itself is an NVL with additional logic wrapped around it. Each WOL device contains four bytes (32 bits) of data. The wrapper outputs a '1' if a super-majority (28 of 32) of its bits match a pre-determined pattern (0×50536F43); it outputs a '0' if this majority is not reached. When the output is 1, the Write Once NV latch locks the part out of Debug and Test modes; it also permanently gates off the ability to erase or alter the contents of the latch. Matching all bits is intentionally not required, so that single (or few) bit failures do not deassert the WOL output. The state of the NVL bits after wafer processing is truly random with no tendency toward 1 or 0.

The WOL only locks the part after the correct 32-bit key (0×50536F43) is loaded into the NVL's volatile memory, programmed into the NVL's nonvolatile cells, and the part is reset. The output of the WOL is only sampled on reset and used to disable the access. This precaution prevents anyone from reading, erasing, or altering the contents of the internal memory.

The user can write the key into the WOL to lock out external access only if no flash protection is set (see "Flash Security" on page 23). However, after setting the values in the WOL, a user still has access to the part until it is reset. Therefore, a user can write the key into the WOL, program the flash protection data, and then reset the part to lock it.

If the device is protected with a WOL setting, Cypress cannot perform failure analysis and, therefore, cannot accept RMAs from customers. The WOL can be read out through the SWD port to electrically identify protected parts. The user can write the key in WOL to lock out external access only if no flash protection is set. For more information on how to take full advantage of the security features in PSoC see the PSoC 3 TRM.

### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

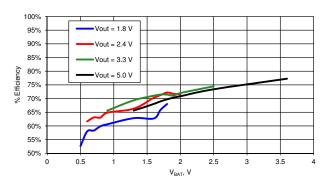

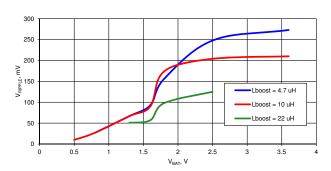

Figure 11-11. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 4.7  $\mu H^{[42]}$

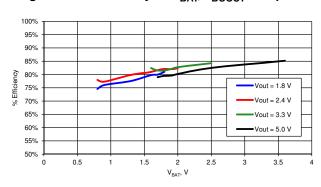

Figure 11-13. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 22  $\mu H^{[42]}$

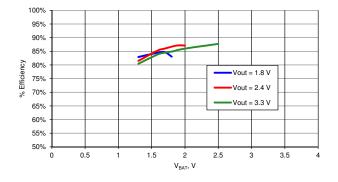

Figure 11-12. Efficiency vs  $V_{BAT}$ ,  $L_{BOOST}$  = 10  $\mu H^{[42]}$

Figure 11-14.  $V_{RIPPLE}$  vs  $V_{BAT}$  [42]

### Note

<sup>42.</sup> Typical example. Actual values may vary depending on external component selection, PCB layout, and other design parameters.

## 11.4 Inputs and Outputs

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point, the low-impedance connections no longer exist and the pins change to their normal NVL settings.

11.4.1 GPIO

Table 11-9. GPIO DC Specifications

| Parameter       | Description                                                                 | Conditions                                                        | Min                     | Тур | Max                     | Units |

|-----------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|-----|-------------------------|-------|

| $V_{IH}$        | Input voltage high threshold                                                | CMOS Input, PRT[×]CTL = 0                                         | $0.7 \times V_{DDIO}$   | _   | -                       | V     |

| $V_{IL}$        | Input voltage low threshold                                                 | CMOS Input, PRT[×]CTL = 0                                         | _                       | -   | $0.3 \times V_{DDIO}$   | V     |

| V <sub>IH</sub> | Input voltage high threshold                                                | LVTTL Input, PRT[×]CTL = 1,V <sub>DDIO</sub> < 2.7 V              | 0.7 × V <sub>DDIO</sub> | -   | _                       | V     |

| V <sub>IH</sub> | Input voltage high threshold                                                | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7 \text{ V}$ | 2.0                     | -   | _                       | V     |

| V <sub>IL</sub> | Input voltage low threshold                                                 | LVTTL Input, PRT[×]CTL = 1,V <sub>DDIO</sub> < 2.7 V              | _                       | -   | 0.3 × V <sub>DDIO</sub> | V     |

| V <sub>IL</sub> | Input voltage low threshold                                                 | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7 \text{ V}$ | _                       | -   | 0.8                     | V     |

| V <sub>OH</sub> | Output voltage high                                                         | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>                   | V <sub>DDIO</sub> – 0.6 | _   | _                       | V     |

|                 |                                                                             | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>                   | V <sub>DDIO</sub> – 0.5 | _   | _                       | V     |

| $V_{OL}$        | Output voltage low                                                          | I <sub>OL</sub> = 8 mA at 3.3 V <sub>DDIO</sub>                   | _                       | _   | 0.6                     | V     |

|                 |                                                                             | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>                   | _                       | _   | 0.6                     | V     |

|                 |                                                                             | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>                   | _                       | _   | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                                            |                                                                   | 3.5                     | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                                          |                                                                   | 3.5                     | 5.6 | 8.5                     | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value)[43]                                  | 25 °C, V <sub>DDIO</sub> = 3.0 V                                  | _                       | _   | 2                       | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[43]</sup>                                           | GPIOs not shared with opamp outputs, MHz ECO or kHzECO            | _                       | 4   | 7                       | pF    |

|                 |                                                                             | GPIOs shared with MHz ECO or kHzECO <sup>[44]</sup>               | _                       | 5   | 7                       | pF    |

|                 |                                                                             | GPIOs shared with opamp outputs                                   | _                       | -   | 18                      | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger) <sup>[43]</sup>                  |                                                                   | _                       | 40  | _                       | mV    |

| Idiode          | Current through protection diode to V <sub>DDIO</sub> and V <sub>SSIO</sub> |                                                                   | -                       | -   | 100                     | μA    |

| Rglobal         | Resistance pin to analog global bus                                         | 25 °C, V <sub>DDIO</sub> = 3.0 V                                  | -                       | 320 | _                       | Ω     |

| Rmux            | Resistance pin to analog mux bus                                            | 25 °C, V <sub>DDIO</sub> = 3.0 V                                  | _                       | 220 | _                       | Ω     |

### Notes

<sup>43.</sup> Based on device characterization (Not production tested).

<sup>44.</sup> For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC® 3 and PSoC 5 External Oscillator.

# 11.4.2 SIO

# Table 11-11. SIO DC Specifications

| Parameter       | Description                                                | Conditions                                                                             | Min                     | Тур | Max                     | Units |  |  |

|-----------------|------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------|-----|-------------------------|-------|--|--|

| Vinmax          | Maximum input voltage                                      | All allowed values of V <sub>DDIO</sub> and V <sub>DDD</sub> , see <i>Section 11.1</i> | -                       | _   | 5.5                     | V     |  |  |

| Vinref          | Input voltage reference (Differential input mode)          |                                                                                        | 0.5                     | -   | $0.52 \times V_{DDIO}$  | V     |  |  |

|                 | Output voltage reference (Regulated output mode)           |                                                                                        |                         |     |                         |       |  |  |

| Voutref         |                                                            | V <sub>DDIO</sub> > 3.7                                                                | 1                       | _   | V <sub>DDIO</sub> – 1   | V     |  |  |

|                 |                                                            | V <sub>DDIO</sub> < 3.7                                                                | 1                       | _   | V <sub>DDIO</sub> – 0.5 | V     |  |  |

|                 | Input voltage high threshold                               |                                                                                        |                         |     |                         |       |  |  |

| $V_{IH}$        | GPIO mode                                                  | CMOS input                                                                             | $0.7 \times V_{DDIO}$   | _   | _                       | V     |  |  |

|                 | Differential input mode <sup>[46]</sup>                    | Hysteresis disabled                                                                    | SIO_ref + 0.2           | _   | _                       | V     |  |  |

|                 | Input voltage low threshold                                |                                                                                        |                         |     |                         |       |  |  |

| $V_{IL}$        | GPIO mode                                                  | CMOS input                                                                             | _                       | _   | $0.3 \times V_{DDIO}$   | V     |  |  |

|                 | Differential input mode <sup>[46]</sup>                    | Hysteresis disabled                                                                    | _                       | _   | SIO_ref - 0.2           | V     |  |  |

|                 | Output voltage high                                        |                                                                                        |                         |     |                         |       |  |  |

| \ <u></u>       | Unregulated mode                                           | I <sub>OH</sub> = 4 mA, V <sub>DDIO</sub> = 3.3 V                                      | V <sub>DDIO</sub> – 0.4 | _   | _                       | V     |  |  |

| V <sub>OH</sub> | Regulated mode <sup>[46]</sup>                             | I <sub>OH</sub> = 1 mA                                                                 | SIO_ref-0.65            | _   | SIO_ref + 0.2           | V     |  |  |

|                 | Regulated mode <sup>[46]</sup>                             | I <sub>OH</sub> = 0.1 mA                                                               | SIO_ref - 0.3           | _   | SIO_ref + 0.2           | V     |  |  |

|                 | Output voltage low                                         | $V_{DDIO} = 3.30 \text{ V}, I_{OL} = 25 \text{ mA}$                                    | _                       | _   | 0.8                     | V     |  |  |

| $V_{OL}$        |                                                            | $V_{\rm DDIO}$ = 3.30 V, $I_{\rm OL}$ = 20 mA                                          | _                       | _   | 0.4                     | V     |  |  |

|                 |                                                            | $V_{DDIO} = 1.80 \text{ V}, I_{OL} = 4 \text{ mA}$                                     | _                       | _   | 0.4                     | V     |  |  |

| Rpullup         | Pull-up resistor                                           |                                                                                        | 3.5                     | 5.6 | 8.5                     | kΩ    |  |  |

| Rpulldown       | Pull-down resistor                                         |                                                                                        | 3.5                     | 5.6 | 8.5                     | kΩ    |  |  |

| I <sub>IL</sub> | Input leakage current (absolute value) <sup>[47]</sup>     |                                                                                        | _                       | -   | _                       | _     |  |  |

|                 | V <sub>IH</sub> ≤ Vddsio                                   | 25 °C, Vddsio = 3.0 V, V <sub>IH</sub> = 3.0 V                                         | _                       | _   | 14                      | nA    |  |  |

|                 | V <sub>IH</sub> > Vddsio                                   | 25 °C, Vddsio = 0 V, V <sub>IH</sub> = 3.0 V                                           | _                       | _   | 10                      | μA    |  |  |

| C <sub>IN</sub> | Input Capacitance <sup>[47]</sup>                          |                                                                                        | _                       | _   | 7                       | pF    |  |  |

|                 | Input voltage hysteresis (Schmitt-Trigger) <sup>[47]</sup> | Single ended mode (GPIO mode)                                                          | _                       | 40  | _                       | mV    |  |  |

| $V_{H}$         | (Schmitt-Trigger) <sup>[47]</sup>                          | Differential mode                                                                      | _                       | 35  | _                       | mV    |  |  |

| Idiode          | Current through protection diode to V <sub>SSIO</sub>      |                                                                                        | -                       | _   | 100                     | μΑ    |  |  |

Notes

46. See Figure 6-10 on page 39 and Figure 6-13 on page 43 for more information on SIO reference.

47. Based on device characterization (Not production tested)

Table 11-12. SIO AC Specifications (continued)

| Parameter | Description                                                                                | Conditions                               | Min | Тур | Max | Units |  |

|-----------|--------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|--|

|           | SIO output operating frequency                                                             |                                          |     |     |     | •     |  |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Unregulated output (GPIO) mode, fast strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 33  | MHz   |  |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Unregulated output (GPIO) mode, fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | _   | 16  | MHz   |  |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregulated output (GPIO) mode, slow strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | _   | 5   | MHz   |  |

| Fsioout   | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregulated output (GPIO) mode, slow strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 4   | MHz   |  |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, fast strong drive mode           | Output continuously switching into 25 pF | _   | _   | 20  | MHz   |  |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Regulated output mode, fast strong drive mode          | Output continuously switching into 25 pF | _   | _   | 10  | MHz   |  |

|           | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated output mode, slow strong drive mode          | Output continuously switching into 25 pF | _   | _   | 2.5 | MHz   |  |

| Fsioin    | SIO input operating frequency                                                              |                                          |     |     |     |       |  |

| 1-210111  | 1.71 V ≤ V <sub>DDIO</sub> ≤ 5.5 V                                                         | 90/10% V <sub>DDIO</sub>                 | _   | _   | 33  | MHz   |  |

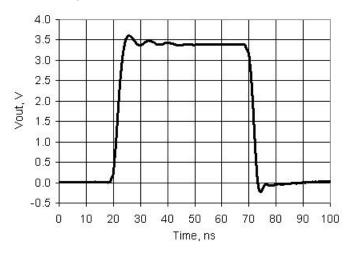

Figure 11-20. SIO Output Rise and Fall Times, Fast Strong Mode,  $\rm V_{DDIO}$  = 3.3 V, 25 pF Load

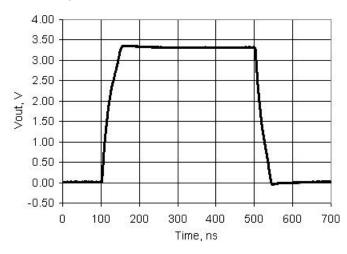

Figure 11-21. SIO Output Rise and Fall Times, Slow Strong Mode,  $V_{\rm DDIO}$  = 3.3 V, 25 pF Load

Table 11-13. SIO Comparator Specifications<sup>[49]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | _   | _   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | _   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | _   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | _   | 250 | μV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | _   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | -   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | _   | -   |       |

| Tresp     | Response time                  |                           | _   | -   | 30  | ns    |

## 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 72.

Table 11-14. USBIO DC Specifications

| Parameter                       | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|---------------------------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                           | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | _   | 1.575          | kΩ    |

| Rusba                           | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | _   | 3.090          | kΩ    |

| Vohusb                          | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb                          | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | _              | -   | 0.3            | V     |

| Vihgpio                         | Input voltage high, GPIO mode          | V <sub>DDD</sub> ≥ 3 V                             | 2              | _   | -              | V     |

| Vilgpio                         | Input voltage low, GPIO mode           | $V_{DDD} \ge 3 \text{ V}$                          | _              | _   | 0.8            | V     |

| Vohgpio                         | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | 2.4            | _   | -              | V     |

| Volgpio                         | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | _              | _   | 0.3            | V     |

| Vdi                             | Differential input sensitivity         | (D+)-(D-)                                          | _              | _   | 0.2            | V     |

| Vcm                             | Differential input common mode range   | -                                                  | 0.8            | -   | 2.5            | V     |

| Vse                             | Single ended receiver threshold        | _                                                  | 0.8            | _   | 2              | V     |

| Rps2                            | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | -   | 7              | kΩ    |

| Rext                            | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                              | USB driver output impedance            | Including Rext                                     | 28             | _   | 44             | Ω     |

| C <sub>IN</sub>                 | USB transceiver input capacitance      |                                                    | -              | _   | 20             | pF    |

| I <sub>IL</sub> <sup>[49]</sup> | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | _              | _   | 2              | nA    |

### Note

Document Number: 001-53413 Rev. \*Y Page 85 of 137

<sup>49.</sup> Based on device characterization (Not production tested).

### 11.4.4 XRES

# Table 11-17. XRES DC Specifications

| Parameter       | Description                                                           | Conditions | Min                   | Тур | Max                   | Units |

|-----------------|-----------------------------------------------------------------------|------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                          |            | $0.7 \times V_{DDIO}$ | _   | _                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                           |            | _                     | _   | $0.3 \times V_{DDIO}$ | V     |

| Rpullup         | Pull-up resistor                                                      |            | 3.5                   | 5.6 | 8.5                   | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[50]</sup>                                     |            | -                     | 3   | _                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt–Trigger) <sup>[50]</sup>            |            | _                     | 100 | _                     | mV    |

| Idiode          | Current through protection diode to $V_{\rm DDIO}$ and $V_{\rm SSIO}$ |            | _                     | -   | 100                   | μA    |

# Table 11-18. XRES AC Specifications

|   | Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|---|--------------------|-------------------|------------|-----|-----|-----|-------|

| Γ | T <sub>RESET</sub> | Reset pulse width |            | 1   | _   | _   | μs    |

# 11.5 Analog Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

# 11.5.1 Opamp

Table 11-19. Opamp DC Specifications

| Parameter         | Description                                 | Conditions                                                                                               | Min                     | Тур  | Max                     | Units   |

|-------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|---------|

| V <sub>IOFF</sub> | Input offset voltage                        |                                                                                                          | _                       | -    | 2                       | mV      |

| V <sub>OS</sub>   | Input offset voltage                        |                                                                                                          | _                       | _    | 2.5                     | mV      |

|                   |                                             | Operating temperature –40 °C to 70 °C                                                                    | _                       | _    | 2                       | mV      |

| TCV <sub>OS</sub> | Input offset voltage drift with temperature | Power mode = high                                                                                        | _                       | _    | ±30                     | μV / °C |

| Ge1               | Gain error, unity gain buffer mode          | Rload = 1 k $\Omega$                                                                                     | _                       | _    | ±0.1                    | %       |

| C <sub>IN</sub>   | Input capacitance                           | Routing from pin                                                                                         | _                       | _    | 18                      | pF      |

| V <sub>O</sub>    | Output voltage range                        | 1 mA, source or sink, power mode = high                                                                  | V <sub>SSA</sub> + 0.05 | _    | V <sub>DDA</sub> – 0.05 | V       |

| I <sub>OUT</sub>  | Output current capability, source or sink   | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, V <sub>DDA</sub> > 2.7 V              | 25                      | -    | -                       | mA      |

|                   |                                             | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, 1.7 V = V <sub>DDA</sub> $\leq$ 2.7 V | 16                      | _    | -                       | mA      |

| $I_{DD}$          | Quiescent current                           | Power mode = min                                                                                         | _                       | 250  | 400                     | uA      |

|                   |                                             | Power mode = low                                                                                         | _                       | 250  | 400                     | uA      |

|                   |                                             | Power mode = med                                                                                         | _                       | 330  | 950                     | uA      |

|                   |                                             | Power mode = high                                                                                        | _                       | 1000 | 2500                    | uA      |

| CMRR              | Common mode rejection ratio                 |                                                                                                          | 80                      | -    | _                       | dB      |

| PSRR              | Power supply rejection ratio                | $V_{DDA} \ge 2.7 \text{ V}$                                                                              | 85                      | -    | _                       | dB      |

|                   |                                             | V <sub>DDA</sub> < 2.7 V                                                                                 | 70                      | -    | -                       | dB      |

| I <sub>IB</sub>   | Input bias current <sup>[50]</sup>          | 25 °C                                                                                                    | -                       | 10   | _                       | pА      |

### Note

50. Based on device characterization (Not production tested).

Document Number: 001-53413 Rev. \*Y Page 88 of 137

Table 11-28. IDAC DC Specifications (continued)

| Parameter       | Description                          | Conditions                                                                                                                              | Min | Тур  | Max  | Units  |

|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|--------|

| Ezs             | Zero scale error                     |                                                                                                                                         | _   | 0    | ±1   | LSB    |

| Eg              | Gain error                           | Range = 2.04 mA, 25 °C                                                                                                                  | _   | _    | ±2.5 | %      |

|                 |                                      | Range = 255 μA, 25 ° C                                                                                                                  | _   | _    | ±2.5 | %      |

|                 |                                      | Range = 31.875 μA, 25 ° C                                                                                                               | _   | _    | ±3.5 | %      |

| TC_Eg           | Temperature coefficient of gain      | Range = 2.04 mA                                                                                                                         | _   | _    | 0.04 | % / °C |

|                 | error                                | Range = 255 μA                                                                                                                          | _   | _    | 0.04 | % / °C |

|                 |                                      | Range = 31.875 μA                                                                                                                       | _   | _    | 0.05 | % / °C |

| INL             | Integral nonlinearity                | Sink mode, range = $255 \mu\text{A}$ , Codes $8-255$ , Rload = $2.4 \mathrm{k}\Omega$ , Cload = $15 \mathrm{pF}$                        | -   | ±0.9 | ±1   | LSB    |

|                 |                                      | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 $k\Omega$ ,<br>Cload = 15 pF                                            | -   | ±1.2 | ±1.6 | LSB    |

| DNL             | Differential nonlinearity            | Sink mode, range = 255 μA, Rload<br>= 2.4 kΩ, Cload = 15 pF                                                                             | _   | ±0.3 | ±1   | LSB    |

|                 |                                      | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 $k\Omega$ , Cload = 15 pF                                                              | _   | ±0.3 | ±1   | LSB    |

| Vcompliance     | Dropout voltage, source or sink mode | Voltage headroom at max current,<br>Rload to V <sub>DDA</sub> or Rload to V <sub>SSA</sub> ,<br>V <sub>DIFF</sub> from V <sub>DDA</sub> | 1   | _    | -    | V      |

| I <sub>DD</sub> | Operating current, code = 0          | Low speed mode, source mode, range = 31.875 µA                                                                                          | _   | 44   | 100  | μA     |

|                 |                                      | Low speed mode, source mode, range = 255 μA,                                                                                            | _   | 33   | 100  | μA     |

|                 |                                      | Low speed mode, source mode, range = 2.04 mA                                                                                            | _   | 33   | 100  | μA     |

|                 |                                      | Low speed mode, sink mode, range = 31.875 µA                                                                                            | _   | 36   | 100  | μA     |

|                 |                                      | Low speed mode, sink mode, range = 255 μA                                                                                               | _   | 33   | 100  | μA     |

|                 |                                      | Low speed mode, sink mode, range = 2.04 mA                                                                                              | _   | 33   | 100  | μA     |

|                 |                                      | High speed mode, source mode, range = 31.875 µA                                                                                         | _   | 310  | 500  | μA     |

|                 |                                      | High speed mode, source mode, range = 255 μA                                                                                            | _   | 305  | 500  | μA     |

|                 |                                      | High speed mode, source mode, range = 2.04 mA                                                                                           | _   | 305  | 500  | μA     |

|                 |                                      | High speed mode, sink mode, range = 31.875 μA                                                                                           | _   | 310  | 500  | μA     |

|                 |                                      | High speed mode, sink mode, range = 255 μA                                                                                              | _   | 300  | 500  | μA     |

|                 |                                      | High speed mode, sink mode, range = 2.04 mA                                                                                             | _   | 300  | 500  | μΑ     |

# 11.6.8 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component data sheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

Table 11-54. UDB AC Specifications

| Parameter              | Description                                                   | Conditions                                       | Min | Тур | Max   | Units |  |

|------------------------|---------------------------------------------------------------|--------------------------------------------------|-----|-----|-------|-------|--|

| Datapath Perfor        | mance                                                         |                                                  | •   | •   |       |       |  |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                  | _   | _   | 67.01 | MHz   |  |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                  | -   | -   | 67.01 | MHz   |  |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit CRC/PRS in a UDB pair             |                                                  | -   | -   | 67.01 | MHz   |  |

| PLD Performan          | ce                                                            |                                                  |     |     |       |       |  |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass PLD function in a UDB pair    |                                                  | _   | _   | 67.01 | MHz   |  |

| Clock to Output        | Clock to Output Performance                                   |                                                  |     |     |       |       |  |

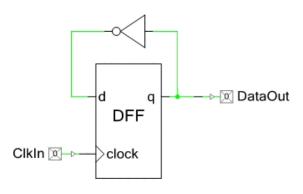

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-65. | 25 °C, V <sub>DDD</sub> ≥ 2.7 V                  | _   | 20  | 25    | ns    |  |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-65. | Worst-case placement, routing, and pin selection | _   | _   | 55    | ns    |  |

Figure 11-65. Clock to Output Performance

Document Number: 001-53413 Rev. \*Y Page 108 of 137

0.395 0.420 0.299 DIMENSIONS IN INCHES MIN. MAX. PKG. WEIGHT: REFER TO PMDD SPEC.

Figure 13-1. 48-pin (300 mil) SSOP Package Outline

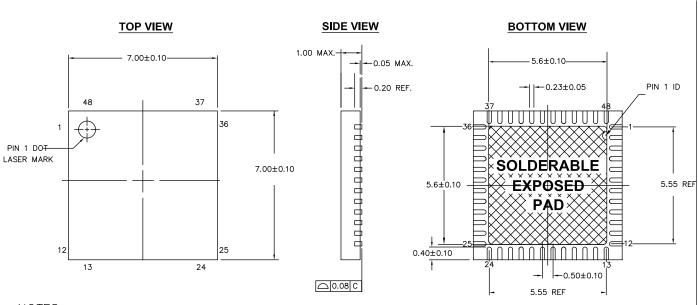

Figure 13-2. 48-pin QFN Package Outline

### NOTES:

- 1. MATCH AREA IS SOLDERABLE EXPOSED METAL.

- 2. REFERENCE JEDEC#: MO-220

- 3. PACKAGE WEIGHT: REFER TO PMDD SPEC.

- 4. ALL DIMENSIONS ARE IN MM [MIN/MAX]

- 5. PACKAGE CODE

| PART # | DESCRIPTION |

|--------|-------------|

| LT48D  | LEAD FREE   |

001-45616 \*E

# 14. Acronyms

Table 14-1. Acronyms Used in this Document

|                  | cronyms Used in this Document                                                                   |

|------------------|-------------------------------------------------------------------------------------------------|

| Acronym          | Description                                                                                     |

| abus             | analog local bus                                                                                |

| ADC              | analog-to-digital converter                                                                     |

| AG               | analog global                                                                                   |

| АНВ              | AMBA (advanced microcontroller bus architecture) high-performance bus, an ARM data transfer bus |

| ALU              | arithmetic logic unit                                                                           |

| AMUXBUS          | analog multiplexer bus                                                                          |

| API              | application programming interface                                                               |

| APSR             | application program status register                                                             |

| ARM <sup>®</sup> | advanced RISC machine, a CPU architecture                                                       |

| ATM              | automatic thump mode                                                                            |

| BW               | bandwidth                                                                                       |

| CAN              | Controller Area Network, a communications protocol                                              |

| CMRR             | common-mode rejection ratio                                                                     |

| CPU              | central processing unit                                                                         |

| CRC              | cyclic redundancy check, an error-checking protocol                                             |

| DAC              | digital-to-analog converter, see also IDAC, VDAC                                                |

| DFB              | digital filter block                                                                            |

| DIO              | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                 |

| DMA              | direct memory access, see also TD                                                               |

| DNL              | differential nonlinearity, see also INL                                                         |

| DNU              | do not use                                                                                      |

| DR               | port write data registers                                                                       |

| DSI              | digital system interconnect                                                                     |

| DWT              | data watchpoint and trace                                                                       |

| ECC              | error correcting code                                                                           |

| ECO              | external crystal oscillator                                                                     |

| EEPROM           | electrically erasable programmable read-only memory                                             |

| EMI              | electromagnetic interference                                                                    |

| EMIF             | external memory interface                                                                       |

| EOC              | end of conversion                                                                               |

| EOF              | end of frame                                                                                    |

| EPSR             | execution program status register                                                               |

| ESD              | electrostatic discharge                                                                         |

| ETM              | embedded trace macrocell                                                                        |

Table 14-1. Acronyms Used in this Document (continued)

| FIR finite impulse response, see also IIR FPB flash patch and breakpoint FS full-speed GPIO general-purpose input/output, applies to a PSoC pin HVI high-voltage interrupt, see also LVI, LVD IC integrated circuit IDAC current DAC, see also DAC, VDAC IDE integrated development environment I²C, or IIC Inter-Integrated Circuit, a communications protocol IIR infinite impulse response, see also FIR ILO internal low-speed oscillator, see also IMO IMO internal main oscillator, see also ILO INL integral nonlinearity, see also DNL I/O input/output, see also GPIO, DIO, SIO, USBIO IPOR initial power-on reset IPSR interrupt program status register IRQ interrupt request ITM instrumentation trace macrocell LCD liquid crystal display LIN Local Interconnect Network, a communications protocol. LR link register LUT lookup table LVD low-voltage detect, see also LVI LVI low-voltage interrupt, see also HVI LVTTL low-voltage transistor-transistor logic MAC multiply-accumulate MCU microcontroller unit MISO master-in slave-out NC no connect NMI nonmaskable interrupt NRZ non-return-to-zero NVIC nested vectored interrupt controller NVL nonvolatile latch, see also WOL opamp operational amplifier PAL programmable gain amplifier                       | Acronym                  | Pagarintian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPB flash patch and breakpoint  FS full-speed  GPIO general-purpose input/output, applies to a PSoC pin  HVI high-voltage interrupt, see also LVI, LVD  IC integrated circuit  IDAC current DAC, see also DAC, VDAC  IDE integrated development environment  I²C, or IIC Inter-Integrated Circuit, a communications protocol  IIR infinite impulse response, see also FIR  ILO internal low-speed oscillator, see also IMO  IMO internal main oscillator, see also ILO  INL integral nonlinearity, see also DNL  I/O input/output, see also GPIO, DIO, SIO, USBIO  IPOR initial power-on reset  IPSR interrupt program status register  IRQ interrupt request  ITM instrumentation trace macrocell  LCD liquid crystal display  LIN Local Interconnect Network, a communications protocol.  LR link register  LUT lookup table  LVD low-voltage detect, see also LVI  LVI low-voltage interrupt, see also HVI  LVTTL low-voltage transistor-transistor logic  MAC multiply-accumulate  MCU microcontroller unit  MISO master-in slave-out  NC no connect  NMI nonmaskable interrupt  NRZ non-return-to-zero  NVIC nested vectored interrupt controller  NVL nonvolatile latch, see also WOL  opamp operational amplifier  PAL programmable array logic, see also PLD  PC program counter |                          | Description (Control of the Control |