Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 68-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 68-QFN (8×8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3665lti-199 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

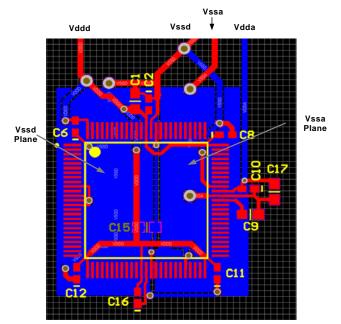

### Figure 2-8. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

## 3. Pin Descriptions

**IDAC0, IDAC1, IDAC2, IDAC3.** Low resistance output pin for high current DACs (IDAC).

### Opamp0out, Opamp1out<sup>[15]</sup>, Opamp2out, Opamp3out<sup>[15]</sup>.

High current output of uncommitted opamp.<sup>[14]</sup>

Extref0, Extref1. External reference input to the analog system.

**Opamp0–**, **Opamp1–**<sup>[15]</sup>, **Opamp2–**, **Opamp3–**<sup>[15]</sup>. Inverting input to uncommitted opamp.

### **Opamp0+, Opamp1+**<sup>[15]</sup>, **Opamp2+, Opamp3+**<sup>[15]</sup>.

Noninverting input to uncommitted opamp.

**GPIO.** General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense.<sup>[14]</sup>

**I2C0: SCL, I2C1: SCL.**  $I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

**I2C0: SDA**, **I2C1: SDA**.  $I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

Ind. Inductor connection to boost pump.

kHz XTAL: Xo, kHz XTAL: Xi. 32.768 kHz crystal oscillator pin.

MHz XTAL: Xo, MHz XTAL: Xi. 4 to 25 MHz crystal oscillator pin.

**nTRST.** Optional JTAG Test Reset programming and debug port connection to reset the JTAG connection.

**SIO.** Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

**SWDCK.** Serial wire debug clock programming and debug port connection.

**SWDIO.** Serial wire debug input and output programming and debug port connection.

SWV. Single wire viewer debug output.

TCK. JTAG test clock programming and debug port connection.

**TDI.** JTAG test data in programming and debug port connection.

**TDO.** JTAG test data out programming and debug port connection.

**TMS.** JTAG test mode select programming and debug port connection.

**USBIO**, **D+**. Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin. Pins are Do Not Use (DNU) on devices without USB.

**USBIO**, **D–.** Provides D– connection directly to a USB 2.0 bus. May be used as a digital I/O pin. Pins are Do Not Use (DNU) on devices without USB.

VBOOST. Power sense connection to boost pump.

VBAT. Battery supply to boost pump.

#### Notes

14. GPIOs with opamp outputs are not recommended for use with CapSense.

<sup>15.</sup> This feature on select devices only. See Ordering Information on page 120 for details.

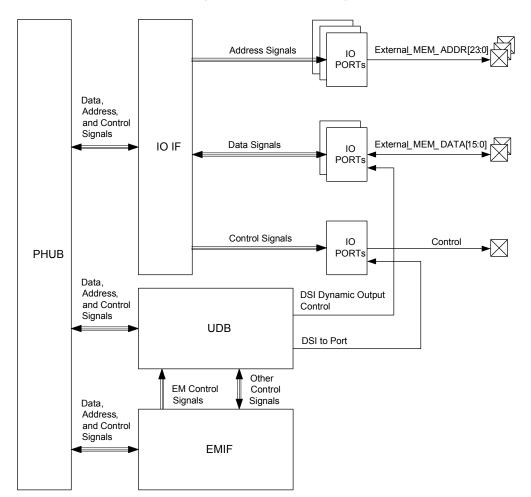

### 5.6 External Memory Interface

CY8C36 provides an external memory interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C36 supports only one type of external memory device at a time.

External memory can be accessed through the 8051 xdata space; up to 24 address bits can be used. See xdata Space on page 27. The memory can be 8 or 16 bits wide.

Figure 5-1. EMIF Block Diagram

# 6. System Integration

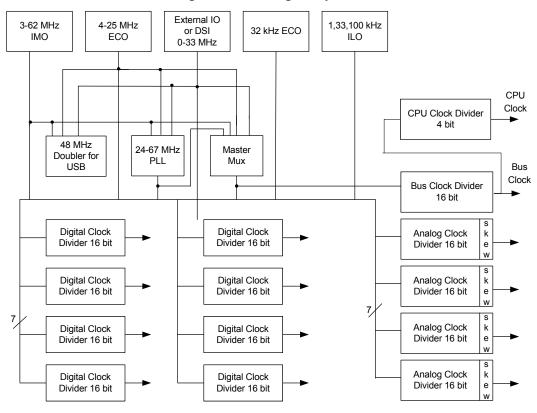

### 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 66 MHz clock, accurate to  $\pm 1\%$  over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC. Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 62-MHz IMO, ±1% at 3 MHz

- 4- to 25-MHz external crystal oscillator (MHzECO)

- Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 30.

- DSI signal from an external I/O pin or other logic

- 24- to 67-MHz fractional PLL sourced from IMO, MHzECO, or DSI

- 1-kHz, 33-kHz, 100-kHz ILO for WDT and sleep timer

32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB. (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

Figure 6-1. Clocking Subsystem

#### Table 6-1. Oscillator Summary

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax | Startup Time                          |

|---------|--------|----------------------------------|---------|-------------------|---------------------------------------|

| IMO     | 3 MHz  | ±1% over voltage and temperature | 62 MHz  | ±7%               | 13 µs max                             |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent | 5 ms typ, max is<br>crystal dependent |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent   | Input dependent                       |

| PLL     | 24 MHz | Input dependent                  | 67 MHz  | Input dependent   | 250 µs max                            |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent   | 1 µs max                              |

| ILO     | 1 kHz  | -50%, +100%                      | 100 kHz | -55%, +100%       | 15 ms max in lowest power mode        |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent | 500 ms typ, max is crystal dependent  |

### 6.1.1 Internal Oscillators

Figure 6-1 shows that there are two internal oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

#### 6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due to its  $\pm 1\%$  accuracy. The IMO operates with no external components and outputs a stable clock. A factory trim for each frequency range is stored in the device. With the factory trim, tolerance varies from  $\pm 1\%$  at 3 MHz, up to  $\pm 7\%$  at 62 MHz. The IMO, in conjunction with the PLL, allows generation of other clocks up to the device's maximum frequency (see Phase-Locked Loop).

The IMO provides clock outputs at 3, 6, 12, 24, 48, and 62 MHz.

#### 6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the input clock. The doubler works at an input frequency of 24 MHz, providing 48 MHz for the USB. It can be configured to use a clock from the IMO, MHzECO, or the DSI (external pin).

#### 6.1.1.3 Phase-Locked Loop

The PLL allows low frequency, high accuracy clocks to be multiplied to higher frequencies. This is a tradeoff between higher clock frequency and accuracy and, higher power consumption and increased startup time.

The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range of 24 to 67 MHz. Its input and feedback dividers supply 4032 discrete ratios to create almost any desired clock frequency. The accuracy of the PLL output depends on the accuracy of the PLL input source. The most common PLL use is to multiply the IMO clock at 3 MHz, where it is most accurate, to generate the other clocks up to the device's maximum frequency.

The PLL achieves phase lock within 250 µs (verified by bit setting). It can be configured to use a clock from the IMO, MHZECO or DSI (external pin). The PLL clock source can be used until lock is complete and signaled with a lock bit. The lock signal can be routed through the DSI to generate an interrupt. Disable the PLL before entering low-power modes.

#### 6.1.1.4 Internal Low-Speed Oscillator

The ILO provides clock frequencies for low-power consumption, including the watchdog timer, and sleep timer. The ILO generates up to three different clocks: 1 kHz, 33 kHz, and 100 kHz.

The 1-kHz clock (CLK1K) is typically used for a background 'heartbeat' timer. This clock inherently lends itself to low-power supervisory operations such as the watchdog timer and long sleep intervals using the central timewheel (CTW).

The central timewheel is a 1-kHz, free-running, 13-bit counter clocked by the ILO. The central timewheel is always enabled, except in hibernate mode and when the CPU is stopped during debug on chip mode. It can be used to generate periodic interrupts for timing purposes or to wake the system from a low-power mode. Firmware can reset the central timewheel. Systems that require accurate timing should use the RTC capability instead of the central timewheel.

The 100-kHz clock (CLK100K) can be used as a low power master clock. It can also generate time intervals using the fast timewheel.

The fast timewheel is a 5-bit counter, clocked by the 100-kHz clock. It features programmable settings and automatically resets when the terminal count is reached. An optional interrupt can be generated each time the terminal count is reached. This enables flexible, periodic interrupts of the CPU at a higher rate than is allowed using the central timewheel.

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal.

#### 6.1.2 External Oscillators

Figure 6-1 shows that there are two external oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

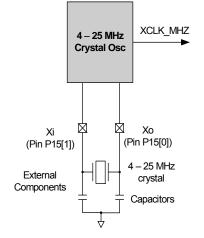

#### 6.1.2.1 MHz External Crystal Oscillator

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate other clocks up to the device's maximum frequency (see Phase-Locked Loop). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

### Figure 6-2. MHzECO Block Diagram

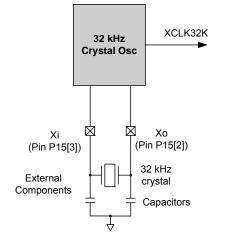

#### 6.1.2.2 32.768-kHz ECO

The 32.768-kHz external crystal oscillator (32kHzECO) provides precision timing with minimal power consumption using an external 32.768-kHz watch crystal (see Figure 6-3). The 32kHzECO also connects directly to the sleep timer and provides the source for the RTC. The RTC uses a 1-second interrupt to implement the RTC functionality in firmware.

The oscillator works in two distinct power modes. This allows users to trade off power consumption with noise immunity from neighboring circuits. The GPIO pins connected to the external crystal and capacitors are fixed.

#### Figure 6-3. 32kHzECO Block Diagram

It is recommended that the external 32.768-kHz watch crystal have a load capacitance (CL) of 6 pF or 12.5 pF. Check the crystal manufacturer's datasheet. The two external capacitors, CL1 and CL2, are typically of the same value, and their total capacitance, CL1CL2 / (CL1 + CL2), including pin and trace capacitance, should equal the crystal CL value. For more information, refer to application note AN54439: PSoC 3 and

PSoC 5 External Oscillators. See also pin capacitance specifications in the "GPIO" section on page 80.

#### 6.1.2.3 Digital System Interconnect

The DSI provides routing for clocks taken from external clock oscillators connected to I/O. The oscillators can also be generated within the device in the digital system and UDBs.

While the primary DSI clock input provides access to all clocking resources, up to eight other DSI clocks (internally or externally generated) may be routed directly to the eight digital clock dividers. This is only possible if there are multiple precision clock sources.

#### 6.1.3 Clock Distribution

All seven clock sources are inputs to the central clock distribution system. The distribution system is designed to create multiple high precision clocks. These clocks are customized for the design's requirements and eliminate the common problems found with limited resolution prescalers attached to peripherals. The clock distribution system generates several types of clock trees.

- The master clock is used to select and supply the fastest clock in the system for general clock requirements and clock synchronization of the PSoC device.

- Bus clock 16-bit divider uses the master clock to generate the bus clock used for data transfers. Bus clock is the source clock for the CPU clock divider.

- Eight fully programmable 16-bit clock dividers generate digital system clocks for general use in the digital system, as configured by the design's requirements. Digital system clocks can generate custom clocks derived from any of the seven clock sources for any purpose. Examples include baud rate generators, accurate PWM periods, and timer clocks, and many others. If more than eight digital clock dividers are required, the Universal Digital Blocks (UDBs) and fixed function timer/counter/PWMs can also generate clocks.

- Four 16-bit clock dividers generate clocks for the analog system components that require clocking, such as ADC and mixers. The analog clock dividers include skew control to ensure that critical analog events do not occur simultaneously with digital switching events. This is done to reduce analog system noise.

Each clock divider consists of an 8-input multiplexer, a 16-bit clock divider (divide by 2 and higher) that generates ~50% duty cycle clocks, master clock resynchronization logic, and deglitch logic. The outputs from each digital clock tree can be routed into the digital system interconnect and then brought back into the clock system as an input, allowing clock chaining of up to 32 bits.

#### 6.1.4 USB Clock Domain

The USB clock domain is unique in that it operates largely asynchronously from the main clock network. The USB logic contains a synchronous bus interface to the chip, while running on an asynchronous clock to process USB data. The USB logic requires a 48 MHz frequency. This frequency can be generated from different sources, including DSI clock at 48 MHz or doubled value of 24 MHz from internal oscillator, DSI signal, or crystal oscillator.

#### Timer DMA IO Port Global Interrupt CAN I2C Counters Controller Controller Pins Clocks Digital System Routing I/F **UDB ARRAY** Digital System Routing I/F Global IO Port SC/CT EMIF Comparators Del-Sia DACs Clocks Blocks Pins

### Figure 7-9. Digital System Interconnect

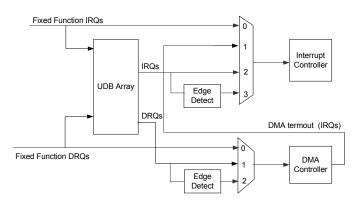

Interrupt and DMA routing is very flexible in the CY8C36 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

#### Figure 7-10. Interrupt and DMA Processing in the IDMUX

Interrupt and DMA Processing in IDMUX

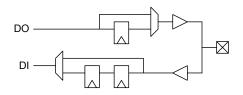

#### 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1 on page 28). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

#### Figure 7-11. I/O Pin Synchronization Routing

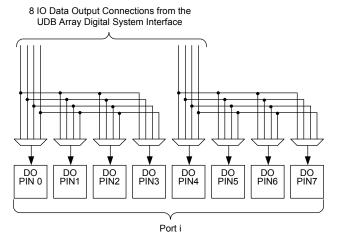

### Figure 7-12. I/O Pin Output Connectivity

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

Document Number: 001-53413 Rev. \*Y

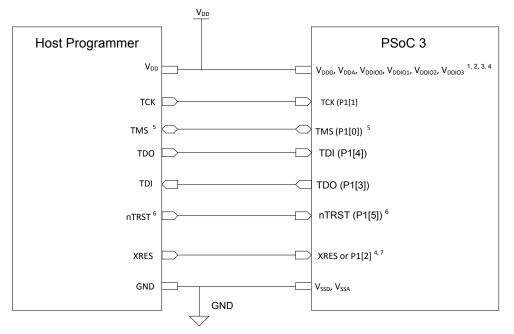

## 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

PSoC 3 has certain timing requirements to be met for entering programming mode through the JTAG interface. Due to these timing requirements, not all standard JTAG programmers, or standard JTAG file formats such as SVF or STAPL, can support

PSoC 3 programming. The list of programmers that support PSoC 3 programming is available at http://www.cypress.com/go/programming.

The JTAG clock frequency can be up to 14 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as GPIO instead.

#### Figure 9-1. JTAG Interface Connections between PSoC 3 and Programmer

The voltage levels of Host Programmer and the PSoC 3 voltage domains involved in Programming should be same. The Port 1 JTAG pins, XRES pin (XRES\_N or P1[2]) are powered by V<sub>DDI01</sub>. So, V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 3, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

<sup>5</sup> By default, PSoC 3 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 3 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controller during first time programming of PSoC 3 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

If XRES pin is used by host, P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

### Table 11-2. DC Specifications (continued)

| Parameter | Description                                                                                                          | Conditions                                                               |            | Min | Typ <sup>[29]</sup> | Max | Units |

|-----------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------|-----|---------------------|-----|-------|

|           | Sleep Mode <sup>[32]</sup>                                                                                           |                                                                          |            |     |                     |     |       |

|           | CPU = OFF                                                                                                            | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C | _   | 1.1                 | 2.3 | μA    |

|           | RTC = ON (= ECO32K ON, in low-power                                                                                  | 4.5 V - 5.5 V                                                            | T = 25 °C  | _   | 1.1                 | 2.2 |       |

|           | mode)<br>Sleep timer = ON (= ILO ON at 1 kHz) <sup>[33]</sup>                                                        |                                                                          | T = 85 °C  | _   | 15                  | 30  |       |

|           | WDT = OFF                                                                                                            | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C | _   | 1                   | 2.2 | _     |

|           | I <sup>2</sup> C Wake = OFF                                                                                          | 2.7 V – 3.6 V                                                            | T = 25 °C  | _   | 1                   | 2.1 |       |

|           | Comparator = OFF                                                                                                     |                                                                          | T = 85 °C  | _   | 12                  | 28  |       |

|           | POR = ON<br>Boost = OFF                                                                                              | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = 25 °C  | _   | 2.2                 | 4.2 |       |

|           | SIO pins in single ended input, unregulated output mode                                                              | 1                                                                        |            |     |                     |     |       |

|           | Comparator = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF                                          | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V <sup>[35]</sup>   | T = 25 °C  | _   | 2.2                 | 2.7 |       |

|           | I <sup>2</sup> C Wake = OFF<br>POR = ON<br>Boost = OFF<br>SIO pins in single ended input, unregulated<br>output mode |                                                                          |            |     |                     |     |       |

|           | I <sup>2</sup> C Wake = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF<br>Comparator = OFF           | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V <sup>[35]</sup>   | T = 25 °C  | -   | 2.2                 | 2.8 |       |

|           | POR = ON<br>Boost = OFF<br>SIO pins in single ended input, unregulated<br>output mode                                |                                                                          |            |     |                     |     |       |

|           | Hibernate Mode <sup>[32]</sup>                                                                                       |                                                                          |            |     |                     |     |       |

|           | Hibernate mode current                                                                                               | $V_{DD} = V_{DDIO} =$                                                    | T = -40 °C | -   | 0.2                 | 1.5 | μA    |

|           | All regulators and oscillators off<br>SRAM retention                                                                 | 4.5 V - 5.5 V                                                            | T = 25 °C  | -   | 0.5                 | 1.5 |       |

|           | GPIO interrupts are active                                                                                           |                                                                          | T = 85 °C  | -   | 4.1                 | 5.3 |       |

|           | Boost = OFF                                                                                                          | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C | -   | 0.2                 | 1.5 |       |

|           |                                                                                                                      | 2.7 V – 3.6 V                                                            | T = 25 °C  | -   | 0.2                 | 1.5 |       |

|           | output<br>mode                                                                                                       |                                                                          | T = 85 °C  | _   | 3.2                 | 4.2 |       |

|           |                                                                                                                      | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>1.71 V – 1.95 V <sup>[34]</sup> | T = -40 °C | -   | 0.2                 | 1.5 |       |

|           |                                                                                                                      | 1.71 V – 1.95 V <sup>[34]</sup>                                          | T = 25 °C  | -   | 0.3                 | 1.5 |       |

|           |                                                                                                                      |                                                                          | T = 85 °C  | _   | 3.3                 | 4.3 | 1     |

| DDAR      | Analog current consumption while device                                                                              | $V_{DDA} \le 3.6 V$                                                      | 1          | _   | 0.3                 | 0.6 | mA    |

|           | is reset <sup>[36]</sup>                                                                                             | V <sub>DDA</sub> > 3.6 V                                                 |            | _   | 1.4                 | 3.3 | mA    |

| DDR       | Digital current consumption while device is                                                                          | $V_{\text{DDD}} \le 3.6 \text{ V}$                                       |            | _   | 1.1                 | 3.1 | mA    |

|           | reset <sup>[36]</sup>                                                                                                | ·                                                                        |            |     |                     | 5.1 |       |

Notes

- If V<sub>CCD</sub> and V<sub>CCA</sub> are externally regulated, the voltage difference between V<sub>CCD</sub> and V<sub>CCA</sub> must be less than 50 mV.

Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

Externally regulated mode.

Based on device characterization (not production tested).

Based on device characterization (not production tested).

Based on device characterization (not production tested).

# Table 11-3. AC Specifications<sup>[37]</sup>

| Parameter              | Description                                                                                                               | Conditions                                                                                                 | Min | Тур | Max   | Units |

|------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

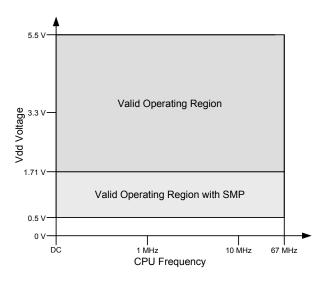

| F <sub>CPU</sub>       | CPU frequency                                                                                                             | $1.71~V \le V_{DDD} \le 5.5~V$                                                                             | DC  | -   | 67.01 | MHz   |

| F <sub>BUSCLK</sub>    | Bus frequency                                                                                                             | $1.71~V \le V_{DDD} \le 5.5~V$                                                                             | DC  | -   | 67.01 | MHz   |

| Svdd                   | V <sub>DD</sub> ramp rate                                                                                                 |                                                                                                            | -   | -   | 0.066 | V/µs  |

| T <sub>IO_INIT</sub>   | Time from $V_{DDD}/V_{DDA}/V_{CCD}/V_{CCA} \ge IPOR$ to I/O ports set to their reset states                               |                                                                                                            | -   | -   | 10    | μs    |

| T <sub>STARTUP</sub>   | Time from $V_{DDD}/V_{DDA}/V_{CCD}/V_{CCA} \ge PRES$ to CPU executing code at reset vector                                | $V_{CCA}/V_{DDA}$ = regulated from<br>$V_{DDA}/V_{DDD}$ , no PLL used, fast IMO<br>boot mode (48 MHz typ.) | -   | -   | 40    | μs    |

|                        |                                                                                                                           | $V_{CCA}/V_{CCD}$ = regulated from<br>$V_{DDA}/V_{DDD}$ , no PLL used, slow<br>IMO boot mode (12 MHz typ.) | _   | -   | 74    | μs    |

| T <sub>SLEEP</sub>     | Wakeup from sleep mode –<br>Application of non–LVD interrupt to<br>beginning of execution of next CPU<br>instruction      |                                                                                                            | _   | -   | 15    | μs    |

| T <sub>HIBERNATE</sub> | Wakeup from hibernate mode –<br>Application of external interrupt to<br>beginning of execution of next CPU<br>instruction |                                                                                                            | -   | -   | 100   | μs    |

Figure 11-4. F<sub>CPU</sub> vs. V<sub>DD</sub>

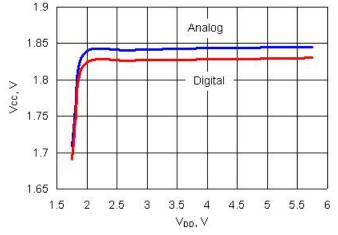

## **11.3 Power Regulators**

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.3.1 Digital Core Regulator

### Table 11-4. Digital Core Regulator DC Specifications

| Parameter        | Description                | Conditions                                                                                                                                               | Min | Тур  | Max | Units |

|------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| V <sub>DDD</sub> | Input voltage              |                                                                                                                                                          | 1.8 | -    | 5.5 | V     |

| V <sub>CCD</sub> | Output voltage             |                                                                                                                                                          | -   | 1.80 | -   | V     |

|                  | Regulator output capacitor | $\pm$ 10%, ×5R ceramic or better. The two V <sub>CCD</sub> pins must be shorted together, with as short a trace as possible, see Power System on page 31 | 0.9 | 1    | 1.1 | μF    |

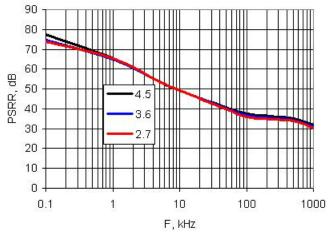

### Figure 11-6. Digital Regulator PSRR vs Frequency and V<sub>DD</sub>

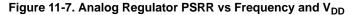

### 11.3.2 Analog Core Regulator

### Table 11-5. Analog Core Regulator DC Specifications

| Parameter        | Description                | Conditions                  | Min | Тур  | Max | Units |

|------------------|----------------------------|-----------------------------|-----|------|-----|-------|

| V <sub>DDA</sub> | Input voltage              |                             | 1.8 | -    | 5.5 | V     |

| V <sub>CCA</sub> | Output voltage             |                             | -   | 1.80 | -   | V     |

|                  | Regulator output capacitor | ±10%, ×5R ceramic or better | 0.9 | 1    | 1.1 | μF    |

## Table 11-13. SIO Comparator Specifications<sup>[49]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | -   | -   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | -   | -   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | -   | -   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | -   | 250 | µV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | -   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | -   | -   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | -   | _   |       |

| Tresp     | Response time                  |                           | -   | -   | 30  | ns    |

### 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 72.

## Table 11-14. USBIO DC Specifications

| Parameter                       | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|---------------------------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                           | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | -   | 1.575          | kΩ    |

| Rusba                           | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | -   | 3.090          | kΩ    |

| Vohusb                          | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | -   | 3.6            | V     |

| Volusb                          | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | -              | -   | 0.3            | V     |

| Vihgpio                         | Input voltage high, GPIO mode          | $V_{DDD} \ge 3 V$                                  | 2              | _   | _              | V     |

| Vilgpio                         | Input voltage low, GPIO mode           | $V_{DDD} \ge 3 V$                                  | _              | -   | 0.8            | V     |

| Vohgpio                         | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 V$                 | 2.4            | -   | -              | V     |

| Volgpio                         | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 V$                 | -              | _   | 0.3            | V     |

| Vdi                             | Differential input sensitivity         | (D+)(D)                                            | _              | -   | 0.2            | V     |

| Vcm                             | Differential input common mode range   | -                                                  | 0.8            | -   | 2.5            | V     |

| Vse                             | Single ended receiver threshold        | -                                                  | 0.8            | _   | 2              | V     |

| Rps2                            | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | -   | 7              | kΩ    |

| Rext                            | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                              | USB driver output impedance            | Including Rext                                     | 28             | -   | 44             | Ω     |

| C <sub>IN</sub>                 | USB transceiver input capacitance      |                                                    | -              | -   | 20             | pF    |

| I <sub>IL</sub> <sup>[49]</sup> | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | _              | -   | 2              | nA    |

### Table 11-28. IDAC DC Specifications (continued)

| Parameter       | Description                          | Conditions                                                                                            | Min | Тур  | Max  | Units  |

|-----------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|-----|------|------|--------|

| Ezs             | Zero scale error                     |                                                                                                       | _   | 0    | ±1   | LSB    |

| Eg              | Gain error                           | Range = 2.04 mA, 25 °C                                                                                | -   | -    | ±2.5 | %      |

|                 |                                      | Range = 255 µA, 25 ° C                                                                                | -   | -    | ±2.5 | %      |

|                 |                                      | Range = 31.875 µA, 25 ° C                                                                             | _   | -    | ±3.5 | %      |

| TC_Eg           | Temperature coefficient of gain      | Range = 2.04 mA                                                                                       | -   | -    | 0.04 | % / °C |

|                 | error                                | Range = 255 µA                                                                                        | _   | -    | 0.04 | % / °C |

|                 |                                      | Range = 31.875 µA                                                                                     | _   | -    | 0.05 | % / °C |

| INL             | Integral nonlinearity                | Sink mode, range = $255 \mu$ A, Codes<br>8 – 255, Rload = 2.4 k $\Omega$ , Cload =<br>15 pF           | _   | ±0.9 | ±1   | LSB    |

|                 |                                      | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 k $\Omega$ ,<br>Cload = 15 pF         | -   | ±1.2 | ±1.6 | LSB    |

| DNL             | Differential nonlinearity            | Sink mode, range = 255 $\mu$ A, Rload<br>= 2.4 k $\Omega$ , Cload = 15 pF                             | -   | ±0.3 | ±1   | LSB    |

|                 |                                      | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 k $\Omega$ , Cload = 15 pF                           | -   | ±0.3 | ±1   | LSB    |

| Vcompliance     | Dropout voltage, source or sink mode | Voltage headroom at max current, Rload to $V_{DDA}$ or Rload to $V_{SSA}$ , $V_{DIFF}$ from $V_{DDA}$ | 1   | -    | _    | V      |

| I <sub>DD</sub> | Operating current, code = 0          | Low speed mode, source mode, range = 31.875 µA                                                        | -   | 44   | 100  | μA     |

|                 |                                      | Low speed mode, source mode, range = 255 µA,                                                          | -   | 33   | 100  | μA     |

|                 |                                      | Low speed mode, source mode,<br>range = 2.04 mA                                                       | -   | 33   | 100  | μA     |

|                 |                                      | Low speed mode, sink mode, range = 31.875 µA                                                          | -   | 36   | 100  | μA     |

|                 |                                      | Low speed mode, sink mode, range = 255 μA                                                             | -   | 33   | 100  | μA     |

|                 |                                      | Low speed mode, sink mode,<br>range = 2.04 mA                                                         | -   | 33   | 100  | μA     |

|                 |                                      | High speed mode, source mode, range = 31.875 μA                                                       | -   | 310  | 500  | μA     |

|                 |                                      | High speed mode, source mode, range = 255 $\mu$ A                                                     | -   | 305  | 500  | μA     |

|                 |                                      | High speed mode, source mode,<br>range = 2.04 mA                                                      | _   | 305  | 500  | μA     |

|                 |                                      | High speed mode, sink mode,<br>range = 31.875 μA                                                      | -   | 310  | 500  | μA     |

|                 |                                      | High speed mode, sink mode, range = 255 $\mu$ A                                                       | -   | 300  | 500  | μA     |

|                 |                                      | High speed mode, sink mode, range = 2.04 mA                                                           | _   | 300  | 500  | μA     |

### 11.5.8 Mixer

The mixer is created using a SC/CT analog block; see the Mixer component data sheet in PSoC Creator for full electrical specifications and APIs.

### Table 11-32. Mixer DC Specifications

| Parameter       | Description          | Conditions | Min | Тур | Max | Units |

|-----------------|----------------------|------------|-----|-----|-----|-------|

| V <sub>OS</sub> | Input offset voltage |            | -   | -   | 15  | mV    |

|                 | Quiescent current    |            | -   | 0.9 | 2   | mA    |

| G               | Gain                 |            | _   | 0   | -   | dB    |

#### Table 11-33. Mixer AC Specifications<sup>[63]</sup>

| Parameter       | Description                | Conditions      | Min | Тур | Max | Units |

|-----------------|----------------------------|-----------------|-----|-----|-----|-------|

| f <sub>LO</sub> | Local oscillator frequency | Down mixer mode | -   | -   | 4   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Down mixer mode | -   | -   | 14  | MHz   |

| f <sub>LO</sub> | Local oscillator frequency | Up mixer mode   | -   | -   | 1   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Up mixer mode   | -   | -   | 1   | MHz   |

| SR              | Slew rate                  |                 | 3   | _   | _   | V/µs  |

#### 11.5.9 Transimpedance Amplifier

The TIA is created using a SC/CT analog block; see the TIA component data sheet in PSoC Creator for full electrical specifications and APIs.

#### Table 11-34. Transimpedance Amplifier (TIA) DC Specifications

| Parameter         | Description                           | Conditions           | Min | Тур | Max | Units |

|-------------------|---------------------------------------|----------------------|-----|-----|-----|-------|

| V <sub>IOFF</sub> | Input offset voltage                  |                      | -   | -   | 10  | mV    |

| Rconv             | Conversion resistance <sup>[64]</sup> | R = 20K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 30K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 40K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 80K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 120K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R = 250K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R= 500K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 1M; 40 pF load   | -25 | -   | +35 | %     |

|                   | Quiescent current                     |                      | _   | 1.1 | 2   | mA    |

#### Table 11-35. Transimpedance Amplifier (TIA) AC Specifications

| Parameter | Description             | Conditions           | Min  | Тур | Max | Units |

|-----------|-------------------------|----------------------|------|-----|-----|-------|

| BW        | Input bandwidth (-3 dB) | R = 20K; –40 pF load | 1500 | -   | -   | kHz   |

|           |                         | R = 120K;40 pF load  | 240  | _   | _   | kHz   |

|           |                         | R = 1M; –40 pF load  | 25   | -   | -   | kHz   |

Notes

<sup>63.</sup> Based on device characterization (Not production tested).

<sup>64.</sup> Conversion resistance values are not calibrated. Calibrated values and details about calibration are provided in PSoC Creator component data sheets. External precision resistors can also be used.

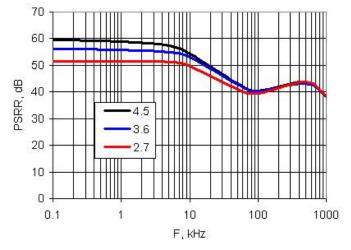

### 11.5.10 Programmable Gain Amplifier

The PGA is created using a SC/CT analog block; see the PGA component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, operating conditions are:

- Operating temperature = 25 °C for typical values

- Unless otherwise specified, all charts and graphs show typical values

### Table 11-36. PGA DC Specifications

| Parameter | Description                                 | Conditions                                                                        | Min                    | Тур | Max                     | Units       |

|-----------|---------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-----|-------------------------|-------------|

| Vin       | Input voltage range                         | Power mode = minimum                                                              | V <sub>SSA</sub>       | _   | V <sub>DDA</sub>        | V           |

| Vos       | Input offset voltage                        | Power mode = high,<br>gain = 1                                                    | -                      | -   | 10                      | mV          |

| TCVos     | Input offset voltage drift with temperature | Power mode = high,<br>gain = 1                                                    | -                      | -   | ±30                     | µV/°C       |

| Ge1       | Gain error, gain = 1                        |                                                                                   | _                      | -   | ±0.15                   | %           |

| Ge16      | Gain error, gain = 16                       |                                                                                   | -                      | _   | ±2.5                    | %           |

| Ge50      | Gain error, gain = 50                       |                                                                                   | -                      | _   | ±5                      | %           |

| Vonl      | DC output nonlinearity                      | Gain = 1                                                                          | -                      | -   | ±0.01                   | % of<br>FSR |

| Cin       | Input capacitance                           |                                                                                   | -                      | _   | 7                       | pF          |

| Voh       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | V <sub>DDA</sub> -0.15 | -   | _                       | V           |

| Vol       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | -                      | -   | V <sub>SSA</sub> + 0.15 | V           |

| Vsrc      | Output voltage under load                   | lload = 250 µA, $V_{DDA} ≥$ 2.7 V, power mode = high                              | -                      | -   | 300                     | mV          |

| ldd       | Operating current                           | Power mode = high                                                                 | _                      | 1.5 | 1.65                    | mA          |

| PSRR      | Power supply rejection ratio                |                                                                                   | 48                     | -   | _                       | dB          |

Figure 11-62. PGA Voffset Histogram, 4096 samples/ 1024 parts

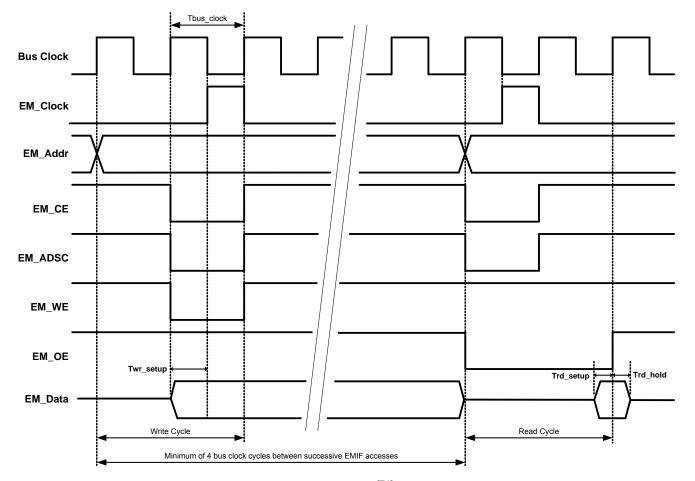

Figure 11-67. Synchronous Write and Read Cycle Timing, No Wait States

## Table 11-64. Synchronous Write and Read Timing Specifications<sup>[71]</sup>

| Parameter  | Description                                                    | Conditions | Min             | Тур | Max | Units |

|------------|----------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[72]</sup>                            |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[73]</sup>                               |            | 30.3            | -   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock             |            | Tbus_clock – 10 | -   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before<br>rising edge of EM_OE |            | 5               | -   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE     |            | 5               | -   | _   | ns    |

#### Notes

- 71. Based on device characterization (Not production tested).

72. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 80.

73. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

### 11.8 PSoC System Resources

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.8.1 POR with Brown Out

For brown out detect in regulated mode,  $V_{DDD}$  and  $V_{DDA}$  must be  $\geq$  2.0 V. Brown out detect is not available in externally regulated mode.

#### Table 11-65. Precise Low-Voltage Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | _   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | 1   | 1.66 | V     |

### Table 11-66. Power On Reset (POR) with Brown Out AC Specifications

| Parameter | Description                                   | Conditions | Min | Тур | Max | Units |  |

|-----------|-----------------------------------------------|------------|-----|-----|-----|-------|--|

| PRES_TR   | Response time                                 |            | -   | _   | 0.5 | μs    |  |

|           | V <sub>DDD</sub> /V <sub>DDA</sub> droop rate | Sleep mode | -   | 5   | -   | V/sec |  |

#### 11.8.2 Voltage Monitors

### Table 11-67. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Мах  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            | _    | -    | _    | -     |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

### Table 11-68. Voltage Monitors AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------------|------------|-----|-----|-----|-------|

|           | Response time <sup>[74]</sup> |            | _   | -   | 1   | μs    |

# **12. Ordering Information**

In addition to the features listed in Table 12-1, every CY8C36 device includes: a precision on-chip voltage reference, precision oscillators, flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and analog subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C36 derivatives incorporate device and flash security in user-selectable security levels; see the TRM for details.

|                 | Ν               | NCU        | Со        | re          |                   |                | An  | alog       |                                        |        | Digital |          |                      |                  |        | I/O[     | 88]       |      |     |       |              |                         |

|-----------------|-----------------|------------|-----------|-------------|-------------------|----------------|-----|------------|----------------------------------------|--------|---------|----------|----------------------|------------------|--------|----------|-----------|------|-----|-------|--------------|-------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT<br>Analog Blocks <sup>[86]</sup> | Opamps | DFB     | CapSense | UDBs <sup>[87]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O | GPIO | SIO | USBIO | Package      | JTAG ID <sup>[89]</sup> |

| 32 KB Flash     |                 |            |           |             |                   |                |     | _          |                                        |        |         |          | _                    |                  |        |          |           |      |     |       |              | -                       |

| CY8C3665PVI-008 | 67              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 2      | >       | >        | 20                   | 4                | -      | -        | 29        | 25   | 4   | 0     | 48-pin SSOP  | 0×1E008069              |

| CY8C3665AXI-198 | 67              | 32         | 8         | 1           | ~                 | 12-bit Del-Sig | 2   | 0          | 0                                      | 0      | Ι       | 2        | 16                   | 0                | Ι      | -        | 70        | 62   | 8   | 0     | 100-pin TQFP | 0x1E0C6069              |

| CY8C3665LTI-044 | 67              | 32         | 4         | 1           | ٢                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 0      | ~       | ~        | 20                   | 4                | ٢      | Ι        | 48        | 38   | 8   | 2     | 68-pin QFN   | 0x1E02C069              |

| CY8C3665LTI-199 | 67              | 32         | 8         | 1           | ٢                 | 12-bit Del-Sig | 2   | 0          | 0                                      | 0      | -       | ~        | 16                   | 0                | Ι      | Ι        | 46        | 38   | 8   | 0     | 68-pin QFN   | 0x1E0C7069              |

| CY8C3665FNI-211 | 67              | 32         | 4         | 1           | ~                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~       | ~        | 20                   | 4                | ~      | -        | 48        | 38   | 8   | 2     | 72 WLCSP     | 0x1E0D3069              |

| 64 KB Flash     |                 |            |           |             |                   |                |     |            |                                        |        |         |          |                      |                  |        |          |           |      |     |       |              |                         |

| CY8C3666AXI-052 | 67              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 4      | 2       | 2        | 24                   | 4                | Ι      | -        | 70        | 62   | 8   | 0     | 100-pin TQFP | 0×1E034069              |

| CY8C3666AXI-036 | 67              | 64         | 8         | 2           | ٢                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~       | ~        | 24                   | 4                | ٢      | -        | 72        | 62   | 8   | 2     | 100-pin TQFP | 0×1E024069              |

| CY8C3666LTI-027 | 67              | 64         | 8         | 2           | ٢                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~       | ~        | 24                   | 4                | ٢      | Ι        | 48        | 38   | 8   | 2     | 68-pin QFN   | 0×1E01B069              |

| CY8C3666LTI-050 | 67              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 2      | ~       | ~        | 24                   | 4                | ~      | -        | 31        | 25   | 4   | 2     | 48-pin QFN   | 0×1E032069              |

| CY8C3666AXI-037 | 67              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 4   | 4          | 4                                      | 4      | ~       | ~        | 24                   | 4                | -      | ~        | 70        | 62   | 8   | 0     | 100-pin TQFP | 0×1E025069              |

| CY8C3666AXI-200 | 67              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 2          | 0                                      | 2      | -       | ~        | 20                   | 2                | -      | -        | 70        | 62   | 8   | 0     | 100-pin TQFP | 0x1E0C8069              |

| CY8C3666LTI-201 | 67              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 2   | 2          | 0                                      | 2      | -       | ~        | 20                   | 2                | -      | -        | 46        | 38   | 8   | 0     | 68-pin QFN   | 0x1E0C9069              |

| CY8C3666AXI-202 | 67              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 4   | 2          | 2                                      | 2      | Ι       | 2        | 24                   | 4                | -      | -        | 70        | 62   | 8   | 0     | 100-pin TQFP | 0x1E0CA069              |

| CY8C3666LTI-203 | 67              | 64         | 8         | 2           | ~                 | 12-bit Del-Sig | 4   | 2          | 2                                      | 2      | -       | 1        | 24                   | 4                | -      | -        | 46        | 38   | 8   | 0     | 68-pin QFN   | 0x1E0CB069              |

Table 12-1. CY8C36 Family with Single Cycle 8051

Notes

86. Analog blocks support a wide variety of functionality including TIA, PGA, and mixers. See the Example Peripherals on page 44 for more information on how analog blocks can be used.

87. UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See the Example Peripherals on page 44 for more information on how UDBs can be used.

88. The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See the I/O System and Routing on page 37 for details on the functionality of each of these types of I/O.

89. The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

# 13. Packaging

## Table 13-1. Package Characteristics

| Parameter       | Description                          | Conditions | Min | Тур   | Max | Units   |

|-----------------|--------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub>  | Operating ambient temperature        |            | -40 | 25.00 | 85  | °C      |

| TJ              | Operating junction temperature       |            | -40 | -     | 100 | °C      |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin SSOP)  |            | -   | 49    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (48-pin QFN)   |            | -   | 14    | I   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (68-pin QFN)   |            | -   | 15    | I   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (100-pin TQFP) |            | -   | 34    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin SSOP)  |            | -   | 24    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (48-pin QFN)   |            | -   | 15    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (68-pin QFN)   |            | -   | 13    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (100-pin TQFP) |            | -   | 10    | -   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (72-pin CSP)   |            | -   | 18    | -   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (72-pin CSP)   |            | _   | 0.13  | -   | °C/Watt |

## Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

| 72-pin CSP   | 260 °C                      | 30 seconds                          |

### Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 72-pin CSP   | MSL 1 |

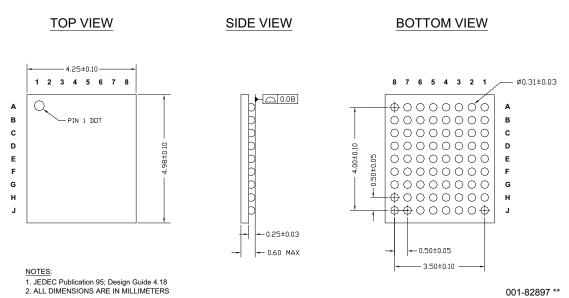

Figure 13-5. WLCSP Package (4.25 × 4.98 × 0.60 mm)

# 18. Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| Automotive               | cypress.com/go/automotive |

|--------------------------|---------------------------|

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

## **PSoC<sup>®</sup> Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

© Cypress Semiconductor Corporation, 2009-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and ober countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-53413 Rev. \*Y

Revised June 27, 2016

ARM is a registered trademark, and Keil, and RealView are trademarks, of ARM Limited.