Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                                |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 4x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 48-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3665pvi-008t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Mnemonic Description |               | Description                           | Bytes | Cycles |

|----------------------|---------------|---------------------------------------|-------|--------|

| ORL                  | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL                  | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL                  | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL                  | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL                  | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL                  | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL                  | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL                  | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL                  | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR                  | A             | Clear accumulator                     | 1     | 1      |

| CPL                  | А             | Complement accumulator                | 1     | 1      |

| RL                   | А             | Rotate accumulator left               | 1     | 1      |

| RLC                  | А             | Rotate accumulator left through carry | 1     | 1      |

| RR                   | А             | Rotate accumulator right              | 1     | 1      |

| RRC                  | А             | Rotate accumulator right though carry | 1     | 1      |

| SWAF                 | PA            | Swap nibbles within accumulator       | 1     | 1      |

## Table 4-2. Logical Instructions (continued)

## 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed addressing mode. Table 4-3 lists the various data transfer instructions available.

## 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit-addressable memory location. It has 128 bits of bit addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 on page 17 lists the available Boolean instructions.

## Table 4-3. Data Transfer Instructions

|     | Mnemonic       | Description                        | Bytes | Cycles |

|-----|----------------|------------------------------------|-------|--------|

| MOV | A,Rn           | Move register to accumulator       | 1     | 1      |

| MOV | A,Direct       | Move direct byte to accumulator    | 2     | 2      |

| MOV | A,@Ri          | Move indirect RAM to accumulator   | 1     | 2      |

| MOV | A,#data        | Move immediate data to accumulator | 2     | 2      |

| MOV | Rn,A           | Move accumulator to register       | 1     | 1      |

| MOV | Rn,Direct      | Move direct byte to register       | 2     | 3      |

| MOV | Rn, #data      | Move immediate data to register    | 2     | 2      |

| MOV | Direct, A      | Move accumulator to direct byte    | 2     | 2      |

| MOV | Direct, Rn     | Move register to direct byte       | 2     | 2      |

| MOV | Direct, Direct | Move direct byte to direct byte    | 3     | 3      |

| MOV | Direct, @Ri    | Move indirect RAM to direct byte   | 2     | 3      |

| MOV | Direct, #data  | Move immediate data to direct byte | 3     | 3      |

| MOV | @Ri, A         | Move accumulator to indirect RAM   | 1     | 2      |

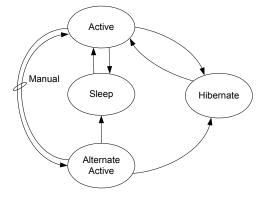

Figure 6-5. Power Mode Transitions

## 6.2.1.1 Active Mode

Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled or disabled. When a resource is disabled, the digital clocks are gated, analog bias currents are disabled, and leakage currents are reduced as appropriate. User firmware can dynamically control subsystem power by setting and clearing bits in the active configuration template. The CPU can disable itself, in which case the CPU is automatically reenabled at the next wakeup event.

When a wakeup event occurs, the global mode is always returned to active, and the CPU is automatically enabled, regardless of its template settings. Active mode is the default global power mode upon boot.

#### 6.2.1.2 Alternate Active Mode

Alternate Active mode is very similar to Active mode. In alternate active mode, fewer subsystems are enabled, to reduce power consumption. One possible configuration is to turn off the CPU and flash, and run peripherals at full speed.

#### 6.2.1.3 Sleep Mode

Sleep mode reduces power consumption when a resume time of 15  $\mu$ s is acceptable. The wake time is used to ensure that the regulator outputs are stable enough to directly enter active mode.

## 6.2.1.4 Hibernate Mode

In hibernate mode nearly all of the internal functions are disabled. Internal voltages are reduced to the minimal level to keep vital systems alive. Configuration state is preserved in hibernate mode and SRAM memory is retained. GPIOs configured as digital outputs maintain their previous values and external GPIO pin interrupt settings are preserved. The device can only return from hibernate mode in response to an external I/O interrupt. The resume time from hibernate mode is less than 100 µs.

To achieve an extremely low current, the hibernate regulator has limited capacity. This limits the frequency of any signal present on the input pins - no GPIO should toggle at a rate greater than 10 kHz while in hibernate mode. If pins must be toggled at a high rate while in a low power mode, use sleep mode instead.

## 6.2.1.5 Wakeup Events

Wakeup events are configurable and can come from an interrupt or device reset. A wakeup event restores the system to active mode. Firmware enabled interrupt sources include internally generated interrupts, power supervisor, central timewheel, and I/O interrupts. Internal interrupt sources can come from a variety of peripherals, such as analog comparators and UDBs. The central timewheel provides periodic interrupts to allow the system to wake up, poll peripherals, or perform real-time functions. Reset event sources include the external reset I/O pin (XRES), WDT, and precision reset (PRES).

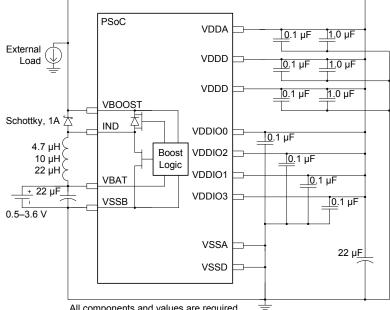

#### 6.2.2 Boost Converter

Applications that use a supply voltage of less than 1.71 V, such as solar panels or single cell battery supplies, may use the on-chip boost converter to generate a minimum of 1.8 V supply voltage. The boost converter may also be used in any system that requires a higher operating voltage than the supply provides such as driving 5.0 V LCD glass in a 3.3 V system. With the addition of an inductor, Schottky diode, and capacitors, it produces a selectable output voltage sourcing enough current to operate the PSoC and other on-board components.

The boost converter accepts an input voltage  $V_{BAT}$  from 0.5 V to 3.6 V, and can start up with  $V_{BAT}$  as low as 0.5 V. The converter provides a user configurable output voltage of 1.8 to 5.0 V ( $V_{OUT}$ ) in 100 mV increments.  $V_{BAT}$  is typically less than  $V_{OUT}$ ; if  $V_{BAT}$  is greater than or equal to  $V_{OUT}$ , then  $V_{OUT}$  will be slightly less than  $V_{BAT}$  due to resistive losses in the boost converter. The block can deliver up to 50 mA ( $I_{BOOST}$ ) depending on configuration to both the PSoC device and external components. The sum of all current sinks in the design including the PSoC device, PSoC I/O pin loads, and external component loads must be less than the  $I_{BOOST}$  specified maximum current.

Four pins are associated with the boost converter: VBAT, VSSB, VBOOST, and IND. The boosted output voltage is sensed at the VBOOST pin and must be connected directly to the chip's supply inputs; VDDA, VDDD, and VDDIO if used to power the PSoC device.

The boost converter requires four components in addition to those required in a non-boost design, as shown in Figure 6-6 on page 34. A 22  $\mu$ F capacitor (C<sub>BAT</sub>) is required close to the VBAT pin to provide local bulk storage of the battery voltage and provide regulator stability. A diode between the battery and VBAT pin should not be used for reverse polarity protection because the diodes forward voltage drop reduces the V<sub>BAT</sub> voltage. Between the VBAT and IND pins, an inductor of 4.7 µH, 10 µH, or 22 µH is required. The inductor value can be optimized to increase the boost converter efficiency based on input voltage, output voltage, temperature, and current. Inductor size is determined by following the design guidance in this chapter and electrical specifications. The inductor must be placed within 1 cm of the VBAT and IND pins and have a minimum saturation current of 750 mA. Between the IND and VBOOST pins a Schottky diode must be placed within 1 cm of the pins. The Schottky diode shall have a forward current rating of at least 1.0 A and a reverse voltage of at least 20 V. A 22 µF bulk capacitor (CBOOST) must be connected close to VBOOST to provide regulator output stability. It is important to sum the total capacitance connected to the VBOOST pin and ensure the maximum C<sub>BOOST</sub> specification is not exceeded. All capacitors

must be rated for a minimum of 10 V to minimize capacitive losses due to voltage de-rating.

Figure 6-6. Application of Boost Converter powering PSoC device

All components and values are required

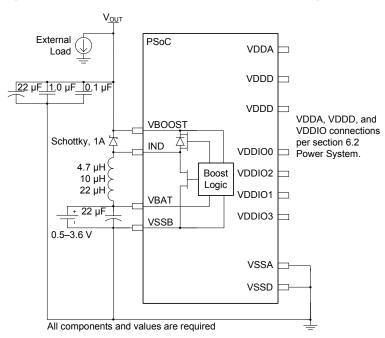

The boost converter may also generate a supply that is not used directly by the PSoC device. An example of this use case is boosting a 1.8 V supply to 4.0 V to drive a white LED. If the boost converter is not supplying the PSoC devices V<sub>DDA</sub>, V<sub>DDD</sub>, and V<sub>DDIO</sub> it must comply with the same design rules as supplying the PSoC device, but with a change to the bulk capacitor requirements. A parallel arrangement 22 µF, 1.0 µF, and 0.1 µF capacitors are all required on the Vout supply and must be placed within 1 cm of the VBOOST pin to ensure regulator stability.

#### Figure 6-7. Application of Boost Converter not powering PSoC device

| Digital Input Path PRT[x]CTL PRT[x]DBL_SYNC_IN                                                                                                           | Naming Convention<br>'x' = Port Number<br>'y' = Pin Number |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----|

| PRT[x]PS Digital System Input                                                                                                                            |                                                            |    |

| PICU[x]INTTYPE[y]  PICU[x]INTSTAT  Pin Interrupt Signal  PICU[x]INTSTAT                                                                                  | Input Buffer Disable                                       |    |

| Digital Output Path  PRT[x]SLW PRT[x]SYNC_OUT  PRT[x]DR  Digital System Output PRT[x]BYP  PRT[x]DM2 PRT[x]DM1 PRT[x]DM0  Bidirectional Control PRT[x]BIE | Vddio Vddio<br>In<br>Drive<br>Logic<br>OE                  | PI |

| Analog                                                                                                                                                   | Switches                                                   |    |

| PRT[x]LCD_COM_SEG<br>_PRT[x]LCD_EN<br>5                                                                                                                  | Display<br>Data<br>Logic & MUX                             |    |

## Figure 6-9. GPIO Block Diagram

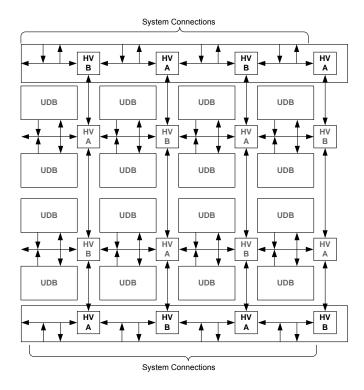

## 7.3 UDB Array Description

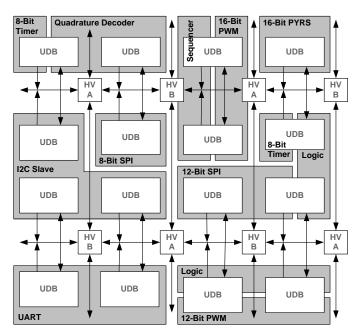

Figure 7-7 shows an example of a 16-UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

#### Figure 7-7. Digital System Interface Structure

#### 7.3.1 UDB Array Programmable Resources

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

Figure 7-8. Function Mapping Example in a Bank of UDBs

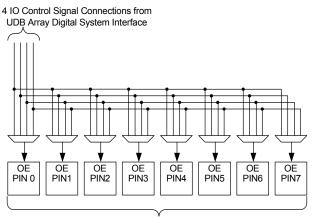

## 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-9 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

#### Figure 7-13. I/O Pin Output Enable Connectivity

#### Port i

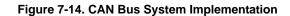

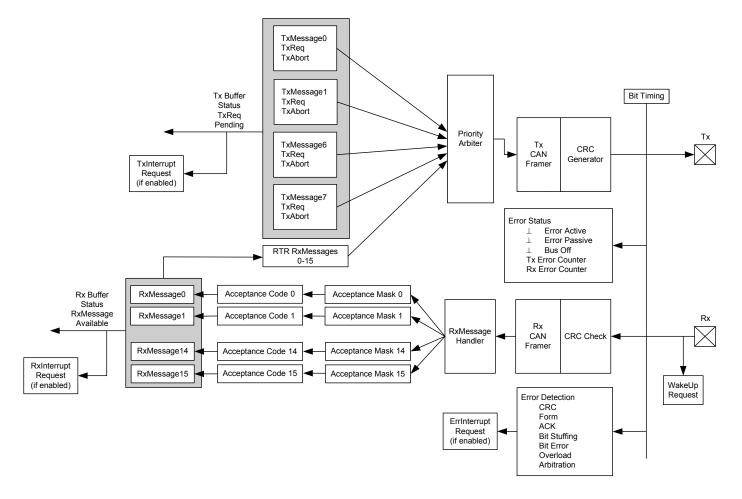

## 7.5 CAN

The CAN peripheral is a fully functional CAN supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level protocols without affecting the performance of the microcontroller CPU. Full configuration support is provided in PSoC Creator.

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

- Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

CAN receive and transmit buffers status

- CAN controller error status including BusOff

- Receive path

- □ 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE, and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- Automatic transmission request (RTR) response handler

Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- · Fixed priority

- Message transmissions abort capability

#### 7.5.2 Software Tools Support

- CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

Figure 7-15. CAN Controller Block Diagram

## 7.8 I<sup>2</sup>C

PSoC includes a single fixed-function  $I^2C$  peripheral. Additional  $I^2C$  interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[20]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead,  $I^2C$  specific support is provided for status detection and generation of framing bits.  $I^2C$  operates as a slave, a master, or multimaster (Slave and Master) $I^{21}$ . In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions.  $I^2C$  interfaces through DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup

address match. If wakeup

functionality is required, I<sup>2</sup>C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 12.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

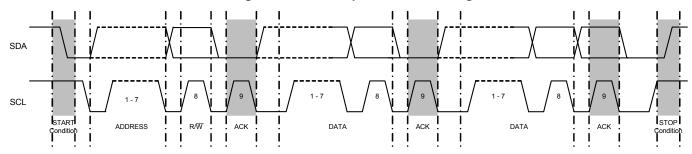

Data transfers follow the format shown in Figure 7-18. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

#### Figure 7-18. I<sup>2</sup>C Complete Transfer Timing

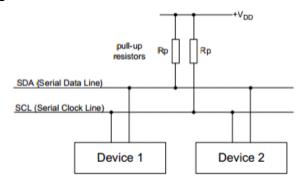

#### 7.8.1 External Electrical Connections

As Figure 7-19 shows, the  $I^2C$  bus requires external pull-up resistors (R<sub>P</sub>). These resistors are primarily determined by the supply voltage, bus speed, and bus capacitance. For detailed information on how to calculate the optimum pull-up resistor value for your design, we recommend using the UM10204 I2C-bus specification and user manual Rev 6, or newer, available from the NXP website at www.nxp.com.

#### Figure 7-19. Connection of Devices to the I<sup>2</sup>C Bus

Notes

- 20. The I<sup>2</sup>C peripheral is non-compliant with the NXP I<sup>2</sup>C specification in the following areas: analog glitch filter, I/O V<sub>OL</sub>/I<sub>OL</sub>, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 80 for details.

- 21. Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I2C component should be used instead.

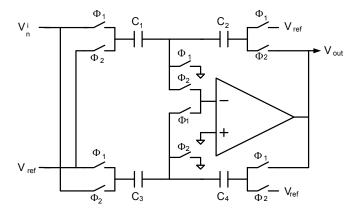

## 8.11 Sample and Hold

The main application for a sample and hold, is to hold a value stable while an ADC is performing a conversion. Some applications require multiple signals to be sampled simultaneously, such as for power calculations (V and I).

## Figure 8-13. Sample and Hold Topology ( $\Phi$ 1 and $\Phi$ 2 are opposite phases of a clock)

#### 8.11.1 Down Mixer

The SC/CT block can be used as a mixer to down convert an input signal. This circuit is a high bandwidth passive sample network that can sample input signals up to 14 MHz. This sampled value is then held using the opamp with a maximum clock rate of 4 MHz. The output frequency is at the difference between the input frequency and the highest integer multiple of the Local Oscillator that is less than the input.

#### 8.11.2 First Order Modulator - SC Mode

A first order modulator is constructed by placing the SC/CT block in an integrator mode and using a comparator to provide a 1-bit feedback to the input. Depending on this bit, a reference voltage is either subtracted or added to the input signal. The block output is the output of the comparator and not the integrator in the modulator case. The signal is downshifted and buffered and then processed by a decimator to make a delta-sigma converter or a counter to make an incremental converter. The accuracy of the sampled data from the first-order modulator is determined from several factors.

The main application for this modulator is for a low frequency ADC with high accuracy. Applications include strain gauges, thermocouples, precision voltage, and current measurement.

## 9. Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

For more information on PSoC 3 Programming, refer to the  $PSoC^{\textcircled{R}}$  3 Device Programming Specifications.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because the you cannot access the device later. Because all programming, debug, and test interfaces are disabled when Device Security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

#### Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

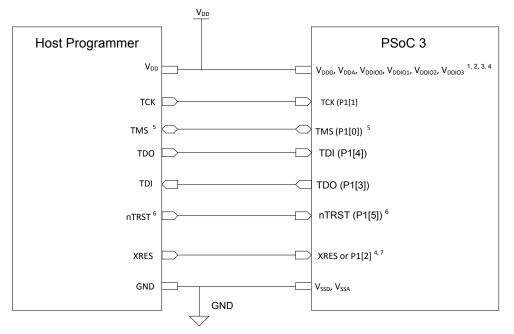

## 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

PSoC 3 has certain timing requirements to be met for entering programming mode through the JTAG interface. Due to these timing requirements, not all standard JTAG programmers, or standard JTAG file formats such as SVF or STAPL, can support

PSoC 3 programming. The list of programmers that support PSoC 3 programming is available at http://www.cypress.com/go/programming.

The JTAG clock frequency can be up to 14 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as GPIO instead.

#### Figure 9-1. JTAG Interface Connections between PSoC 3 and Programmer

The voltage levels of Host Programmer and the PSoC 3 voltage domains involved in Programming should be same. The Port 1 JTAG pins, XRES pin (XRES\_N or P1[2]) are powered by V<sub>DDI01</sub>. So, V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 3, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

<sup>5</sup> By default, PSoC 3 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 3 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controller during first time programming of PSoC 3 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

If XRES pin is used by host, P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

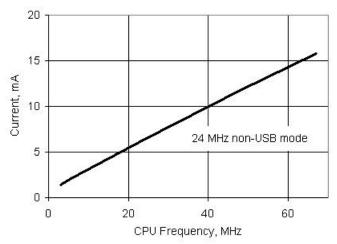

Figure 11-1. Active Mode Current vs  $F_{CPU}$ ,  $V_{DD}$  = 3.3 V, Temperature = 25 °C

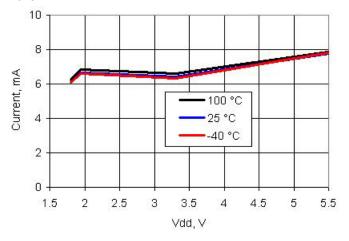

Figure 11-3. Active Mode Current vs  $V_{\text{DD}}$  and Temperature,  $F_{\text{CPU}}$  = 24 MHz

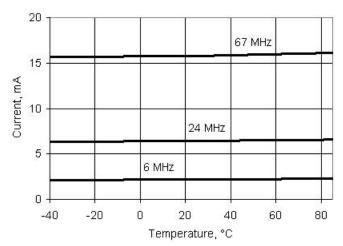

Figure 11-2. Active Mode Current vs Temperature and  $F_{CPU},\ V_{DD}$  = 3.3 V

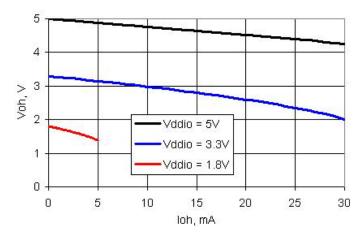

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

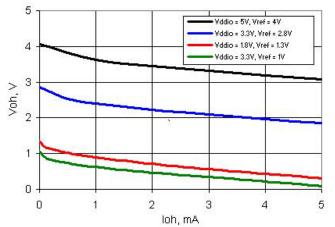

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

Table 11-12. SIO AC Specifications

| Parameter | Description                                            | Conditions                               | Min | Тур | Max | Units |

|-----------|--------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode (90/10%) <sup>[48]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TfallF    | Fall time in Fast Strong Mode (90/10%) <sup>[48]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.3 V | -   | -   | 12  | ns    |

| TriseS    | Rise time in Slow Strong Mode (90/10%) <sup>[48]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | -   | 75  | ns    |

| TfallS    | Fall time in Slow Strong Mode (90/10%) <sup>[48]</sup> | Cload = 25 pF, V <sub>DDIO</sub> = 3.0 V | -   | _   | 60  | ns    |

Note 48. Based on device characterization (Not production tested).

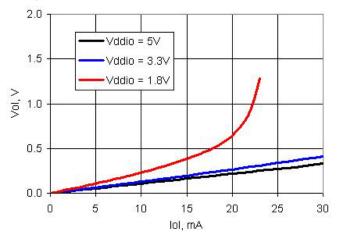

Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

## Table 11-20. Opamp AC Specifications<sup>[51]</sup>

| Parameter      | Description            | Conditions                                               | Min | Тур | Max | Units     |

|----------------|------------------------|----------------------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = low, 15 pF load                             | 2   | -   | -   | MHz       |

|                |                        | Power mode = medium, 200 pF load                         | 1   | -   | -   | MHz       |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | MHz       |

| SR             | Slew rate, 20%–80%     | Power mode = low, 15 pF load                             | 1.1 | -   | _   | V/µs      |

|                |                        | Power mode = medium, 200 pF load                         | 0.9 | -   | -   | V/µs      |

|                |                        | Power mode = high, 200 pF load                           | 3   | -   | -   | V/µs      |

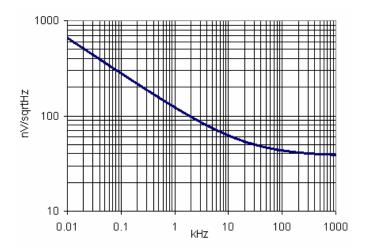

| e <sub>n</sub> | Input noise density    | Power mode = high, V <sub>DDA</sub> = 5 V,<br>at 100 kHz | _   | 45  | _   | nV/sqrtHz |

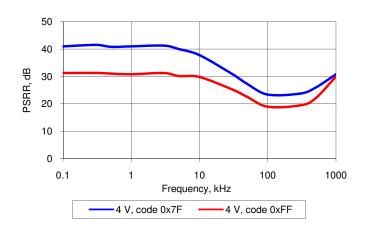

# Figure 11-30. Opamp Noise vs Frequency, Power Mode = High, $V_{DDA}$ = 5 V

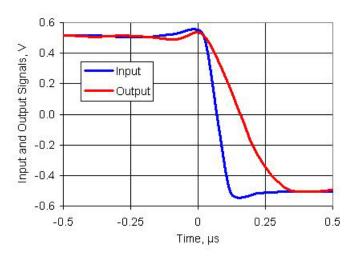

## Figure 11-32. Opamp Step Response, Falling

## Note

51. Based on device characterization (Not production tested).

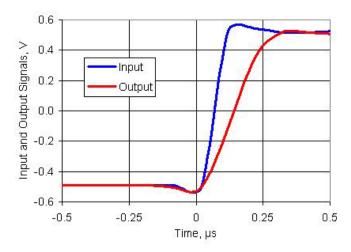

## Figure 11-31. Opamp Step Response, Rising

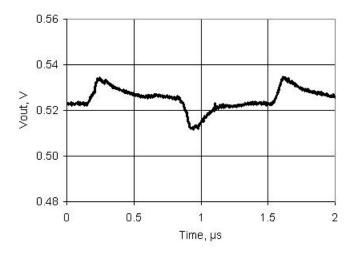

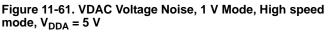

#### Table 11-31. VDAC AC Specifications

| Parameter        | Description                            | Conditions                                                      | Min | Тур  | Max  | Units     |

|------------------|----------------------------------------|-----------------------------------------------------------------|-----|------|------|-----------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                                                       | -   | -    | 1000 | ksps      |

|                  |                                        | 4 V scale                                                       | -   | -    | 250  | ksps      |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF                                        | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | -   | 0.8  | 3.2  | μs        |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF                                        | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | -   | 0.7  | 3    | μs        |

|                  | Voltage noise                          | Range = 1 V, High speed mode,<br>V <sub>DDA</sub> = 5 V, 10 kHz | -   | 750  | -    | nV/sqrtHz |

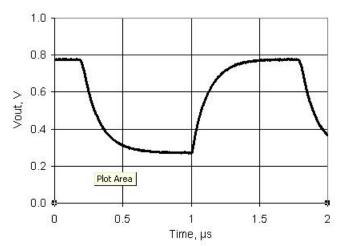

# Figure 11-58. VDAC Step Response, Codes 0x40 - 0xC0, 1 V Mode, High speed mode, $V_{DDA} = 5 V$

Figure 11-59. VDAC Glitch Response, Codes 0x7F - 0x80, 1 V Mode, High speed mode,  $V_{DDA}$  = 5 V

#### 11.6.3 Pulse Width Modulation

The following specifications apply to the Timer/Counter/PWM peripheral, in PWM mode. PWM components can also be implemented in UDBs; for more information, see the PWM component data sheet in PSoC Creator.

#### Table 11-45. PWM DC Specifications

| Parameter | Description               | Conditions                                  | Min | Тур | Max | Units |

|-----------|---------------------------|---------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit PWM, at listed input clock frequency | -   | _   | -   | μA    |

|           | 3 MHz                     |                                             | -   | 15  | -   | μA    |

|           | 12 MHz                    |                                             | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                             | _   | 260 | -   | μA    |

|           | 67 MHz                    |                                             | _   | 350 | _   | μA    |

#### Table 11-46. Pulse Width Modulation (PWM) AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | -   | 67.01 | MHz   |

|           | Pulse width                   |            | 15  | -   | -     | ns    |

|           | Pulse width (external)        |            | 30  | _   | _     | ns    |

|           | Kill pulse width              |            | 15  | -   | -     | ns    |

|           | Kill pulse width (external)   |            | 30  | -   | -     | ns    |

|           | Enable pulse width            |            | 15  | -   | -     | ns    |

|           | Enable pulse width (external) |            | 30  | -   | -     | ns    |

|           | Reset pulse width             |            | 15  | _   | -     | ns    |

|           | Reset pulse width (external)  |            | 30  | -   | -     | ns    |

## 11.6.4 P<sup>2</sup>C

## Table 11-47. Fixed I<sup>2</sup>C DC Specifications

| Parameter | Description               | Conditions                       | Min | Тур | Max | Units |

|-----------|---------------------------|----------------------------------|-----|-----|-----|-------|

|           | Block current consumption | Enabled, configured for 100 kbps | _   | -   | 250 | μA    |

|           |                           | Enabled, configured for 400 kbps | _   | -   | 260 | μA    |

|           |                           | Wake from sleep mode             | _   | _   | 30  | μA    |

## Table 11-48. Fixed I<sup>2</sup>C AC Specifications

| Parameter | Description | Conditions | Min | Тур | Max | Units |

|-----------|-------------|------------|-----|-----|-----|-------|

|           | Bit rate    |            | -   | -   | 1   | Mbps  |

11.6.5 Controller Area Network

#### Table 11-49. CAN DC Specifications<sup>[65]</sup>

| Parameter       | Description               | Conditions | Min | Тур | Max | Units |

|-----------------|---------------------------|------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Block current consumption |            | -   | _   | 200 | μA    |

## Table 11-50. CAN AC Specifications<sup>[65]</sup>

| Parameter | Description | Conditions          | Min | Тур | Max | Units |

|-----------|-------------|---------------------|-----|-----|-----|-------|

|           | Bit rate    | Minimum 8 MHz clock | _   | _   | 1   | Mbit  |

Note

65. Refer to ISO 11898 specification for details.

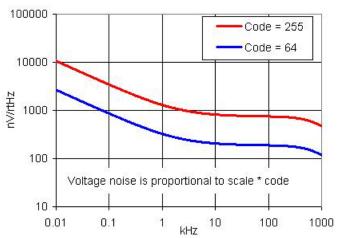

Figure 11-67. Synchronous Write and Read Cycle Timing, No Wait States

## Table 11-64. Synchronous Write and Read Timing Specifications<sup>[71]</sup>

| Parameter  | Description                                                    | Conditions | Min             | Тур | Max | Units |

|------------|----------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[72]</sup>                            |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[73]</sup>                               |            | 30.3            | -   | _   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of EM_Clock             |            | Tbus_clock – 10 | -   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before<br>rising edge of EM_OE |            | 5               | _   | _   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE     |            | 5               | -   | _   | ns    |

#### Notes

- 71. Based on device characterization (Not production tested).

72. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 80.

73. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

| Acronym | Description                                                  |  |  |  |  |

|---------|--------------------------------------------------------------|--|--|--|--|

| PHUB    | peripheral hub                                               |  |  |  |  |

| PHY     | physical layer                                               |  |  |  |  |

| PICU    | port interrupt control unit                                  |  |  |  |  |

| PLA     | programmable logic array                                     |  |  |  |  |

| PLD     | programmable logic device, see also PAL                      |  |  |  |  |

| PLL     | phase-locked loop                                            |  |  |  |  |

| PMDD    | package material declaration data sheet                      |  |  |  |  |

| POR     | power-on reset                                               |  |  |  |  |

| PRES    | precise low-voltage reset                                    |  |  |  |  |

| PRS     | pseudo random sequence                                       |  |  |  |  |

| PS      | port read data register                                      |  |  |  |  |

| PSoC®   | Programmable System-on-Chip™                                 |  |  |  |  |

| PSRR    | power supply rejection ratio                                 |  |  |  |  |

| PWM     | pulse-width modulator                                        |  |  |  |  |

| RAM     | random-access memory                                         |  |  |  |  |

| RISC    | reduced-instruction-set computing                            |  |  |  |  |

| RMS     | root-mean-square                                             |  |  |  |  |

| RTC     | real-time clock                                              |  |  |  |  |

| RTL     | register transfer language                                   |  |  |  |  |

| RTR     | remote transmission request                                  |  |  |  |  |

| RX      | receive                                                      |  |  |  |  |

| SAR     | successive approximation register                            |  |  |  |  |

| SC/CT   | switched capacitor/continuous time                           |  |  |  |  |

| SCL     | I <sup>2</sup> C serial clock                                |  |  |  |  |

| SDA     | I <sup>2</sup> C serial data                                 |  |  |  |  |

| S/H     | sample and hold                                              |  |  |  |  |

| SINAD   | signal to noise and distortion ratio                         |  |  |  |  |

| SIO     | special input/output, GPIO with advanced features. See GPIO. |  |  |  |  |

| SOC     | start of conversion                                          |  |  |  |  |

## Table 14-1. Acronyms Used in this Document (continued)

#### Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                               |

|---------|---------------------------------------------------------------------------|

| SOF     | start of frame                                                            |

| SPI     | Serial Peripheral Interface, a communications protocol                    |

| SR      | slew rate                                                                 |

| SRAM    | static random access memory                                               |

| SRES    | software reset                                                            |

| SWD     | serial wire debug, a test protocol                                        |

| SWV     | single-wire viewer                                                        |

| TD      | transaction descriptor, see also DMA                                      |

| THD     | total harmonic distortion                                                 |

| TIA     | transimpedance amplifier                                                  |

| TRM     | technical reference manual                                                |

| TTL     | transistor-transistor logic                                               |

| ТХ      | transmit                                                                  |

| UART    | Universal Asynchronous Transmitter Receiver, a<br>communications protocol |

| UDB     | universal digital block                                                   |

| USB     | Universal Serial Bus                                                      |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port                 |

| VDAC    | voltage DAC, see also DAC, IDAC                                           |

| WDT     | watchdog timer                                                            |

| WOL     | write once latch, see also NVL                                            |

| WRES    | watchdog timer reset                                                      |

| XRES    | external reset I/O pin                                                    |

| XTAL    | crystal                                                                   |

## **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

## 17. Revision History

| Document Number: 001-53413 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision                   | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| **                         | 2714854 | 06/04/09           | PVKV               | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| *A                         | 2758970 | 09/02/09           | MKEA               | Updated Part Numbering Conventions<br>Added Section 11.7.5 (EMIF Figures and Tables)<br>Updated GPIO and SIO AC specifications<br>Updated XRES Pin Description and Xdata Address Map specifications<br>Updated DFB and Comparator specifications<br>Updated PHUB features section and RTC in sleep mode<br>Updated IDAC and VDAC DC and Analog Global specifications<br>Updated USBIO AC and Delta Sigma ADC specifications<br>Updated PPOR and Voltage Monitors DC specifications<br>Updated Drive Mode diagram<br>Added 48-QFN Information<br>Updated other electrical specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| *В                         | 2824546 | 12/09/09           | MKEA               | Updated I2C section to reflect 1 Mbps. Updated Table 11-6 and 11-7 (Boost AC<br>and DC specs); also added Shottky Diode specs. Changed current for<br>sleep/hibernate mode to include SIO; Added footnote to analog global specs.<br>Updated Figures 1-1, 6-2, 7-14, and 8-1. Updated Table 6-2 and Table 6-3<br>(Hibernate and Sleep rows) and Power Modes section. Updated GPIO and SIC<br>AC specifications. Updated Gain error in IDAC and VDAC specifications.<br>Updated description of V <sub>DDA</sub> spec in Table 11-1 and removed GPIO Clamp<br>Current parameter. Updated number of UDBs on page 1.<br>Moved FILO from ILO DC to AC table.<br>Added PCB Layout and PCB Schematic diagrams.<br>Updated Fgpioout spec (Table 11-9). Added duty cycle frequency in PLL AC spec<br>table. Added note for Sleep and Hibernate modes and Active Mode specs in Table<br>11-2. Linked URL in Section 10.3 to PSoC Creator site.<br>Updated Ja and Jc values in Table 13-1. Updated Single Sample Mode and Fas<br>FIR Mode sections. Updated Input Resistance specification in Del-Sig ADC table<br>Added Tio_init parameter. Updated PGA and UGB AC Specs. Removed SPC<br>ADC. Updated Boost Converter section.<br>Added section 'SIO as Comparator'; updated Hysteresis spec (differential mode<br>in Table 11-10.<br>Updated V <sub>BAT</sub> condition and deleted Vstart parameter in Table 11-6.<br>Added 'Bytes' column for Tables 4-1 to 4-5. |  |

| *C                         | 2873322 | 02/04/10           | MKEA               | Changed maximum value of PPOR_TR to '1'. Updated V <sub>BIAS</sub> specification.<br>Updated PCB Schematic. Updated Figure 8-1 and Figure 6-3. Updated Interrup<br>Vector table, Updated Sales links. Updated JTAG and SWD specifications.<br>Removed Jp-p and Jperiod from ECO AC Spec table. Added note on sleep time<br>in Table 11-2. Updated ILO AC and DC specifications. Added Resolution<br>parameter in VDAC and IDAC tables. Updated I <sub>OUT</sub> typical and maximum values<br>Changed Temperature Sensor range to -40 °C to +85 °C. Removed Latchup<br>specification from Table 11-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Description Document | Description Title: PSoC <sup>®</sup> 3: CY8C36 Family Datasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued)<br>Document Number: 001-53413 |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision             | ECN                                                                                                                                                        | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| *J                   | 3179219                                                                                                                                                    | 02/22/2011         | MKEA               | Updated conditions for flash data retention time.<br>Updated 100-pin TQFP package spec.<br>Updated EEPROM AC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| *К                   | 3200146                                                                                                                                                    | 03/28/2011         | MKEA               | Removed Preliminary status from the data sheet.<br>Updated JTAG ID<br>Deleted Cin_G1, ADC input capacitance from Delta-Sigma ADC DC spec table<br>Updated JTAG Interface AC Specifications and SWD Interface Specifications<br>tables<br>Updated USBIO DC specs<br>Added 0.01 to max speed<br>Updated Features on page 1<br>Added Section 5.5, Nonvolatile Latches<br>Updated Flash AC specs<br>Added CAN DC specs<br>Updated delta-sigma graphs, noise histogram figures and RMS Noise spec tables<br>Add reference to application note AN58304 in section 8.1<br>Updated 100-pin TQFP package spec<br>Added oscillator, I/O, VDAC, regulator graphs<br>Updated GPIO and SIO AC specs<br>Updated GPIO and SIO AC spec table<br>Updated POR with Brown Out AC spec table<br>Updated IDAC graphs<br>Added DMA timing diagram, interrupt timing and interrupt vector, I2C timing<br>diagrams<br>Updated opamp graphs and PGA graphs<br>Added full chip performance graphs<br>Changed MHzECO range.<br>Added "Solder Reflow Peak Temperature" table. |  |  |  |

| *L                   | 3259185                                                                                                                                                    | 05/17/2011         | MKEA               | Added JTAG and SWD interface connection diagrams<br>Updated $T_{JA}$ and $T_{JC}$ values in Table 13-1<br>Changed typ and max values for the TCVos parameter in Opamp DC<br>specifications table.<br>Updated Clocking subsystem diagram.<br>Changed VSSD to VSSB in the PSoC Power System diagram<br>Updated Ordering information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| N       3645908       06/14/2012       MKEA       Added paragraph clarifying that to achieve low hibemate current, you must limit the frequency of IO input signals. Revised description of IPOR and clarified PRES term. Changed footnote to state that all GPIO input voltages - not just analog voltages - must be less than Vddio. Updated 100-TOFP package drawing Clarified description of opamp lout spec Changed "compliant with I2C" Updated 48-QFN package drawing Changed reserving mining description text to clarify that not all reset sources are in the register         Updated 48-QFN package drawing       Changed reserving that FTW is a wakeup source (Changed supply ramp rate spec from 1 //ms and values Added "based on char" footnote to voltage monitors response time spec Changed analog global spec descriptions and values Added spec for ESD <sub>rBM</sub> for when VSas and Vsas are separate Added a statement about support for JTAG programmers and file formats Changed et with and added figures descriptions and values Added text describility of buzz frequency         Updated text descriptions pace discriptions and values       Added text descriptions and values (Changed text and added figures description of JTAG programmers and file formats. Changed et with additions Added text and added figures descriptions are possible while the device is reset"         Deleted the text "device operations are possible while the device is reset"       Deleted the text "device operations are possible while the device is reset"         Deleted and updated text regarding SIO performance under certain power ramp conditions       Removed from boost mention of 22 µH inductors. This included deleting some graph figures.         Changed Land DM Startup Ime spec form 1 Vims to .0066 Viµs       Changed ackage diagram | Revision    | ECN | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Updated package diagram spec 001-45616 to *D revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Revision *N |     | Date               | Change             | Added paragraph clarifying that to achieve low hibernate current, you must limit<br>the frequency of IO input signals.<br>Revised description of IPOR and clarified PRES term.<br>Changed footnote to state that all GPIO input voltages - not just analog voltages<br>- must be less than Vddio.<br>Updated 100-TQFP package drawing<br>Clarified description of opamp lout spec<br>Changed "compliant with 12C" to "compatible with 12C"<br>Updated 48-QFN package drawing<br>Changed reset status register description text to clarify that not all reset sources<br>are in the register<br>Updated example PCB layout figure<br>Removed text stating that FTW is a wakeup source<br>Changed supply ramp rate spec from 1 V/ns to 0.066 V/µs<br>Added "based on char" footnote to voltage monitors response time spec<br>Changed analog global spec descriptions and values<br>Added spec for ESD <sub>HBM</sub> for when Vssa and Vssd are separate<br>Added a statement about support for JTAG programmers and file formats<br>Changed comparator specs and conditions<br>Added text describing flash cache, and updated related text<br>Changed text and added figures describing Vddio source and sink<br>Added a statement about support for JTAG programmers and file formats.<br>Changed text and added figures describing Vddio source and sink<br>Added text on adjustability of buzz frequency<br>Updated terminology for "master" and "system" clock<br>Deleted the text "debug operations are possible while the device is reset"<br>Deleted and updated text regarding SIO performance under certain power ramp<br>conditions<br>Changed DAC high and low speed/power mode descriptions and conditions<br>Changed DAC high and low speed/power mode descriptions and conditions<br>Changed text dos XIP RES re-arm times<br>Added text and sugge in externally regulated mode<br>Updated text describing SIO modes for overvoltage tolerance<br>Added text doscribing SIO modes for overvoltage tolerance<br>Added text describing SIO modes for |