#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                  |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 4x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3666axi-037t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to guickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 3:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 3 are:

- AN54181: Getting Started With PSoC 3

- AN61290: Hardware Design Considerations

- AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

- Development Kits:

- CY8CKIT-030 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1. PSoC 3. PSoC 4. or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

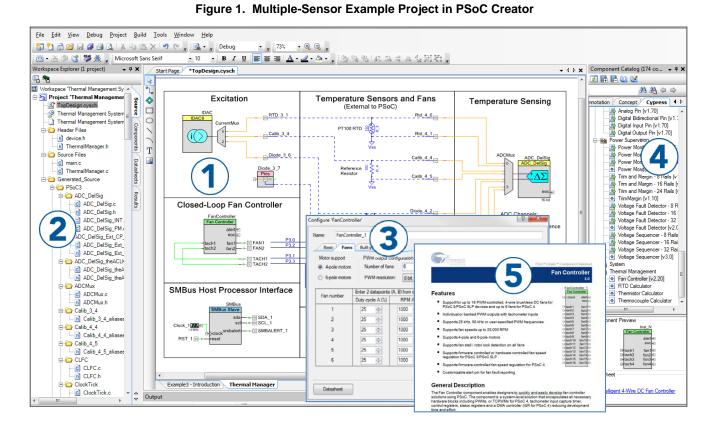

PSoC Creator PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100

- pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can: 1. Drag and drop component icons to build your hardware system design in the main design workspace

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 2. Codesign your application firmware with the PSoC hardware, using the PSoC Creator IDE C compiler

- 5. Review component datasheets

# Contents

| 1. Architectural Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2. Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                |

| 3. Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                               |

| 4. CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  |

| 4.1 8051 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

| 4.2 Addressing Modes<br>4.3 Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14<br>14                         |

| 4.4 DMA and PHUB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14<br>18                         |

| 4.5 Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  |

| 5. Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| 5.1 Static RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| 5.2 Flash Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                               |

| 5.3 Flash Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                               |

| 5.4 EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| 5.5 Nonvolatile Latches (NVLs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| 5.6 External Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                  |

| 5.7 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| 6. System Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| 6.1 Clocking System<br>6.2 Power System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                  |

| 6.3 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| 6.4 I/O System and Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| , 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |

| 7. Digital Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                               |

| 7. Digital Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| 7.1 Example Peripherals<br>7.2 Universal Digital Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44<br>46                         |

| <ul><li>7.1 Example Peripherals</li><li>7.2 Universal Digital Block</li><li>7.3 UDB Array Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44<br>46<br>49                   |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 | 44<br>46<br>49<br>49             |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                | 44<br>46<br>49<br>49<br>51       |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> </ul>                                                                                                                                                                                                                                                                                                                                       | 44<br>46<br>49<br>51<br>53<br>53 |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> </ul>                                                                                                                                                                                                                                                                                                           |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul>                                                                                                                                                                                                                                                                         |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 l<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul> 8. Analog Subsystem                                                                                                                                                                                                                                                     |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 l<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul> 8. Analog Subsystem <ul> <li>8.1 Analog Routing</li> </ul>                                                                                                                                                                                                              |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 l<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul> 8. Analog Subsystem                                                                                                                                                                                                                                                     |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> </ul>                                                                                                                                      |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> </ul>                                                                                               |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> </ul>                                                                 |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> </ul>                                           |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> <li>8.8 Temp Sensor</li> </ul>                  |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> <li>8.8 Temp Sensor</li> <li>8.9 DAC</li> </ul> |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> <li>8.8 Temp Sensor</li> </ul>                  |                                  |

| 9. Programming, Debug Interfaces, Resources<br>9.1 JTAG Interface |            |

|-------------------------------------------------------------------|------------|

| 9.2 Serial Wire Debug Interface                                   |            |

| 9.3 Debug Features                                                |            |

| 9.4 Trace Features                                                |            |

| 9.5 Single Wire Viewer Interface                                  |            |

| 9.6 Programming Features                                          |            |

| 9.7 Device Security                                               | 68         |

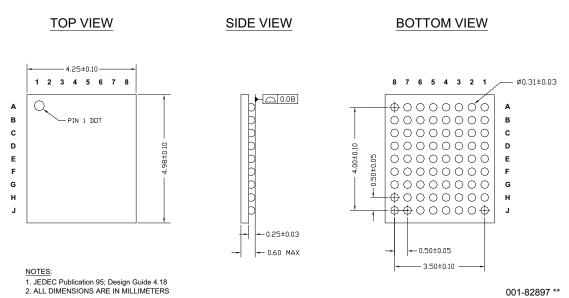

| 9.8 CSP Package Bootloader                                        | 69         |

| 10. Development Support                                           |            |

| 10.1 Documentation                                                |            |

| 10.2 Online                                                       |            |

| 10.3 Tools                                                        |            |

| 11. Electrical Specifications                                     |            |

| 11.1 Absolute Maximum Ratings                                     |            |

| 11.2 Device Level Specifications                                  |            |

| 11.3 Power Regulators                                             |            |

| 11.4 Inputs and Outputs                                           |            |

| 11.5 Analog Peripherals                                           |            |

| 11.6 Digital Peripherals                                          |            |

| 11.7 Memory<br>11.8 PSoC System Resources                         | 109<br>112 |

| 11.9 Clocking                                                     |            |

| -                                                                 |            |

| 12. Ordering Information                                          |            |

| C C                                                               |            |

| 13. Packaging                                                     |            |

| 14. Acronyms                                                      |            |

| 15. Reference Documents                                           | 127        |

| 16. Document Conventions                                          | 128        |

| 16.1 Units of Measure                                             | 128        |

| 17. Revision History                                              | 129        |

| 18. Sales, Solutions, and Legal Information                       |            |

| Worldwide Sales and Design Support                                |            |

| Products                                                          |            |

| PSoC® Solutions                                                   |            |

| Cypress Developer Community                                       |            |

| Technical Support                                                 | 137        |

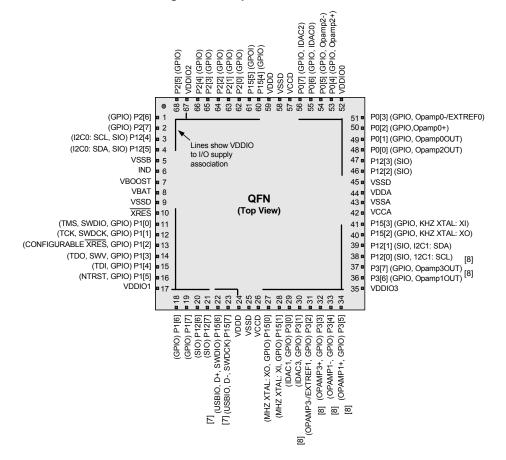

# Figure 2-5. 68-pin QFN Part Pinout<sup>[9]</sup>

Notes

Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating. 7

- 8.

- This feature on select devices only. See Ordering Information on page 120 for details. The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices. 9.

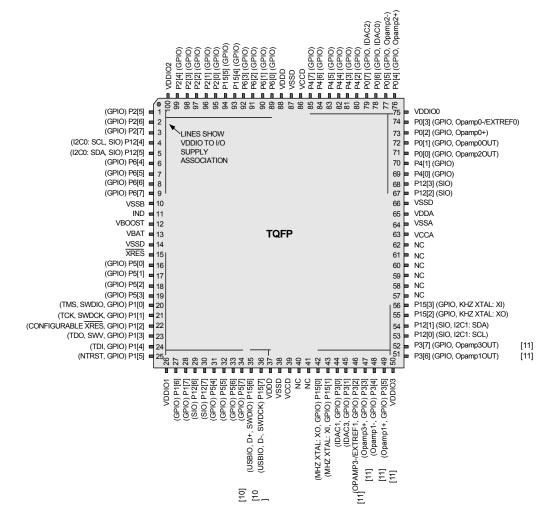

# Figure 2-6. 100-pin TQFP Part Pinout

#### Table 2-1. VDDIO and Port Pin Associations

| VDDIO  | Port Pins                            |

|--------|--------------------------------------|

| VDDIO0 | P0[7:0], P4[7:0], P12[3:2]           |

| VDDIO1 | P1[7:0], P5[7:0], P12[7:6]           |

| VDDIO2 | P2[7:0], P6[7:0], P12[5:4], P15[5:4] |

| VDDIO3 | P3[7:0], P12[1:0], P15[3:0]          |

| VDDD   | P15[7:6] (USB D+, D-)                |

#### Notes

10. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

11. This feature on select devices only. See Ordering Information on page 120 for details.

# 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

# Table 4-5. Jump Instructions

| Mnemonic             | Description                                                  | Bytes | Cycles |

|----------------------|--------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                     | 2     | 4      |

| LCALL addr16         | Long subroutine call                                         | 3     | 4      |

| RET                  | Return from subroutine                                       | 1     | 4      |

| RETI                 | Return from interrupt                                        | 1     | 4      |

| AJMP addr11          | Absolute jump                                                | 2     | 3      |

| LJMP addr16          | Long jump                                                    | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                               | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                  | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                               | 2     | 4      |

| CJNE A, Direct, rel  | Compare direct byte to accumulator and jump if not equal     | 3     | 5      |

| CJNE A, #data, rel   | Compare immediate data to accumulator and jump if not equal  | 3     | 4      |

| CJNE Rn, #data, rel  | Compare immediate data to register and jump if not equal     | 3     | 4      |

| CJNE @Ri, #data, rel | Compare immediate data to indirect RAM and jump if not equal | 3     | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                      | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                   | 3     | 5      |

| NOP                  | No operation                                                 | 1     | 1      |

# 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

# 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight Multi-layer AHB Bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8-, 16-, 24-, and 32-bit addressing and data Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

# 4.4.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TD) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

#### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100% of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.4.4.1 Simple DMA

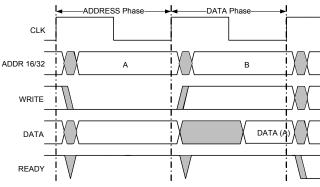

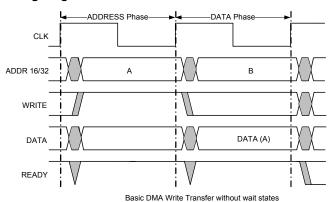

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles shown in Figure 4-1. For more description on other transfer modes, refer to the Technical Reference Manual.

# Figure 4-1. DMA Timing Diagram

Basic DMA Read Transfer without wait states

# 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

# 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the

data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

## 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

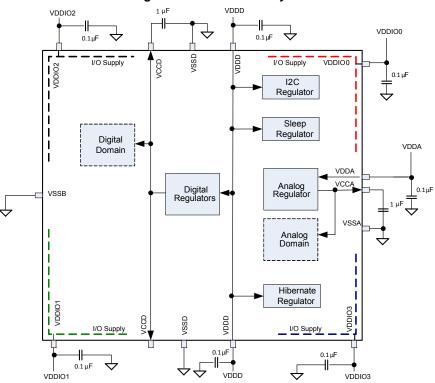

# 6.2 Power System

The power system consists of separate analog, digital, and I/O supply pins, labeled VDDA, VDDD, and VDDIO×, respectively. It also includes two internal 1.8 V regulators that provide the digital (VCCD) and analog (VCCA) supplies for the internal core logic. The output pins of the regulators (VCCD and VCCA) and the

VDDIO pins must have capacitors connected as shown in Figure 6-4. The two VCCD pins must be shorted together, with as short a trace as possible, and connected to a  $1-\mu F \pm 10\% \times 5R$  capacitor. The power system also contains a sleep regulator, an  $I^2C$  regulator, and a hibernate regulator.

# Figure 6-4. PSoC Power System

# Notes

- The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 12.

- It is good practice to check the datasheets for your bypass capacitors, specifically the working voltage and the DC bias specifications. With some capacitors, the actual capacitance can decrease considerably when the DC bias (VDDX or VCCX in Figure 6-4) is a significant percentage of the rated working voltage.

- You can power the device in internally regulated mode, where the voltage applied to the VDDx pins is as high as 5.5 V, and the internal regulators provide the core voltages. In this mode, do not apply power to the VCCx pins, and do not tie the VDDx pins to the VCCx pins.

- You can also power the device in externally regulated mode, that is, by directly powering the VCCD and VCCA pins. In this configuration, the VDDD pins should be shorted to the VCCD pins and the VDDA pin should be shorted to the VCCA pin. The allowed supply range in this configuration is 1.71 V to 1.89 V. After power up in this configuration, the internal regulators are on by default, and should be disabled to reduce power consumption.

#### Timer DMA IO Port Global Interrupt CAN I2C Counters Controller Controller Pins Clocks Digital System Routing I/F **UDB ARRAY** Digital System Routing I/F Global IO Port SC/CT EMIF Comparators Del-Sia DACs Clocks Blocks Pins

# Figure 7-9. Digital System Interconnect

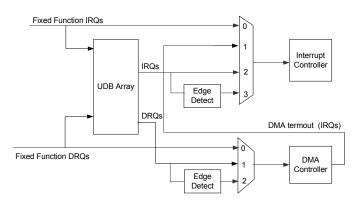

Interrupt and DMA routing is very flexible in the CY8C36 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

# Figure 7-10. Interrupt and DMA Processing in the IDMUX

Interrupt and DMA Processing in IDMUX

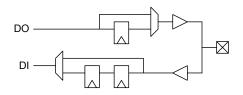

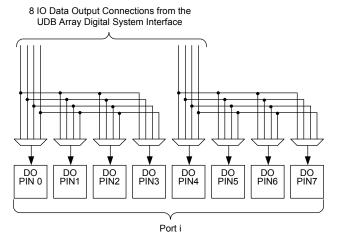

# 7.4.1 I/O Port Routing

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1 on page 28). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

## Figure 7-11. I/O Pin Synchronization Routing

# Figure 7-12. I/O Pin Output Connectivity

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

Document Number: 001-53413 Rev. \*Y

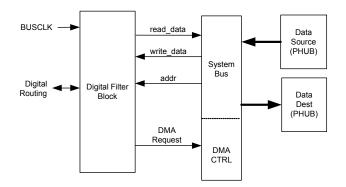

# 7.9 Digital Filter Block

Some devices in the CY8C36 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one bus clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes MCU bandwidth.

The heart of the DFB is a datapath (DP), which is the numerical calculation unit of the DFB. The DP is a 24-bit fixed-point numerical processor containing a 48-bit multiply and accumulate function (MAC), a multi-function ALU, sample and coefficient data RAMs as well as data routing, shifting, holding and rounding functions.

In the MAC, two 24-bit values can be multiplied and the result added to the 48-bit accumulator in each bus clock cycle. The MAC is the only portion of the DP that is wider than 24 bits. All results from the MAC are passed on to the ALU as 24-bit values representing the high-order 24 bits in the accumulator shifted by one (bits 46:23). The MAC assumes an implied binary point after the most significant bit.

The DP also contains an optimized ALU that supports add, subtract, comparison, threshold, absolute value, squelch, saturation, and other functions. The DP unit is controlled by seven control fields totaling 18 bits coming from the DFB Controller. For more information see the TRM.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

# Figure 7-20. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

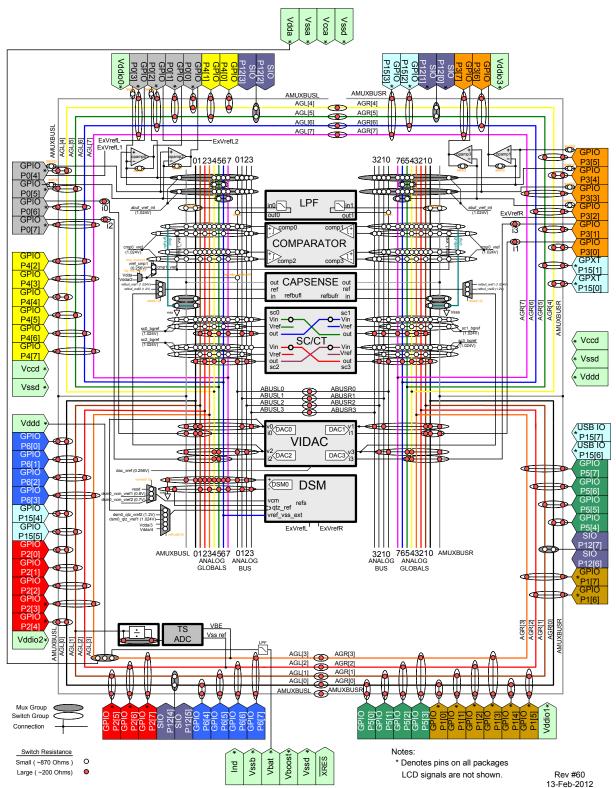

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution Delta-Sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

# Figure 8-2. CY8C36 Analog Interconnect

To preserve detail of this figure, this figure is best viewed with a PDF display program or printed on a 11" × 17" paper.

Analog local buses (abus) are routing resources located within the analog subsystem and are used to route signals between different analog blocks. There are eight abus routes in CY8C36, four in the left half (abusl [0:3]) and four in the right half (abusr [0:3]) as shown in Figure 8-2. Using the abus saves the analog globals and analog mux buses from being used for interconnecting the analog blocks.

Multiplexers and switches exist on the various buses to direct signals into and out of the analog blocks. A multiplexer can have only one connection on at a time, whereas a switch can have multiple connections on simultaneously. In Figure 8-2, multiplexers are indicated by grayed ovals and switches are indicated by transparent ovals.

# 8.2 Delta-sigma ADC

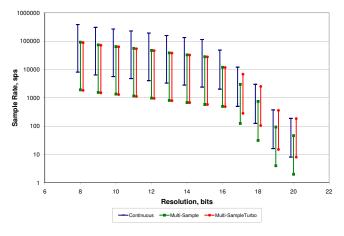

The CY8C36 device contains one delta-sigma ADC. This ADC offers differential input, high resolution and excellent linearity, making it a good ADC choice for measurement applications. The converter can be configured to output 12-bit resolution at data rates of up to 192 ksps. At a fixed clock rate, resolution can be traded for faster data rates as shown in Table 8-1 and Figure 8-3.

| Table 8-1. | Delta-sigma | ADC | Performance |

|------------|-------------|-----|-------------|

|------------|-------------|-----|-------------|

| Bits | Maximum Sample Rate<br>(sps) | SINAD (dB) |

|------|------------------------------|------------|

| 12   | 192 k                        | 66         |

| 8    | 384 k                        | 43         |

# Figure 8-3. Delta-sigma ADC Sample Rates, Range = $\pm 1.024$ V

# 8.2.1 Functional Description

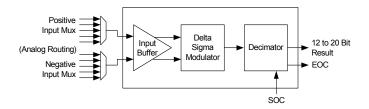

The ADC connects and configures three basic components, input buffer, delta-sigma modulator, and decimator. The basic block diagram is shown in Figure 8-4. The signal from the input muxes is delivered to the delta-sigma modulator either directly or through the input buffer. The delta-sigma modulator performs the actual analog to digital conversion. The modulator over-samples the input and generates a serial data stream output. This high speed data stream is not useful for most applications without some type of post processing, and so is passed to the decimator through the Analog Interface block. The decimator converts the

high speed serial data stream into parallel ADC results. The modulator/decimator frequency response is  $[(\sin x)/x]^4$ .

## Figure 8-4. Delta-sigma ADC Block Diagram

Resolution and sample rate are controlled by the Decimator. Data is pipelined in the decimator; the output is a function of the last four samples. When the input multiplexer is switched, the output data is not valid until after the fourth sample after the switch.

## 8.2.2 Operational Modes

The ADC can be configured by the user to operate in one of four modes: Single Sample, Multi Sample, Continuous, or Multi Sample (Turbo). All four modes are started by either a write to the start bit in a control register or an assertion of the Start of Conversion (SoC) signal. When the conversion is complete, a status bit is set and the output signal End of Conversion (EoC) asserts high and remains high until the value is read by either the DMA controller or the CPU.

# 8.2.2.1 Single Sample

In Single Sample mode, the ADC performs one sample conversion on a trigger. In this mode, the ADC stays in standby state waiting for the SoC signal to be asserted. When SoC is signaled the ADC performs four successive conversions. The first three conversions prime the decimator. The ADC result is valid and available after the fourth conversion, at which time the EoC signal is generated. To detect the end of conversion, the system may poll a control register for status or configure the external EoC signal to generate an interrupt or invoke a DMA request. When the transfer is done the ADC reenters the standby state where it stays until another SoC event.

#### 8.2.2.2 Continuous

Continuous sample mode is used to take multiple successive samples of a single input signal. Multiplexing multiple inputs should not be done with this mode. There is a latency of three conversion times before the first conversion result is available. This is the time required to prime the decimator. After the first result, successive conversions are available at the selected sample rate.

#### 8.2.2.3 Multi Sample

Multi sample mode is similar to continuous mode except that the ADC is reset between samples. This mode is useful when the input is switched between multiple signals. The decimator is re-primed between each sample so that previous samples do not affect the current conversion. Upon completion of a sample, the next sample is automatically initiated. The results can be transferred using either firmware polling, interrupt, or DMA.

More information on output formats is provided in the Technical Reference Manual.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

The opamp and resistor array is programmable to perform various analog functions including

- Naked operational amplifier Continuous mode

- Unity-gain buffer Continuous mode

- Programmable gain amplifier (PGA) Continuous mode

- Transimpedance amplifier (TIA) Continuous mode

- Up/down mixer Continuous mode

- Sample and hold mixer (NRZ S/H) Switched cap mode

- First order analog to digital modulator Switched cap mode

#### 8.5.1 Naked Opamp

The Naked Opamp presents both inputs and the output for connection to internal or external signals. The opamp has a unity gain bandwidth greater than 6.0 MHz and output drive current up to 650  $\mu$ A. This is sufficient for buffering internal signals (such as DAC outputs) and driving external loads greater than 7.5 k $\Omega$ .

## 8.5.2 Unity Gain

The Unity Gain buffer is a Naked Opamp with the output directly connected to the inverting input for a gain of 1.00. It has a -3 dB bandwidth greater than 6.0 MHz.

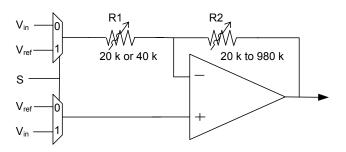

## 8.5.3 PGA

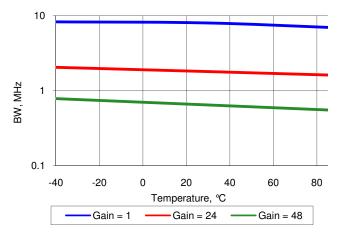

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-8 on page 62. The schematic in Figure 8-8 on page 62 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

# Table 8-3. Bandwidth

| Gain | Bandwidth |

|------|-----------|

| 1    | 6.0 MHz   |

| 24   | 340 kHz   |

| 48   | 220 kHz   |

| 50   | 215 kHz   |

# Figure 8-8. PGA Resistor Settings

The PGA is used in applications where the input signal may not be large enough to achieve the desired resolution in the ADC, or dynamic range of another SC/CT block such as a mixer. The gain is adjustable at runtime, including changing the gain of the PGA prior to each ADC sample.

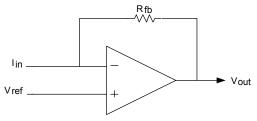

# 8.5.4 TIA

The Transimpedance Amplifier (TIA) converts an internal or external current to an output voltage. The TIA uses an internal feedback resistor in a continuous time configuration to convert input current to output voltage. For an input current I<sub>in</sub>, the output voltage is V<sub>REF</sub> - I<sub>in</sub> x R<sub>fb</sub>, where V<sub>REF</sub> is the value placed on the non inverting input. The feedback resistor Rfb is programmable between 20 K $\Omega$  and 1 M $\Omega$  through a configuration register. Table 8-4 shows the possible values of Rfb and associated configuration settings.

#### Table 8-4. Feedback Resistor Settings

| Configuration Word | Nominal $R_{fb}(K\Omega)$ |

|--------------------|---------------------------|

| 000b               | 20                        |

| 001b               | 30                        |

| 010b               | 40                        |

| 011b               | 60                        |

| 100b               | 120                       |

| 101b               | 250                       |

| 110b               | 500                       |

| 111b               | 1000                      |

#### Figure 8-9. Continuous Time TIA Schematic

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the V<sub>REF</sub> TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

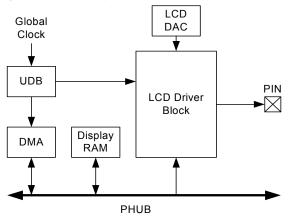

# 8.6 LCD Direct Drive

The PSoC Liquid Crystal Display (LCD) driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C36 family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

# Figure 8-10. LCD System

# 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

## 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through DMA.

## 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

# 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

# 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, and proximity detection. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator. A capacitive sensing method using a Delta-Sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

# 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

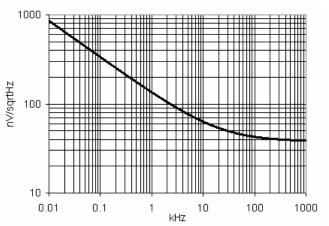

# Table 11-37. PGA AC Specifications

| Parameter      | Description         | Conditions                                                     | Min | Тур | Max | Units     |

|----------------|---------------------|----------------------------------------------------------------|-----|-----|-----|-----------|

| BW1            | –3 dB bandwidth     | Power mode = high,<br>gain = 1, input = 100 mV<br>peak-to-peak | 6.7 | 8   | -   | MHz       |

| SR1            | Slew rate           | Power mode = high,<br>gain = 1, 20% to 80%                     | 3   | _   | _   | V/µs      |

| e <sub>n</sub> | Input noise density | Power mode = high,<br>V <sub>DDA</sub> = 5 V, at 100 kHz       | -   | 43  | _   | nV/sqrtHz |

# Figure 11-63. Bandwidth vs. Temperature, at Different Gain Settings, Power Mode = High

Figure 11-64. Noise vs. Frequency,  $V_{DDA} = 5 V$ , Power Mode = High

# 11.5.11 Temperature Sensor

# Table 11-38. Temperature Sensor Specifications

| Parameter | Description          | Conditions              | Min | Тур | Max | Units |

|-----------|----------------------|-------------------------|-----|-----|-----|-------|

|           | Temp sensor accuracy | Range: –40 °C to +85 °C | -   | ±5  | 1   | °C    |

# 11.5.12 LCD Direct Drive

# Table 11-39. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                 | Min | Тур                    | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|------|-------|

| lcc                 | LCD system operating current                                                        | Device sleep mode with wakeup at 400-Hz rate to refresh LCDs, bus clock = 3 MHz, $V_{DDIO} = V_{DDA} = 3 V$ , 4 commons, 16 segments, 1/4 duty cycle, 50 Hz frame rate, no glass connected | _   | 38                     | -    | μΑ    |

| I <sub>CC SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                          | -   | 260                    | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \geq 3~V$ and $V_{DDA} \geq V_{BIAS}$                                                                                                                                             | 2   | -                      | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                | _   | 9.1 × V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                    | _   | 500                    | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                            | _   | -                      | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | $V_{DDIO}$ = 5.5V, strong drive mode                                                                                                                                                       | 355 | -                      | 710  | μA    |

## Table 11-40. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

# 11.9.2 Internal Low Speed Oscillator

# Table 11-75. ILO DC Specifications

| Parameter       |                                   | Conditions                 | Min | Тур | Max | Units |

|-----------------|-----------------------------------|----------------------------|-----|-----|-----|-------|

|                 | Operating current <sup>[82]</sup> | F <sub>OUT</sub> = 1 kHz   | _   | -   | 1.7 | μA    |

| I <sub>CC</sub> |                                   | F <sub>OUT</sub> = 33 kHz  | -   | -   | 2.6 | μA    |

|                 |                                   | F <sub>OUT</sub> = 100 kHz | -   | -   | 2.6 | μA    |

|                 | Leakage current <sup>[82]</sup>   | Power down mode            | -   | -   | 15  | nA    |

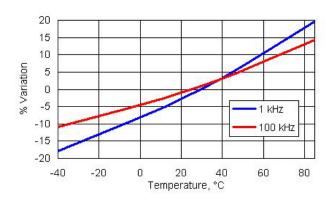

# Table 11-76. ILO AC Specifications

| Parameter        | Description                   | Conditions | Min | Тур | Max | Units |

|------------------|-------------------------------|------------|-----|-----|-----|-------|

|                  | Startup time, all frequencies | Turbo mode | -   | -   | 2   | ms    |

| F <sub>ILO</sub> | ILO frequencies               |            |     |     |     |       |

|                  | 100 kHz                       |            | 45  | 100 | 200 | kHz   |

|                  | 1 kHz                         |            | 0.5 | 1   | 2   | kHz   |

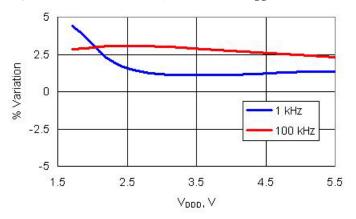

# Figure 11-73. ILO Frequency Variation vs. Temperature

# Figure 11-74. ILO Frequency Variation vs. V<sub>DD</sub>

# **12.1 Part Numbering Conventions**

PSoC 3 devices follow the part numbering convention described here. All fields are single character alphanumeric (0, 1, 2, ..., 9, A, B, ..., Z) unless stated otherwise.

| CY8Cabcdefg-xxx                                                                                                                |                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ■ a: Architecture<br>□ 3: PSoC 3                                                                                               | <ul> <li>■ ef: Package code</li> <li>□ Two character alphanumeric</li> </ul>                                                                  |

| <ul> <li>5: PSoC 5</li> <li>b: Family group within architecture</li> <li>4: CY8C34 family</li> <li>6: CY8C36 family</li> </ul> | □ AX: TQFP<br>□ LT: QFN<br>□ PV: SSOP<br>□ FN: CSP                                                                                            |

| <ul> <li>■ 8: CY8C38 family</li> <li>■ c: Speed grade</li> <li>□ 4: 48 MHz</li> <li>□ 6: 67 MHz</li> </ul>                     | <ul> <li>g: Temperature range</li> <li>C: commercial</li> <li>I: industrial</li> <li>A: automotive</li> </ul>                                 |

| ■ d: Flash capacity<br>□ 4: 16 KB<br>□ 5: 32 KB                                                                                | <ul> <li>■ xxx: Peripheral set</li> <li>□ Three character numeric</li> <li>□ No meaning is associated with these three characters.</li> </ul> |

□ 6: 64 KB

| Example          | $-\underline{CY8C}_{3} \xrightarrow{G}_{F} \xrightarrow{G}_{F} \xrightarrow{G}_{F} \xrightarrow{G}_{F} \xrightarrow{F}_{F} \xrightarrow{F}_{F}} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}_{F} \xrightarrow{F}} \xrightarrow{F} \xrightarrow{F}_{F} \xrightarrow{F} \xrightarrow{F}} \xrightarrow{F}_{F} \xrightarrow{F}} \xrightarrow{F}_{F} \xrightarrow{F}} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F}} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F}} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F}} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F}} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F} \xrightarrow{F}} \xrightarrow{F} \xrightarrow$ |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|