#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                                |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 4x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3666axi-052t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1. Architectural Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2. Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6                                |

| 3. Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                               |

| 4. CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                  |

| 4.1 8051 CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

| 4.2 Addressing Modes<br>4.3 Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 14<br>14                         |

| 4.4 DMA and PHUB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14<br>18                         |

| 4.5 Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  |

| 5. Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| 5.1 Static RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| 5.2 Flash Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                               |

| 5.3 Flash Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                               |

| 5.4 EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| 5.5 Nonvolatile Latches (NVLs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| 5.6 External Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                  |

| 5.7 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| 6. System Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| 6.1 Clocking System<br>6.2 Power System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                  |

| 6.3 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| 6.4 I/O System and Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                  |

| , 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |

| 7. Digital Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44                               |

| 7. Digital Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| 7.1 Example Peripherals<br>7.2 Universal Digital Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44<br>46                         |

| <ul><li>7.1 Example Peripherals</li><li>7.2 Universal Digital Block</li><li>7.3 UDB Array Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44<br>46<br>49                   |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                 | 44<br>46<br>49<br>49             |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                | 44<br>46<br>49<br>49<br>51       |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               | 44<br>46<br>49<br>51<br>53       |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> </ul>                                                                                                                                                                                                                                                                                                                                       | 44<br>46<br>49<br>51<br>53<br>53 |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> </ul>                                                                                                                                                                                                                                                                                                           |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul>                                                                                                                                                                                                                                                                         |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 l<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul> 8. Analog Subsystem                                                                                                                                                                                                                                                     |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 l<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul> 8. Analog Subsystem <ul> <li>8.1 Analog Routing</li> </ul>                                                                                                                                                                                                              |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 l<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> </ul> 8. Analog Subsystem                                                                                                                                                                                                                                                     |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> </ul>                                                                                                                                      |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> </ul>                                                                                               |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> </ul>                                                                 |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> </ul>                                           |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> <li>8.8 Temp Sensor</li> </ul>                  |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> <li>8.8 Temp Sensor</li> <li>8.9 DAC</li> </ul> |                                  |

| <ul> <li>7.1 Example Peripherals</li> <li>7.2 Universal Digital Block</li> <li>7.3 UDB Array Description</li> <li>7.4 DSI Routing Interface Description</li> <li>7.5 CAN</li> <li>7.6 USB</li> <li>7.7 Timers, Counters, and PWMs</li> <li>7.8 I<sup>2</sup>C</li> <li>7.9 Digital Filter Block</li> <li>8. Analog Subsystem</li> <li>8.1 Analog Routing</li> <li>8.2 Delta-sigma ADC</li> <li>8.3 Comparators</li> <li>8.4 Opamps</li> <li>8.5 Programmable SC/CT Blocks</li> <li>8.6 LCD Direct Drive</li> <li>8.7 CapSense</li> <li>8.8 Temp Sensor</li> </ul>                  |                                  |

| 9. Programming, Debug Interfaces, Resources<br>9.1 JTAG Interface |            |

|-------------------------------------------------------------------|------------|

| 9.2 Serial Wire Debug Interface                                   |            |

| 9.3 Debug Features                                                |            |

| 9.4 Trace Features                                                |            |

| 9.5 Single Wire Viewer Interface                                  |            |

| 9.6 Programming Features                                          |            |

| 9.7 Device Security                                               | 68         |

| 9.8 CSP Package Bootloader                                        | 69         |

| 10. Development Support                                           |            |

| 10.1 Documentation                                                |            |

| 10.2 Online                                                       |            |

| 10.3 Tools                                                        |            |

| 11. Electrical Specifications                                     |            |

| 11.1 Absolute Maximum Ratings                                     |            |

| 11.2 Device Level Specifications                                  |            |

| 11.3 Power Regulators                                             |            |

| 11.4 Inputs and Outputs                                           |            |

| 11.5 Analog Peripherals                                           |            |

| 11.6 Digital Peripherals                                          |            |

| 11.7 Memory<br>11.8 PSoC System Resources                         | 109<br>112 |

| 11.9 Clocking                                                     |            |

| -                                                                 |            |

| 12. Ordering Information                                          |            |

| C C                                                               |            |

| 13. Packaging                                                     |            |

| 14. Acronyms                                                      |            |

| 15. Reference Documents                                           | 127        |

| 16. Document Conventions                                          | 128        |

| 16.1 Units of Measure                                             | 128        |

| 17. Revision History                                              | 129        |

| 18. Sales, Solutions, and Legal Information                       |            |

| Worldwide Sales and Design Support                                |            |

| Products                                                          |            |

| PSoC® Solutions                                                   |            |

| Cypress Developer Community                                       |            |

| Technical Support                                                 | 137        |

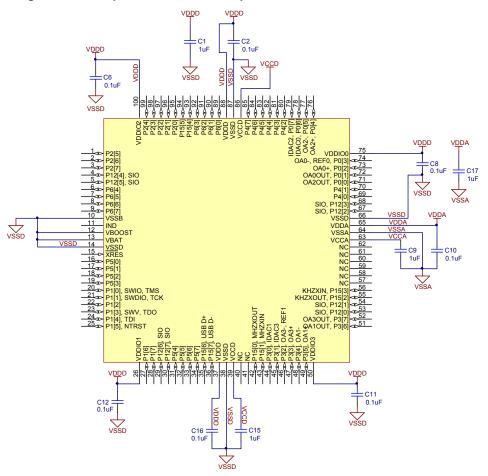

## Figure 2-7. Example Schematic for 100-pin TQFP Part With Power Connections

**Note** The two Vccd pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 12.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-3-cad-libraries.

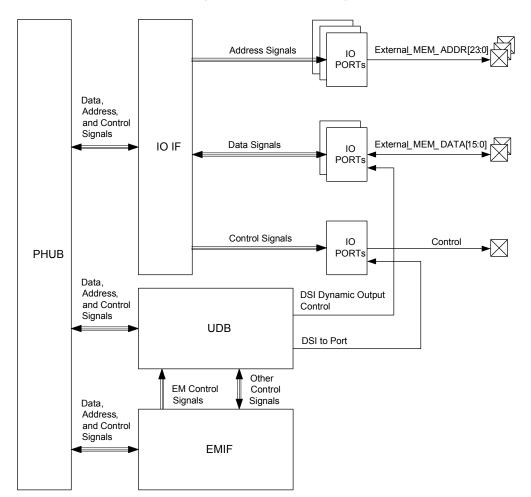

## 5.6 External Memory Interface

CY8C36 provides an external memory interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C36 supports only one type of external memory device at a time.

External memory can be accessed through the 8051 xdata space; up to 24 address bits can be used. See xdata Space on page 27. The memory can be 8 or 16 bits wide.

Figure 5-1. EMIF Block Diagram

## 5.7 Memory Map

The CY8C36 8051 memory map is very similar to the MCS-51 memory map.

#### 5.7.1 Code Space

The CY8C36 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 23.

#### 5.7.2 Internal Data Space

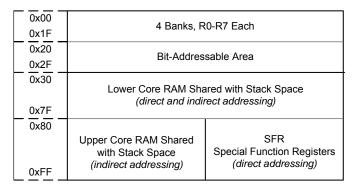

The CY8C36 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in "Static RAM" on page 23) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for four banks of registers R0-R7. The next 16 bytes are bit-addressable.

#### Figure 5-2. 8051 Internal Data Space

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 14.

#### 5.7.3 SFRs

The special function register (SFR) space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-4.

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | -    | -    | -    | -   | -   |

| 0×F0    | В          | -          | SFRPRT12SEL | -    | -    | -    | -   | -   |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        | -    | -    | -    | -   | -   |

| 0×E0    | ACC        | -          | -           | -    | -    | -    | -   | -   |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | -    | -    | -    | -   | -   |

| 0×D0    | PSW        | -          | -           | -    | -    | -    | -   | -   |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | -    | -    | -    | -   | -   |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | -    | _    | -    | -   | -   |

| 0×B8    | -          | -          | -           | -    | -    | -    | -   | -   |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | -    | _    | -    | -   | -   |

| 0×A8    | IE         | -          | -           | -    | _    | -    | -   | -   |

| 0×A0    | P2AX       | -          | SFRPRT1SEL  | -    | -    | -    | -   | -   |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | -    | -    | -    | -   | -   |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  | -           | DPX0 | _    | DPX1 | -   | -   |

| 0×88    | -          | SFRPRT0PS  | SFRPRT0SEL  | -    | _    | -    | -   | -   |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | -   |

#### Table 5-4. SFR Map

The CY8C36 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C36 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C36 family.

#### Table 6-1. Oscillator Summary

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax | Startup Time                          |

|---------|--------|----------------------------------|---------|-------------------|---------------------------------------|

| IMO     | 3 MHz  | ±1% over voltage and temperature | 62 MHz  | ±7%               | 13 µs max                             |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent | 5 ms typ, max is<br>crystal dependent |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent   | Input dependent                       |

| PLL     | 24 MHz | Input dependent                  | 67 MHz  | Input dependent   | 250 µs max                            |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent   | 1 µs max                              |

| ILO     | 1 kHz  | -50%, +100%                      | 100 kHz | -55%, +100%       | 15 ms max in lowest power mode        |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent | 500 ms typ, max is crystal dependent  |

#### 6.1.1 Internal Oscillators

Figure 6-1 shows that there are two internal oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

#### 6.1.1.1 Internal Main Oscillator

In most designs the IMO is the only clock source required, due to its  $\pm 1\%$  accuracy. The IMO operates with no external components and outputs a stable clock. A factory trim for each frequency range is stored in the device. With the factory trim, tolerance varies from  $\pm 1\%$  at 3 MHz, up to  $\pm 7\%$  at 62 MHz. The IMO, in conjunction with the PLL, allows generation of other clocks up to the device's maximum frequency (see Phase-Locked Loop).

The IMO provides clock outputs at 3, 6, 12, 24, 48, and 62 MHz.

#### 6.1.1.2 Clock Doubler

The clock doubler outputs a clock at twice the frequency of the input clock. The doubler works at an input frequency of 24 MHz, providing 48 MHz for the USB. It can be configured to use a clock from the IMO, MHzECO, or the DSI (external pin).

#### 6.1.1.3 Phase-Locked Loop

The PLL allows low frequency, high accuracy clocks to be multiplied to higher frequencies. This is a tradeoff between higher clock frequency and accuracy and, higher power consumption and increased startup time.

The PLL block provides a mechanism for generating clock frequencies based upon a variety of input sources. The PLL outputs clock frequencies in the range of 24 to 67 MHz. Its input and feedback dividers supply 4032 discrete ratios to create almost any desired clock frequency. The accuracy of the PLL output depends on the accuracy of the PLL input source. The most common PLL use is to multiply the IMO clock at 3 MHz, where it is most accurate, to generate the other clocks up to the device's maximum frequency.

The PLL achieves phase lock within 250 µs (verified by bit setting). It can be configured to use a clock from the IMO, MHZECO or DSI (external pin). The PLL clock source can be used until lock is complete and signaled with a lock bit. The lock signal can be routed through the DSI to generate an interrupt. Disable the PLL before entering low-power modes.

#### 6.1.1.4 Internal Low-Speed Oscillator

The ILO provides clock frequencies for low-power consumption, including the watchdog timer, and sleep timer. The ILO generates up to three different clocks: 1 kHz, 33 kHz, and 100 kHz.

The 1-kHz clock (CLK1K) is typically used for a background 'heartbeat' timer. This clock inherently lends itself to low-power supervisory operations such as the watchdog timer and long sleep intervals using the central timewheel (CTW).

The central timewheel is a 1-kHz, free-running, 13-bit counter clocked by the ILO. The central timewheel is always enabled, except in hibernate mode and when the CPU is stopped during debug on chip mode. It can be used to generate periodic interrupts for timing purposes or to wake the system from a low-power mode. Firmware can reset the central timewheel. Systems that require accurate timing should use the RTC capability instead of the central timewheel.

The 100-kHz clock (CLK100K) can be used as a low power master clock. It can also generate time intervals using the fast timewheel.

The fast timewheel is a 5-bit counter, clocked by the 100-kHz clock. It features programmable settings and automatically resets when the terminal count is reached. An optional interrupt can be generated each time the terminal count is reached. This enables flexible, periodic interrupts of the CPU at a higher rate than is allowed using the central timewheel.

The 33-kHz clock (CLK33K) comes from a divide-by-3 operation on CLK100K. This output can be used as a reduced accuracy version of the 32.768-kHz ECO clock with no need for a crystal.

#### 6.1.2 External Oscillators

Figure 6-1 shows that there are two external oscillators. They can be routed directly or divided. The direct routes may not have a 50% duty cycle. Divided clocks have a 50% duty cycle.

#### 6.1.2.1 MHz External Crystal Oscillator

The MHzECO provides high frequency, high precision clocking using an external crystal (see Figure 6-2). It supports a wide variety of crystal types, in the range of 4 to 25 MHz. When used in conjunction with the PLL, it can generate other clocks up to the device's maximum frequency (see Phase-Locked Loop). The GPIO pins connecting to the external crystal and capacitors are fixed. MHzECO accuracy depends on the crystal chosen.

## 7.3 UDB Array Description

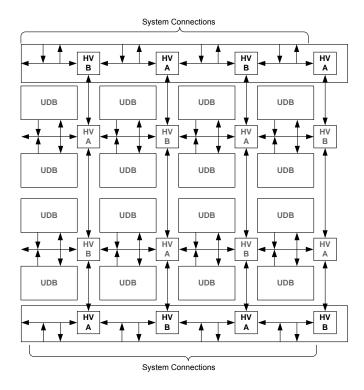

Figure 7-7 shows an example of a 16-UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

#### Figure 7-7. Digital System Interface Structure

#### 7.3.1 UDB Array Programmable Resources

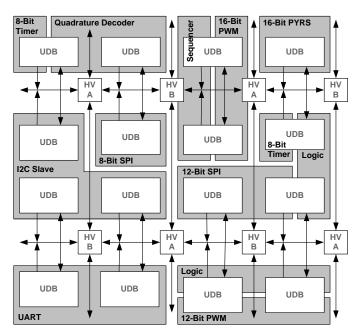

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

Figure 7-8. Function Mapping Example in a Bank of UDBs

## 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-9 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

## 7.8 I<sup>2</sup>C

PSoC includes a single fixed-function  $I^2C$  peripheral. Additional  $I^2C$  interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

The I<sup>2</sup>C peripheral provides a synchronous two-wire interface designed to interface the PSoC device with a two-wire I<sup>2</sup>C serial communication bus. It is compatible<sup>[20]</sup> with I<sup>2</sup>C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I<sup>2</sup>C bus I/O may be implemented with GPIO or SIO in open-drain modes.

To eliminate the need for excessive CPU intervention and overhead,  $I^2C$  specific support is provided for status detection and generation of framing bits.  $I^2C$  operates as a slave, a master, or multimaster (Slave and Master) $I^{21}$ . In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions.  $I^2C$  interfaces through DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup

address match. If wakeup

functionality is required, I<sup>2</sup>C pin connections are limited to one of two specific pairs of SIO pins. See descriptions of SCL and SDA pins in Pin Descriptions on page 12.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware support)

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

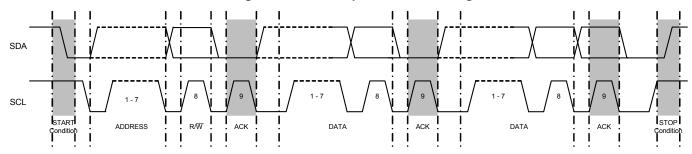

Data transfers follow the format shown in Figure 7-18. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

#### Figure 7-18. I<sup>2</sup>C Complete Transfer Timing

#### 7.8.1 External Electrical Connections

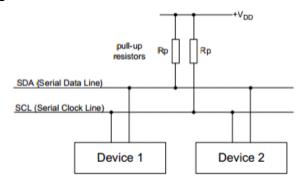

As Figure 7-19 shows, the  $I^2C$  bus requires external pull-up resistors (R<sub>P</sub>). These resistors are primarily determined by the supply voltage, bus speed, and bus capacitance. For detailed information on how to calculate the optimum pull-up resistor value for your design, we recommend using the UM10204 I2C-bus specification and user manual Rev 6, or newer, available from the NXP website at www.nxp.com.

#### Figure 7-19. Connection of Devices to the I<sup>2</sup>C Bus

Notes

- 20. The I<sup>2</sup>C peripheral is non-compliant with the NXP I<sup>2</sup>C specification in the following areas: analog glitch filter, I/O V<sub>OL</sub>/I<sub>OL</sub>, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 80 for details.

- 21. Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I2C component should be used instead.

## 7.9 Digital Filter Block

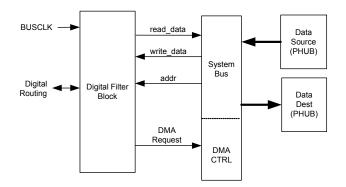

Some devices in the CY8C36 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one bus clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes MCU bandwidth.

The heart of the DFB is a datapath (DP), which is the numerical calculation unit of the DFB. The DP is a 24-bit fixed-point numerical processor containing a 48-bit multiply and accumulate function (MAC), a multi-function ALU, sample and coefficient data RAMs as well as data routing, shifting, holding and rounding functions.

In the MAC, two 24-bit values can be multiplied and the result added to the 48-bit accumulator in each bus clock cycle. The MAC is the only portion of the DP that is wider than 24 bits. All results from the MAC are passed on to the ALU as 24-bit values representing the high-order 24 bits in the accumulator shifted by one (bits 46:23). The MAC assumes an implied binary point after the most significant bit.

The DP also contains an optimized ALU that supports add, subtract, comparison, threshold, absolute value, squelch, saturation, and other functions. The DP unit is controlled by seven control fields totaling 18 bits coming from the DFB Controller. For more information see the TRM.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

#### Figure 7-20. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

## 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution Delta-Sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

#### 8.2.3 Start of Conversion Input

The SoC signal is used to start an ADC conversion. A digital clock or UDB output can be used to drive this input. It can be used when the sampling period must be longer than the ADC conversion time or when the ADC must be synchronized to other hardware. This signal is optional and does not need to be connected if ADC is running in a continuous mode.

#### 8.2.4 End of Conversion Output

The EoC signal goes high at the end of each ADC conversion. This signal may be used to trigger either an interrupt or DMA request.

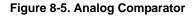

#### 8.3 Comparators

The CY8C36 family of devices contains four comparators in a device. Comparators have these features:

Input offset factory trimmed to less than 5 mV

- Rail-to-rail common mode input range (VSSA to VDDA)

- Speed and power can be traded off by using one of three modes: fast, slow, or ultra low-power

- Comparator outputs can be routed to lookup tables to perform simple logic functions and then can also be routed to digital blocks

- The positive input of the comparators may be optionally passed through a low pass filter. Two filters are provided

- Comparator inputs can be connections to GPIO, DAC outputs and SC block outputs

#### 8.3.1 Input and Output Interface

The positive and negative inputs to the comparators come from the analog global buses, the analog mux line, the analog local bus and precision reference through multiplexers. The output from each comparator could be routed to any of the two input LUTs. The output of that LUT is routed to the UDB Digital System Interface.

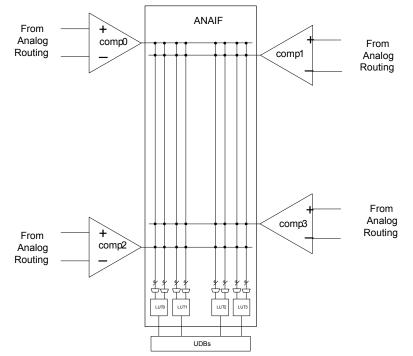

## 8.11 Sample and Hold

The main application for a sample and hold, is to hold a value stable while an ADC is performing a conversion. Some applications require multiple signals to be sampled simultaneously, such as for power calculations (V and I).

## Figure 8-13. Sample and Hold Topology ( $\Phi$ 1 and $\Phi$ 2 are opposite phases of a clock)

#### 8.11.1 Down Mixer

The SC/CT block can be used as a mixer to down convert an input signal. This circuit is a high bandwidth passive sample network that can sample input signals up to 14 MHz. This sampled value is then held using the opamp with a maximum clock rate of 4 MHz. The output frequency is at the difference between the input frequency and the highest integer multiple of the Local Oscillator that is less than the input.

#### 8.11.2 First Order Modulator - SC Mode

A first order modulator is constructed by placing the SC/CT block in an integrator mode and using a comparator to provide a 1-bit feedback to the input. Depending on this bit, a reference voltage is either subtracted or added to the input signal. The block output is the output of the comparator and not the integrator in the modulator case. The signal is downshifted and buffered and then processed by a decimator to make a delta-sigma converter or a counter to make an incremental converter. The accuracy of the sampled data from the first-order modulator is determined from several factors.

The main application for this modulator is for a low frequency ADC with high accuracy. Applications include strain gauges, thermocouples, precision voltage, and current measurement.

## 9. Programming, Debug Interfaces, Resources

PSoC devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. Three interfaces are available: JTAG, SWD, and SWV. JTAG and SWD support all programming and debug features of the device. JTAG also supports standard JTAG scan chains for board level test and chaining multiple JTAG devices to a single JTAG connection.

For more information on PSoC 3 Programming, refer to the  $PSoC^{\textcircled{R}}$  3 Device Programming Specifications.

Complete Debug on Chip (DoC) functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The PSoC Creator IDE software provides fully integrated programming and debug support for PSoC devices. The low cost MiniProg3 programmer and debugger is designed to provide full programming and debug support of PSoC devices in conjunction with the PSoC Creator IDE. PSoC JTAG, SWD, and SWV interfaces are compatible with industry standard third party tools.

All DOC circuits are disabled by default and can only be enabled in firmware. If not enabled, the only way to reenable them is to erase the entire device, clear flash protection, and reprogram the device with new firmware that enables DOC. Disabling DOC features, robust flash protection, and hiding custom analog and digital functionality inside the PSoC device provide a level of security not possible with multichip application solutions. Additionally, all device interfaces can be permanently disabled (Device Security) for applications concerned about phishing attacks due to a maliciously reprogrammed device. Permanently disabling interfaces is not recommended in most applications because the you cannot access the device later. Because all programming, debug, and test interfaces are disabled when Device Security is enabled, PSoCs with Device Security enabled may not be returned for failure analysis.

#### Table 9-1. Debug Configurations

| Debug and Trace Configuration | GPIO Pins Used |

|-------------------------------|----------------|

| All debug and trace disabled  | 0              |

| JTAG                          | 4 or 5         |

| SWD                           | 2              |

| SWV                           | 1              |

| SWD + SWV                     | 3              |

## Table 11-2. DC Specifications (continued)

| Parameter | Description Conditions                                                                                               |                                                                          | Min        | Typ <sup>[29]</sup> | Max | Units |    |

|-----------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------|---------------------|-----|-------|----|

|           | Sleep Mode <sup>[32]</sup>                                                                                           |                                                                          |            |                     |     |       |    |

|           | CPU = OFF                                                                                                            | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C | _                   | 1.1 | 2.3   | μA |

|           | RTC = ON (= ECO32K ON, in low-power                                                                                  | 4.5 V - 5.5 V                                                            | T = 25 °C  | _                   | 1.1 | 2.2   |    |

|           | mode)<br>Sleep timer = ON (= ILO ON at 1 kHz) <sup>[33]</sup>                                                        |                                                                          | T = 85 °C  | _                   | 15  | 30    |    |

|           | WDT = OFF                                                                                                            | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C | _                   | 1   | 2.2   | _  |

|           | I <sup>2</sup> C Wake = OFF                                                                                          | 2.7 V – 3.6 V                                                            | T = 25 °C  | _                   | 1   | 2.1   |    |

|           | Comparator = OFF                                                                                                     |                                                                          | T = 85 °C  | _                   | 12  | 28    |    |

|           | POR = ON<br>Boost = OFF                                                                                              | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = 25 °C  | _                   | 2.2 | 4.2   |    |

|           | SIO pins in single ended input, unregulated output mode                                                              | 1                                                                        |            |                     |     |       |    |

|           | Comparator = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF                                          | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V <sup>[35]</sup>   | T = 25 °C  | _                   | 2.2 | 2.7   |    |

|           | I <sup>2</sup> C Wake = OFF<br>POR = ON<br>Boost = OFF<br>SIO pins in single ended input, unregulated<br>output mode |                                                                          |            |                     |     |       |    |

|           | I <sup>2</sup> C Wake = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF<br>Comparator = OFF           | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7 V – 3.6 V <sup>[35]</sup>   | T = 25 °C  | -                   | 2.2 | 2.8   |    |

|           | POR = ON<br>Boost = OFF<br>SIO pins in single ended input, unregulated<br>output mode                                |                                                                          |            |                     |     |       |    |

|           | Hibernate Mode <sup>[32]</sup>                                                                                       |                                                                          |            |                     |     |       |    |

|           | Hibernate mode current                                                                                               | $V_{DD} = V_{DDIO} =$                                                    | T = -40 °C | -                   | 0.2 | 1.5   | μA |

|           | All regulators and oscillators off<br>SRAM retention                                                                 | 4.5 V - 5.5 V                                                            | T = 25 °C  | -                   | 0.5 | 1.5   |    |

|           | GPIO interrupts are active                                                                                           |                                                                          | T = 85 °C  | -                   | 4.1 | 5.3   |    |

|           | Boost = OFF                                                                                                          | V <sub>DD</sub> = V <sub>DDIO</sub> =                                    | T = -40 °C | -                   | 0.2 | 1.5   |    |

|           |                                                                                                                      | 2.7 V – 3.6 V                                                            | T = 25 °C  | -                   | 0.2 | 1.5   |    |

|           | output<br>mode                                                                                                       |                                                                          | T = 85 °C  | _                   | 3.2 | 4.2   |    |

|           |                                                                                                                      | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>1.71 V – 1.95 V <sup>[34]</sup> | T = -40 °C | -                   | 0.2 | 1.5   |    |

|           |                                                                                                                      | 1.71 V – 1.95 V <sup>[34]</sup>                                          | T = 25 °C  | -                   | 0.3 | 1.5   |    |

|           |                                                                                                                      |                                                                          | T = 85 °C  | _                   | 3.3 | 4.3   | 1  |

| DDAR      | Analog current consumption while device                                                                              | $V_{DDA} \le 3.6 V$                                                      | 1          | _                   | 0.3 | 0.6   | mA |

|           | is reset <sup>[36]</sup>                                                                                             | V <sub>DDA</sub> > 3.6 V                                                 |            | _                   | 1.4 | 3.3   | mA |

| DDR       | Digital current consumption while device is                                                                          | $V_{\text{DDD}} \le 3.6 \text{ V}$                                       |            | _                   | 1.1 | 3.1   | mA |

|           | reset <sup>[36]</sup>                                                                                                | ·                                                                        |            |                     |     | 5.1   |    |

Notes

- If V<sub>CCD</sub> and V<sub>CCA</sub> are externally regulated, the voltage difference between V<sub>CCD</sub> and V<sub>CCA</sub> must be less than 50 mV.

Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

Externally regulated mode.

Based on device characterization (not production tested).

Based on device characterization (not production tested).

Based on device characterization (not production tested).

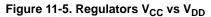

## **11.3 Power Regulators**

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.3.1 Digital Core Regulator

## Table 11-4. Digital Core Regulator DC Specifications

| Parameter        | Description                | Conditions                                                                                                                                               | Min | Тур  | Max | Units |

|------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| V <sub>DDD</sub> | Input voltage              |                                                                                                                                                          | 1.8 | -    | 5.5 | V     |

| V <sub>CCD</sub> | Output voltage             |                                                                                                                                                          | -   | 1.80 | -   | V     |

|                  | Regulator output capacitor | $\pm$ 10%, ×5R ceramic or better. The two V <sub>CCD</sub> pins must be shorted together, with as short a trace as possible, see Power System on page 31 | 0.9 | 1    | 1.1 | μF    |

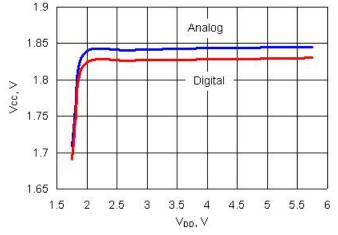

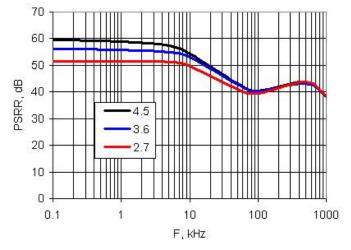

## Figure 11-6. Digital Regulator PSRR vs Frequency and V<sub>DD</sub>

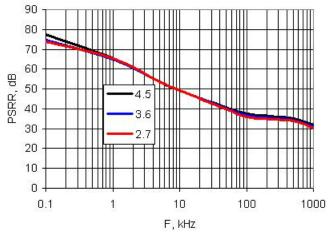

## 11.3.2 Analog Core Regulator

## Table 11-5. Analog Core Regulator DC Specifications

| Parameter        | Description                | Conditions                  | Min | Тур  | Max | Units |

|------------------|----------------------------|-----------------------------|-----|------|-----|-------|

| V <sub>DDA</sub> | Input voltage              |                             | 1.8 | -    | 5.5 | V     |

| V <sub>CCA</sub> | Output voltage             |                             | -   | 1.80 | -   | V     |

|                  | Regulator output capacitor | ±10%, ×5R ceramic or better | 0.9 | 1    | 1.1 | μF    |

## Table 11-12. SIO AC Specifications (continued)

| Parameter | Description                                                                                        | Conditions                               | Min | Тур | Max | Units |

|-----------|----------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

|           | SIO output operating frequency                                                                     | •                                        |     | •   |     |       |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 33  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | _   | 16  | MHz   |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 5   | MHz   |

| Fsioout   | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | _   | 4   | MHz   |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, fast strong drive<br>mode             | Output continuously switching into 25 pF | -   | _   | 20  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Regulated<br>output mode, fast strong drive<br>mode            | Output continuously switching into 25 pF | -   | -   | 10  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, slow strong drive<br>mode            | Output continuously switching into 25 pF | -   | -   | 2.5 | MHz   |

| Faiain    | SIO input operating frequency                                                                      | ·                                        | •   | · · |     |       |

| Fsioin    | 1.71 V <u>&lt;</u> V <sub>DDIO</sub> <u>&lt;</u> 5.5 V                                             | 90/10% V <sub>DDIO</sub>                 | -   | -   | 33  | MHz   |

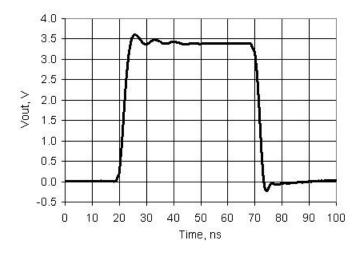

# Figure 11-20. SIO Output Rise and Fall Times, Fast Strong Mode, $V_{DDIO}$ = 3.3 V, 25 pF Load

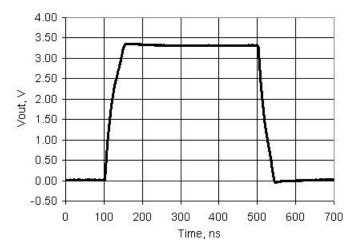

Figure 11-21. SIO Output Rise and Fall Times, Slow Strong Mode,  $V_{DDIO}$  = 3.3 V, 25 pF Load

## 11.4.4 XRES

## Table 11-17. XRES DC Specifications

| Parameter       | Description                                                   | Conditions | Min                   | Тур | Max                   | Units |

|-----------------|---------------------------------------------------------------|------------|-----------------------|-----|-----------------------|-------|

| V <sub>IH</sub> | Input voltage high threshold                                  |            | $0.7 \times V_{DDIO}$ | -   | -                     | V     |

| V <sub>IL</sub> | Input voltage low threshold                                   |            | -                     | -   | $0.3 \times V_{DDIO}$ | V     |

| Rpullup         | Pull-up resistor                                              |            | 3.5                   | 5.6 | 8.5                   | kΩ    |

| C <sub>IN</sub> | Input capacitance <sup>[50]</sup>                             |            | -                     | 3   | -                     | pF    |

| V <sub>H</sub>  | Input voltage hysteresis<br>(Schmitt–Trigger) <sup>[50]</sup> |            | -                     | 100 | -                     | mV    |

| Idiode          | Current through protection diode to $V_{DDIO}$ and $V_{SSIO}$ |            | -                     | -   | 100                   | μA    |

## Table 11-18. XRES AC Specifications

| Parameter          | Description       | Conditions | Min | Тур | Max | Units |

|--------------------|-------------------|------------|-----|-----|-----|-------|

| T <sub>RESET</sub> | Reset pulse width |            | 1   | -   | -   | μs    |

## 11.5 Analog Peripherals

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

## 11.5.1 Opamp

### Table 11-19. Opamp DC Specifications

| Parameter         | Description                                 | Conditions                                                                                               | Min                     | Тур  | Max                     | Units |

|-------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| V <sub>IOFF</sub> | Input offset voltage                        |                                                                                                          | -                       | -    | 2                       | mV    |

| V <sub>OS</sub>   | Input offset voltage                        |                                                                                                          | _                       |      | 2.5                     | mV    |

|                   |                                             | Operating temperature –40 °C to 70 °C                                                                    | _                       | I    | 2                       | mV    |

| TCV <sub>OS</sub> | Input offset voltage drift with temperature | Power mode = high                                                                                        | -                       | -    | ±30                     | µV/°C |

| Ge1               | Gain error, unity gain buffer mode          | Rload = 1 k $\Omega$                                                                                     | -                       | -    | ±0.1                    | %     |

| C <sub>IN</sub>   | Input capacitance                           | Routing from pin                                                                                         | -                       | -    | 18                      | pF    |

| V <sub>O</sub>    | Output voltage range                        | 1 mA, source or sink, power mode<br>= high                                                               | V <sub>SSA</sub> + 0.05 | -    | V <sub>DDA</sub> – 0.05 | V     |

| I <sub>OUT</sub>  | Output current capability, source or sink   | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, V <sub>DDA</sub> > 2.7 V              | 25                      | -    | -                       | mA    |

|                   |                                             | $V_{SSA}$ + 500 mV $\leq$ Vout $\leq$ V <sub>DDA</sub><br>-500 mV, 1.7 V = V <sub>DDA</sub> $\leq$ 2.7 V | 16                      | Ι    | -                       | mA    |

| I <sub>DD</sub>   | Quiescent current                           | Power mode = min                                                                                         | -                       | 250  | 400                     | uA    |

|                   |                                             | Power mode = low                                                                                         | -                       | 250  | 400                     | uA    |

|                   |                                             | Power mode = med                                                                                         | -                       | 330  | 950                     | uA    |

|                   |                                             | Power mode = high                                                                                        | -                       | 1000 | 2500                    | uA    |

| CMRR              | Common mode rejection ratio                 |                                                                                                          | 80                      | -    | -                       | dB    |

| PSRR              | Power supply rejection ratio                | $V_{DDA} \ge 2.7 V$                                                                                      | 85                      | -    | -                       | dB    |

|                   |                                             | V <sub>DDA</sub> < 2.7 V                                                                                 | 70                      | -    | -                       | dB    |

| I <sub>IB</sub>   | Input bias current <sup>[50]</sup>          | 25 °C                                                                                                    | _                       | 10   | _                       | pА    |

#### Note

50. Based on device characterization (Not production tested).

## 11.5.5 Comparator

## Table 11-26. Comparator DC Specifications

| Parameter         | Description                                       | Conditions                                             | Min              | Тур | Max                     | Units |

|-------------------|---------------------------------------------------|--------------------------------------------------------|------------------|-----|-------------------------|-------|

|                   | Input offset voltage in fast mode                 | Factory trim, V <sub>DDA</sub> > 2.7 V,<br>Vin ≥ 0.5 V | -                |     | 10                      | mV    |

|                   | Input offset voltage in slow mode                 | Factory trim, Vin $\ge 0.5$ V                          | -                |     | 9                       | mV    |

| V <sub>OS</sub>   | Input offset voltage in fast mode <sup>[60]</sup> | Custom trim                                            | -                | -   | 4                       | mV    |

|                   | Input offset voltage in slow mode <sup>[60]</sup> | Custom trim                                            | -                | -   | 4                       | mV    |