Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3666axi-200t |

# 1. Architectural Overview

Introducing the CY8C36 family of ultra low-power, flash Programmable System-on-Chip (PSoC®) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C36 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

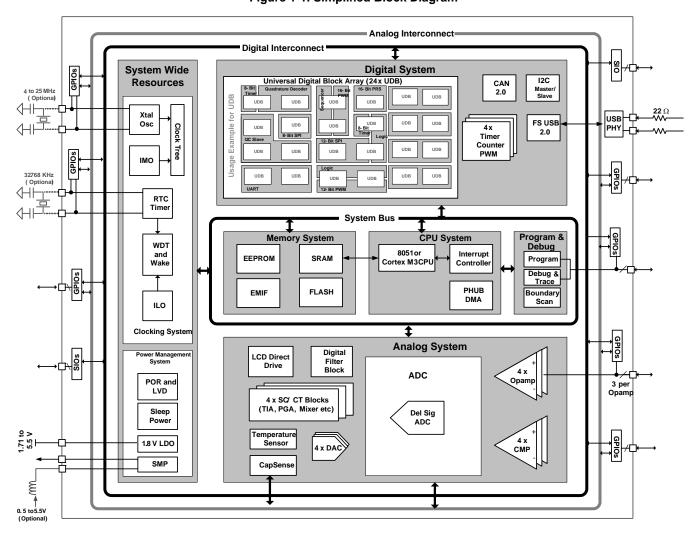

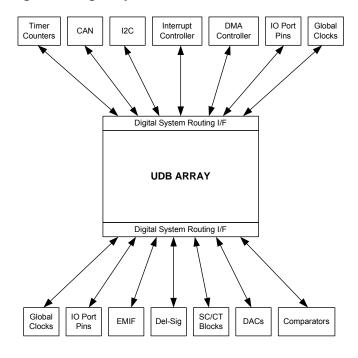

Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C36 family. They are:

- 8051 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

- Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, low-power UDBs. PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/programmable logic device (PLD) functionality, together with a small state machine engine to support a wide variety of peripherals.

# 5.6 External Memory Interface

CY8C36 provides an external memory interface (EMIF) for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles.

Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C36 supports only one type of external memory device at a time.

External memory can be accessed through the 8051 xdata space; up to 24 address bits can be used. See xdata Space on page 27. The memory can be 8 or 16 bits wide.

External\_MEM\_ADDR[23: Address Signals **PORTs** Data, Address, and Control Signals Data Signals External\_MEM\_DATA[15:0] IO IF Ю **PORTs** Control Signals IO Control **PHUB** PORT: Data, Address, **DSI Dynamic Output** and Control Control Signals **UDB** DSI to Port Other **EM Control** Control Signals Data, Signals Address, and Control Signals **EMIF**

Figure 5-1. EMIF Block Diagram

Document Number: 001-53413 Rev. \*Y Page 25 of 137

# 5.7 Memory Map

The CY8C36 8051 memory map is very similar to the MCS-51 memory map.

#### 5.7.1 Code Space

The CY8C36 8051 code space is 64 KB. Only main flash exists in this space. See the "Flash Program Memory" section on page 23.

#### 5.7.2 Internal Data Space

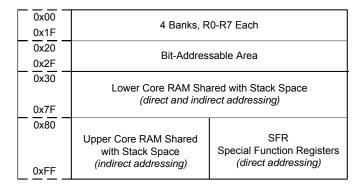

The CY8C36 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in "Static RAM" on page 23) and a 128-byte space for Special Function Registers (SFRs). See Figure 5-2. The lowest 32 bytes are used for four banks of registers R0-R7. The next 16 bytes are bit-addressable.

Figure 5-2. 8051 Internal Data Space

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 14.

#### 5.7.3 SFRs

The special function register (SFR) space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-4.

Table 5-4. SFR Map

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | _    | -    | _    | _   | -   |

| 0×F0    | В          | _          | SFRPRT12SEL | _    | -    | _    | _   | -   |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        | _    | -    | _    | _   | -   |

| 0×E0    | ACC        | _          | _           | _    | _    | _    | _   | _   |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | _    | _    | _    | _   | _   |

| 0×D0    | PSW        | _          | _           | _    | _    | _    | _   | _   |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | -    | _    | _    | =   | -   |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | _    | _    | _    | _   | _   |

| 0×B8    | _          | _          | _           | -    | _    | _    | _   | -   |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | _    | _    | _    | _   | _   |

| 0×A8    | IE         | _          | _           | _    | _    | _    | _   | _   |

| 0×A0    | P2AX       | _          | SFRPRT1SEL  | _    | _    | _    | _   | _   |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | _    | _    | _    | _   | _   |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  | _           | DPX0 | _    | DPX1 | _   | _   |

| 0×88    | _          | SFRPRT0PS  | SFRPRT0SEL  | _    | _    | _    | _   | _   |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | _   |

The CY8C36 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C36 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C36 family.

# 6.2 Power System

The power system consists of separate analog, digital, and I/O supply pins, labeled VDDA, VDDD, and VDDIO×, respectively. It also includes two internal 1.8 V regulators that provide the digital (VCCD) and analog (VCCA) supplies for the internal core logic. The output pins of the regulators (VCCD and VCCA) and the

VDDIO pins must have capacitors connected as shown in Figure 6-4. The two VCCD pins must be shorted together, with as short a trace as possible, and connected to a 1- $\mu$ F ±10% ×5R capacitor. The power system also contains a sleep regulator, an I<sup>2</sup>C regulator, and a hibernate regulator.

VDDD VDDIO2 VDDIOO 0.1 μF 0.1μF VDIDION I/O Supply I/O Supply I2C Regulator Sleep Regulator Digital VDDA Domain VDDA VCCA Analog Regulator Digital Regulators 0.1μF VSSB  $\forall$ vss Analog Domain Hibernate Regulator VDDD I/O Supply I/O Supply 0.1μF 0.1 μF VDDI03

Figure 6-4. PSoC Power System

# Notes

- The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-8 on page 12.

- It is good practice to check the datasheets for your bypass capacitors, specifically the working voltage and the DC bias specifications. With some capacitors, the actual capacitance can decrease considerably when the DC bias (VDDX or VCCX in Figure 6-4) is a significant percentage of the rated working voltage.

- You can power the device in internally regulated mode, where the voltage applied to the VDDx pins is as high as 5.5 V, and the internal regulators provide the core voltages. In this mode, do not apply power to the VCCx pins, and do not tie the VDDx pins to the VCCx pins.

- You can also power the device in externally regulated mode, that is, by directly powering the VCCD and VCCA pins. In this configuration, the VDDD pins should be shorted to the VCCD pins and the VDDA pin should be shorted to the VCCA pin. The allowed supply range in this configuration is 1.71 V to 1.89 V. After power up in this configuration, the internal regulators are on by default, and should be disabled to reduce power consumption.

Document Number: 001-53413 Rev. \*Y Page 31 of 137

#### 6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and RTC functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all V<sub>DDIO</sub> supplies are at valid voltage levels.

Table 6-2. Power Modes

| Power<br>Modes      | Description                                                                                                                                                                                               | Entry Condition                            | Wakeup<br>Source                                           | Active Clocks         | Regulator                                                                                                             |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all peripherals available (programmable)                                                                                                                                       | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                              | Any<br>(programmable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Alternate<br>Active | Similar to Active mode, and is typically configured to have fewer peripherals active to reduce power. One possible configuration is to use the UDBs for processing, with the CPU turned off               | Manual register entry                      | Any interrupt                                              | Any<br>(programmable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                     | Manual register entry                      | Comparator,<br>PICU, I <sup>2</sup> C,<br>RTC, CTW,<br>LVD | ILO/kHzECO            | Both digital and analog regulators buzzed. Digital and analog regulators can be disabled if external regulation used. |

| Hibernate           | All subsystems automatically disabled Lowest power consuming mode with all peripherals and internal regulators disabled, except hibernate regulator is enabled Configuration and memory contents retained | Manual register entry                      | PICU                                                       | -                     | Only hibernate regulator active.                                                                                      |

# **Table 6-3. Power Modes Wakeup Time and Power Consumption**

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(Typ)       | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|------------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | -              | 1.2 mA <sup>[16]</sup> | Yes               | All                  | All                 | All                        | _                                                       | All               |

| Alternate<br>Active | -              | _                      | User<br>defined   | All                  | All                 | All                        | -                                                       | All               |

| Sleep               | <15 µs         | 1 μΑ                   | No                | I <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | XRES, LVD,<br>WDR |

| Hibernate           | <100 µs        | 200 nA                 | No                | None                 | None                | None                       | PICU                                                    | XRES              |

#### Note

Document Number: 001-53413 Rev. \*Y

<sup>16.</sup> Bus clock off. Execute from cache at 6 MHz. See Table 11-2 on page 72.

# PSoC® 3: CY8C36 Family Datasheet

The switching frequency is set to 400 kHz using an oscillator integrated into the boost converter. The boost converter can be operated in two different modes: active and standby. Active mode is the normal mode of operation where the boost regulator actively generates a regulated output voltage. In standby mode, most boost functions are disabled, thus reducing power consumption of the boost circuit. Only minimal power is provided, typically < 5  $\mu A$  to power the PSoC device in Sleep mode. The boost typically draws 250  $\mu A$  in active mode and 25  $\mu A$  in standby mode. The boost operating modes must be used in conjunction with chip power modes to minimize total power consumption. Table 6-1 lists the boost power modes available in different chip power modes.

Table 6-1. Chip and Boost Power Modes Compatibility

| Chip Power Modes                     | Boost Power Modes                                                                                                                                                            |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip-active or alternate active mode | Boost must be operated in its active mode.                                                                                                                                   |

| Chip-sleep mode                      | Boost can be operated in either active or standby mode. In boost standby mode, the chip must wake up periodically for boost active-mode refresh.                             |

| Chip-hibernate mode                  | Boost can be operated in its active mode. However, it is recommended not to use the boost in chip hibernate mode due to the higher current consumption in boost active mode. |

#### 6.2.2.1 Boost Firmware Requirements

To ensure boost inrush current is within specification at startup, the **Enable Fast IMO During Startup** value must be unchecked in the PSoC Creator IDE. The **Enable Fast IMO During Startup** option is found in PSoC Creator in the design wide resources (cydwr) file **System** tab. Un-checking this option configures the device to run at 12 MHz vs 48 MHz during startup while configuring the device. The slower clock speed results in reduced current draw through the boost circuit.

# 6.2.2.2 Boost Design Process

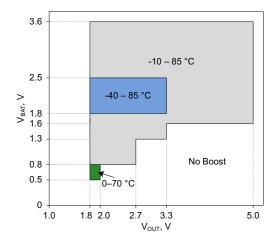

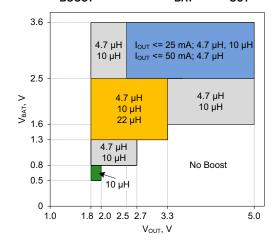

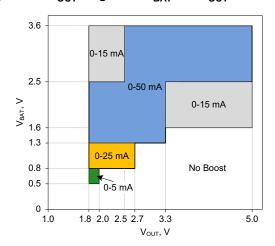

Correct operation of the boost converter requires specific component values determined for each designs unique operating conditions. The  $C_{BAT}$  capacitor, Inductor, Schottky diode, and  $C_{BOOST}$  capacitor components are required with the values specified in the electrical specifications, Table 11-7 on page 78. The only variable component value is the inductor  $L_{BOOST}$  which is primarily sized for correct operation of the boost across operating conditions and secondarily for efficiency. Additional operating region constraints exist for  $V_{OUT},\,V_{BAT},\,I_{OUT},\,$  and  $T_A.$

The following steps must be followed to determine boost converter operating parameters and  $L_{\mbox{\footnotesize{BOOST}}}$  value.

- Choose desired V<sub>BAT</sub>, V<sub>OUT</sub>, T<sub>A</sub>, and I<sub>OUT</sub> operating condition ranges for the application.

- Determine if V<sub>BAT</sub> and V<sub>OUT</sub> ranges fit the boost operating range based on the T<sub>A</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-8 on page 78. If the operating ranges are not met, modify the operating conditions or use an external boost regulator.

- Determine if the desired ambient temperature (T<sub>A</sub>) range fits the ambient temperature operating range based on the T<sub>A</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-8 on page 78. If the temperature range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

- 4. Determine if the desired output current (I<sub>OUT</sub>) range fits the output current operating range based on the I<sub>OUT</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-9 on page 78. If the output current range is not met, modify the operating conditions and return to step 2, or use an external boost regulator.

- Find the allowed inductor values based on the L<sub>BOOST</sub> values over V<sub>BAT</sub> and V<sub>OUT</sub> chart, Figure 11-10 on page 78.

- 6. Based on the allowed inductor values, inductor dimensions, inductor cost, boost efficiency, and V<sub>RIPPLE</sub> choose the optimum inductor value for the system. Boost efficiency and V<sub>RIPPLE</sub> typical values are provided in the Efficiency vs V<sub>BAT</sub> and V<sub>RIPPLE</sub> vs V<sub>BAT</sub> charts, Figure 11-11 on page 79 through Figure 11-14 on page 79. In general, if high efficiency and low V<sub>RIPPLE</sub> are most important, then the highest allowed inductor value should be used. If low inductor cost or small inductor size are most important, then one of the smaller allowed inductor values should be used. If the allowed inductor(s) efficiency, V<sub>RIPPLE</sub>, cost or dimensions are not acceptable for the application than an external boost regulator should be used.

#### 6.3 Reset

CY8C36 has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring The analog and digital power voltages, VDDA, VDDD, VCCA, and VCCD are monitored in several different modes during power up, active mode, and sleep mode (buzzing). If any of the voltages goes outside predetermined ranges then a reset is generated. The monitors are programmable to generate an interrupt to the processor under certain conditions before reaching the reset thresholds.

- External The device <u>can</u> be reset from <u>an</u> external source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull-up to VDDIO1. VDDD, VDDA, and VDDIO1 must all have voltage applied before the part comes out of reset.

- Watchdog timer A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset.

- Software The device can be reset under program control.

Document Number: 001-53413 Rev. \*Y Page 35 of 137

#### 6.4.1 Drive Modes

Each GPIO and SIO pin is individually configurable into one of the eight drive modes listed in Table 6-3. Three configuration bits are used for each pin (DM[2:0]) and set in the PRTxDM[2:0] registers. Figure 6-12 depicts a simplified pin view based on each of the eight drive modes. Table 6-3 shows the I/O pin's drive state based on the port data register value or digital array signal if bypass mode is selected. Note that the actual I/O pin voltage is determined by a combination of the selected drive mode and the load at the pin. For example, if a GPIO pin is configured for resistive pull-up mode and driven high while the pin is floating, the voltage measured at the pin is a high logic state. If the same GPIO pin is externally tied to ground then the voltage unmeasured at the pin is a low logic state.

0. High Impedance 1. High Impedance 2. Resistive Pull-Up 3. Resistive Pull-Down 4. Open Drain, 5. Open Drain, 7. Resistive Pull-Up 6. Strong Drive Drives Low and Pull-Dowr

Figure 6-12. Drive Mode

The 'Out' connection is driven from either the Digital System (when the Digital Output terminal is connected) or the Data Register

When HW connection is disabled).

The 'In' connection drives the Pin State register, and the Digital System if the Digital Input terminal is enabled and connected. The 'An' connection connects to the Analog System.

Table 6-3. Drive Modes

| Diagram | Drive Mode                                      | PRTxDM2 | PRTxDM1 | PRTxDM0 | PRTxDR = 1    | PRTxDR = 0   |

|---------|-------------------------------------------------|---------|---------|---------|---------------|--------------|

| 0       | High impedance analog                           | 0       | 0       | 0       | High Z        | High Z       |

| 1       | High impedance digital                          | 0       | 0       | 1       | High Z        | High Z       |

| 2       | Resistive pull-up <sup>[18]</sup>               | 0       | 1       | 0       | Res High (5K) | Strong Low   |

| 3       | Resistive pull-down <sup>[18]</sup>             | 0       | 1       | 1       | Strong High   | Res Low (5K) |

| 4       | Open drain, drives low                          | 1       | 0       | 0       | High Z        | Strong Low   |

| 5       | Open drain, drive high                          | 1       | 0       | 1       | Strong High   | High Z       |

| 6       | Strong drive                                    | 1       | 1       | 0       | Strong High   | Strong Low   |

| 7       | Resistive pull-up and pull-down <sup>[18]</sup> | 1       | 1       | 1       | Res High (5K) | Res Low (5K) |

#### Note

<sup>18.</sup> Resistive pull-up and pull-down are not available with SIO in regulated output mode.

# 7.3 UDB Array Description

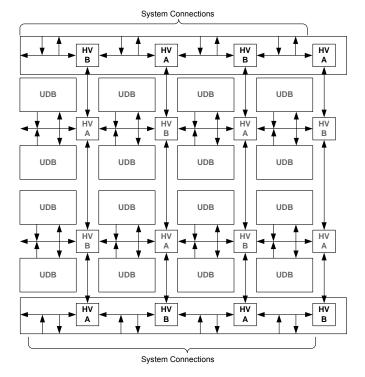

Figure 7-7 shows an example of a 16-UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

Figure 7-7. Digital System Interface Structure

# 7.3.1 UDB Array Programmable Resources

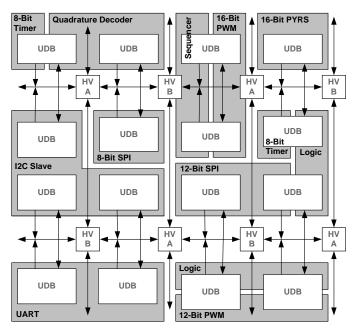

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions.

An example of this is the 8-bit Timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

Figure 7-8. Function Mapping Example in a Bank of UDBs

# 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-9 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

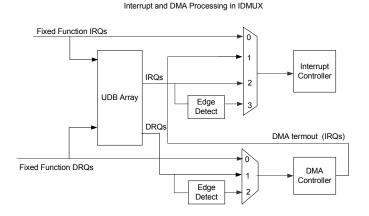

Figure 7-9. Digital System Interconnect

Interrupt and DMA routing is very flexible in the CY8C36 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

Figure 7-10. Interrupt and DMA Processing in the IDMUX

# 7.4.1 I/O Port Routing

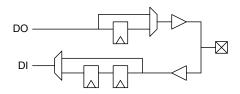

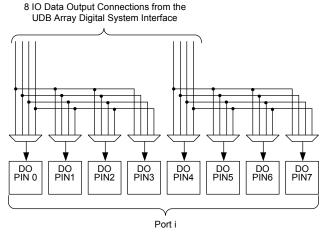

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1 on page 28). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

Figure 7-11. I/O Pin Synchronization Routing

Figure 7-12. I/O Pin Output Connectivity

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

Document Number: 001-53413 Rev. \*Y Page 50 of 137

# PSoC® 3: CY8C36 Family Datasheet

For most designs, the default values in Table 7-2 will provide excellent performance without any calculations. The default values were chosen to use standard resistor values between the minimum and maximum limits. The values in Table 7-2 work for designs with 1.8 V to 5.0V  $V_{DD}$ , less than 200-pF bus capacitance ( $C_{B}$ ), up to 25  $\mu A$  of total input leakage ( $I_{IL}$ ), up to 0.4 V output voltage level ( $V_{OL}$ ), and a max  $V_{IH}$  of 0.7  $^{*}$   $V_{DD}$ . Standard Mode and Fast Mode can use either GPIO or SIO PSoC pins. Fast Mode Plus requires use of SIO pins to meet the  $V_{OL}$  spec at 20 mA. Calculation of custom pull-up resistor values is required; if your design does not meet the default assumptions, you use series resistors (RS) to limit injected noise, or you need to maximize the resistor value for low power consumption.

Table 7-2. Recommended default Pull-up Resistor Values

|                          | R <sub>P</sub> | Units |

|--------------------------|----------------|-------|

| Standard Mode – 100 kbps | 4.7 k, 5%      | Ω     |

| Fast Mode – 400 kbps     | 1.74 k, 1%     | Ω     |

| Fast Mode Plus – 1 Mbps  | 620, 5%        | Ω     |

Calculation of the ideal pull-up resistor value involves finding a value between the limits set by three equations detailed in the NXP  $I^2$ C specification. These equations are:

# Equation 1:

$$R_{PMIN} = (V_{DD}(max) - V_{OL}(max))/(I_{OL}(min))$$

#### **Equation 2:**

$$R_{PMAX} = T_R(max)/0.8473 \times C_R(max)$$

# **Equation 3:**

$$R_{PMAX} = V_{DD}(min) - V_{IH}(min) + V_{NH}(min)/I_{IH}(max)$$

Equation parameters:

$V_{DD}$  = Nominal supply voltage for  $I^2C$  bus

V<sub>OL</sub> = Maximum output low voltage of bus devices.

I<sub>OI</sub> = Low-level output current from I<sup>2</sup>C specification

$T_R$  = Rise Time of bus from I<sup>2</sup>C specification

C<sub>B</sub> = Capacitance of each bus line including pins and PCB traces

V<sub>IH</sub> = Minimum high-level input voltage of all bus devices

V<sub>NH</sub> = Minimum high-level input noise margin from I<sup>2</sup>C specification

I<sub>IH</sub> = Total input leakage current of all devices on the bus

The supply voltage ( $V_{DD}$ ) limits the minimum pull-up resistor value due to bus devices maximum low output voltage ( $V_{OL}$ ) specifications. Lower pull-up resistance increases current through the pins and can, therefore, exceed the spec conditions of  $V_{OL}$ . Equation 1 is derived using Ohm's law to determine the minimum resistance that will still meet the  $V_{OL}$  specification at 3 mA for standard and fast modes, and 20 mA for fast mode plus at the given  $V_{DD}$ .

Equation 2 determines the maximum pull-up resistance due to bus capacitance. Total bus capacitance is comprised of all pin, wire, and trace capacitance on the bus. The higher the bus capacitance, the lower the pull-up resistance required to meet the specified bus speeds rise time due to RC delays. Choosing a pull-up resistance higher than allowed can result in failing timing requirements resulting in communication errors. Most designs with five or less I<sup>2</sup>C devices and up to 20 centimeters of bus trace length have less than 100 pF of bus capacitance.

A secondary effect that limits the maximum pull-up resistor value is total bus leakage calculated in Equation 3. The primary source of leakage is I/O pins connected to the bus. If leakage is too high, the pull-ups will have difficulty maintaining an acceptable  $V_{IH}$  level causing communication errors. Most designs with five or less  $I^2C$  devices on the bus have less than 10  $\mu A$  of total leakage current.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

The opamp and resistor array is programmable to perform various analog functions including

- Naked operational amplifier Continuous mode

- Unity-gain buffer Continuous mode

- Programmable gain amplifier (PGA) Continuous mode

- Transimpedance amplifier (TIA) Continuous mode

- Up/down mixer Continuous mode

- Sample and hold mixer (NRZ S/H) Switched cap mode

- First order analog to digital modulator Switched cap mode

#### 8.5.1 Naked Opamp

The Naked Opamp presents both inputs and the output for connection to internal or external signals. The opamp has a unity gain bandwidth greater than 6.0 MHz and output drive current up to 650  $\mu$ A. This is sufficient for buffering internal signals (such as DAC outputs) and driving external loads greater than 7.5 k $\Omega$ .

#### 8.5.2 Unity Gain

The Unity Gain buffer is a Naked Opamp with the output directly connected to the inverting input for a gain of 1.00. It has a –3 dB bandwidth greater than 6.0 MHz.

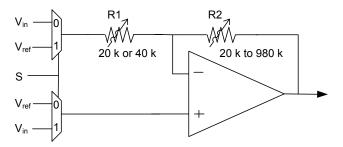

#### 8.5.3 PGA

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-8 on page 62. The schematic in Figure 8-8 on page 62 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

Table 8-3. Bandwidth

| Gain | Bandwidth |

|------|-----------|

| 1    | 6.0 MHz   |

| 24   | 340 kHz   |

| 48   | 220 kHz   |

| 50   | 215 kHz   |

Figure 8-8. PGA Resistor Settings

The PGA is used in applications where the input signal may not be large enough to achieve the desired resolution in the ADC, or dynamic range of another SC/CT block such as a mixer. The gain is adjustable at runtime, including changing the gain of the PGA prior to each ADC sample.

#### 8.5.4 TIA

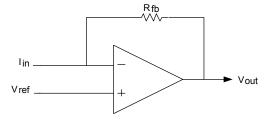

The Transimpedance Amplifier (TIA) converts an internal or external current to an output voltage. The TIA uses an internal feedback resistor in a continuous time configuration to convert input current to output voltage. For an input current  $I_{in}$ , the output voltage is  $V_{REF}$ -  $I_{in}$  x  $R_{fb}$ , where  $V_{REF}$  is the value placed on the non inverting input. The feedback resistor Rfb is programmable between 20  $K\Omega$  and 1  $M\Omega$  through a configuration register. Table 8-4 shows the possible values of Rfb and associated configuration settings.

Table 8-4. Feedback Resistor Settings

| Configuration Word | Nominal $R_{fb}(K\Omega)$ |

|--------------------|---------------------------|

| 000b               | 20                        |

| 001b               | 30                        |

| 010b               | 40                        |

| 011b               | 60                        |

| 100b               | 120                       |

| 101b               | 250                       |

| 110b               | 500                       |

| 111b               | 1000                      |

Figure 8-9. Continuous Time TIA Schematic

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the  $V_{REF}$  TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

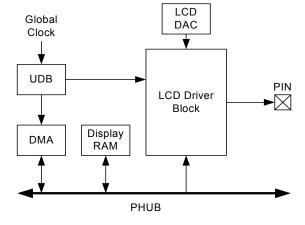

#### 8.6 LCD Direct Drive

The PSoC Liquid Crystal Display (LCD) driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C36 family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

Document Number: 001-53413 Rev. \*Y

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

# Figure 8-10. LCD System

# 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

#### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

# 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, and proximity detection. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator. A capacitive sensing method using a Delta-Sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

# 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

Table 11-7. Recommended External Components for Boost Circuit

| Parameter          | Description                                                              | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                           | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                          | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                          | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μΗ    |

| C <sub>BOOST</sub> | Total capacitance sum of $V_{\rm DDD}, V_{\rm DDA}, V_{\rm DDIO}^{[41]}$ |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                 |                | 17.0 | 22.0 | 27.0 | μF    |

| I <sub>F</sub>     | Schottky diode average forward current                                   |                | 1.0  | _    | 1    | Α     |

| V <sub>R</sub>     | Schottky reverse voltage                                                 |                | 20.0 | _    | 1    | V     |

Figure 11-8.  $T_A$  range over  $V_{BAT}$  and  $V_{OUT}$

Figure 11-10.  $L_{\text{BOOST}}$  values over  $V_{\text{BAT}}$  and  $V_{\text{OUT}}$

Figure 11-9.  $I_{OUT}$  range over  $V_{BAT}$  and  $V_{OUT}$

#### Note

<sup>41.</sup> Based on device characterization (Not production tested).

# 11.4 Inputs and Outputs

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

When the power supplies ramp up, there are low-impedance connections between each GPIO pin and its  $V_{DDIO}$  supply. This causes the pin voltages to track  $V_{DDIO}$  until both  $V_{DDIO}$  and  $V_{DDA}$  reach the IPOR voltage, which can be as high as 1.45 V. At that point, the low-impedance connections no longer exist and the pins change to their normal NVL settings.

11.4.1 GPIO

Table 11-9. GPIO DC Specifications

| Parameter       | Description                                                                 | Conditions                                                        | Min                     | Тур | Max                     | Units |

|-----------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|-----|-------------------------|-------|

| $V_{IH}$        | Input voltage high threshold                                                | CMOS Input, PRT[×]CTL = 0                                         | $0.7 \times V_{DDIO}$   | _   | -                       | V     |

| $V_{IL}$        | Input voltage low threshold                                                 | CMOS Input, PRT[×]CTL = 0                                         | _                       | -   | $0.3 \times V_{DDIO}$   | V     |

| V <sub>IH</sub> | Input voltage high threshold                                                | LVTTL Input, PRT[×]CTL = 1,V <sub>DDIO</sub> < 2.7 V              | 0.7 × V <sub>DDIO</sub> | -   | _                       | V     |

| V <sub>IH</sub> | Input voltage high threshold                                                | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7 \text{ V}$ | 2.0                     | -   | _                       | V     |

| V <sub>IL</sub> | Input voltage low threshold                                                 | LVTTL Input, PRT[×]CTL = 1,V <sub>DDIO</sub> < 2.7 V              | _                       | -   | 0.3 × V <sub>DDIO</sub> | V     |

| V <sub>IL</sub> | Input voltage low threshold                                                 | LVTTL Input, PRT[ $\times$ ]CTL = 1, $V_{DDIO} \ge 2.7 \text{ V}$ | _                       | -   | 0.8                     | V     |

| V <sub>OH</sub> | Output voltage high                                                         | I <sub>OH</sub> = 4 mA at 3.3 V <sub>DDIO</sub>                   | V <sub>DDIO</sub> – 0.6 | _   | _                       | V     |

|                 |                                                                             | I <sub>OH</sub> = 1 mA at 1.8 V <sub>DDIO</sub>                   | V <sub>DDIO</sub> – 0.5 | _   | _                       | V     |

| $V_{OL}$        | Output voltage low                                                          | I <sub>OL</sub> = 8 mA at 3.3 V <sub>DDIO</sub>                   | _                       | _   | 0.6                     | V     |

|                 |                                                                             | I <sub>OL</sub> = 4 mA at 1.8 V <sub>DDIO</sub>                   | _                       | _   | 0.6                     | V     |

|                 |                                                                             | I <sub>OL</sub> = 3 mA at 3.3 V <sub>DDIO</sub>                   | _                       | _   | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                                            |                                                                   | 3.5                     | 5.6 | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                                          |                                                                   | 3.5                     | 5.6 | 8.5                     | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value)[43]                                  | 25 °C, V <sub>DDIO</sub> = 3.0 V                                  | _                       | _   | 2                       | nA    |

| C <sub>IN</sub> | Input capacitance <sup>[43]</sup>                                           | GPIOs not shared with opamp outputs, MHz ECO or kHzECO            | _                       | 4   | 7                       | pF    |

|                 |                                                                             | GPIOs shared with MHz ECO or kHzECO <sup>[44]</sup>               | _                       | 5   | 7                       | pF    |

|                 |                                                                             | GPIOs shared with opamp outputs                                   | _                       | -   | 18                      | pF    |

| V <sub>H</sub>  | Input voltage hysteresis (Schmitt-Trigger) <sup>[43]</sup>                  |                                                                   | _                       | 40  | _                       | mV    |

| Idiode          | Current through protection diode to V <sub>DDIO</sub> and V <sub>SSIO</sub> |                                                                   | -                       | -   | 100                     | μA    |

| Rglobal         | Resistance pin to analog global bus                                         | 25 °C, V <sub>DDIO</sub> = 3.0 V                                  | -                       | 320 | _                       | Ω     |

| Rmux            | Resistance pin to analog mux bus                                            | 25 °C, V <sub>DDIO</sub> = 3.0 V                                  | _                       | 220 | _                       | Ω     |

#### Notes

<sup>43.</sup> Based on device characterization (Not production tested).

<sup>44.</sup> For information on designing with PSoC oscillators, refer to the application note, AN54439 - PSoC® 3 and PSoC 5 External Oscillator.

# 11.4.2 SIO

# Table 11-11. SIO DC Specifications

| Parameter       | Description                                                | Conditions                                                                             | Min                     | Тур                                                                            | Max                     | Units |

|-----------------|------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------|-------------------------|-------|

| Vinmax          | Maximum input voltage                                      | All allowed values of V <sub>DDIO</sub> and V <sub>DDD</sub> , see <i>Section 11.1</i> | -                       | _                                                                              | 5.5                     | V     |

| Vinref          | Input voltage reference (Differential input mode)          |                                                                                        | 0.5                     | -                                                                              | $0.52 \times V_{DDIO}$  | V     |

|                 | Output voltage reference (Regulat                          | ted output mode)                                                                       |                         |                                                                                |                         |       |

| Voutref         |                                                            | V <sub>DDIO</sub> > 3.7                                                                | 1                       | _                                                                              | V <sub>DDIO</sub> – 1   | V     |

|                 |                                                            | V <sub>DDIO</sub> < 3.7                                                                | 1                       | _                                                                              | V <sub>DDIO</sub> – 0.5 | V     |

|                 | Input voltage high threshold                               |                                                                                        |                         |                                                                                |                         |       |

| $V_{IH}$        | GPIO mode                                                  | CMOS input                                                                             | $0.7 \times V_{DDIO}$   | _                                                                              | _                       | V     |

|                 | Differential input mode <sup>[46]</sup>                    | Hysteresis disabled                                                                    | SIO_ref + 0.2           | _                                                                              | _                       | V     |

|                 | Input voltage low threshold                                |                                                                                        |                         |                                                                                |                         |       |

| $V_{IL}$        | GPIO mode                                                  | CMOS input                                                                             | _                       | _                                                                              | $0.3 \times V_{DDIO}$   | V     |

|                 | Differential input mode <sup>[46]</sup>                    | Hysteresis disabled                                                                    | _                       | _                                                                              | SIO_ref - 0.2           | V     |

|                 | Output voltage high                                        |                                                                                        | '                       |                                                                                |                         |       |

| V <sub>OH</sub> | Unregulated mode                                           | I <sub>OH</sub> = 4 mA, V <sub>DDIO</sub> = 3.3 V                                      | V <sub>DDIO</sub> – 0.4 | _                                                                              | _                       | V     |

| VOH             | Regulated mode <sup>[46]</sup>                             | I <sub>OH</sub> = 1 mA                                                                 | SIO_ref-0.65            | _                                                                              | SIO_ref + 0.2           | V     |

|                 | Regulated mode <sup>[46]</sup>                             | I <sub>OH</sub> = 0.1 mA                                                               | SIO_ref - 0.3           | _                                                                              | SIO_ref + 0.2           | V     |

|                 | Output voltage low                                         | $V_{DDIO} = 3.30 \text{ V}, I_{OL} = 25 \text{ mA}$                                    | _                       | _                                                                              | 0.8                     | V     |

| $V_{OL}$        |                                                            | $V_{\rm DDIO}$ = 3.30 V, $I_{\rm OL}$ = 20 mA                                          | _                       | _                                                                              | 0.4                     | V     |

|                 |                                                            | $V_{DDIO} = 1.80 \text{ V}, I_{OL} = 4 \text{ mA}$                                     | _                       | _                                                                              | 0.4                     | V     |

| Rpullup         | Pull-up resistor                                           |                                                                                        | 3.5                     | 5.6                                                                            | 8.5                     | kΩ    |

| Rpulldown       | Pull-down resistor                                         |                                                                                        | 3.5                     | 5.6                                                                            | 8.5                     | kΩ    |

| I <sub>IL</sub> | Input leakage current (absolute value) <sup>[47]</sup>     |                                                                                        | _                       | -                                                                              | _                       | _     |

|                 | V <sub>IH</sub> ≤ Vddsio                                   | 25 °C, Vddsio = 3.0 V, V <sub>IH</sub> = 3.0 V                                         | _                       | - V <sub>DDIO</sub> - 1 - V <sub>DDIO</sub> - 1 - V <sub>DDIO</sub> - 0.5  DIO | nA                      |       |

|                 | V <sub>IH</sub> > Vddsio                                   | 25 °C, Vddsio = 0 V, V <sub>IH</sub> = 3.0 V                                           | _                       | _                                                                              | 10                      | μA    |

| C <sub>IN</sub> | Input Capacitance <sup>[47]</sup>                          |                                                                                        | _                       | _                                                                              | 7                       | pF    |

|                 | Input voltage hysteresis (Schmitt-Trigger) <sup>[47]</sup> | Single ended mode (GPIO mode)                                                          | _                       | 40                                                                             | _                       | mV    |

| $V_{H}$         | (Schmitt-Trigger) <sup>[47]</sup>                          | Differential mode                                                                      | _                       | 35                                                                             | _                       | mV    |

| Idiode          | Current through protection diode to V <sub>SSIO</sub>      |                                                                                        | -                       | _                                                                              | 100                     | μΑ    |

Notes

46. See Figure 6-10 on page 39 and Figure 6-13 on page 43 for more information on SIO reference.

47. Based on device characterization (Not production tested)

Table 11-13. SIO Comparator Specifications<sup>[49]</sup>

| Parameter | Description                    | Conditions                | Min | Тур | Max | Units |

|-----------|--------------------------------|---------------------------|-----|-----|-----|-------|

| Vos       | Offset voltage                 | V <sub>DDIO</sub> = 2 V   | _   | _   | 68  | mV    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | _   | _   | 72  |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | _   | _   | 82  |       |

| TCVos     | Offset voltage drift with temp |                           | -   | _   | 250 | μV/°C |

| CMRR      | Common mode rejection ratio    | V <sub>DDIO</sub> = 2 V   | 30  | _   | -   | dB    |

|           |                                | V <sub>DDIO</sub> = 2.7 V | 35  | _   | -   |       |

|           |                                | V <sub>DDIO</sub> = 5.5 V | 40  | _   | -   |       |

| Tresp     | Response time                  |                           | _   | -   | 30  | ns    |

# 11.4.3 USBIO

For operation in GPIO mode, the standard range for  $V_{DDD}$  applies, see Device Level Specifications on page 72.

Table 11-14. USBIO DC Specifications

| Parameter                       | Description                            | Conditions                                         | Min            | Тур | Max            | Units |

|---------------------------------|----------------------------------------|----------------------------------------------------|----------------|-----|----------------|-------|

| Rusbi                           | USB D+ pull-up resistance              | With idle bus                                      | 0.900          | -   | 1.575          | kΩ    |

| Rusba                           | USB D+ pull-up resistance              | While receiving traffic                            | 1.425          | -   | 3.090          | kΩ    |

| Vohusb                          | Static output high                     | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | 2.8            | _   | 3.6            | V     |

| Volusb                          | Static output low                      | 15 k $\Omega$ ±5% to Vss, internal pull-up enabled | _              | _   | 0.3            | V     |

| Vihgpio                         | Input voltage high, GPIO mode          | V <sub>DDD</sub> ≥ 3 V                             | 2              | -   | _              | V     |

| Vilgpio                         | Input voltage low, GPIO mode           | $V_{DDD} \ge 3 \text{ V}$                          | _              | _   | 0.8            | V     |

| Vohgpio                         | Output voltage high, GPIO mode         | $I_{OH}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | 2.4            | _   | _              | V     |

| Volgpio                         | Output voltage low, GPIO mode          | $I_{OL}$ = 4 mA, $V_{DDD} \ge 3 \text{ V}$         | _              | _   | 0.3            | V     |

| Vdi                             | Differential input sensitivity         | (D+)-(D-)                                          | _              | -   | 0.2            | V     |

| Vcm                             | Differential input common mode range   | -                                                  | 0.8            | _   | 2.5            | V     |

| Vse                             | Single ended receiver threshold        | -                                                  | 0.8            | _   | 2              | V     |

| Rps2                            | PS/2 pull-up resistance                | In PS/2 mode, with PS/2 pull-up enabled            | 3              | _   | 7              | kΩ    |

| Rext                            | External USB series resistor           | In series with each USB pin                        | 21.78<br>(–1%) | 22  | 22.22<br>(+1%) | Ω     |

| Zo                              | USB driver output impedance            | Including Rext                                     | 28             | -   | 44             | Ω     |

| C <sub>IN</sub>                 | USB transceiver input capacitance      |                                                    | -              | _   | 20             | pF    |

| I <sub>IL</sub> <sup>[49]</sup> | Input leakage current (absolute value) | 25 °C, V <sub>DDD</sub> = 3.0 V                    | _              | _   | 2              | nA    |

#### Note

Document Number: 001-53413 Rev. \*Y Page 85 of 137

<sup>49.</sup> Based on device characterization (Not production tested).

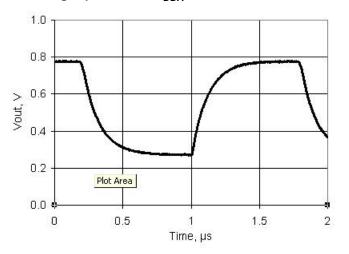

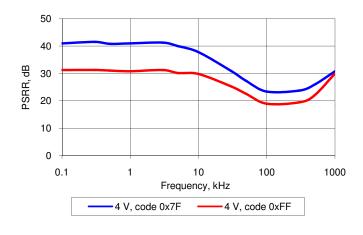

Table 11-31. VDAC AC Specifications

| Parameter        | Description                            | Conditions                                                      | Min | Тур  | Max  | Units     |

|------------------|----------------------------------------|-----------------------------------------------------------------|-----|------|------|-----------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                                                       | _   | _    | 1000 | ksps      |

|                  |                                        | 4 V scale                                                       | _   | _    | 250  | ksps      |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF                                        | _   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | _   | 0.8  | 3.2  | μs        |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF                                        | _   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                        | _   | 0.7  | 3    | μs        |

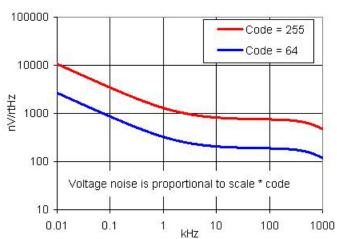

|                  | Voltage noise                          | Range = 1 V, High speed mode,<br>V <sub>DDA</sub> = 5 V, 10 kHz | _   | 750  | _    | nV/sqrtHz |

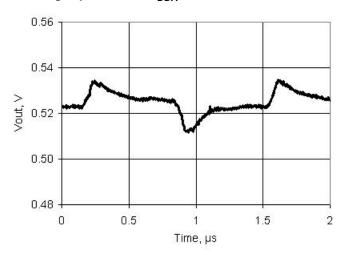

Figure 11-58. VDAC Step Response, Codes 0x40 - 0xC0, 1 V Mode, High speed mode,  $V_{DDA} = 5 \text{ V}$

Figure 11-60. VDAC PSRR vs Frequency

Figure 11-59. VDAC Glitch Response, Codes 0x7F - 0x80, 1 V Mode, High speed mode,  $V_{DDA} = 5 V$

Figure 11-61. VDAC Voltage Noise, 1 V Mode, High speed mode,  $V_{\text{DDA}}$  = 5 V

# 11.8 PSoC System Resources

Specifications are valid for  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$  and  $T_{J} \le 100~^{\circ}\text{C}$ , except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

# 11.8.1 POR with Brown Out

For brown out detect in regulated mode,  $V_{DDD}$  and  $V_{DDA}$  must be  $\geq 2.0$  V. Brown out detect is not available in externally regulated mode.

Table 11-65. Precise Low-Voltage Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | _   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | _   | 1.66 | V     |

# Table 11-66. Power On Reset (POR) with Brown Out AC Specifications

| Parameter | Description                                   | Conditions | Min | Тур | Max | Units |

|-----------|-----------------------------------------------|------------|-----|-----|-----|-------|

| PRES_TR   | Response time                                 |            | _   | _   | 0.5 | μs    |

|           | V <sub>DDD</sub> /V <sub>DDA</sub> droop rate | Sleep mode | -   | 5   | _   | V/sec |

# 11.8.2 Voltage Monitors

# Table 11-67. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Max  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            | -    | -    | -    | -     |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

# Table 11-68. Voltage Monitors AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------------|------------|-----|-----|-----|-------|

|           | Response time <sup>[74]</sup> |            | _   | _   | 1   | μs    |

#### Note

Document Number: 001-53413 Rev. \*Y Page 113 of 137

<sup>74.</sup> Based on device characterization (Not production tested).

# 11.9.2 Internal Low Speed Oscillator

# Table 11-75. ILO DC Specifications

| Parameter       |                                   | Conditions                 | Min | Тур | Max | Units |

|-----------------|-----------------------------------|----------------------------|-----|-----|-----|-------|

|                 | Operating current <sup>[82]</sup> | F <sub>OUT</sub> = 1 kHz   | _   | _   | 1.7 | μΑ    |

| I <sub>CC</sub> |                                   | F <sub>OUT</sub> = 33 kHz  | _   | _   | 2.6 | μA    |

|                 |                                   | F <sub>OUT</sub> = 100 kHz | _   | _   | 2.6 | μΑ    |

|                 | Leakage current <sup>[82]</sup>   | Power down mode            | _   | _   | 15  | nA    |

# Table 11-76. ILO AC Specifications

| Parameter        | Description                   | Conditions | Min | Тур | Max | Units |

|------------------|-------------------------------|------------|-----|-----|-----|-------|

|                  | Startup time, all frequencies | Turbo mode | -   | _   | 2   | ms    |

| F <sub>ILO</sub> | ILO frequencies               |            |     |     | 1   |       |

|                  | 100 kHz                       |            | 45  | 100 | 200 | kHz   |

|                  | 1 kHz                         |            | 0.5 | 1   | 2   | kHz   |

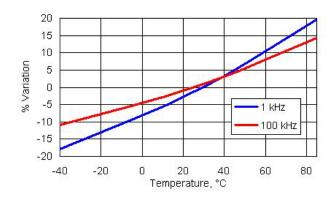

Figure 11-73. ILO Frequency Variation vs. Temperature

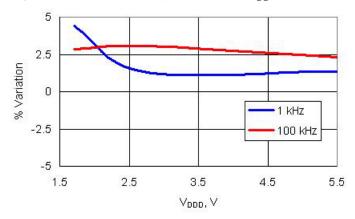

Figure 11-74. ILO Frequency Variation vs.  $V_{\rm DD}$

# 13. Packaging

Table 13-1. Package Characteristics

| Parameter      | Description                            | Conditions | Min | Тур   | Max | Units   |

|----------------|----------------------------------------|------------|-----|-------|-----|---------|

| T <sub>A</sub> | Operating ambient temperature          |            | -40 | 25.00 | 85  | °C      |

| T <sub>J</sub> | Operating junction temperature         |            | -40 | -     | 100 | °C      |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin SSOP)  |            | _   | 49    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (48-pin QFN)   |            | _   | 14    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (68-pin QFN)   |            | _   | 15    | -   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (100-pin TQFP) |            | _   | 34    | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (48-pin SSOP)  |            | _   | 24    | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (48-pin QFN)   |            | _   | 15    | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (68-pin QFN)   |            | _   | 13    | _   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (100-pin TQFP) |            | _   | 10    | _   | °C/Watt |

| $T_{JA}$       | Package θ <sub>JA</sub> (72-pin CSP)   |            | _   | 18    | -   | °C/Watt |

| $T_JC$         | Package θ <sub>JC</sub> (72-pin CSP)   |            | _   | 0.13  | _   | °C/Watt |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 48-pin QFN   | 260 °C                      | 30 seconds                          |

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

| 72-pin CSP   | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 48-pin QFN   | MSL 3 |

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 72-pin CSP   | MSL 1 |

Document Number: 001-53413 Rev. \*Y Page 122 of 137