#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                        |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 67MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                           |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 16x12b; D/A 4x8b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-QFN (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3666lti-050t |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase "subchains" can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

## 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty-two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

- Multiple I/O interrupt vectors

- Software can send interrupts

- Software can clear pending interrupts

When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address provided by the vector. After the ISR is completed, a RETI instruction is executed and returns execution to the instruction following the previously interrupted instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. Fixed function interrupts and all interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

Figure 4-2 on page 21 represents typical flow of events when an interrupt triggered. Figure 4-3 on page 22 shows the interrupt structure and priority polling.

#### Table 4-8. Interrupt Vector Table (continued)

| #  | Fixed Function    | DMA               | UDB          |

|----|-------------------|-------------------|--------------|

| 23 | USB Bus Int       | phub_termout1[7]  | udb_intr[23] |

| 24 | USB Endpoint[0]   | phub_termout1[8]  | udb_intr[24] |

| 25 | USB Endpoint Data | phub_termout1[9]  | udb_intr[25] |

| 26 | Reserved          | phub_termout1[10] | udb_intr[26] |

| 27 | LCD               | phub_termout1[11] | udb_intr[27] |

| 28 | DFB Int           | phub_termout1[12] | udb_intr[28] |

| 29 | Decimator Int     | phub_termout1[13] | udb_intr[29] |

| 30 | PHUB Error Int    | phub_termout1[14] | udb_intr[30] |

| 31 | EEPROM Fault Int  | phub_termout1[15] | udb_intr[31] |

# 5. Memory

#### 5.1 Static RAM

CY8C36 Static RAM (SRAM) is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 26. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

#### 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for ECC. If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

# 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices. The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a boot loader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security that permanently disables all test, programming, and debug ports, protecting your application from external access (see Device Security on page 68). For information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

#### Table 5-1. Flash Protection

| Protection<br>Setting | Allowed                                              | Not Allowed                                    |

|-----------------------|------------------------------------------------------|------------------------------------------------|

| Unprotected           | External read and write<br>+ internal read and write | -                                              |

| Factory Upgrade       | External write + internal read and write             | External read                                  |

| Field Upgrade         | Internal read and write                              | External read and write                        |

| Full Protection       | Internal read                                        | External read<br>and write +<br>internal write |

## Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# 6. System Integration

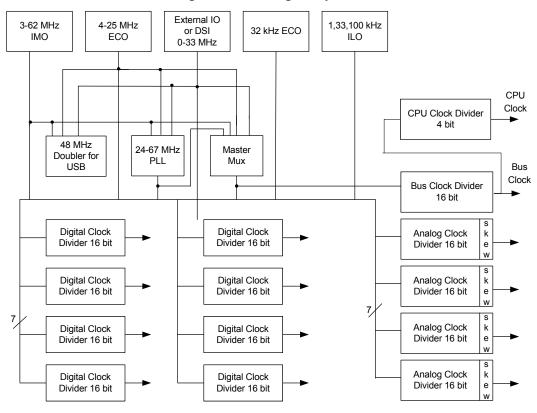

# 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 66 MHz clock, accurate to  $\pm 1\%$  over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC. Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 62-MHz IMO, ±1% at 3 MHz

- 4- to 25-MHz external crystal oscillator (MHzECO)

- Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 30.

- DSI signal from an external I/O pin or other logic

- 24- to 67-MHz fractional PLL sourced from IMO, MHzECO, or DSI

- 1-kHz, 33-kHz, 100-kHz ILO for WDT and sleep timer

32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB. (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

Figure 6-1. Clocking Subsystem

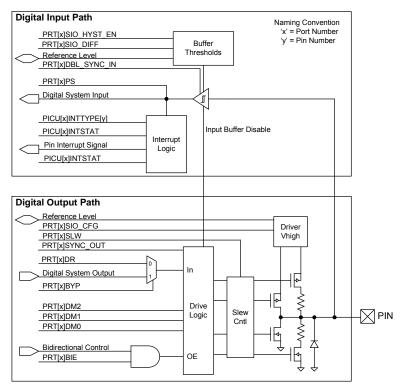

# 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[17]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- □ User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- □ LCD segment drive on LCD equipped devices □ CapSense<sup>[17]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- □ Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- B Higher drive strength than GPIO

- Hot swap capability (5 V tolerance at any operating V<sub>DD</sub>)

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- □ Over voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

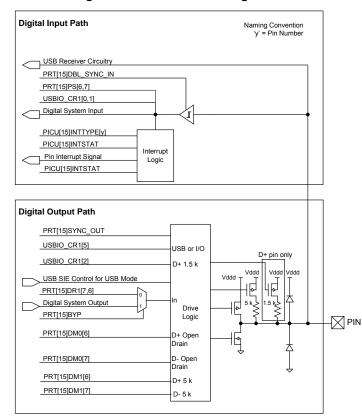

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- Input, output, or both for CPU and DMA

- Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

#### Figure 6-10. SIO Input/Output Block Diagram

Figure 6-11. USBIO Block Diagram

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-4 shows the drive mode configuration for the USBIO pins.

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

# Table 6-4. USBIO Drive Modes (P15[7] and P15[6])

#### High Impedance Analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

High Impedance Digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

#### Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

Open Drain, Drives High and Open Drain, Drives Low

Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the  $I^2C$  bus signal lines.

Strong Drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

■ Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

# 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

#### 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRT×DM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

#### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRT×SLW registers.

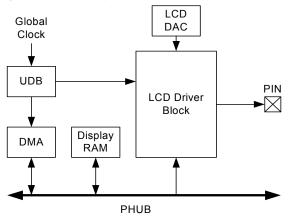

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

Key features of the PSoC LCD segment system are:

- LCD panel direct driving

- Type A (standard) and Type B (low-power) waveform support

- Wide operating voltage range support (2 V to 5 V) for LCD panels

- Static, 1/2, 1/3, 1/4, 1/5 bias voltage levels

- Internal bias voltage generation through internal resistor ladder

- Up to 62 total common and segment outputs

- Up to 1/16 multiplex for a maximum of 16 backplane/common outputs

- Up to 62 front plane/segment outputs for direct drive

- Drives up to 736 total segments (16 backplane × 46 front plane)

- Up to 64 levels of software controlled contrast

- Ability to move display data from memory buffer to LCD driver through DMA (without CPU intervention)

- Adjustable LCD refresh rate from 10 Hz to 150 Hz

- Ability to invert LCD display for negative image

- Three LCD driver drive modes, allowing power optimization

#### Figure 8-10. LCD System

# 8.6.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.6.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers through DMA.

#### 8.6.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

#### 8.6.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

#### 8.7 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, and proximity detection. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator. A capacitive sensing method using a Delta-Sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

#### 8.8 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

# 9.1 JTAG Interface

The IEEE 1149.1 compliant JTAG interface exists on four or five pins (the nTRST pin is optional). The JTAG interface is used for programming the flash memory, debugging, I/O scan chains, and JTAG device chaining.

PSoC 3 has certain timing requirements to be met for entering programming mode through the JTAG interface. Due to these timing requirements, not all standard JTAG programmers, or standard JTAG file formats such as SVF or STAPL, can support

PSoC 3 programming. The list of programmers that support PSoC 3 programming is available at http://www.cypress.com/go/programming.

The JTAG clock frequency can be up to 14 MHz, or 1/3 of the CPU clock frequency for 8 and 16-bit transfers, or 1/5 of the CPU clock frequency for 32-bit transfers. By default, the JTAG pins are enabled on new devices but the JTAG interface can be disabled, allowing these pins to be used as GPIO instead.

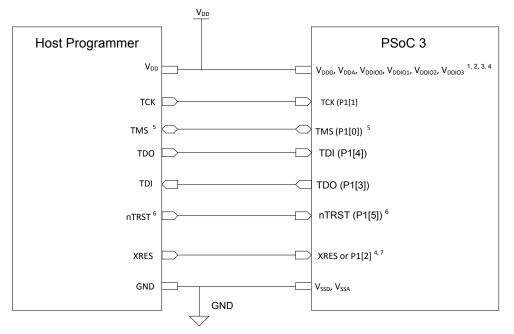

#### Figure 9-1. JTAG Interface Connections between PSoC 3 and Programmer

The voltage levels of Host Programmer and the PSoC 3 voltage domains involved in Programming should be same. The Port 1 JTAG pins, XRES pin (XRES\_N or P1[2]) are powered by V<sub>DDI01</sub>. So, V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 3, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

<sup>5</sup> By default, PSoC 3 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 3 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controller during first time programming of PSoC 3 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

If XRES pin is used by host, P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48-pin devices, but use dedicated XRES pin for rest of devices.

| Table 11-7. Recommended External Components for Boost Circuit |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| Parameter          | Description                                                                                      | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                                                   | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                                                  | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                                                  | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μH    |

| C <sub>BOOST</sub> | Total capacitance sum of V <sub>DDD</sub> , V <sub>DDA</sub> , V <sub>DDIO</sub> <sup>[41]</sup> |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                                         |                | 17.0 | 22.0 | 27.0 | μF    |

| l <sub>F</sub>     | Schottky diode average forward current                                                           |                | 1.0  | -    | -    | A     |

| V <sub>R</sub>     | Schottky reverse voltage                                                                         |                | 20.0 | _    | -    | V     |

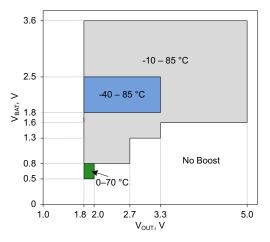

# Figure 11-8. T<sub>A</sub> range over $V_{BAT}$ and $V_{OUT}$

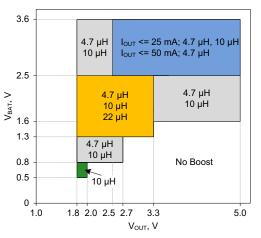

Figure 11-10. L\_{BOOST} values over  $V_{BAT}$  and  $V_{OUT}$

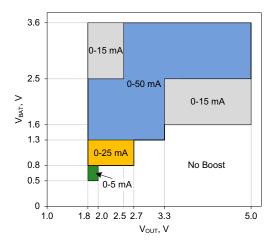

# Figure 11-9. $I_{OUT}$ range over $V_{BAT}$ and $V_{OUT}$

Note

41. Based on device characterization (Not production tested).

# Table 11-22. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | -   | -   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[55]</sup>                         | Buffer gain = 1, 12-bit,<br>Range = ±1.024 V | _   | -   | 0.0032 | %       |

| 12-Bit Reso  | lution Mode                                                       |                                              |     |     |        |         |

| SR12         | Sample rate, continuous, high power <sup>[55]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | _   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[55]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 44  | _      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[55]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | _      | dB      |

| 8-Bit Resolu | ution Mode                                                        |                                              |     |     |        |         |

| SR8          | Sample rate, continuous, high power <sup>[55]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | -   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[55]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 88  | -      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[55]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | _   | _      | dB      |

# Table 11-23. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, | Continuous |        | Multi-Sample |       |  |

|-------------|------------|--------|--------------|-------|--|

| Bits        | Min        | Max    | Min          | Max   |  |

| 8           | 8000       | 384000 | 1911         | 91701 |  |

| 9           | 6400       | 307200 | 1543         | 74024 |  |

| 10          | 5566       | 267130 | 1348         | 64673 |  |

| 11          | 4741       | 227555 | 1154         | 55351 |  |

| 12          | 4000       | 192000 | 978          | 46900 |  |

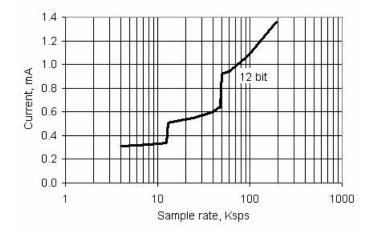

# Figure 11-33. Delta-sigma ADC IDD vs sps, Range = $\pm$ 1.024 V, Continuous Sample Mode, Input Buffer Bypassed

Note 55. Based on device characterization (Not production tested).

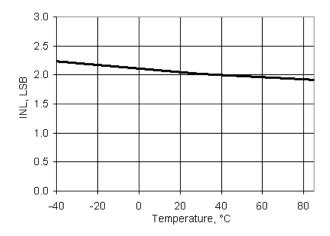

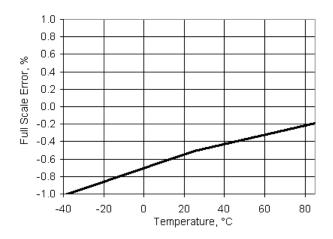

Figure 11-52. VDAC INL vs Temperature, 1 V Mode

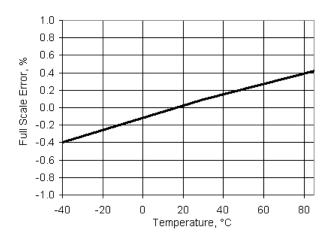

Figure 11-54. VDAC Full Scale Error vs Temperature, 1 V Mode

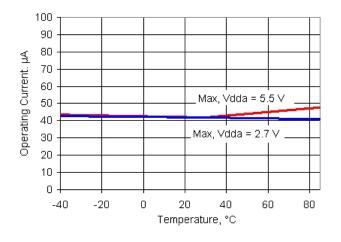

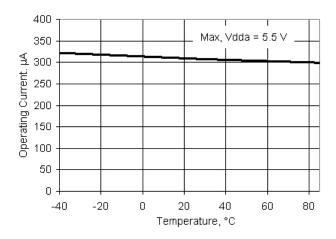

Figure 11-56. VDAC Operating Current vs Temperature, 1V Mode, Low speed mode

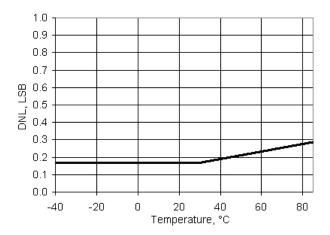

Figure 11-53. VDAC DNL vs Temperature, 1 V Mode

Figure 11-55. VDAC Full Scale Error vs Temperature, 4 V Mode

Figure 11-57. VDAC Operating Current vs Temperature, 1 V Mode, High speed mode

# 11.5.8 Mixer

The mixer is created using a SC/CT analog block; see the Mixer component data sheet in PSoC Creator for full electrical specifications and APIs.

# Table 11-32. Mixer DC Specifications

| Parameter       | Description          | Conditions | Min | Тур | Max | Units |

|-----------------|----------------------|------------|-----|-----|-----|-------|

| V <sub>OS</sub> | Input offset voltage |            | -   | -   | 15  | mV    |

|                 | Quiescent current    |            | -   | 0.9 | 2   | mA    |

| G               | Gain                 |            | _   | 0   | -   | dB    |

#### Table 11-33. Mixer AC Specifications<sup>[63]</sup>

| Parameter       | Description                | Conditions      | Min | Тур | Max | Units |

|-----------------|----------------------------|-----------------|-----|-----|-----|-------|

| f <sub>LO</sub> | Local oscillator frequency | Down mixer mode | -   | -   | 4   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Down mixer mode | -   | -   | 14  | MHz   |

| f <sub>LO</sub> | Local oscillator frequency | Up mixer mode   | -   | -   | 1   | MHz   |

| f <sub>in</sub> | Input signal frequency     | Up mixer mode   | -   | -   | 1   | MHz   |

| SR              | Slew rate                  |                 | 3   | _   | _   | V/µs  |

#### 11.5.9 Transimpedance Amplifier

The TIA is created using a SC/CT analog block; see the TIA component data sheet in PSoC Creator for full electrical specifications and APIs.

#### Table 11-34. Transimpedance Amplifier (TIA) DC Specifications

| Parameter         | Description                           | Conditions           | Min | Тур | Max | Units |

|-------------------|---------------------------------------|----------------------|-----|-----|-----|-------|

| V <sub>IOFF</sub> | Input offset voltage                  |                      | -   | -   | 10  | mV    |

| Rconv             | Conversion resistance <sup>[64]</sup> | R = 20K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 30K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 40K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 80K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 120K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R = 250K; 40 pF load | -25 | -   | +35 | %     |

|                   |                                       | R= 500K; 40 pF load  | -25 | -   | +35 | %     |

|                   |                                       | R = 1M; 40 pF load   | -25 | -   | +35 | %     |

|                   | Quiescent current                     |                      | _   | 1.1 | 2   | mA    |

#### Table 11-35. Transimpedance Amplifier (TIA) AC Specifications

| Parameter | Description             | Conditions           | Min  | Тур | Max | Units |

|-----------|-------------------------|----------------------|------|-----|-----|-------|

| BW        | Input bandwidth (-3 dB) | R = 20K; –40 pF load | 1500 | -   | -   | kHz   |

|           |                         | R = 120K;40 pF load  | 240  | _   | _   | kHz   |

|           |                         | R = 1M; –40 pF load  | 25   | -   | -   | kHz   |

Notes

<sup>63.</sup> Based on device characterization (Not production tested).

<sup>64.</sup> Conversion resistance values are not calibrated. Calibrated values and details about calibration are provided in PSoC Creator component data sheets. External precision resistors can also be used.

# 11.5.10 Programmable Gain Amplifier

The PGA is created using a SC/CT analog block; see the PGA component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, operating conditions are:

- Operating temperature = 25 °C for typical values

- Unless otherwise specified, all charts and graphs show typical values

# Table 11-36. PGA DC Specifications

| Parameter | Description                                 | Conditions                                                                        | Min                    | Тур | Max                     | Units       |

|-----------|---------------------------------------------|-----------------------------------------------------------------------------------|------------------------|-----|-------------------------|-------------|

| Vin       | Input voltage range                         | Power mode = minimum                                                              | V <sub>SSA</sub>       | _   | V <sub>DDA</sub>        | V           |

| Vos       | Input offset voltage                        | Power mode = high,<br>gain = 1                                                    | -                      | -   | 10                      | mV          |

| TCVos     | Input offset voltage drift with temperature | Power mode = high,<br>gain = 1                                                    | -                      | -   | ±30                     | µV/°C       |

| Ge1       | Gain error, gain = 1                        |                                                                                   | _                      | -   | ±0.15                   | %           |

| Ge16      | Gain error, gain = 16                       |                                                                                   | -                      | _   | ±2.5                    | %           |

| Ge50      | Gain error, gain = 50                       |                                                                                   | -                      | _   | ±5                      | %           |

| Vonl      | DC output nonlinearity                      | Gain = 1                                                                          | -                      | -   | ±0.01                   | % of<br>FSR |

| Cin       | Input capacitance                           |                                                                                   | -                      | _   | 7                       | pF          |

| Voh       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | V <sub>DDA</sub> -0.15 | -   | _                       | V           |

| Vol       | Output voltage swing                        | Power mode = high,<br>gain = 1, Rload = 100 k $\Omega$<br>to V <sub>DDA</sub> / 2 | -                      | -   | V <sub>SSA</sub> + 0.15 | V           |

| Vsrc      | Output voltage under load                   | lload = 250 µA, $V_{DDA} ≥$ 2.7 V, power mode = high                              | -                      | -   | 300                     | mV          |

| ldd       | Operating current                           | Power mode = high                                                                 | _                      | 1.5 | 1.65                    | mA          |

| PSRR      | Power supply rejection ratio                |                                                                                   | 48                     | -   | _                       | dB          |

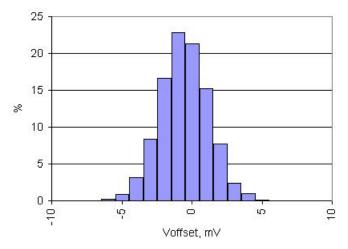

Figure 11-62. PGA Voffset Histogram, 4096 samples/ 1024 parts

# 11.6.3 Pulse Width Modulation

The following specifications apply to the Timer/Counter/PWM peripheral, in PWM mode. PWM components can also be implemented in UDBs; for more information, see the PWM component data sheet in PSoC Creator.

# Table 11-45. PWM DC Specifications

| Parameter | Description               | Conditions                                  | Min | Тур | Max | Units |

|-----------|---------------------------|---------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit PWM, at listed input clock frequency | -   | _   | -   | μA    |

|           | 3 MHz                     |                                             | -   | 15  | -   | μA    |

|           | 12 MHz                    |                                             | -   | 60  | -   | μA    |

|           | 48 MHz                    |                                             | _   | 260 | -   | μA    |

|           | 67 MHz                    |                                             | _   | 350 | _   | μA    |

# Table 11-46. Pulse Width Modulation (PWM) AC Specifications

| Parameter | Description                   | Conditions | Min | Тур | Max   | Units |

|-----------|-------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency           |            | DC  | -   | 67.01 | MHz   |

|           | Pulse width                   |            | 15  | -   | -     | ns    |

|           | Pulse width (external)        |            | 30  | _   | _     | ns    |

|           | Kill pulse width              |            | 15  | -   | -     | ns    |

|           | Kill pulse width (external)   |            | 30  | -   | -     | ns    |

|           | Enable pulse width            |            | 15  | -   | -     | ns    |

|           | Enable pulse width (external) |            | 30  | -   | -     | ns    |

|           | Reset pulse width             |            | 15  | _   | -     | ns    |

|           | Reset pulse width (external)  |            | 30  | -   | -     | ns    |

# 11.6.4 P<sup>2</sup>C

# Table 11-47. Fixed I<sup>2</sup>C DC Specifications

| Parameter | Description               | Conditions                       | Min | Тур | Max | Units |

|-----------|---------------------------|----------------------------------|-----|-----|-----|-------|

|           | Block current consumption | Enabled, configured for 100 kbps | _   | -   | 250 | μA    |

|           |                           | Enabled, configured for 400 kbps | _   | -   | 260 | μA    |

|           |                           | Wake from sleep mode             | _   | _   | 30  | μA    |

# Table 11-48. Fixed I<sup>2</sup>C AC Specifications

| Parameter | Description | Conditions | Min | Тур | Max | Units |

|-----------|-------------|------------|-----|-----|-----|-------|

|           | Bit rate    |            | -   | -   | 1   | Mbps  |

11.6.5 Controller Area Network

# Table 11-49. CAN DC Specifications<sup>[65]</sup>

| Parameter       | Description               | Conditions | Min | Тур | Max | Units |

|-----------------|---------------------------|------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Block current consumption |            | _   | -   | 200 | μA    |

# Table 11-50. CAN AC Specifications<sup>[65]</sup>

| Parameter | Description | Conditions          | Min | Тур | Max | Units |

|-----------|-------------|---------------------|-----|-----|-----|-------|

|           | Bit rate    | Minimum 8 MHz clock | _   | _   | 1   | Mbit  |

Note

65. Refer to ISO 11898 specification for details.

# 11.7 Memory

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.7.1 Flash

# Table 11-55. Flash DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | -   | 5.5 | V     |

# Table 11-56. Flash AC Specifications

| Parameter          | Description                                                                | Conditions                                                        | Min | Тур | Max | Units   |

|--------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|---------|

| T <sub>WRITE</sub> | Row write time (erase + program)                                           |                                                                   | _   | 15  | 20  | ms      |

| T <sub>ERASE</sub> | Row erase time                                                             |                                                                   | -   | 10  | 13  | ms      |

|                    | Row program time                                                           |                                                                   | -   | 5   | 7   | ms      |

| T <sub>BULK</sub>  | Bulk erase time (16 KB to 64 KB)                                           |                                                                   | -   | -   | 35  | ms      |

|                    | Sector erase time (8 KB to 16 KB)                                          |                                                                   | _   | _   | 15  | ms      |

| T <sub>PROG</sub>  | Total device programming time                                              | No overhead <sup>[67]</sup>                                       | -   | 1.5 | 2   | seconds |

|                    | Flash data retention time, retention period measured from last erase cycle | Average ambient temp. $T_A \le 55$ °C, 100 K erase/program cycles | 20  | -   | -   | years   |

|                    |                                                                            | Average ambient temp. $T_A \le 85$ °C, 10 K erase/program cycles  | 10  | -   | -   |         |

# 11.7.2 EEPROM

#### Table 11-57. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Max | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | -   | 5.5 | V     |

# Table 11-58. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                                      | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                                 | -   | 10  | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, $T_A \le 25 \degree C$ , 1M erase/program cycles          | 20  | -   | -   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C,<br>100 K erase/program cycles     | 20  | -   | -   |       |

|                    |                                                                             | Average ambient temp.<br>T <sub>A</sub> $\leq$ 85 °C, 10 K erase/program cycles | 10  | _   | -   |       |

# 11.9.3 MHz External Crystal Oscillator

For more information on crystal or ceramic resonator selection for the MHzECO, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators.

# Table 11-77. MHzECO DC Specifications

| Parameter       |                                   | Conditions        | Min | Тур | Max | Units |

|-----------------|-----------------------------------|-------------------|-----|-----|-----|-------|

| I <sub>CC</sub> | Operating current <sup>[83]</sup> | 13.56 MHz crystal | -   | 3.8 | _   | mA    |

#### Table 11-78. MHzECO AC Specifications

| Parameter | Description             | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------|------------|-----|-----|-----|-------|

| F         | Crystal frequency range |            | 4   | -   | 25  | MHz   |

#### 11.9.4 kHz External Crystal Oscillator

# Table 11-79. kHzECO DC Specifications<sup>[83]</sup>

| Parameter       | Description Conditions N |                          | Min | Тур  | Max | Units |

|-----------------|--------------------------|--------------------------|-----|------|-----|-------|

| I <sub>CC</sub> | Operating current        | Low-power mode; CL= 6 pF | _   | 0.25 | 1.0 | μA    |

| DL              | Drive level              |                          | -   | _    | 1   | μW    |

#### Table 11-80. kHzECO AC Specifications

| Parameter       | Description  | Conditions      | Min | Тур    | Max | Units |

|-----------------|--------------|-----------------|-----|--------|-----|-------|

| F               | Frequency    |                 | _   | 32.768 | _   | kHz   |

| T <sub>ON</sub> | Startup time | High power mode | Ι   | 1      | -   | S     |

# 11.9.5 External Clock Reference

# Table 11-81. External Clock Reference AC Specifications<sup>[83]</sup>

| Parameter | Description              | Conditions                       | Min | Тур | Max | Units |

|-----------|--------------------------|----------------------------------|-----|-----|-----|-------|

|           | External frequency range |                                  | 0   | -   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2 | 30  | 50  | 70  | %     |

|           | Input edge rate          | $V_{IL}$ to $V_{IH}$             | 0.5 | _   | -   | V/ns  |

#### 11.9.6 Phase-Locked Loop

# Table 11-82. PLL DC Specifications

| Parameter       | Description           | Conditions               | Min | Тур | Max | Units |

|-----------------|-----------------------|--------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | PLL operating current | In = 3 MHz, Out = 67 MHz | _   | 400 | _   | μA    |

|                 |                       | In = 3 MHz, Out = 24 MHz | _   | 200 | _   | μA    |

#### Table 11-83. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Max | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[84]</sup>        |                     | 1   | _   | 48  | MHz   |

|             | PLL intermediate frequency <sup>[85]</sup> | Output of prescaler | 1   | -   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[84]</sup>       |                     | 24  | -   | 67  | MHz   |

|             | Lock time at startup                       |                     | -   | -   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[83]</sup>               |                     | -   | -   | 250 | ps    |

Notes

<sup>83.</sup> Based on device characterization (Not production tested).

<sup>84.</sup> This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL.

<sup>85.</sup> PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16.

| Acronym | Description                                                  |  |  |  |  |

|---------|--------------------------------------------------------------|--|--|--|--|

| PHUB    | peripheral hub                                               |  |  |  |  |

| PHY     | physical layer                                               |  |  |  |  |

| PICU    | port interrupt control unit                                  |  |  |  |  |

| PLA     | rogrammable logic array                                      |  |  |  |  |

| PLD     | programmable logic device, see also PAL                      |  |  |  |  |

| PLL     | phase-locked loop                                            |  |  |  |  |

| PMDD    | package material declaration data sheet                      |  |  |  |  |

| POR     | power-on reset                                               |  |  |  |  |

| PRES    | precise low-voltage reset                                    |  |  |  |  |

| PRS     | pseudo random sequence                                       |  |  |  |  |

| PS      | port read data register                                      |  |  |  |  |

| PSoC®   | Programmable System-on-Chip™                                 |  |  |  |  |

| PSRR    | power supply rejection ratio                                 |  |  |  |  |

| PWM     | pulse-width modulator                                        |  |  |  |  |

| RAM     | random-access memory                                         |  |  |  |  |

| RISC    | reduced-instruction-set computing                            |  |  |  |  |

| RMS     | root-mean-square                                             |  |  |  |  |

| RTC     | real-time clock                                              |  |  |  |  |

| RTL     | register transfer language                                   |  |  |  |  |

| RTR     | remote transmission request                                  |  |  |  |  |

| RX      | receive                                                      |  |  |  |  |

| SAR     | successive approximation register                            |  |  |  |  |

| SC/CT   | switched capacitor/continuous time                           |  |  |  |  |

| SCL     | I <sup>2</sup> C serial clock                                |  |  |  |  |

| SDA     | I <sup>2</sup> C serial data                                 |  |  |  |  |

| S/H     | sample and hold                                              |  |  |  |  |

| SINAD   | signal to noise and distortion ratio                         |  |  |  |  |

| SIO     | special input/output, GPIO with advanced features. See GPIO. |  |  |  |  |

| SOC     | start of conversion                                          |  |  |  |  |

# Table 14-1. Acronyms Used in this Document (continued)

# Table 14-1. Acronyms Used in this Document (continued)

| Acronym | Description                                                               |

|---------|---------------------------------------------------------------------------|

| SOF     | start of frame                                                            |

| SPI     | Serial Peripheral Interface, a communications protocol                    |

| SR      | slew rate                                                                 |

| SRAM    | static random access memory                                               |

| SRES    | software reset                                                            |

| SWD     | serial wire debug, a test protocol                                        |

| SWV     | single-wire viewer                                                        |

| TD      | transaction descriptor, see also DMA                                      |

| THD     | total harmonic distortion                                                 |

| TIA     | transimpedance amplifier                                                  |

| TRM     | technical reference manual                                                |

| TTL     | transistor-transistor logic                                               |

| ТХ      | transmit                                                                  |

| UART    | Universal Asynchronous Transmitter Receiver, a<br>communications protocol |

| UDB     | universal digital block                                                   |

| USB     | Universal Serial Bus                                                      |

| USBIO   | USB input/output, PSoC pins used to connect to a USB port                 |

| VDAC    | voltage DAC, see also DAC, IDAC                                           |

| WDT     | watchdog timer                                                            |

| WOL     | write once latch, see also NVL                                            |

| WRES    | watchdog timer reset                                                      |

| XRES    | external reset I/O pin                                                    |

| XTAL    | crystal                                                                   |

# **15. Reference Documents**

PSoC® 3, PSoC® 5 Architecture TRM PSoC® 3 Registers TRM

# 17. Revision History

|          | t Number: |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | ECN       | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| **       | 2714854   | 06/04/09           | PVKV               | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| *A       | 2758970   | 09/02/09           | MKEA               | Updated Part Numbering Conventions<br>Added Section 11.7.5 (EMIF Figures and Tables)<br>Updated GPIO and SIO AC specifications<br>Updated XRES Pin Description and Xdata Address Map specifications<br>Updated DFB and Comparator specifications<br>Updated PHUB features section and RTC in sleep mode<br>Updated IDAC and VDAC DC and Analog Global specifications<br>Updated USBIO AC and Delta Sigma ADC specifications<br>Updated PPOR and Voltage Monitors DC specifications<br>Updated Drive Mode diagram<br>Added 48-QFN Information<br>Updated other electrical specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *В       | 2824546   | 12/09/09           | MKEA               | Updated I2C section to reflect 1 Mbps. Updated Table 11-6 and 11-7 (Boost AC<br>and DC specs); also added Shottky Diode specs. Changed current for<br>sleep/hibernate mode to include SIO; Added footnote to analog global specs.<br>Updated Figures 1-1, 6-2, 7-14, and 8-1. Updated Table 6-2 and Table 6-3<br>(Hibernate and Sleep rows) and Power Modes section. Updated GPIO and SIC<br>AC specifications. Updated Gain error in IDAC and VDAC specifications.<br>Updated description of V <sub>DDA</sub> spec in Table 11-1 and removed GPIO Clamp<br>Current parameter. Updated number of UDBs on page 1.<br>Moved FILO from ILO DC to AC table.<br>Added PCB Layout and PCB Schematic diagrams.<br>Updated Fgpioout spec (Table 11-9). Added duty cycle frequency in PLL AC spec<br>table. Added note for Sleep and Hibernate modes and Active Mode specs in Table<br>11-2. Linked URL in Section 10.3 to PSoC Creator site.<br>Updated Ja and Jc values in Table 13-1. Updated Single Sample Mode and Fas<br>FIR Mode sections. Updated Input Resistance specification in Del-Sig ADC table<br>Added Tio_init parameter. Updated PGA and UGB AC Specs. Removed SPC<br>ADC. Updated Boost Converter section.<br>Added section 'SIO as Comparator'; updated Hysteresis spec (differential mode<br>in Table 11-10.<br>Updated V <sub>BAT</sub> condition and deleted Vstart parameter in Table 11-6.<br>Added 'Bytes' column for Tables 4-1 to 4-5. |

| *C       | 2873322   | 02/04/10           | MKEA               | Changed maximum value of PPOR_TR to '1'. Updated V <sub>BIAS</sub> specification.<br>Updated PCB Schematic. Updated Figure 8-1 and Figure 6-3. Updated Interrup<br>Vector table, Updated Sales links. Updated JTAG and SWD specifications.<br>Removed Jp-p and Jperiod from ECO AC Spec table. Added note on sleep time<br>in Table 11-2. Updated ILO AC and DC specifications. Added Resolution<br>parameter in VDAC and IDAC tables. Updated I <sub>OUT</sub> typical and maximum values<br>Changed Temperature Sensor range to -40 °C to +85 °C. Removed Latchup<br>specification from Table 11-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Description Documen | on Title: PS<br>t Number: ( | oC <sup>®</sup> 3: CY8C3<br>001-53413 | 6 Family Da        | tasheet Programmable System-on-Chip (PSoC <sup>®</sup> ) (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|-----------------------------|---------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision            | ECN                         | Submission<br>Date                    | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |