Welcome to **E-XFL.COM**

**Embedded - System On Chip (SoC):** The Heart of Modern Embedded Systems

Embedded - System On Chip (SoC) refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

What are **Embedded - System On Chip (SoC)?**

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Active                                                                      |

| Architecture            | MCU, FPGA                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                             |

| Flash Size              | 256KB                                                                       |

| RAM Size                | 64KB                                                                        |

| Peripherals             | DMA, POR, WDT                                                               |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                        |

| Speed                   | 100MHz                                                                      |

| Primary Attributes      | ProASIC®3 FPGA, 200K Gates, 4608 D-Flip-Flops                               |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                             |

| Package / Case          | 256-LBGA                                                                    |

| Supplier Device Package | 256-FPBGA (17x17)                                                           |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f200m3f-1fgg256 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **SmartFusion cSoC Family Product Table**

|                                    | A2F060 |        |                  | A2F200 |           |          | A2F500 |       |         |           |          |

|------------------------------------|--------|--------|------------------|--------|-----------|----------|--------|-------|---------|-----------|----------|

| FPGA Fabric                        | TQ144  | CS288  | FG256            | PQ208  | CS288     | FG256    | FG484  | PQ208 | CS288   | FG256     | FG484    |

| System Gates                       | 60,000 |        |                  |        | 200       | ,000     |        |       | 500,000 |           |          |

| Tiles (D-flip-flops)               |        | 1,536  |                  |        | 4,6       | 808      |        |       | 11,     | 520       |          |

| RAM Blocks (4,608 bits)            |        | 8      |                  |        | 3         | 3        |        |       | 2       | 4         |          |

|                                    |        | A2F060 |                  |        | A2F       | 200      |        |       | A2F     | 500       |          |

| Microcontroller Subsystem (MSS)    | TQ144  | CS288  | FG256            | PQ208  | CS288     | FG256    | FG484  | PQ208 | CS288   | FG256     | FG484    |

| Flash (Kbytes)                     |        | 128    |                  |        | 25        | 56       |        |       | 5′      | 12        |          |

| SRAM (Kbytes)                      |        | 16     |                  |        | 6         | 4        |        |       | 6       | 4         |          |

| Cortex-M3 processor with MPU       |        | Yes    |                  |        | Ye        | es       |        |       | Ye      | es        |          |

| 10/100 Ethernet MAC                |        | No     |                  |        | Ye        | es       |        |       | Ye      | es        |          |

| External Memory Controller (EMC)   | -      |        | 6-bit<br>ss/data | 26-b   | it addres | s,16-bit | data   | -     | 26-/16- | bit addre | ess/data |

| DMA                                |        | 8 Ch   |                  | 8 Ch   |           |          |        | 8 Ch  |         |           |          |

| l <sup>2</sup> C                   |        | 2      |                  | 2      |           |          | 2      |       |         |           |          |

| SPI                                | 1      | 2      | 2                | 1 2    |           |          | 1 2    |       |         |           |          |

| 16550 UART                         |        | 2      |                  | 2      |           | 2        |        |       |         |           |          |

| 32-Bit Timer                       |        | 2      |                  | 2      |           | 2        |        |       |         |           |          |

| PLL                                |        | 1      |                  | 1      |           | 1        | 2      | 1     | 2       |           |          |

| 32 KHz Low Power Oscillator        |        | 1      |                  | 1      |           | 1        |        |       |         |           |          |

| 100 MHz On-Chip RC Oscillator      |        | 1      |                  | 1      |           |          | 1      |       |         |           |          |

| Main Oscillator (32 KHz to 20 MHz) |        | 1      |                  |        | •         |          |        |       | •       | 1         |          |

|                                    |        | A2F060 |                  |        | A2F       | 200      |        |       | A2F     | 500       |          |

| Programmable Analog                | TQ144  | CS288  | FG256            | PQ208  | CS288     | FG256    | FG484  | PQ208 | CS288   | FG256     | FG484    |

| ADCs (8-/10-/12-bit SAR)           |        | 1      |                  |        | 2         | 2        |        |       | 2       |           | 3        |

| DACs (8-/16-/24-bit sigma-delta)   |        | 1      |                  |        | 2         | 2        |        |       | 2       |           | 3        |

| Signal Conditioning Blocks (SCBs)  | 1      |        |                  | 4      |           |          |        | 4     |         |           | 5        |

| Comparator*                        | 2      |        |                  | 8      |           |          | 8      |       |         | 10        |          |

| Current Monitors*                  |        | 1      |                  | 4      |           |          | 4      |       |         | 5         |          |

| Temperature Monitors*              |        | 1      |                  | 4      |           |          | 4      |       |         | 5         |          |

| Bipolar High Voltage Monitors*     |        | 2      |                  |        | 8         | 3        |        | 8     |         |           | 10       |

Note: \*These functions share I/O pins and may not all be available at the same time. See the "Analog Front-End Overview" section in the http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130925 for details.

II Revision 13

Table 2-3 • Recommended Operating Conditions<sup>5,6</sup>

| Symbol                   | Paramete                             | er <sup>1</sup>               | Commercial     | Industrial     | Units |

|--------------------------|--------------------------------------|-------------------------------|----------------|----------------|-------|

| $T_J$                    | Junction temperature                 | 0 to +85                      | -40 to +100    | °C             |       |

| VCC <sup>2</sup>         | 1.5 V DC core supply voltage         | 1.425 to 1.575                | 1.425 to 1.575 | V              |       |

| VJTAG                    | JTAG DC voltage                      |                               | 1.425 to 3.6   | 1.425 to 3.6   | V     |

| VPP                      | Programming voltage                  | Programming mode <sup>3</sup> | 3.15 to 3.45   | 3.15 to 3.45   | V     |

|                          |                                      | Operation <sup>4</sup>        | 0 to 3.6       | 0 to 3.6       | V     |

| VCCPLLx                  | Analog power supply (PLL)            |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCFPGAIOBx/             | 1.5 V DC supply voltage              |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCMSSIOBx <sup>5</sup>  | 1.8 V DC supply voltage              |                               | 1.7 to 1.9     | 1.7 to 1.9     | V     |

|                          | 2.5 V DC supply voltage              |                               | 2.3 to 2.7     | 2.3 to 2.7     | V     |

|                          | 3.3 V DC supply voltage              | 3.0 to 3.6                    | 3.0 to 3.6     | V              |       |

|                          | LVDS differential I/O                | 2.375 to 2.625                | 2.375 to 2.625 | V              |       |

|                          | LVPECL differential I/O              |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

| VCC33A <sup>6</sup>      | Analog clean 3.3 V supply to t       | the analog circuitry          | 3.15 to 3.45   | 3.15 to 3.45   | V     |

| VCC33ADCx <sup>6</sup>   | Analog 3.3 V supply to ADC           |                               | 3.15 to 3.45   | 3.15 to 3.45   | V     |

| VCC33AP <sup>6</sup>     | Analog clean 3.3 V supply to t       | he charge pump                | 3.15 to 3.45   | 3.15 to 3.45   | V     |

| VCC33SDDx <sup>6</sup>   | Analog 3.3 V supply to sigma-        | delta DAC                     | 3.15 to 3.45   | 3.15 to 3.45   | V     |

| VAREFx                   | Voltage reference for ADC            |                               | 2.527 to 3.3   | 2.527 to 3.3   | V     |

| VCCRCOSC                 | Analog supply to the integrate       | d RC oscillator               | 3.15 to 3.45   | 3.15 to 3.45   | V     |

| VDDBAT                   | External battery supply              |                               | 2.7 to 3.63    | 2.7 to 3.63    | V     |

| VCCMAINXTAL <sup>6</sup> | Analog supply to the main cry        | stal oscillator               | 3.15 to 3.45   | 3.15 to 3.45   | V     |

| VCCLPXTAL <sup>6</sup>   | Analog supply to the low poscillator | ower 32 KHz crystal           | 3.15 to 3.45   | 3.15 to 3.45   | V     |

| VCCENVM                  | Embedded nonvolatile memor           | 1.425 to 1.575                | 1.425 to 1.575 | V              |       |

| VCCESRAM                 | Embedded SRAM supply                 |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCC15A <sup>2</sup>      | Analog 1.5 V supply to the an        | alog circuitry                | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCC15ADCx <sup>2</sup>   | Analog 1.5 V supply to the AD        | OC .                          | 1.425 to 1.575 | 1.425 to 1.575 | V     |

- 1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

- 3. The Programming temperature range supported is  $T_{ambient} = 0$ °C to 85°C.

- 4. VPP can be left floating during operation (not programming mode).

- 5. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-19 on page 2-23. VCCxxxxIOBx should be at the same voltage within a given I/O bank.

- 6. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33AD, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs

|           |                                                      | Power Supply Device         |        |        |        |        |       |

|-----------|------------------------------------------------------|-----------------------------|--------|--------|--------|--------|-------|

| Parameter | Definition                                           | Name                        | Domain | A2F060 | A2F200 | A2F500 | Units |

| PAC24     | Current Monitor Power Contribution                   | See Table 2-93 on page 2-78 | _      |        | 1.03   |        |       |

| PAC25     | ABPS Power Contribution                              | See Table 2-96 on page 2-82 | _      |        | 0.70   |        | mW    |

| PAC26     | Sigma-Delta DAC Power<br>Contribution <sup>2</sup>   | See Table 2-98 on page 2-85 | _      |        | 0.58   |        | mW    |

| PAC27     | Comparator Power Contribution                        | See Table 2-97 on page 2-84 | _      | 1.02   |        |        | mW    |

| PAC28     | Voltage Regulator Power<br>Contribution <sup>3</sup> | See Table 2-99 on page 2-87 | _      |        | 36.30  |        | mW    |

- 1. For a different use of MSS peripherals and resources, refer to SmartPower.

- 2. Assumes Input = Half Scale Operation mode.

- 3. Assumes 100 mA load on 1.5 V domain.

Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs

|           |                                                                                                 | Power Supp                 |                                             |        |            |           |         |

|-----------|-------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------|--------|------------|-----------|---------|

| Parameter | Definition                                                                                      | Name                       | Domain                                      | A2F060 | A2F200     | A2F200    | Units   |

| PDC1      | Core static power contribution in SoC mode                                                      | VCC                        | 1.5 V                                       | 11.10  | 23.70      | 37.95     | mW      |

| PDC2      | Device static power contribution in Standby Mode                                                | See Table 2-8 on page 2-10 | _                                           | 11.10  | 23.70      | 37.95     | mW      |

| PDC3      | Device static power contribution in<br>Time Keeping mode                                        | See Table 2-8 on page 2-10 | 3.3 V                                       | 33.00  | 33.00      | 33.00     | μW      |

| PDC7      | Static contribution per input pin VCCxxxxIOBx/VCC See Table 2-(standard dependent contribution) |                            |                                             |        | d Table 2- | 11 on pag | e 2-11. |

| PDC8      | Static contribution per output pin (standard dependent contribution)                            | VCCxxxxIOBx/VCC            | See Table 2-12 and Table 2-13 on page 2-11. |        |            |           |         |

| PDC9      | Static contribution per PLL                                                                     | VCC                        | 1.5 V                                       | 2.55   | 2.55       | 2.55      | mW      |

Table 2-16 • eNVM Dynamic Power Consumption

| Parameter   | Description                     | Condition      | Min. | Тур.      | Max.        | Units  |

|-------------|---------------------------------|----------------|------|-----------|-------------|--------|

| eNVM System | eNVM array operating power      | Idle           |      | 795       |             | μA     |

|             |                                 | Read operation | See  | Table 2-1 | 4 on page 2 | 2-12   |

|             |                                 | Erase          |      | 900       |             | μA     |

|             |                                 | Write          |      | 900       |             | μA     |

| PNVMCTRL    | eNVM controller operating power |                |      | 20        |             | μW/MHz |

## **User I/O Characteristics**

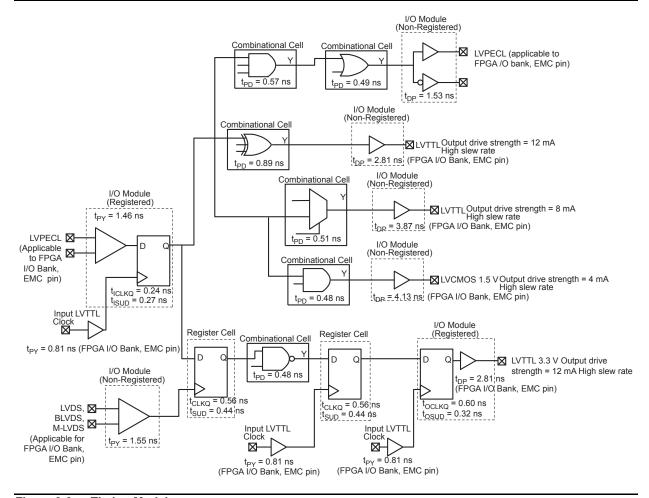

## **Timing Model**

Figure 2-2 • Timing Model

Operating Conditions: -1 Speed, Commercial Temperature Range (T<sub>J</sub> = 85°C),

Worst Case VCC = 1.425 V

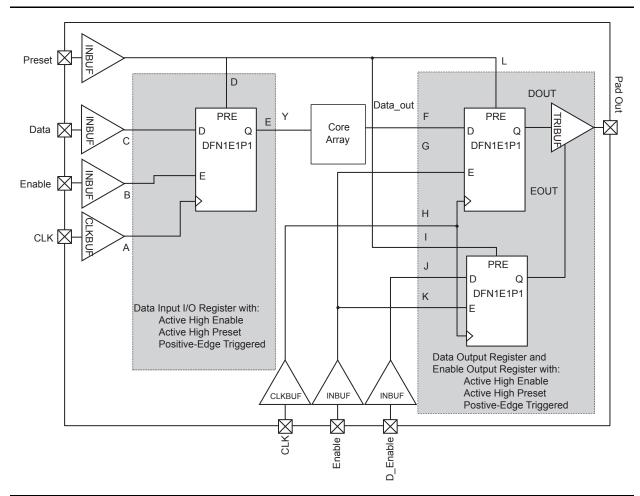

## I/O Register Specifications

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

Figure 2-14 • Timing Model of Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

2-44 Revision 13

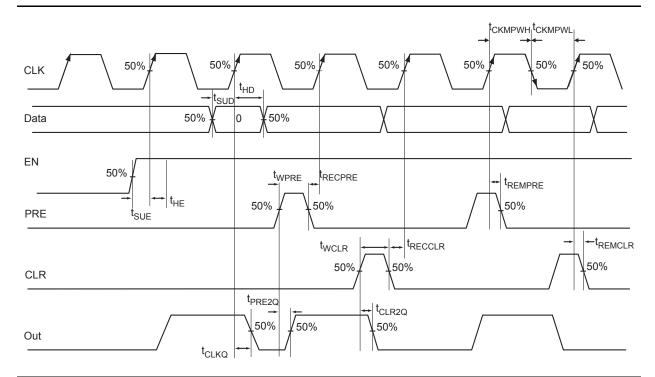

Figure 2-26 • Timing Model and Waveforms

### **Timing Characteristics**

Table 2-79 • Register Delays

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.56 | 0.67 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.44 | 0.52 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.46 | 0.55 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.41 | 0.49 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.41 | 0.49 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.23 | 0.27 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | 0.27 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.22 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.22 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.32 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.36 | ns    |

|                     | •                                                             | •    |      |       |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

2-58 Revision 13

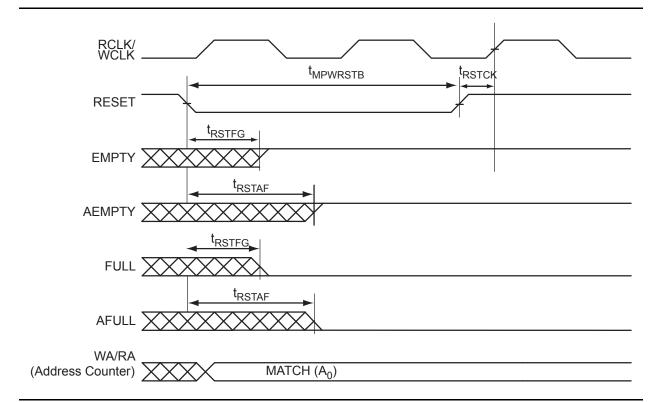

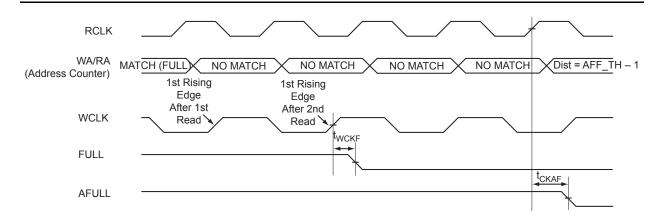

Figure 2-38 • FIFO Reset

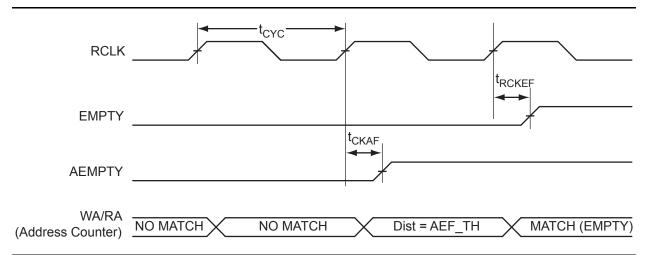

Figure 2-39 • FIFO EMPTY Flag and AEMPTY Flag Assertion

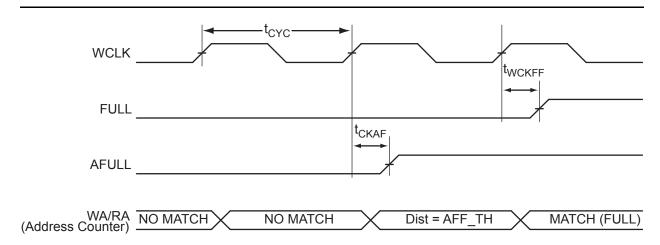

Figure 2-40 • FIFO FULL Flag and AFULL Flag Assertion

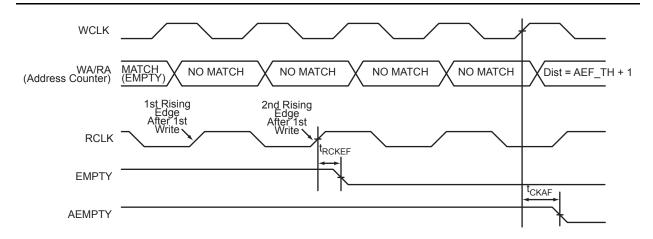

Figure 2-41 • FIFO EMPTY Flag and AEMPTY Flag Deassertion

Figure 2-42 • FIFO FULL Flag and AFULL Flag Deassertion

2-74 Revision 13

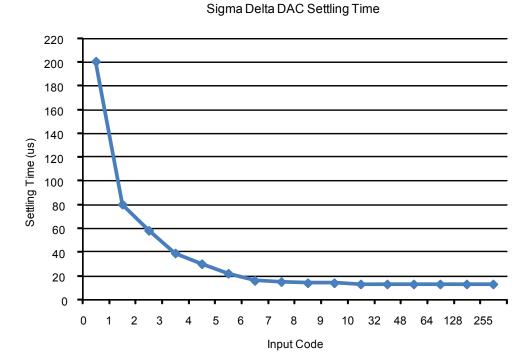

Table 2-98 • Analog Sigma-Delta DAC (continued)

| Specification                                                            | Test Conditions                                  | Min. | Тур. | Max. | Units |

|--------------------------------------------------------------------------|--------------------------------------------------|------|------|------|-------|

| Sigma-delta DAC power supply current requirements (not including VAREFx) | Input = 0, EN = 1<br>(operational mode)          |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 30   | 35   | μΑ    |

|                                                                          | VCC15A                                           |      | 3    | 5    | μΑ    |

|                                                                          | Input = Half scale, EN = 1 (operational mode)    |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 160  | 165  | μΑ    |

|                                                                          | VCC15A                                           |      | 33   | 35   | μA    |

|                                                                          | Input = Full scale, EN = 1<br>(operational mode) |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 280  | 285  | μA    |

|                                                                          | VCC15A                                           |      | 70   | 75   | μA    |

Note: \*FS is full-scale error, defined as the difference between the actual value that triggers the transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error. Refer to the Analog-to-Digital Converter chapter of the SmartFusion Programmable Analog User's Guide for more information.

Figure 2-44 • Sigma-Delta DAC Setting Time

2-86 Revision 13

# **Voltage Regulator**

Table 2-99 • Voltage Regulator

| Symbol              | Parameter                    |                       | Test Conditions                                         | Min.  | Тур. | Max.  | Unit |

|---------------------|------------------------------|-----------------------|---------------------------------------------------------|-------|------|-------|------|

| V <sub>OUT</sub>    | Output voltage               | T <sub>J</sub> = 25°C |                                                         | 1.425 | 1.5  | 1.575 | V    |

| V <sub>OS</sub>     | Output offset voltage        | T <sub>J</sub> = 25°C |                                                         |       | 11   |       | mV   |

| ICC33A              | Operation current            | T <sub>J</sub> = 25°C | I <sub>LOAD</sub> = 1 mA                                |       | 3.4  |       | mA   |

|                     |                              |                       | I <sub>LOAD</sub> = 100 mA                              |       | 11   |       | mA   |

|                     |                              |                       | I <sub>LOAD</sub> = 0.5 A                               |       | 21   |       | mA   |

| ΔV <sub>OUT</sub>   | Load regulation              | T <sub>J</sub> = 25°C | I <sub>LOAD</sub> = 1 mA to 0.5 A                       |       | 5.8  |       | mV   |

| ΔV <sub>OUT</sub>   | Line regulation              | T <sub>J</sub> = 25°C | VCC33A = 2.97 V to 3.63 V<br>I <sub>LOAD</sub> = 1 mA   |       | 5.3  |       | mV/V |

|                     |                              |                       | VCC33A = 2.97 V to 3.63 V<br>I <sub>LOAD</sub> = 100 mA |       | 5.3  |       | mV/V |

|                     |                              |                       | VCC33A = 2.97 V to 3.63 V<br>I <sub>LOAD</sub> = 500mA  |       | 5.3  |       | mV/V |

|                     | Dropout voltage <sup>1</sup> | T <sub>J</sub> = 25°C | I <sub>LOAD</sub> = 1 mA                                |       | 0.63 |       | V    |

|                     |                              |                       | I <sub>LOAD</sub> = 100 mA                              |       | 0.84 |       | V    |

|                     |                              |                       | I <sub>LOAD</sub> = 0.5 A                               |       | 1.35 |       | V    |

| I <sub>PTBASE</sub> | PTBase current               | T <sub>J</sub> = 25°C | I <sub>LOAD</sub> = 1 mA                                |       | 48   |       | μA   |

|                     |                              |                       | I <sub>LOAD</sub> = 100 mA                              |       | 736  |       | μΑ   |

|                     |                              |                       | I <sub>LOAD</sub> = 0.5 A                               |       | 12   |       | mA   |

|                     | Startup time <sup>2</sup>    | T <sub>J</sub> = 25°C |                                                         |       | 200  |       | μs   |

### Notes:

<sup>1.</sup> Dropout voltage is defined as the minimum VCC33A voltage. The parameter is specified with respect to the output voltage. The specification represents the minimum input-to-output differential voltage required to maintain regulation.

<sup>2.</sup> Assumes 10 μF.

# **User-Defined Supply Pins**

| Name     | Туре  | Polarity/<br>Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAREF0   | Input | 1                     | Analog reference voltage for first ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |       |                       | The SmartFusion cSoC can be configured to generate a 2.56 V internal reference that can be used by the ADC. While using the internal reference, the reference voltage is output on the VAREFOUT pin for use as a system reference. If a different reference voltage is required, it can be supplied by an external source and applied to this pin. The valid range of values that can be supplied to the ADC is 1.0 V to 3.3 V. When VAREF0 is internally generated, a bypass capacitor must be connected from this pin to ground. The value of the bypass capacitor should be between 3.3 $\mu\text{F}$ and 22 $\mu\text{F}$ , which is based on the needs of the individual designs. The choice of the capacitor value has an impact on the settling time it takes the VAREF0 signal to reach the required specification of 2.56 V to initiate valid conversions by the ADC. If the lower capacitor value is chosen, the settling time required for VAREF0 to achieve 2.56 V will be shorter than when selecting the larger capacitor value. The above range of capacitor values supports the accuracy specification of the ADC, which is detailed in the datasheet. Designers choosing the smaller capacitor value will not obtain as much margin in the accuracy as that achieved with a larger capacitor value. See the Analog-to-Digital Converter (ADC) section in the SmartFusion Programmable Analog User's Guide for more information. The SoC Products Group recommends customers use 10 $\mu\text{F}$ as the value of the bypass capacitor. Designers choosing to use an extranal VAREF0 pin before initiating conversions by the ADC. To use the internal voltage reference, the VAREFOUT pin must be connected to the appropriate ADC VAREFx input on the PCB. For example, VAREFOUT can be connected to VAREF1 only, if ADC1 alone is used. VAREFOUT can be connected to VAREF1 and VAREF2 together, if ADC0, ADC1, and ADC2 all are used. |

| VAREF1   | Input | 1                     | Analog reference voltage for second ADC See "VAREF0" above for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VAREF2   | Input | 1                     | Analog reference voltage for third ADC See "VAREF0" above for more.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VAREFOUT | Out   | 1                     | Internal 2.56 V voltage reference output. Can be used to provide the two ADCs with a unique voltage reference externally by connecting VAREFOUT to both VAREF0 and VAREF1. To use the internal voltage reference, you must connect the VAREFOUT pin to the appropriate ADC VAREFx input—either the VAREF0 or VAREF1 pin—on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# **JTAG Pins**

SmartFusion cSoCs have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the SmartFusion cSoC part must be supplied to allow JTAG signals to transition the SmartFusion cSoC. Isolating the JTAG power supply in a separate I/O bank gives greater flexibility with supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRSTB pin could be tied to GND.

| Name    | Туре | Polarity/<br>Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAGSEL | ln   | 1                     | JTAG controller selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Depending on the state of the JTAGSEL pin, an external JTAG controller will either see the FPGA fabric TAP/auxiliary TAP (High) or the Cortex-M3 JTAG debug interface (Low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |      |                       | The JTAGSEL pin should be connected to an external pull-up resistor such that the default configuration selects the FPGA fabric TAP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TCK     | In   | 1                     | Test clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |      |                       | Serial input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pull-up/-down resistor. If JTAG is not used, it is recommended to tie off TCK to GND or $V_{\rm JTAG}$ through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.                                                                                                                                                                                                                                                                                                                             |

|         |      |                       | Note that to operate at all V <sub>JTAG</sub> voltages, 500 $\Omega$ to 1 k $\Omega$ will satisfy the requirements. Refer to Table 5-1 on page 5-11 for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Can be left floating when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TDI     | In   | 1                     | Test data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDO     | Out  | 1                     | Test data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |      |                       | Serial output for JTAG boundary scan, ISP, and UJTAG usage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TMS     | In   | HIGH                  | Test mode select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |      |                       | The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |      |                       | Can be left floating when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRSTB   | In   | HIGH                  | Boundary scan reset pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |      |                       | The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the TAP is held in reset mode. The resistor values must be chosen from Table 5-1 on page 5-11 and must satisfy the parallel resistance value requirement. The values in Table 5-1 on page 5-11 correspond to the resistor recommended when a single device is used. The values correspond to the equivalent parallel resistor when multiple devices are connected via a JTAG chain. |

|         |      |                       | In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, it is recommended that you tie off TRST to GND through a resistor placed close to the FPGA pin.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |      |                       | The TRSTB pin also resets the serial wire JTAG – debug port (SWJ-DP) circuitry within the Cortex-M3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         |      |                       | Can be left floating when unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

5-10 Revision 13

### Pin Descriptions

| TQ144      |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| Pin Number | A2F060 Function |  |  |  |  |  |

| 109        | VPP             |  |  |  |  |  |

| 110        | GNDQ            |  |  |  |  |  |

| 111        | GCA1/IO20PDB0V0 |  |  |  |  |  |

| 112        | GCA0/IO20NDB0V0 |  |  |  |  |  |

| 113        | GCB1/IO19PDB0V0 |  |  |  |  |  |

| 114        | GCB0/IO19NDB0V0 |  |  |  |  |  |

| 115        | GCC1/IO18PDB0V0 |  |  |  |  |  |

| 116        | GCC0/IO18NDB0V0 |  |  |  |  |  |

| 117        | VCCFPGAIOB0     |  |  |  |  |  |

| 118        | GND             |  |  |  |  |  |

| 119        | VCC             |  |  |  |  |  |

| 120        | IO14PDB0V0      |  |  |  |  |  |

| 121        | IO14NDB0V0      |  |  |  |  |  |

| 122        | IO13NSB0V0      |  |  |  |  |  |

| 123        | IO11PDB0V0      |  |  |  |  |  |

| 124        | IO11NDB0V0      |  |  |  |  |  |

| 125        | IO09PDB0V0      |  |  |  |  |  |

| 126        | IO09NDB0V0      |  |  |  |  |  |

| 127        | VCCFPGAIOB0     |  |  |  |  |  |

| 128        | GND             |  |  |  |  |  |

| 129        | IO07PDB0V0      |  |  |  |  |  |

| 130        | IO07NDB0V0      |  |  |  |  |  |

| 131        | IO06PDB0V0      |  |  |  |  |  |

| 132        | IO06NDB0V0      |  |  |  |  |  |

| 133        | IO05PDB0V0      |  |  |  |  |  |

| 134        | IO05NDB0V0      |  |  |  |  |  |

| 135        | IO03PDB0V0      |  |  |  |  |  |

| 136        | IO03NDB0V0      |  |  |  |  |  |

| 137        | VCCFPGAIOB0     |  |  |  |  |  |

| 138        | GND             |  |  |  |  |  |

| 139        | VCC             |  |  |  |  |  |

| 140        | IO01PDB0V0      |  |  |  |  |  |

| 141        | IO01NDB0V0      |  |  |  |  |  |

| 142        | IO00PDB0V0      |  |  |  |  |  |

| 143        | IO00NDB0V0      |  |  |  |  |  |

| 144        | GNDQ            |  |  |  |  |  |

5-22 Revision 13

| Pin | CS288                 |                           |                           |  |

|-----|-----------------------|---------------------------|---------------------------|--|

| No. | A2F060 Function       | A2F200 Function           | A2F500 Function           |  |

| F12 | EMC_AB[12]/IO10NDB0V0 | EMC_AB[12]/IO10NDB0V0     | EMC_AB[12]/IO14NDB0V0     |  |

| F13 | GND                   | GND                       | GND                       |  |

| F14 | GCB1/IO19PPB0V0       | GCC1/IO26PPB1V0           | GCC1/IO35PPB1V0           |  |

| F15 | GNDQ                  | GNDQ                      | GNDQ                      |  |

| F16 | VCCFPGAIOB1           | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

| F17 | GCB0/IO19NPB0V0       | IO24NDB1V0                | IO33NDB1V0                |  |

| F19 | IO23NDB1V0            | GDB1/IO30PDB1V0           | GDB1/IO39PDB1V0           |  |

| F21 | GCA2/IO21PDB1V0       | GDB0/IO30NDB1V0           | GDB0/IO39NDB1V0           |  |

| G1  | IO41NDB5V0            | IO67NDB5V0                | IO84NDB5V0                |  |

| G3  | GFC2/IO41PDB5V0       | GFC2/IO67PDB5V0           | GFC2/IO84PDB5V0           |  |

| G5  | NC                    | GFB1/IO65PDB5V0           | GFB1/IO82PDB5V0           |  |

| G6  | EMC_DB[10]/IO43NDB5V0 | EMC_DB[10]/IO69NDB5V0     | EMC_DB[10]/IO86NDB5V0     |  |

| G9  | NC                    | GFC0/IO66NPB5V0           | GFC0/IO83NPB5V0           |  |

| G13 | GCA0/IO20NPB0V0       | GCC0/IO26NPB1V0           | GCC0/IO35NPB1V0           |  |

| G16 | NC                    | GDA0/IO31NDB1V0           | GDA0/IO40NDB1V0           |  |

| G17 | IO22NPB1V0            | GDC1/IO29PDB1V0           | GDC1/IO38PDB1V0           |  |

| G19 | GCC2/IO23PDB1V0       | GDC0/IO29NDB1V0           | GDC0/IO38NDB1V0           |  |

| G21 | GND                   | GND                       | GND                       |  |

| H1  | EMC_DB[9]/IO40PPB5V0  | EMC_DB[9]/GEC1/IO63PPB5V0 | EMC_DB[9]/GEC1/IO80PPB5V0 |  |

| Н3  | GND                   | GND                       | GND                       |  |

| H5  | NC                    | GFB0/IO65NDB5V0           | GFB0/IO82NDB5V0           |  |

| H6  | EMC_DB[7]/IO39PDB5V0  | EMC_DB[7]/GEB1/IO62PDB5V0 | EMC_DB[7]/GEB1/IO79PDB5V0 |  |

| H8  | GND                   | GND                       | GND                       |  |

| Н9  | VCC                   | VCC                       | VCC                       |  |

| H10 | GND                   | GND                       | GND                       |  |

| H11 | VCC                   | VCC                       | VCC                       |  |

| H12 | GND                   | GND                       | GND                       |  |

| H13 | VCC                   | VCC                       | VCC                       |  |

| H14 | GND                   | GND                       | GND                       |  |

| H16 | NC                    | GDA1/IO31PDB1V0           | GDA1/IO40PDB1V0           |  |

| H17 | NC                    | GDC2/IO32PPB1V0           | GDC2/IO41PPB1V0           |  |

- 1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

- 2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

| Pin | CS288             |                   |                   |  |

|-----|-------------------|-------------------|-------------------|--|

| No. | A2F060 Function   | A2F200 Function   | A2F500 Function   |  |

| U5  | VCC33SDD0         | VCC33SDD0         | VCC33SDD0         |  |

| U6  | VCC15A            | VCC15A            | VCC15A            |  |

| U7  | NC                | ABPS3             | ABPS3             |  |

| U8  | NC                | ADC2              | ADC2              |  |

| U9  | NC                | VCC33ADC0         | VCC33ADC0         |  |

| U10 | GND15ADC0         | GND15ADC1         | GND15ADC1         |  |

| U11 | VCC33ADC0         | VCC33ADC1         | VCC33ADC1         |  |

| U12 | ADC10             | ADC7              | ADC7              |  |

| U13 | ABPS0             | ABPS6             | ABPS6             |  |

| U14 | GNDTM0            | GNDTM1            | GNDTM1            |  |

| U15 | SPI_1_CLK/GPIO_26 | SPI_1_CLK/GPIO_26 | SPI_1_CLK/GPIO_26 |  |

| U16 | SPI_0_CLK/GPIO_18 | SPI_0_CLK/GPIO_18 | SPI_0_CLK/GPIO_18 |  |

| U17 | SPI_0_SS/GPIO_19  | SPI_0_SS/GPIO_19  | SPI_0_SS/GPIO_19  |  |

| U19 | GND               | GND               | GND               |  |

| U21 | SPI_1_DO/GPIO_24  | SPI_1_DO/GPIO_24  | SPI_1_DO/GPIO_24  |  |

| V1  | NC                | MAC_CLK           | MAC_CLK           |  |

| V3  | GNDSDD0           | GNDSDD0           | GNDSDD0           |  |

| V19 | SPI_1_DI/GPIO_25  | SPI_1_DI/GPIO_25  | SPI_1_DI/GPIO_25  |  |

| V21 | VCCMSSIOB2        | VCCMSSIOB2        | VCCMSSIOB2        |  |

| W1  | PCAP              | PCAP              | PCAP              |  |

| W3  | NCAP              | NCAP              | NCAP              |  |

| W4  | ADC2              | CM0               | CM0               |  |

| W5  | ADC3              | TM0               | TM0               |  |

| W6  | ADC4              | TM1               | TM1               |  |

| W7  | NC                | ADC0              | ADC0              |  |

| W8  | NC                | ADC3              | ADC3              |  |

| W9  | NC                | GND33ADC0         | GND33ADC0         |  |

| W10 | VCC15ADC0         | VCC15ADC1         | VCC15ADC1         |  |

| W11 | GND33ADC0         | GND33ADC1         | GND33ADC1         |  |

| W12 | ADC8              | ADC5              | ADC5              |  |

| W13 | CM0               | CM3               | CM3               |  |

- 1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

- 2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

5-32 Revision 13

|            | PQ208                        |                 |

|------------|------------------------------|-----------------|

| Pin Number | A2F200                       | A2F500          |

| 187        | VCCFPGAIOB0                  | VCCFPGAIOB0     |

| 188        | GND                          | GND             |

| 189        | VCC                          | VCC             |

| 190        | EMC_AB[5]/IO06PDB0V0         | IO08PDB0V0      |

| 191        | EMC_AB[4]/IO06NDB0V0         | IO08NDB0V0      |

| 192        | EMC_AB[3]/IO05PDB0V0         | GAC1/IO07PDB0V0 |

| 193        | EMC_AB[2]/IO05NDB0V0         | GAC0/IO07NDB0V0 |

| 194        | EMC_AB[1]/IO04PDB0V0         | IO04PDB0V0      |

| 195        | EMC_AB[0]/IO04NDB0V0         | IO04NDB0V0      |

| 196        | EMC_OEN1_N/IO03PDB0V0        | IO03PDB0V0      |

| 197        | EMC_OEN0_N/IO03NDB0V0        | IO03NDB0V0      |

| 198        | EMC_BYTEN[1]/GAC1/IO02PDB0V0 | GAA1/IO02PDB0V0 |

| 199        | EMC_BYTEN[0]/GAC0/IO02NDB0V0 | GAA0/IO02NDB0V0 |

| 200        | VCCFPGAIOB0                  | VCCFPGAIOB0     |

| 201        | GND                          | GND             |

| 202        | VCC                          | VCC             |

| 203        | EMC_CS1_N/GAB1/IO01PDB0V0    | IO01PDB0V0      |

| 204        | EMC_CS0_N/GAB0/IO01NDB0V0    | IO01NDB0V0      |

| 205        | EMC_RW_N/GAA1/IO00PDB0V0     | IO00PDB0V0      |

| 206        | EMC_CLK/GAA0/IO00NDB0V0      | IO00NDB0V0      |

| 207        | VCCFPGAIOB0                  | VCCFPGAIOB0     |

| 208        | GNDQ                         | GNDQ            |

<sup>1.</sup> Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

<sup>2. \*:</sup> Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

| Pin FG256 |                         |                              |                              |

|-----------|-------------------------|------------------------------|------------------------------|

| No.       | A2F060 Function         | A2F200 Function              | A2F500 Function              |

| A1        | GND                     | GND                          | GND                          |

| A2        | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |

| A3        | EMC_AB[0]/IO04NDB0V0    | EMC_AB[0]/IO04NDB0V0         | EMC_AB[0]/IO06NDB0V0         |

| A4        | EMC_AB[1]/IO04PDB0V0    | EMC_AB[1]/IO04PDB0V0         | EMC_AB[1]/IO06PDB0V0         |

| A5        | GND                     | GND                          | GND                          |

| A6        | EMC_AB[3]/IO05PDB0V0    | EMC_AB[3]/IO05PDB0V0         | EMC_AB[3]/IO09PDB0V0         |

| A7        | EMC_AB[5]/IO06PDB0V0    | EMC_AB[5]/IO06PDB0V0         | EMC_AB[5]/IO10PDB0V0         |

| A8        | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |

| A9        | GND                     | GND                          | GND                          |

| A10       | EMC_AB[14]/IO11NDB0V0   | EMC_AB[14]/IO11NDB0V0        | EMC_AB[14]/IO15NDB0V0        |

| A11       | EMC_AB[15]/IO11PDB0V0   | EMC_AB[15]/IO11PDB0V0        | EMC_AB[15]/IO15PDB0V0        |

| A12       | GND                     | GND                          | GND                          |

| A13       | EMC_AB[20]/IO14NDB0V0   | EMC_AB[20]/IO14NDB0V0        | EMC_AB[20]/IO21NDB0V0        |

| A14       | EMC_AB[24]/IO16NDB0V0   | EMC_AB[24]/IO16NDB0V0        | EMC_AB[24]/IO20NDB0V0        |

| A15       | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |

| A16       | GND                     | GND                          | GND                          |

| B1        | EMC_DB[15]/IO45PDB5V0   | EMC_DB[15]/GAA2/IO71PDB5V0   | EMC_DB[15]/GAA2/IO88PDB5V0   |

| B2        | GND                     | GND                          | GND                          |

| В3        | EMC_BYTEN[1]/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO07PDB0V0 |

| B4        | EMC_OEN0_N/IO03NDB0V0   | EMC_OEN0_N/IO03NDB0V0        | EMC_OEN0_N/IO08NDB0V0        |

| B5        | EMC_OEN1_N/IO03PDB0V0   | EMC_OEN1_N/IO03PDB0V0        | EMC_OEN1_N/IO08PDB0V0        |

| В6        | EMC_AB[2]/IO05NDB0V0    | EMC_AB[2]/IO05NDB0V0         | EMC_AB[2]/IO09NDB0V0         |

| B7        | EMC_AB[4]/IO06NDB0V0    | EMC_AB[4]/IO06NDB0V0         | EMC_AB[4]/IO10NDB0V0         |

| B8        | EMC_AB[9]/IO08PDB0V0    | EMC_AB[9]/IO08PDB0V0         | EMC_AB[9]/IO13PDB0V0         |

| В9        | EMC_AB[12]/IO10NDB0V0   | EMC_AB[12]/IO10NDB0V0        | EMC_AB[12]/IO14NDB0V0        |

| B10       | EMC_AB[13]/IO10PDB0V0   | EMC_AB[13]/IO10PDB0V0        | EMC_AB[13]/IO14PDB0V0        |

| B11       | EMC_AB[16]/IO12NDB0V0   | EMC_AB[16]/IO12NDB0V0        | EMC_AB[16]/IO17NDB0V0        |

| B12       | EMC_AB[18]/IO13NDB0V0   | EMC_AB[18]/IO13NDB0V0        | EMC_AB[18]/IO18NDB0V0        |

| B13       | EMC_AB[21]/IO14PDB0V0   | EMC_AB[21]/IO14PDB0V0        | EMC_AB[21]/IO21PDB0V0        |

| B14       | EMC_AB[25]/IO16PDB0V0   | EMC_AB[25]/IO16PDB0V0        | EMC_AB[25]/IO20PDB0V0        |

| B15       | GND                     | GND                          | GND                          |

- 1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

- 2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

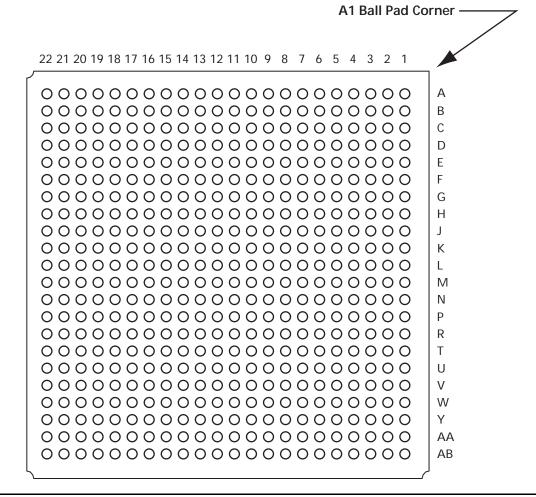

## **FG484**

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

5-52 Revision 13

|            | FG484                     |                           |  |

|------------|---------------------------|---------------------------|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |

| F17        | NC                        | IO25PPB1V0                |  |

| F18        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |

| F19        | IO23NDB1V0                | IO28NDB1V0                |  |

| F20        | NC                        | IO31PDB1V0                |  |

| F21        | NC                        | IO31NDB1V0                |  |

| F22        | IO22PDB1V0                | IO32PDB1V0                |  |

| G1         | GND                       | GND                       |  |

| G2         | GFB0/IO65NPB5V0           | GFB0/IO82NPB5V0           |  |

| G3         | EMC_DB[9]/GEC1/IO63PDB5V0 | EMC_DB[9]/GEC1/IO80PDB5V0 |  |

| G4         | GFC1/IO66PPB5V0           | GFC1/IO83PPB5V0           |  |

| G5         | EMC_DB[11]/IO69PPB5V0     | EMC_DB[11]/IO86PPB5V0     |  |

| G6         | GNDQ                      | GNDQ                      |  |

| G7         | NC                        | NC                        |  |

| G8         | GND                       | GND                       |  |

| G9         | VCCFPGAIOB0               | VCCFPGAIOB0               |  |

| G10        | GND                       | GND                       |  |

| G11        | VCCFPGAIOB0               | VCCFPGAIOB0               |  |

| G12        | GND                       | GND                       |  |

| G13        | VCCFPGAIOB0               | VCCFPGAIOB0               |  |

| G14        | GND                       | GND                       |  |

| G15        | VCCFPGAIOB0               | VCCFPGAIOB0               |  |

| G16        | GNDQ                      | GNDQ                      |  |

| G17        | NC                        | IO26PDB1V0                |  |

| G18        | NC                        | IO26NDB1V0                |  |

| G19        | GCA2/IO23PDB1V0           | GCA2/IO28PDB1V0 *         |  |

| G20        | IO24NDB1V0                | IO33NDB1V0                |  |

| G21        | GCB2/IO24PDB1V0           | GCB2/IO33PDB1V0           |  |

| G22        | GND                       | GND                       |  |

| H1         | EMC_DB[7]/GEB1/IO62PDB5V0 | EMC_DB[7]/GEB1/IO79PDB5V0 |  |

| H2         | VCCFPGAIOB5               | VCCFPGAIOB5               |  |

| H3         | EMC_DB[8]/GEC0/IO63NDB5V0 | EMC_DB[8]/GEC0/IO80NDB5V0 |  |

| H4         | GND                       | GND                       |  |

| H5         | GFC0/IO66NPB5V0           | GFC0/IO83NPB5V0           |  |

| H6         | GFA1/IO64PDB5V0           | GFA1/IO81PDB5V0           |  |

- 1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

- 2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

5-58 Revision 13

**Microsemi Corporate Headquarters** One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.