# E·XFL

Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

### Details

| Detalls                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Active                                                                       |

| Architecture            | MCU, FPGA                                                                    |

| Core Processor          | ARM® Cortex®-M3                                                              |

| Flash Size              | 256KB                                                                        |

| RAM Size                | 64KB                                                                         |

| Peripherals             | DMA, POR, WDT                                                                |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                         |

| Speed                   | 100MHz                                                                       |

| Primary Attributes      | ProASIC®3 FPGA, 200K Gates, 4608 D-Flip-Flops                                |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                           |

| Package / Case          | 208-BFQFP                                                                    |

| Supplier Device Package | 208-PQFP (28x28)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f200m3f-1pqg208i |

|                         |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

#### Standby Mode and Time Keeping Mode

$P_{NET} = 0 W$

### I/O Input Buffer Dynamic Contribution—PINPUTS

### SoC Mode

$\mathsf{P}_{\mathsf{INPUTS}}$  =  $\mathsf{N}_{\mathsf{INPUTS}}$  \*  $(\alpha_2$  / 2) \*  $\mathsf{P}_{\mathsf{AC9}}$  \*  $\mathsf{F}_{\mathsf{CLK}}$  Where:

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

### Standby Mode and Time Keeping Mode

P<sub>INPUTS</sub> = 0 W

### I/O Output Buffer Dynamic Contribution—POUTPUTS

### SoC Mode

$\mathsf{P}_{OUTPUTS} = \mathsf{N}_{OUTPUTS} * (\alpha_2 / 2) * \beta_1 * \mathsf{P}_{AC10} * \mathsf{F}_{CLK}$  Where:

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-17 on page 2-18.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-18 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

### Standby Mode and Time Keeping Mode

P<sub>OUTPUTS</sub> = 0 W

### FPGA Fabric SRAM Dynamic Contribution—P<sub>MEMORY</sub>

#### SoC Mode

$P_{MEMORY} = (N_{BLOCKS} * P_{AC11} * \beta_2 * F_{READ-CLOCK}) + (N_{BLOCKS} * P_{AC12} * \beta_3 * F_{WRITE-CLOCK})$ Where:

N<sub>BLOCKS</sub> is the number of RAM blocks used in the design.

$F_{READ-CLOCK}$  is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations—guidelines are provided in Table 2-18 on page 2-18.

$\beta_3$  the RAM enable rate for write operations—guidelines are provided in Table 2-18 on page 2-18. F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

#### Standby Mode and Time Keeping Mode

P<sub>MEMORY</sub> = 0 W

### PLL/CCC Dynamic Contribution—P<sub>PLL</sub>

#### SoC Mode

P<sub>PLL</sub> = P<sub>AC13</sub> \* F<sub>CLKOUT</sub>

F<sub>CLKIN</sub> is the input clock frequency.

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

### Standby Mode and Time Keeping Mode

<sup>1.</sup> The PLL dynamic contribution depends on the input clock frequency, the number of output clock signals generated by the PLL, and the frequency of each output clock. If a PLL is used to generate more than one output clock, include each output clock in the formula output clock by adding its corresponding contribution (P<sub>AC14</sub> \* F<sub>CLKOUT</sub> product) to the total PLL contribution.

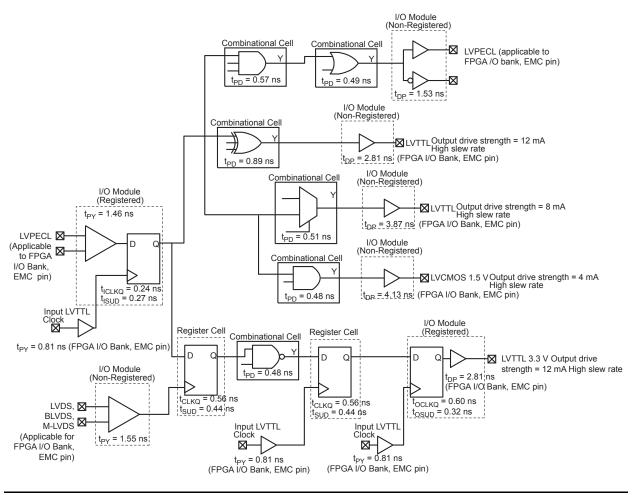

### **User I/O Characteristics**

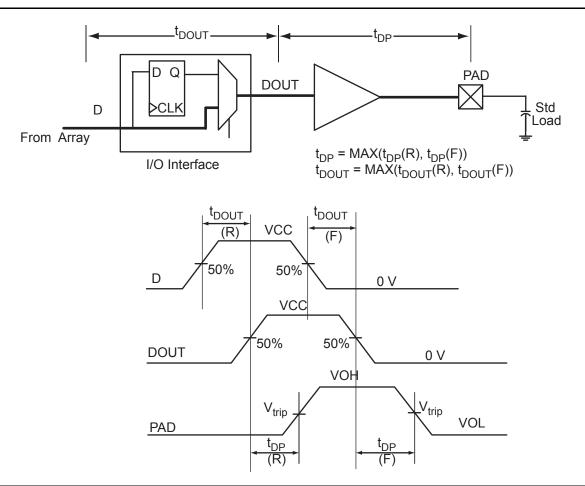

### **Timing Model**

Figure 2-2 • Timing Model Operating Conditions: –1 Speed, Commercial Temperature Range (T<sub>J</sub> = 85°C), Worst Case VCC = 1.425 V

SmartFusion Customizable System-on-Chip (cSoC)

Figure 2-4 • Output Buffer Model and Delays (example)

SmartFusion DC and Switching Characteristics

### **Detailed I/O DC Characteristics**

#### Table 2-26 • Input Capacitance

| Symbol          | Definition                         | Conditions                       | Min. | Max. | Units |

|-----------------|------------------------------------|----------------------------------|------|------|-------|

| C <sub>IN</sub> | Input capacitance                  | V <sub>IN</sub> = 0, f = 1.0 MHz |      | 8    | pF    |

| CINCLK          | Input capacitance on the clock pin | V <sub>IN</sub> = 0, f = 1.0 MHz |      | 8    | pF    |

#### Table 2-27 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to FPGA I/O Banks

| Standard                   | Drive Strength              | $R_{PULL-DOWN}$ $(\Omega)^2$ | ${\sf R}_{\sf PULL-UP} \ (\Omega)^3$ |

|----------------------------|-----------------------------|------------------------------|--------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 100                          | 300                                  |

|                            | 4 mA                        | 100                          | 300                                  |

|                            | 6 mA                        | 50                           | 150                                  |

|                            | 8 mA                        | 50                           | 150                                  |

|                            | 12 mA                       | 25                           | 75                                   |

|                            | 16 mA                       | 17                           | 50                                   |

|                            | 24 mA                       | 11                           | 33                                   |

| 2.5 V LVCMOS               | 2 mA                        | 100                          | 200                                  |

|                            | 4 mA                        | 100                          | 200                                  |

|                            | 6 mA                        | 50                           | 100                                  |

|                            | 8 mA                        | 50                           | 100                                  |

|                            | 12 mA                       | 25                           | 50                                   |

|                            | 16 mA                       | 20                           | 40                                   |

|                            | 24 mA                       | 11                           | 22                                   |

| 1.8 V LVCMOS               | 2 mA                        | 200                          | 225                                  |

|                            | 4 mA                        | 100                          | 112                                  |

|                            | 6 mA                        | 50                           | 56                                   |

|                            | 8 mA                        | 50                           | 56                                   |

|                            | 12 mA                       | 20                           | 22                                   |

|                            | 16 mA                       | 20                           | 22                                   |

| 1.5 V LVCMOS               | 2 mA                        | 200                          | 224                                  |

|                            | 4 mA                        | 100                          | 112                                  |

|                            | 6 mA                        | 67                           | 75                                   |

|                            | 8 mA                        | 33                           | 37                                   |

|                            | 12 mA                       | 33                           | 37                                   |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 25                           | 75                                   |

Notes:

1. These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website (also generated by the SoC Products Group Libero SoC toolset).

2. R<sub>(PULL-DOWN-MAX)</sub> = (V<sub>OLspec</sub>) / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (V<sub>CCImax</sub> - V<sub>OHspec</sub>) / I<sub>OHspec</sub>

### Timing Characteristics

### Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 7.20            | 0.04             | 0.97            | 0.39              | 7.34            | 6.18            | 2.52            | 2.46            | 9.39             | 8.23             | ns    |

|                   | -1             | 0.50              | 6.00            | 0.03             | 0.81            | 0.32              | 6.11            | 5.15            | 2.10            | 2.05            | 7.83             | 6.86             | ns    |

| 8 mA              | Std.           | 0.60              | 4.64            | 0.04             | 0.97            | 0.39              | 4.73            | 3.84            | 2.85            | 3.02            | 6.79             | 5.90             | ns    |

|                   | -1             | 0.50              | 3.87            | 0.03             | 0.81            | 0.32              | 3.94            | 3.20            | 2.37            | 2.52            | 5.65             | 4.91             | ns    |

| 12 mA             | Std.           | 0.60              | 3.37            | 0.04             | 0.97            | 0.39              | 3.43            | 2.67            | 3.07            | 3.39            | 5.49             | 4.73             | ns    |

|                   | -1             | 0.50              | 2.81            | 0.03             | 0.81            | 0.32              | 2.86            | 2.23            | 2.55            | 2.82            | 4.58             | 3.94             | ns    |

| 16 mA             | Std.           | 0.60              | 3.18            | 0.04             | 0.97            | 0.39              | 3.24            | 2.43            | 3.11            | 3.48            | 5.30             | 4.49             | ns    |

|                   | -1             | 0.50              | 2.65            | 0.03             | 0.81            | 0.32              | 2.70            | 2.03            | 2.59            | 2.90            | 4.42             | 3.74             | ns    |

| 24 mA             | Std.           | 0.60              | 2.93            | 0.04             | 0.97            | 0.39              | 2.99            | 2.03            | 3.17            | 3.83            | 5.05             | 4.09             | ns    |

|                   | -1             | 0.50              | 2.45            | 0.03             | 0.81            | 0.32              | 2.49            | 1.69            | 2.64            | 3.19            | 4.21             | 3.41             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### Table 2-39 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 9.75            | 0.04             | 0.97            | 0.39              | 9.93            | 8.22            | 2.52            | 2.31            | 11.99            | 10.28            | ns    |

|                   | -1             | 0.50              | 8.12            | 0.03             | 0.81            | 0.32              | 8.27            | 6.85            | 2.10            | 1.93            | 9.99             | 8.57             | ns    |

| 8 mA              | Std.           | 0.60              | 6.96            | 0.04             | 0.97            | 0.39              | 7.09            | 5.85            | 2.84            | 2.87            | 9.15             | 7.91             | ns    |

|                   | -1             | 0.50              | 5.80            | 0.03             | 0.81            | 0.32              | 5.91            | 4.88            | 2.37            | 2.39            | 7.62             | 6.59             | ns    |

| 12 mA             | Std.           | 0.60              | 5.35            | 0.04             | 0.97            | 0.39              | 5.45            | 4.58            | 3.06            | 3.23            | 7.51             | 6.64             | ns    |

|                   | -1             | 0.50              | 4.46            | 0.03             | 0.81            | 0.32              | 4.54            | 3.82            | 2.55            | 2.69            | 6.26             | 5.53             | ns    |

| 16 mA             | Std.           | 0.60              | 5.01            | 0.04             | 0.97            | 0.39              | 5.10            | 4.30            | 3.11            | 3.32            | 7.16             | 6.36             | ns    |

|                   | -1             | 0.50              | 4.17            | 0.03             | 0.81            | 0.32              | 4.25            | 3.58            | 2.59            | 2.77            | 5.97             | 5.30             | ns    |

| 24 mA             | Std.           | 0.60              | 4.67            | 0.04             | 0.97            | 0.39              | 4.75            | 4.28            | 3.16            | 3.66            | 6.81             | 6.34             | ns    |

|                   | -1             | 0.50              | 3.89            | 0.03             | 0.81            | 0.32              | 3.96            | 3.57            | 2.64            | 3.05            | 5.68             | 5.28             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### Table 2-40 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 8 mA              | Std.           | 0.22              | 2.31            | 0.09             | 0.94            | 1.30             | 0.22              | 2.35            | 1.86            | 2.20            | 2.45            | ns    |

|                   | -1             | 0.18              | 1.92            | 0.07             | 0.78            | 1.09             | 0.18              | 1.96            | 1.55            | 1.83            | 2.04            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### **Timing Characteristics**

### Table 2-44 • 2.5 V LVCMOS High Slew

Worst Commercial-Case Conditions:  $T_J = 85^{\circ}C$ , Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 2.3 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.55              | 8.10            | 0.04             | 1.23            | 0.39              | 7.37            | 8.10            | 2.54            | 2.17            | 9.43             | 10.15            | ns    |

|                   | –1             | 0.46              | 6.75            | 0.03             | 1.03            | 0.32              | 6.14            | 6.75            | 2.12            | 1.81            | 7.85             | 8.46             | ns    |

| 8 mA              | Std.           | 0.55              | 4.85            | 0.04             | 1.23            | 0.39              | 4.76            | 4.85            | 2.90            | 2.83            | 6.82             | 6.91             | ns    |

|                   | –1             | 0.46              | 4.04            | 0.03             | 1.03            | 0.32              | 3.97            | 4.04            | 2.42            | 2.36            | 5.68             | 5.76             | ns    |

| 12 mA             | Std.           | 0.60              | 3.28            | 0.04             | 1.23            | 0.39              | 3.46            | 3.23            | 3.15            | 3.24            | 5.52             | 5.29             | ns    |

|                   | -1             | 0.50              | 2.73            | 0.03             | 1.03            | 0.32              | 2.88            | 2.69            | 2.62            | 2.70            | 4.60             | 4.41             | ns    |

| 16 mA             | Std.           | 0.60              | 3.09            | 0.04             | 1.23            | 0.39              | 3.27            | 2.88            | 3.20            | 3.35            | 5.33             | 4.94             | ns    |

|                   | -1             | 0.50              | 2.57            | 0.03             | 1.03            | 0.32              | 2.72            | 2.40            | 2.67            | 2.79            | 4.44             | 4.12             | ns    |

| 24 mA             | Std.           | 0.60              | 2.95            | 0.04             | 1.23            | 0.39              | 3.01            | 2.31            | 3.27            | 3.76            | 5.07             | 4.37             | ns    |

|                   | -1             | 0.50              | 2.46            | 0.03             | 1.03            | 0.32              | 2.51            | 1.93            | 2.73            | 3.13            | 4.22             | 3.64             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-45 • 2.5 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J = 85^{\circ}C$ , Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 2.3 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.55              | 10.50           | 0.04             | 1.23            | 0.39              | 10.69           | 10.50           | 2.54            | 2.07            | 12.75            | 12.56            | ns    |

|                   | -1             | 0.46              | 8.75            | 0.03             | 1.03            | 0.32              | 8.91            | 8.75            | 2.12            | 1.73            | 10.62            | 10.47            | ns    |

| 8 mA              | Std.           | 0.55              | 7.61            | 0.04             | 1.23            | 0.39              | 7.46            | 7.19            | 2.81            | 2.66            | 9.52             | 9.25             | ns    |

|                   | -1             | 0.46              | 6.34            | 0.03             | 1.03            | 0.32              | 6.22            | 5.99            | 2.34            | 2.22            | 7.93             | 7.71             | ns    |

| 12 mA             | Std.           | 0.60              | 5.92            | 0.04             | 1.23            | 0.39              | 5.79            | 5.45            | 3.04            | 3.06            | 7.85             | 7.51             | ns    |

|                   | -1             | 0.50              | 4.93            | 0.03             | 1.03            | 0.32              | 4.83            | 4.54            | 2.53            | 2.55            | 6.54             | 6.26             | ns    |

| 16 mA             | Std.           | 0.60              | 5.53            | 0.04             | 1.23            | 0.39              | 5.40            | 5.09            | 3.09            | 3.16            | 7.46             | 7.14             | ns    |

|                   | -1             | 0.50              | 4.61            | 0.03             | 1.03            | 0.32              | 4.50            | 4.24            | 2.58            | 2.64            | 6.22             | 5.95             | ns    |

| 24 mA             | Std.           | 0.60              | 5.18            | 0.04             | 1.23            | 0.39              | 5.28            | 5.14            | 3.27            | 3.64            | 7.34             | 7.20             | ns    |

|                   | -1             | 0.50              | 4.32            | 0.03             | 1.03            | 0.32              | 4.40            | 4.29            | 2.72            | 3.03            | 6.11             | 6.00             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### Table 2-46 • 2.5 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 8 mA              | Std.           | 0.22              | 2.35            | 0.09             | 1.18            | 1.39             | 0.22              | 2.40            | 2.18            | 2.19            | 2.32            | ns    |

|                   | -1             | 0.18              | 1.96            | 0.07             | 0.99            | 1.16             | 0.18              | 2.00            | 1.82            | 1.82            | 1.93            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

SmartFusion DC and Switching Characteristics

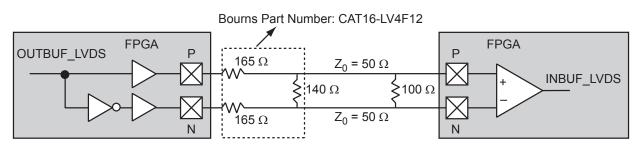

### **Differential I/O Characteristics**

### **Physical Implementation**

Configuration of the I/O modules as a differential pair is handled by SoC Products Group Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

### LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-11. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, SmartFusion cSoCs also support bus LVDS structure and multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-11 • LVDS Circuit Diagram and Board-Level Implementation

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>ОНD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| tosue                 | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| tOESUE                | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

### Table 2-70 • Parameter Definition and Measuring Nodes

\* See Figure 2-15 on page 2-46 for more information.

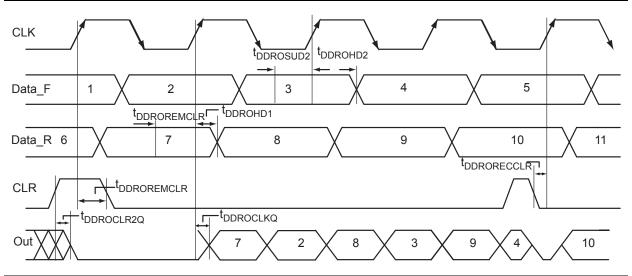

SmartFusion DC and Switching Characteristics

|  | Figure 2-22 | Output D | DR Timing | Diagram |

|--|-------------|----------|-----------|---------|

|--|-------------|----------|-----------|---------|

### **Timing Characteristics**

### *Table 2-77* • Output DDR Propagation Delays Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                           | –1   | Units |

|-------------------------|-------------------------------------------------------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.71 | ns    |

| t <sub>DDROSUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.38 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.38 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.81 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.23 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.22 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width High for the Output DDR     | 0.36 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output DDR      | 0.32 | ns    |

| F <sub>DDOMAX</sub>     | Maximum Frequency for the Output DDR                  | 350  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### **Temperature Monitor**

Unless otherwise noted, temperature monitor performance is specified with a 2N3904 diode-connected bipolar transistor from National Semiconductor or Infineon Technologies, nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 62.5 Ksps. After digital compensation. Unless otherwise noted, the specifications pertain to conditions where the SmartFusion cSoC and the sensing diode are at the same temperature.

| Table 2-94 • Temperature Monitor Performance Specifications |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Specification                                                  | Test Conditions                                                                                         | Min.  | Typical | Max.   | Units  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|---------|--------|--------|

| Input diode temperature range                                  |                                                                                                         | -55   |         | 150    | °C     |

|                                                                |                                                                                                         | 233.2 |         | 378.15 | K      |

| Temperature sensitivity                                        |                                                                                                         |       | 2.5     |        | mV/K   |

| Intercept                                                      | Extrapolated to 0K                                                                                      |       | 0       |        | V      |

| Input referred temperature offset error                        | At 25°C (298.15K)                                                                                       |       | ±1      | 1.5    | °C     |

| Gain error                                                     | Slope of BFSL vs. 2.5 mV/K                                                                              |       | ±1      | 2.5    | % nom. |

| Overall accuracy                                               | Peak error from ideal transfer function                                                                 |       | ±2      | ±3     | °C     |

| Input referred noise                                           | At 25°C (298.15K) – no output averaging                                                                 |       | 4       |        | °C rms |

| Output current                                                 | Idle mode                                                                                               |       | 100     |        | μA     |

|                                                                | Final measurement phases                                                                                |       | 10      |        | μA     |

| Analog settling time                                           | Measured to 0.1% of final value, (with ADC load)                                                        |       |         |        |        |

|                                                                | From TM_STB (High)                                                                                      | 5     |         |        | μs     |

|                                                                | From ADC_START (High)                                                                                   | 5     |         | 105    | μs     |

| AT parasitic capacitance                                       |                                                                                                         |       |         | 500    | pF     |

| Power supply rejection ratio                                   | DC (0–10 KHz)                                                                                           | 1.2   | 0.7     |        | °C/V   |

| Input referred temperature sensitivity error                   | Variation due to device temperature<br>(-40°C to +100°C). External temperature<br>sensor held constant. |       | 0.005   | 0.008  | °C/°C  |

| Temperature monitor (TM)                                       | VCC33A                                                                                                  |       | 200     |        | μA     |

| operational power supply current requirements (per temperature | VCC33AP                                                                                                 |       | 150     |        | μA     |

| monitor instance, not including ADC or VAREFx)                 | VCC15A                                                                                                  |       | 50      |        | μA     |

Note: All results are based on averaging over 64 samples.

### static Microsemi.

SmartFusion DC and Switching Characteristics

### Comparator

Unless otherwise specified, performance is specified at 25°C with nominal power supply voltages.

| Specification                                                   | Test Condition                                  | IS                                   | Min. | Тур.                                                                                                            | Max.                                                                                                                                                                                                                              | Units |

|-----------------------------------------------------------------|-------------------------------------------------|--------------------------------------|------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Input voltage range                                             | Minimum                                         |                                      |      | 0                                                                                                               |                                                                                                                                                                                                                                   | V     |

|                                                                 | Maximum                                         |                                      |      | 2.56                                                                                                            |                                                                                                                                                                                                                                   | V     |

| Input offset voltage                                            | HYS[1:0] = 00                                   |                                      |      | ±1                                                                                                              | ±3                                                                                                                                                                                                                                | mV    |

|                                                                 | (no hysteresis)                                 |                                      |      |                                                                                                                 |                                                                                                                                                                                                                                   |       |

| Input bias current                                              | t Comparator 1, 3, 5, 7, 9 (measured at 2.56 V) |                                      |      | 40                                                                                                              | 100                                                                                                                                                                                                                               | nA    |

|                                                                 | Comparator 0,                                   | 2, 4, 6, 8 (measured at 2.56 V)      |      | 150                                                                                                             | 300                                                                                                                                                                                                                               | nA    |

| Input resistance                                                |                                                 |                                      |      |                                                                                                                 |                                                                                                                                                                                                                                   | MΩ    |

| Power supply rejection ratio                                    | DC (0 – 10 KHz                                  | z)                                   | 50   | 60                                                                                                              |                                                                                                                                                                                                                                   | dB    |

| Propagation delay                                               | 100 mV overdri                                  | ve                                   |      |                                                                                                                 |                                                                                                                                                                                                                                   |       |

|                                                                 | HYS[1:0] = 00                                   |                                      |      |                                                                                                                 |                                                                                                                                                                                                                                   |       |

|                                                                 | (no hysteresis)                                 |                                      |      | 15                                                                                                              | 18                                                                                                                                                                                                                                | ns    |

|                                                                 | 100 mV overdrive                                |                                      |      |                                                                                                                 |                                                                                                                                                                                                                                   |       |

|                                                                 | HYS[1:0] = 10                                   |                                      |      |                                                                                                                 |                                                                                                                                                                                                                                   |       |

|                                                                 | (with hysteresis                                | 3)                                   |      | 25                                                                                                              | 30                                                                                                                                                                                                                                | ns    |

| Hysteresis                                                      | HYS[1:0] = 00                                   | Typical (25°C)                       | 0    | 0                                                                                                               | ±5                                                                                                                                                                                                                                | mV    |

| (± refers to rising and falling threshold shifts, respectively) |                                                 | Across all corners (–40°C to +100°C) | 0    |                                                                                                                 | ±5                                                                                                                                                                                                                                | mV    |

| tineshold sinits, respectively)                                 | HYS[1:0] = 01                                   | Typical (25°C)                       | ±3   | 40 100   150 300   60 -   60 -   15 18   15 18   15 18   25 30   0 ±5   ±16 ±30   ±36 ±36   ±31 ±48   ±105 ±190 | mV                                                                                                                                                                                                                                |       |

|                                                                 |                                                 | Across all corners (–40°C to +100°C) | 0    |                                                                                                                 | 1 $\pm$ 3 $\pm$ 1 $\pm$ 3   40 100   150 300   150 300   60 -   15 18   15 18   25 30   0 $\pm$ 5   16 $\pm$ 30 $\pm$ 31 $\pm$ 48 $\pm$ 31 $\pm$ 48   105 $\pm$ 190 $\pm$ 194 $\pm$ 194   150 165   160 $\pm$ 164   105 $\pm$ 194 | mV    |

|                                                                 | HYS[1:0] = 10                                   | Typical (25°C)                       | ±19  | ± 31                                                                                                            | ±48                                                                                                                                                                                                                               | mV    |

|                                                                 |                                                 | Across all corners (–40°C to +100°C) | ±12  |                                                                                                                 | ±54                                                                                                                                                                                                                               | mV    |

|                                                                 | HYS[1:0] = 11                                   | Typical (25°C)                       | ±80  | ± 105                                                                                                           | ±190                                                                                                                                                                                                                              | mV    |

|                                                                 |                                                 | Across all corners (–40°C to +100°C) | ±80  |                                                                                                                 | ±194                                                                                                                                                                                                                              | mV    |

| Comparator current                                              | VCC33A = 3.3                                    | V (operational mode); COMP_EN = 1    |      |                                                                                                                 | 1                                                                                                                                                                                                                                 |       |

| requirements<br>(per comparator)                                | VCC33A                                          |                                      |      | 150                                                                                                             | 165                                                                                                                                                                                                                               | μA    |

|                                                                 | VCC33AP 140                                     | 165                                  | μA   |                                                                                                                 |                                                                                                                                                                                                                                   |       |

|                                                                 | VCC15A                                          |                                      |      | 1                                                                                                               | 3                                                                                                                                                                                                                                 | μA    |

# **Serial Peripheral Interface (SPI) Characteristics**

This section describes the DC and switching of the SPI interface. Unless otherwise noted, all output characteristics given for a 35 pF load on the pins and all sequential timing characteristics are related to SPI\_x\_CLK. For timing parameter definitions, refer to Figure 2-47 on page 2-90.

| Symbol | Description and Condition                                      | A2F060 | A2F200 | A2F500 | Unit |  |  |

|--------|----------------------------------------------------------------|--------|--------|--------|------|--|--|

| sp1    | SPI_x_CLK minimum period                                       |        |        |        |      |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 20     | NA     | 20     | ns   |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 40     | 40     | 40     | ns   |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 80     | 80     | 80     | ns   |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.64   | 0.64   | 0.64   | μs   |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 1.28   | 1.28   | 1.28   | μs   |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 2.56   | 2.56   | 2.56   | μs   |  |  |

| sp2    | SPI_x_CLK minimum pulse width high                             |        |        |        |      |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | us   |  |  |

| sp3    | SPI_x_CLK minimum pulse width low                              |        |        |        |      |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | μs   |  |  |

| sp4    | SPI_x_CLK, SPI_x_DO, SPI_x_SS rise time (10%-90%) <sup>1</sup> | 4.7    | 4.7    | 4.7    | ns   |  |  |

| sp5    | SPI_x_CLK, SPI_x_DO, SPI_x_SS fall time (10%-90%) <sup>1</sup> | 3.4    | 3.4    | 3.4    | ns   |  |  |

### Table 2-100 • SPI Characteristics

Commercial Case Conditions: T<sub>J</sub> = 85°C, VDD = 1.425 V, -1 Speed Grade

Notes:

These values are provided for a load of 35 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

2. For allowable pclk configurations, refer to the Serial Peripheral Interface Controller section in the SmartFusion Microcontroller Subsystem User's Guide.

# **3 – SmartFusion Development Tools**

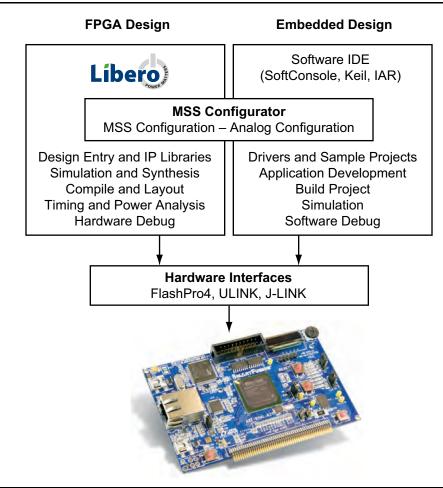

Designing with SmartFusion cSoCs involves three different types of design: FPGA design, embedded design and analog design. These roles can be filled by three different designers, two designers or even a single designer, depending on company structure and project complexity.

# **Types of Design Tools**

Microsemi has developed design tools and flows to meet the needs of these three types of designers so they can work together smoothly on a single project (Figure 3-1).

Figure 3-1 • Three Design Roles

### **FPGA** Design

Libero System-on-Chip (SoC) software is Microsemi's comprehensive software toolset for designing with all Microsemi FPGAs and cSoCs. Libero SoC includes industry-leading synthesis, simulation and debug tools from Synopsys<sup>®</sup> and Mentor Graphics<sup>®</sup>, as well as innovative timing and power optimization and analysis.

SmartFusion Customizable System-on-Chip (cSoC)

### Table 5-1 • Recommended Tie-Off Values for the TCK and TRST Pins

| VJTAG          | Tie-Off Resistance <sup>1, 2</sup> |

|----------------|------------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                      |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                      |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ                      |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                      |

Notes:

1. The TCK pin can be pulled up/down.

2. The TRST pin can only be pulled down.

1. Equivalent parallel resistance if more than one device is on JTAG chain.

# **Pin Assignment Tables**

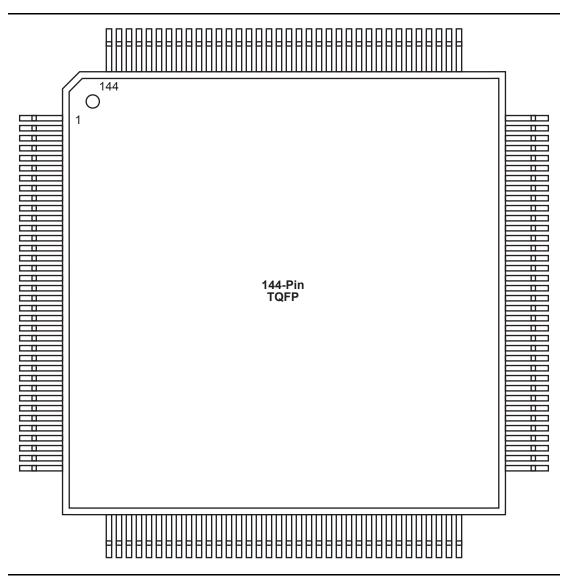

**TQ144**

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin | CS288            |                  |                  |  |  |

|-----|------------------|------------------|------------------|--|--|

| No. | A2F060 Function  | A2F200 Function  | A2F500 Function  |  |  |

| W14 | ADC5             | CM2              | CM2              |  |  |

| W15 | NC               | ABPS5            | ABPS5            |  |  |

| W16 | GNDAQ            | GNDAQ            | GNDAQ            |  |  |

| W17 | NC               | VCC33SDD1        | VCC33SDD1        |  |  |

| W18 | NC               | GNDSDD1          | GNDSDD1          |  |  |

| W19 | PTBASE           | PTBASE           | PTBASE           |  |  |

| W21 | SPI_0_DI/GPIO_17 | SPI_0_DI/GPIO_17 | SPI_0_DI/GPIO_17 |  |  |

| Y1  | VCC33AP          | VCC33AP          | VCC33AP          |  |  |

| Y21 | SPI_0_DO/GPIO_16 | SPI_0_DO/GPIO_16 | SPI_0_DO/GPIO_16 |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin | FG256                   |                              |                              |  |  |

|-----|-------------------------|------------------------------|------------------------------|--|--|

| No. | A2F060 Function         | A2F200 Function              | A2F500 Function              |  |  |

| A1  | GND                     | GND                          | GND                          |  |  |

| A2  | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| A3  | EMC_AB[0]/IO04NDB0V0    | EMC_AB[0]/IO04NDB0V0         | EMC_AB[0]/IO06NDB0V0         |  |  |

| A4  | EMC_AB[1]/IO04PDB0V0    | EMC_AB[1]/IO04PDB0V0         | EMC_AB[1]/IO06PDB0V0         |  |  |

| A5  | GND                     | GND                          | GND                          |  |  |

| A6  | EMC_AB[3]/IO05PDB0V0    | EMC_AB[3]/IO05PDB0V0         | EMC_AB[3]/IO09PDB0V0         |  |  |

| A7  | EMC_AB[5]/IO06PDB0V0    | EMC_AB[5]/IO06PDB0V0         | EMC_AB[5]/IO10PDB0V0         |  |  |

| A8  | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| A9  | GND                     | GND                          | GND                          |  |  |

| A10 | EMC_AB[14]/IO11NDB0V0   | EMC_AB[14]/IO11NDB0V0        | EMC_AB[14]/IO15NDB0V0        |  |  |

| A11 | EMC_AB[15]/IO11PDB0V0   | EMC_AB[15]/IO11PDB0V0        | EMC_AB[15]/IO15PDB0V0        |  |  |

| A12 | GND                     | GND                          | GND                          |  |  |

| A13 | EMC_AB[20]/IO14NDB0V0   | EMC_AB[20]/IO14NDB0V0        | EMC_AB[20]/IO21NDB0V0        |  |  |

| A14 | EMC_AB[24]/IO16NDB0V0   | EMC_AB[24]/IO16NDB0V0        | EMC_AB[24]/IO20NDB0V0        |  |  |

| A15 | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| A16 | GND                     | GND                          | GND                          |  |  |

| B1  | EMC_DB[15]/IO45PDB5V0   | EMC_DB[15]/GAA2/IO71PDB5V0   | EMC_DB[15]/GAA2/IO88PDB5V0   |  |  |

| B2  | GND                     | GND                          | GND                          |  |  |

| B3  | EMC_BYTEN[1]/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO07PDB0V0 |  |  |

| B4  | EMC_OEN0_N/IO03NDB0V0   | EMC_OEN0_N/IO03NDB0V0        | EMC_OEN0_N/IO08NDB0V0        |  |  |

| B5  | EMC_OEN1_N/IO03PDB0V0   | EMC_OEN1_N/IO03PDB0V0        | EMC_OEN1_N/IO08PDB0V0        |  |  |

| B6  | EMC_AB[2]/IO05NDB0V0    | EMC_AB[2]/IO05NDB0V0         | EMC_AB[2]/IO09NDB0V0         |  |  |

| B7  | EMC_AB[4]/IO06NDB0V0    | EMC_AB[4]/IO06NDB0V0         | EMC_AB[4]/IO10NDB0V0         |  |  |

| B8  | EMC_AB[9]/IO08PDB0V0    | EMC_AB[9]/IO08PDB0V0         | EMC_AB[9]/IO13PDB0V0         |  |  |

| B9  | EMC_AB[12]/IO10NDB0V0   | EMC_AB[12]/IO10NDB0V0        | EMC_AB[12]/IO14NDB0V0        |  |  |

| B10 | EMC_AB[13]/IO10PDB0V0   | EMC_AB[13]/IO10PDB0V0        | EMC_AB[13]/IO14PDB0V0        |  |  |

| B11 | EMC_AB[16]/IO12NDB0V0   | EMC_AB[16]/IO12NDB0V0        | EMC_AB[16]/IO17NDB0V0        |  |  |

| B12 | EMC_AB[18]/IO13NDB0V0   | EMC_AB[18]/IO13NDB0V0        | EMC_AB[18]/IO18NDB0V0        |  |  |

| B13 | EMC_AB[21]/IO14PDB0V0   | EMC_AB[21]/IO14PDB0V0        | EMC_AB[21]/IO21PDB0V0        |  |  |

| B14 | EMC_AB[25]/IO16PDB0V0   | EMC_AB[25]/IO16PDB0V0        | EMC_AB[25]/IO20PDB0V0        |  |  |

| B15 | GND                     | GND                          | GND                          |  |  |

### Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin   | FG256                 |                            |                            |  |  |

|-------|-----------------------|----------------------------|----------------------------|--|--|

| No.   | A2F060 Function       | A2F200 Function            | A2F500 Function            |  |  |

| D15   | GCA1/IO20PDB0V0       | IO24NDB1V0                 | IO33NDB1V0                 |  |  |

| D16   | VCCFPGAIOB1           | VCCFPGAIOB1                | VCCFPGAIOB1                |  |  |

| E1    | EMC_DB[13]/IO44PDB5V0 | EMC_DB[13]/GAC2/IO70PDB5V0 | EMC_DB[13]/GAC2/IO87PDB5V0 |  |  |

| E2    | EMC_DB[12]/IO44NDB5V0 | EMC_DB[12]/IO70NDB5V0      | EMC_DB[12]/IO87NDB5V0      |  |  |

| E3    | GFA2/IO42PDB5V0       | GFA2/IO68PDB5V0            | GFA2/IO85PDB5V0            |  |  |

| E4    | EMC_DB[10]/IO43NPB5V0 | EMC_DB[10]/IO69NPB5V0      | EMC_DB[10]/IO86NPB5V0      |  |  |

| E5    | GNDQ                  | GNDQ                       | GNDQ                       |  |  |

| E6    | GND                   | GND                        | GND                        |  |  |

| E7    | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |  |  |

| E8    | GND                   | GND                        | GND                        |  |  |

| E9    | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |  |  |

| E10   | GND                   | GND                        | GND                        |  |  |

| E11   | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |  |  |

| E12   | GCB2/IO22PDB1V0       | GCA1/IO28PDB1V0            | GCA1/IO36PDB1V0 *          |  |  |

| E13   | VCCFPGAIOB1           | VCCFPGAIOB1                | VCCFPGAIOB1                |  |  |

| E14   | GCA2/IO21PDB1V0       | GCB1/IO27PDB1V0            | GCB1/IO34PDB1V0            |  |  |

| E15   | GCC2/IO23PDB1V0       | GDC1/IO29PDB1V0            | GDC1/IO38PDB1V0            |  |  |

| E16   | IO23NDB1V0            | GDC0/IO29NDB1V0            | GDC0/IO38NDB1V0            |  |  |

| F1    | EMC_DB[9]/IO40PDB5V0  | EMC_DB[9]/GEC1/IO63PDB5V0  | EMC_DB[9]/GEC1/IO80PDB5V0  |  |  |

| F2    | GND                   | GND                        | GND                        |  |  |

| F3    | GFB2/IO42NDB5V0       | GFB2/IO68NDB5V0            | GFB2/IO85NDB5V0            |  |  |

| F4    | VCCFPGAIOB5           | VCCFPGAIOB5                | VCCFPGAIOB5                |  |  |

| F5    | EMC_DB[11]/IO43PPB5V0 | EMC_DB[11]/IO69PPB5V0      | EMC_DB[11]/IO86PPB5V0      |  |  |

| F6    | VCCFPGAIOB5           | VCCFPGAIOB5                | VCCFPGAIOB5                |  |  |

| F7    | GND                   | GND                        | GND                        |  |  |

| F8    | VCC                   | VCC                        | VCC                        |  |  |

| F9    | GND                   | GND                        | GND                        |  |  |

| F10   | VCC                   | VCC                        | VCC                        |  |  |

| F11   | GND                   | GND                        | GND                        |  |  |

| F12   | IO22NDB1V0            | GCA0/IO28NDB1V0            | GCA0/IO36NDB1V0 *          |  |  |

| F13   | NC                    | GNDQ                       | GNDQ                       |  |  |

| Notes |                       | ·                          |                            |  |  |

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                   | Changes                                                                                                                                                                                                                                                             | Page                   |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Revision 7                 | Usage instructions, such as how to handle the pin when unused, were added for the                                                                                                                                                                                   | 5-2                    |

| (continued)                | following supply pins (SAR 29769):                                                                                                                                                                                                                                  | through                |

|                            | "VCC15A"                                                                                                                                                                                                                                                            | 5-3                    |

|                            | "VCC15ADC0" through "VCC15ADC2"                                                                                                                                                                                                                                     |                        |

|                            | "VCC33ADC0" through "VCC33ADC2"                                                                                                                                                                                                                                     |                        |

|                            | "VCC33AP"                                                                                                                                                                                                                                                           |                        |

|                            | "VCC33ADC2"                                                                                                                                                                                                                                                         |                        |

|                            | "VCCLPXTAL"                                                                                                                                                                                                                                                         |                        |

|                            | "VCCMAINXTAL"                                                                                                                                                                                                                                                       |                        |

|                            | "VCCMSSIOB2"                                                                                                                                                                                                                                                        |                        |

|                            | "VCCPLLx"                                                                                                                                                                                                                                                           |                        |

|                            | "VCCRCOSC"                                                                                                                                                                                                                                                          |                        |

|                            | "VDDBAT"                                                                                                                                                                                                                                                            |                        |

|                            | The "IO" description was revised to clarify the definitions of u, I/O pair, and w, differential pair (SAR 31147). Information on configuration of unused I/Os (including unused MSS I/Os, SAR 26891) was added (SAR 32643).                                         | 5-6                    |

|                            | Usage instructions were added for the following pins (SAR 29769):                                                                                                                                                                                                   | 5-9                    |

|                            | "MSS_RESET_N"                                                                                                                                                                                                                                                       | through                |

|                            | "TCK"                                                                                                                                                                                                                                                               | 5-13                   |

|                            | "TMS"                                                                                                                                                                                                                                                               |                        |

|                            | "TRSTB"                                                                                                                                                                                                                                                             |                        |

|                            | "MAC_CLK"                                                                                                                                                                                                                                                           |                        |

|                            | Package names used in the "Pin Assignment Tables" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                                  | 5-18                   |

|                            | The pin assignments for A2F060 for "TQ144" and "FG256" have been revised due to the device status change from advance to preliminary (SAR 33068).                                                                                                                   | 5-18,<br>5-42          |

|                            | The "TQ144" and "FG256" pin assignment sections previously compared functions between A2F060/A2F200 devices in one table and A2F200/A2F500 in a separate table. Functions for all three devices have now been combined into one table for each package (SAR 33072). |                        |

|                            | The "PQ208" pin table was revised for A2F500 to remove EMC functions, which are not available for this device/package combination (SAR 33041).                                                                                                                      | 5-34                   |