Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

-XF

| Product Status          | Active                                                                     |

|-------------------------|----------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                  |

| Core Processor          | ARM® Cortex®-M3                                                            |

| Flash Size              | 256KB                                                                      |

| RAM Size                | 64KB                                                                       |

| Peripherals             | DMA, POR, WDT                                                              |

| Connectivity            | EBI/EMI, Ethernet, I²C, SPI, UART/USART                                    |

| Speed                   | 80MHz                                                                      |

| Primary Attributes      | ProASIC®3 FPGA, 200K Gates, 4608 D-Flip-Flops                              |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                            |

| Package / Case          | 256-LBGA                                                                   |

| Supplier Device Package | 256-FPBGA (17x17)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f200m3f-fgg256 |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                               | VCCMSSIOBx (V) | Static Power<br>PDC7 (mW) | Dynamic Power<br>PAC9 (µW/MHz) |

|-----------------------------------------------|----------------|---------------------------|--------------------------------|

| Single-Ended                                  | + +            |                           |                                |

| 3.3 V LVTTL / 3.3 V LVCMOS                    | 3.3            | _                         | 17.21                          |

| 3.3 V LVCMOS / 3.3 V LVCMOS – Schmitt trigger | 3.3            | _                         | 20.00                          |

| 2.5 V LVCMOS                                  | 2.5            | _                         | 5.55                           |

| 2.5 V LVCMOS – Schmitt trigger                | 2.5            | -                         | 7.03                           |

| 1.8 V LVCMOS                                  | 1.8            | _                         | 2.61                           |

| 1.8 V LVCMOS – Schmitt trigger                | 1.8            | -                         | 2.72                           |

| 1.5 V LVCMOS (JESD8-11)                       | 1.5            | _                         | 1.98                           |

| 1.5 V LVCMOS (JESD8-11) – Schmitt trigger     | 1.5            | -                         | 1.93                           |

## Table 2-11 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings Applicable to MSS I/O Banks

## Table 2-12 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings<sup>\*</sup> Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

|                            | C <sub>LOAD</sub> (pF) | VCCFPGAIOBx<br>(V) | Static Power<br>PDC8 (mW) | Dynamic Power<br>PAC10 (µW/MHz) |

|----------------------------|------------------------|--------------------|---------------------------|---------------------------------|

| Single-Ended               |                        |                    |                           |                                 |

| 3.3 V LVTTL / 3.3 V LVCMOS | 35                     | 3.3                | _                         | 475.66                          |

| 2.5 V LVCMOS               | 35                     | 2.5                | _                         | 270.50                          |

| 1.8 V LVCMOS               | 35                     | 1.8                | _                         | 152.17                          |

| 1.5 V LVCMOS (JESD8-11)    | 35                     | 1.5                | _                         | 104.44                          |

| 3.3 V PCI                  | 10                     | 3.3                | _                         | 202.69                          |

| 3.3 V PCI-X                | 10                     | 3.3                | _                         | 202.69                          |

| Differential               |                        |                    |                           | -                               |

| LVDS                       | -                      | 2.5                | 7.74                      | 88.26                           |

| LVPECL                     | _                      | 3.3                | 19.54                     | 164.99                          |

*Note:* \*Dynamic power consumption is given for standard load and software default drive strength and output slew.

## Table 2-13 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings Applicable to MSS I/O Banks

|                            | C <sub>LOAD</sub> (pF) | VCCMSSIOBx (V) Static Power<br>PDC8 (mW) <sup>2</sup> |   | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|----------------------------|------------------------|-------------------------------------------------------|---|----------------------------------------------|

| Single-Ended               |                        |                                                       |   |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS | 10                     | 3.3                                                   | _ | 155.65                                       |

| 2.5 V LVCMOS               | 10                     | 2.5                                                   | _ | 88.23                                        |

| 1.8 V LVCMOS               | 10                     | 1.8                                                   | _ | 45.03                                        |

| 1.5 V LVCMOS (JESD8-11)    | 10                     | 1.5                                                   | _ | 31.01                                        |

### Standby Mode

$P_{DYN} = P_{RC-OSC} + P_{LPXTAL-OSC}$

### Time Keeping Mode

$P_{DYN} = P_{LPXTAL-OSC}$

# **Global Clock Dynamic Contribution**—**P**<sub>CLOCK</sub>

#### SoC Mode

$P_{CLOCK} = (P_{AC1} + N_{SPINE} * P_{AC2} + N_{ROW} * PAC3 + N_{S-CELL} * P_{AC4}) * F_{CLK}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Device Architecture" chapter of the *SmartFusion FPGA Fabric User's Guide.*

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Device Architecture" chapter of the *SmartFusion FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

#### Standby Mode and Time Keeping Mode

$P_{CLOCK} = 0 W$

### Sequential Cells Dynamic Contribution—P<sub>S-CELL</sub>

#### SoC Mode

$P_{S-CELL} = N_{S-CELL} * (P_{AC5} + (\alpha_1 / 2) * P_{AC6}) * F_{CLK}$

$N_{S-CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Time Keeping Mode

$P_{S-CELL} = 0 W$

## Combinatorial Cells Dynamic Contribution—P<sub>C-CELL</sub>

#### SoC Mode

$P_{C-CELL} = N_{C-CELL} * (\alpha_1 / 2) * P_{AC7} * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Time Keeping Mode

$P_{C-CELL} = 0 W$

## Routing Net Dynamic Contribution—P<sub>NET</sub>

### SoC Mode

$\mathsf{P}_{\mathsf{NET}} = (\mathsf{N}_{\mathsf{S}\text{-}\mathsf{CELL}} + \mathsf{N}_{\mathsf{C}\text{-}\mathsf{CELL}}) * (\alpha_1 / 2) * \mathsf{P}_{\mathsf{AC8}} * \mathsf{F}_{\mathsf{CLK}}$

N<sub>S-CELL</sub> is the number VersaTiles used as sequential modules in the design.

$N_{C\mbox{-}C\mbox{-}E\mbox{-}L\mbox{-}L}$  is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the frequency of the clock driving the logic including these nets.

SmartFusion DC and Switching Characteristics

## Table 2-30 • I/O Short Currents I<sub>OSH</sub>/I<sub>OSL</sub> Applicable to FPGA I/O Banks

|                            | Drive Strength              | I <sub>OSL</sub> (mA) <sup>*</sup> | l <sub>OSH</sub> (mA) <sup>*</sup> |

|----------------------------|-----------------------------|------------------------------------|------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 27                                 | 25                                 |

|                            | 4 mA                        | 27                                 | 25                                 |

|                            | 6 mA                        | 54                                 | 51                                 |

|                            | 8 mA                        | 54                                 | 51                                 |

|                            | 12 mA                       | 109                                | 103                                |

|                            | 16 mA                       | 127                                | 132                                |

|                            | 24 mA                       | 181                                | 268                                |

| 2.5 V LVCMOS               | 2 mA                        | 18                                 | 16                                 |

|                            | 4 mA                        | 18                                 | 16                                 |

|                            | 6 mA                        | 37                                 | 32                                 |

|                            | 8 mA                        | 37                                 | 32                                 |

|                            | 12 mA                       | 74                                 | 65                                 |

|                            | 16 mA                       | 87                                 | 83                                 |

|                            | 24 mA                       | 124                                | 169                                |

| 1.8 V LVCMOS               | 2 mA                        | 11                                 | 9                                  |

|                            | 4 mA                        | 22                                 | 17                                 |

|                            | 6 mA                        | 44                                 | 35                                 |

|                            | 8 mA                        | 51                                 | 45                                 |

|                            | 12 mA                       | 74                                 | 91                                 |

|                            | 16 mA                       | 74                                 | 91                                 |

| 1.5 V LVCMOS               | 2 mA                        | 16                                 | 13                                 |

|                            | 4 mA                        | 33                                 | 25                                 |

|                            | 6 mA                        | 39                                 | 32                                 |

|                            | 8 mA                        | 55                                 | 66                                 |

|                            | 12 mA                       | 55                                 | 66                                 |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 109                                | 103                                |

*Note:*  $^{*}T_{J} = 85^{\circ}C.$

## Table 2-31 • I/O Short Currents I<sub>OSH</sub>/I<sub>OSL</sub> Applicable to MSS I/O Banks

|                            | Drive Strength | I <sub>OSL</sub> (mA)* | I <sub>OSH</sub> (mA)* |

|----------------------------|----------------|------------------------|------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 8 mA           | 54                     | 51                     |

| 2.5 V LVCMOS               | 8 mA           | 37                     | 32                     |

| 1.8 V LVCMOS               | 4 mA           | 22                     | 17                     |

| 1.5 V LVCMOS               | 2 mA           | 16                     | 13                     |

*Note:*  $^{*}T_{J} = 85^{\circ}C$

The length of time an I/O can withstand  $I_{OSH}/I_{OSL}$  events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than 2200 operation hours to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

Table 2-32 • Duration of Short Circuit Event before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| –40°C       | > 20 years          |

| 0°C         | > 20 years          |

| 25°C        | > 20 years          |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

# Table 2-33 • Schmitt Trigger Input Hysteresis

## Hysteresis Voltage Value (typical) for Schmitt Mode Input Buffers

| Input Buffer Configuration                                | Hysteresis Value (typical) |

|-----------------------------------------------------------|----------------------------|

| 3.3 V LVTTL / LVCMOS / PCI / PCI-X (Schmitt trigger mode) | 240 mV                     |

| 2.5 V LVCMOS (Schmitt trigger mode)                       | 140 mV                     |

| 1.8 V LVCMOS (Schmitt trigger mode)                       | 80 mV                      |

| 1.5 V LVCMOS (Schmitt trigger mode)                       | 60 mV                      |

## Table 2-34 • I/O Input Rise Time, Fall Time, and Related I/O Reliability

| Input Buffer                  | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.) | Reliability      |

|-------------------------------|-----------------------------|-----------------------------|------------------|

| LVTTL/LVCMOS                  | No requirement              | 10 ns *                     | 20 years (100°C) |

| LVDS/B-LVDS/<br>M-LVDS/LVPECL | No requirement              | 10 ns *                     | 10 years (100°C) |

Note: \*The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi SoC Products Group recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

#### Microsemi 5

SmartFusion DC and Switching Characteristics

# Table 2-52 • 1.8 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to MSS I/O Banks

|                   | pplicable      |                   | Dunks           |                  |                 |                  |                   |                 |                 |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>Zł</sub> |

| 4 mA              | Std.           | 0.22              | 2.77            | 0.09             | 1.09            | 1.64             | 0.22              | 2.82            | 2.7             |

| ength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> |

|-------|-------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|

| A     | Std.  | 0.22              | 2.77            | 0.09             | 1.09            | 1.64             | 0.22              | 2.82            | 2.72            | 2.21            |

|       | –1    | 0.18              | 2.31            | 0.07             | 0.91            | 1.37             | 0.18              | 2.35            | 2.27            | 1.84            |

|       |       |                   |                 |                  |                 |                  |                   |                 |                 |                 |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

Units

ns

ns

t<sub>HZ</sub>

2.25

1.87

# **I/O Register Specifications**

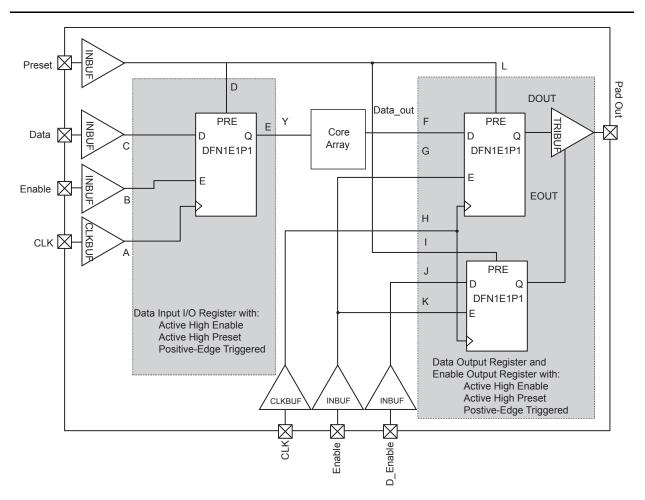

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

Figure 2-14 • Timing Model of Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

# 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

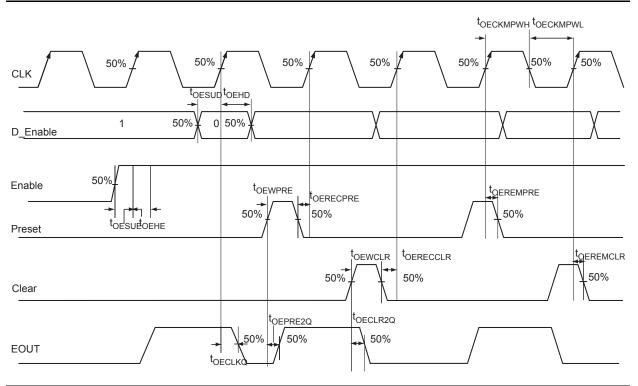

# **Output Enable Register**

Figure 2-18 • Output Enable Register Timing Diagram

# **Timing Characteristics**

Table 2-73 • Output Enable Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.45 | 0.54 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.32 | 0.38 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.53 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.68 | 0.81 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.68 | 0.81 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.23 | 0.27 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.23 | 0.27 | ns    |

| tOEWCLR               | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.22 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.22 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.36 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.32 | 0.32 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# **VersaTile Characteristics**

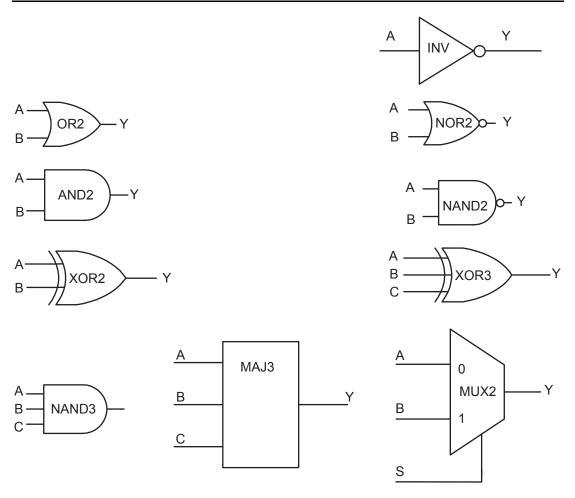

# VersaTile Specifications as a Combinatorial Module

The SmartFusion library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *IGLOO/e, Fusion, ProASIC3/E, and SmartFusion Macro Library Guide*.

Figure 2-23 • Sample of Combinatorial Cells

# **FPGA Fabric SRAM and FIFO Characteristics**

# **FPGA Fabric SRAM**

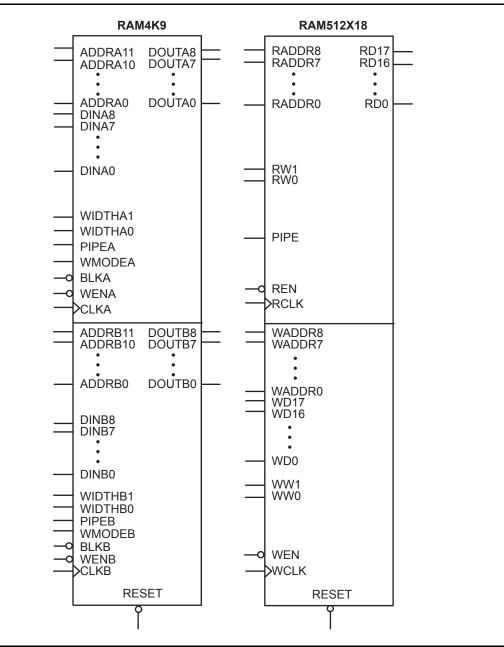

Figure 2-29 • RAM Models

# static Microsemi.

SmartFusion DC and Switching Characteristics

### *Table 2-88* • RAM512X18

| Parameter             | Description                                                                                                        | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.30 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.09 | 0.11 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.06 | 0.07 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.19 | 0.22 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained, WMODE = 0)                                                    | 2.19 | 2.63 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     | 0.91 | 1.09 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—applicable to opening edge | 0.38 | 0.43 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—applicable to opening edge | 0.44 | 0.50 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on RD (flow-through)                                                                     | 0.94 | 1.12 | ns    |

|                       | RESET Low to data out Low on RD (pipelined)                                                                        | 0.94 | 1.12 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.35 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.52 | 1.83 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          | 0.22 | 0.22 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.28 | 3.28 | ns    |

| F <sub>MAX</sub>      | Maximum clock frequency                                                                                            | 305  | 305  | MHz   |

Notes:

1. For more information, refer to the Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs application note.

2. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

| Parameter            | Description           | -1    | Std.  | Units |

|----------------------|-----------------------|-------|-------|-------|

| t <sub>RSTB2Q</sub>  | Reset to Q (data out) | 26.67 | 30.67 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency | 19.00 | 21.85 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time   | 0.00  | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time  | 0.27  | 0.31  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse  | TBD   | TBD   | ns    |

## Table 2-92 • JTAG 1532 Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# **Temperature Monitor**

Unless otherwise noted, temperature monitor performance is specified with a 2N3904 diode-connected bipolar transistor from National Semiconductor or Infineon Technologies, nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 62.5 Ksps. After digital compensation. Unless otherwise noted, the specifications pertain to conditions where the SmartFusion cSoC and the sensing diode are at the same temperature.

| Table 2-94 • Temperature Monitor Performance Specifications |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Specification                                                  | Test Conditions                                                                                         | Min.  | Typical | Max.   | Units  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|---------|--------|--------|

| Input diode temperature range                                  |                                                                                                         | -55   |         | 150    | °C     |

|                                                                |                                                                                                         | 233.2 |         | 378.15 | K      |

| Temperature sensitivity                                        |                                                                                                         |       | 2.5     |        | mV/K   |

| Intercept                                                      | Extrapolated to 0K                                                                                      |       | 0       |        | V      |

| Input referred temperature offset error                        | At 25°C (298.15K)                                                                                       |       | ±1      | 1.5    | °C     |

| Gain error                                                     | Slope of BFSL vs. 2.5 mV/K                                                                              |       | ±1      | 2.5    | % nom. |

| Overall accuracy                                               | Peak error from ideal transfer function                                                                 |       | ±2      | ±3     | °C     |

| Input referred noise                                           | At 25°C (298.15K) – no output averaging                                                                 |       | 4       |        | °C rms |

| Output current                                                 | Idle mode                                                                                               |       | 100     |        | μA     |

|                                                                | Final measurement phases                                                                                |       | 10      |        | μA     |

| Analog settling time                                           | Measured to 0.1% of final value, (with ADC load)                                                        |       |         |        |        |

|                                                                | From TM_STB (High)                                                                                      | 5     |         |        | μs     |

|                                                                | From ADC_START (High)                                                                                   | 5     |         | 105    | μs     |

| AT parasitic capacitance                                       |                                                                                                         |       |         | 500    | pF     |

| Power supply rejection ratio                                   | DC (0–10 KHz)                                                                                           | 1.2   | 0.7     |        | °C/V   |

| Input referred temperature sensitivity error                   | Variation due to device temperature<br>(-40°C to +100°C). External temperature<br>sensor held constant. |       | 0.005   | 0.008  | °C/°C  |

| Temperature monitor (TM)                                       | VCC33A                                                                                                  |       | 200     |        | μA     |

| operational power supply current requirements (per temperature | VCC33AP                                                                                                 |       | 150     |        | μA     |

| monitor instance, not including ADC or VAREFx)                 | VCC15A                                                                                                  |       | 50      |        | μA     |

Note: All results are based on averaging over 64 samples.

# **3 – SmartFusion Development Tools**

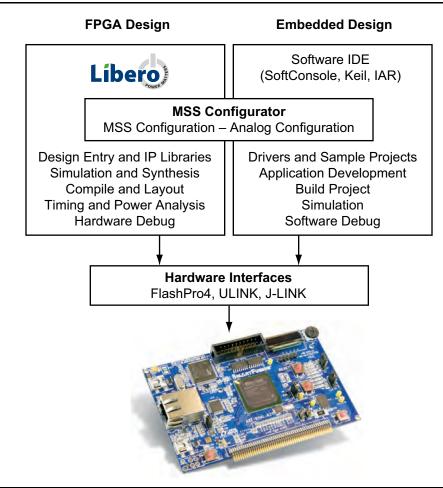

Designing with SmartFusion cSoCs involves three different types of design: FPGA design, embedded design and analog design. These roles can be filled by three different designers, two designers or even a single designer, depending on company structure and project complexity.

# **Types of Design Tools**

Microsemi has developed design tools and flows to meet the needs of these three types of designers so they can work together smoothly on a single project (Figure 3-1).

Figure 3-1 • Three Design Roles

# **FPGA** Design

Libero System-on-Chip (SoC) software is Microsemi's comprehensive software toolset for designing with all Microsemi FPGAs and cSoCs. Libero SoC includes industry-leading synthesis, simulation and debug tools from Synopsys<sup>®</sup> and Mentor Graphics<sup>®</sup>, as well as innovative timing and power optimization and analysis.

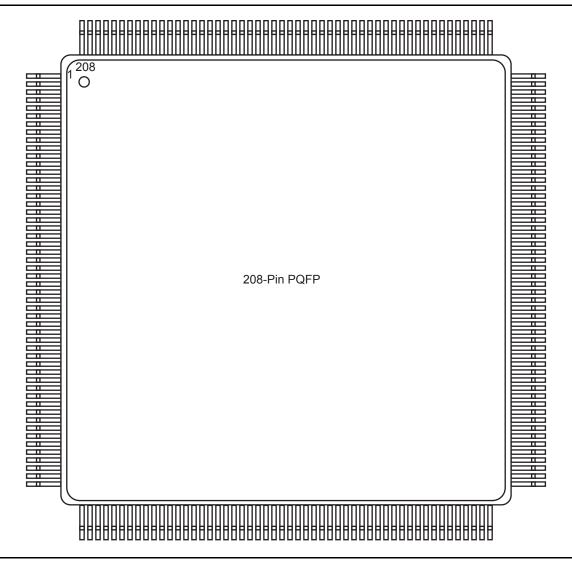

# PQ208

# Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

|            | PQ                    | 208                   |

|------------|-----------------------|-----------------------|

| Pin Number | A2F200                | A2F500                |

| 32         | VCCRCOSC              | VCCRCOSC              |

| 33         | MSS_RESET_N           | MSS_RESET_N           |

| 34         | VCCESRAM              | VCCESRAM              |

| 35         | MAC_MDC/IO48RSB4V0    | MAC_MDC/IO57RSB4V0    |

| 36         | MAC_MDIO/IO49RSB4V0   | MAC_MDIO/IO58RSB4V0   |

| 37         | MAC_TXEN/IO52RSB4V0   | MAC_TXEN/IO61RSB4V0   |

| 38         | MAC_CRSDV/IO51RSB4V0  | MAC_CRSDV/IO60RSB4V0  |

| 39         | MAC_RXER/IO50RSB4V0   | MAC_RXER/IO59RSB4V0   |

| 40         | GND                   | GND                   |

| 41         | VCCMSSIOB4            | VCCMSSIOB4            |

| 42         | VCC                   | VCC                   |

| 43         | MAC_TXD[0]/IO56RSB4V0 | MAC_TXD[0]/IO65RSB4V0 |

| 44         | MAC_TXD[1]/IO55RSB4V0 | MAC_TXD[1]/IO64RSB4V0 |

| 45         | MAC_RXD[0]/IO54RSB4V0 | MAC_RXD[0]/IO63RSB4V0 |

| 46         | MAC_RXD[1]/IO53RSB4V0 | MAC_RXD[1]/IO62RSB4V0 |

| 47         | MAC_CLK               | MAC_CLK               |

| 48         | GNDSDD0               | GNDSDD0               |

| 49         | VCC33SDD0             | VCC33SDD0             |

| 50         | VCC15A                | VCC15A                |

| 51         | PCAP                  | PCAP                  |

| 52         | NCAP                  | NCAP                  |

| 53         | VCC33AP               | VCC33AP               |

| 54         | VCC33N                | VCC33N                |

| 55         | SDD0                  | SDD0                  |

| 56         | GNDA                  | GNDA                  |

| 57         | GNDAQ                 | GNDAQ                 |

| 58         | ABPS0                 | ABPS0                 |

| 59         | ABPS1                 | ABPS1                 |

| 60         | CM0                   | СМО                   |

| 61         | ТМО                   | ТМО                   |

| 62         | GNDTM0                | GNDTM0                |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | PC              | 2208              |

|------------|-----------------|-------------------|

| Pin Number | A2F200          | A2F500            |

| 125        | TMS             | TMS               |

| 126        | TDO             | TDO               |

| 127        | TRSTB           | TRSTB             |

| 128        | VJTAG           | VJTAG             |

| 129        | VDDBAT          | VDDBAT            |

| 130        | VCCLPXTAL       | VCCLPXTAL         |

| 131        | LPXOUT          | LPXOUT            |

| 132        | LPXIN           | LPXIN             |

| 133        | GNDLPXTAL       | GNDLPXTAL         |

| 134        | GNDMAINXTAL     | GNDMAINXTAL       |

| 135        | MAINXOUT        | MAINXOUT          |

| 136        | MAINXIN         | MAINXIN           |

| 137        | VCCMAINXTAL     | VCCMAINXTAL       |

| 138        | GND             | GND               |

| 139        | VCC             | VCC               |

| 140        | VPP             | VPP               |

| 141        | VCCFPGAIOB1     | VCCFPGAIOB1       |

| 142        | GDA0/IO31NDB1V0 | GDA0/IO40NDB1V0   |

| 143        | GDA1/IO31PDB1V0 | GDA1/IO40PDB1V0   |

| 144        | GDC0/IO29NSB1V0 | GDC0/IO38NSB1V0   |

| 145        | GCA0/IO28NDB1V0 | GCA0/IO36NDB1V0 * |

| 146        | GCA1/IO28PDB1V0 | GCA1/IO36PDB1V0 * |

| 147        | VCCFPGAIOB1     | VCCFPGAIOB1       |

| 148        | GND             | GND               |

| 149        | VCC             | VCC               |

| 150        | IO25NDB1V0      | IO30NDB1V0        |

| 151        | GCC2/IO25PDB1V0 | GBC2/IO30PDB1V0   |

| 152        | IO23NDB1V0      | IO28NDB1V0        |

| 153        | GCA2/IO23PDB1V0 | GCA2/IO28PDB1V0 * |

| 154        | GBC2/IO21PSB1V0 | GBB2/IO27NDB1V0   |

| 155        | GBA2/IO20PSB1V0 | GBA2/IO27PDB1V0   |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

FG256 Pin A2F060 Function A2F200 Function A2F500 Function No. GNDQ GNDQ GNDQ B16 C1 EMC DB[14]/IO45NDB5V0 EMC DB[14]/GAB2/IO71NDB5V0 EMC DB[14]/GAB2/IO88NDB5V0 **VCCPLL0** VCCPLL VCCPLL0 C2 EMC BYTEN[0]/GAC0/IO02NDB0V0 EMC BYTEN[0]/GAC0/IO07NDB0V0 C3 EMC BYTEN[0]/IO02NDB0V0 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 C4 EMC CS0 N/GAB0/IO05NDB0V0 C5 EMC CS0 N/IO01NDB0V0 EMC CS0 N/GAB0/IO01NDB0V0 EMC CS1 N/IO01PDB0V0 EMC CS1 N/GAB1/IO01PDB0V0 EMC CS1 N/GAB1/IO05PDB0V0 C6 C7 GND GND GND EMC AB[8]/IO08NDB0V0 EMC AB[8]/IO08NDB0V0 EMC AB[8]/IO13NDB0V0 C8 EMC AB[11]/IO09PDB0V0 EMC AB[11]/IO09PDB0V0 EMC AB[11]/IO11PDB0V0 C9 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 C10 C11 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO17PDB0V0 EMC AB[19]/IO13PDB0V0 C12 EMC AB[19]/IO13PDB0V0 EMC AB[19]/IO18PDB0V0 C13 GND GND GND C14 GCC0/IO18NPB0V0 GBA2/IO20PPB1V0 GBA2/IO27PPB1V0 C15 GCB0/IO19NDB0V0 GCA2/IO23PDB1V0 GCA2/IO28PDB1V0 \* C16 GCB1/IO19PDB0V0 IO23NDB1V0 IO28NDB1V0 D1 VCCFPGAIOB5 VCCFPGAIOB5 VCCFPGAIOB5 D2 VCOMPLA0 **VCOMPLA** VCOMPLA0 GND GND D3 GND D4 GNDQ GNDQ GNDQ D5 EMC CLK/IO00NDB0V0 EMC CLK/GAA0/IO00NDB0V0 EMC CLK/GAA0/IO02NDB0V0 D6 EMC RW N/IO00PDB0V0 EMC RW N/GAA1/IO00PDB0V0 EMC RW N/GAA1/IO02PDB0V0 EMC\_AB[6]/IO07NDB0V0 EMC AB[6]/IO07NDB0V0 EMC AB[6]/IO12NDB0V0 D7 D8 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO12PDB0V0 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO11NDB0V0 D9 D10 EMC AB[22]/IO15NDB0V0 EMC AB[22]/IO15NDB0V0 EMC AB[22]/IO19NDB0V0 EMC AB[23]/IO15PDB0V0 EMC AB[23]/IO15PDB0V0 EMC AB[23]/IO19PDB0V0 D11 D12 GNDQ GNDQ GNDQ GCC1/IO18PPB0V0 GBB2/IO20NPB1V0 GBB2/IO27NPB1V0 D13 D14 GCA0/IO20NDB0V0 GCB2/IO24PDB1V0 GCB2/IO33PDB1V0

Notes:

Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | FG484                     |                           |  |

|------------|---------------------------|---------------------------|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |

| A1         | GND                       | GND                       |  |

| A2         | NC                        | NC                        |  |

| A3         | NC                        | NC                        |  |

| A4         | GND                       | GND                       |  |

| A5         | EMC_CS0_N/GAB0/IO01NDB0V0 | EMC_CS0_N/GAB0/IO05NDB0V0 |  |

| A6         | EMC_CS1_N/GAB1/IO01PDB0V0 | EMC_CS1_N/GAB1/IO05PDB0V0 |  |

| A7         | GND                       | GND                       |  |

| A8         | EMC_AB[0]/IO04NDB0V0      | EMC_AB[0]/IO06NDB0V0      |  |

| A9         | EMC_AB[1]/IO04PDB0V0      | EMC_AB[1]/IO06PDB0V0      |  |

| A10        | GND                       | GND                       |  |

| A11        | NC                        | NC                        |  |

| A12        | EMC_AB[7]/IO07PDB0V0      | EMC_AB[7]/IO12PDB0V0      |  |

| A13        | GND                       | GND                       |  |

| A14        | EMC_AB[12]/IO10NDB0V0     | EMC_AB[12]/IO14NDB0V0     |  |

| A15        | EMC_AB[13]/IO10PDB0V0     | EMC_AB[13]/IO14PDB0V0     |  |

| A16        | GND                       | GND                       |  |

| A17        | NC                        | IO16NDB0V0                |  |

| A18        | NC                        | IO16PDB0V0                |  |

| A19        | GND                       | GND                       |  |

| A20        | NC                        | NC                        |  |

| A21        | NC                        | NC                        |  |

| A22        | GND                       | GND                       |  |

| AA1        | GPIO_4/IO43RSB4V0         | GPIO_4/IO52RSB4V0         |  |

| AA2        | GPIO_12/IO37RSB4V0        | GPIO_12/IO46RSB4V0        |  |

| AA3        | MAC_MDC/IO48RSB4V0        | MAC_MDC/IO57RSB4V0        |  |

| AA4        | MAC_RXER/IO50RSB4V0       | MAC_RXER/IO59RSB4V0       |  |

| AA5        | MAC_TXD[0]/IO56RSB4V0     | MAC_TXD[0]/IO65RSB4V0     |  |

| AA6        | ABPS0                     | ABPS0                     |  |

| AA7        | TM1                       | TM1                       |  |

| AA8        | ADC1                      | ADC1                      |  |

| AA9        | GND15ADC1                 | GND15ADC1                 |  |

| AA10       | GND33ADC1                 | GND33ADC1                 |  |

| AA11       | CM3                       | СМЗ                       |  |

| AA12       | GNDTM1                    | GNDTM1                    |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

Datasheet Information

| Revision                      | Changes                                                                                                                                                                                                                                      | Page          |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 10<br>(January 2013) | The "SmartFusion cSoC Family Product Table" section has been updated to specify that External Memory Controller support for A2F060-TQ144 is not available (SAR 41555).                                                                       | Ш             |

|                               | The following Note was added to the "Package I/Os: MSS + FPGA I/Os" table (SAR 41027): "There are no LVTTL capable direct inputs available on A2F060 devices."                                                                               | III           |

|                               | The "Product Ordering Codes" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43218).                    | VI            |

|                               | Added a note to Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> (SAR 43428): The programming temperature range supported is $T_{ambient} = 0^{\circ}C$ to 85°C.                                                                  | 2-3           |

|                               | Statements about the state of the I/Os during programming were updated in the following sections: "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" and "User I/O Naming Conventions" (SAR 43380). | 2-4, 5-7      |

|                               | In Table 2-4 • FPGA and Embedded Flash Programming, Storage and Operating Limits, the upper value of temperature ranges was corrected from "Min." to "Max." (SAR 41826).                                                                     | 2-4           |

|                               | Information for A2F200M3F-CS288 was added to Table 2-6 • Package Thermal Resistance. The die size column was removed (SARs 41828, 42168).<br>Also added details for A2F200M3F-PQG208I (SAR 35728).                                           | 2-7           |

|                               | Added the following note to Table 2-65 • LVDS and Table 2-68 • LVPECL: "The above mentioned timing parameters correspond to 24mA drive strength." (SAR 43457)                                                                                | 2-41,<br>2-43 |

|                               | The note in Table 2-86 • SmartFusion CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 34816).                                                            | 2-63          |

|                               | The SRAM collision data in Table 2-87 • RAM4K9 and Table 2-88 • RAM512X18 was updated (SAR 38583).                                                                                                                                           | 2-69,2-70     |

|                               | The maximum input bias current for comparators 1, 3, 5, 7, and 9, in Table 2-97 • Comparator Performance Specifications, was revised from 60 to 100 nA (SAR 36008).                                                                          | 2-84          |

Datasheet Information

| Revision | Changes                                                                                                                                                                                                   | Page                  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|          | The A2F060 device was added to product information tables.                                                                                                                                                | N/A                   |

|          | The "Product Ordering Codes" table was updated to removed Std. speed and add speed grade 1. Pre-production was removed from the application ordering code category.                                       | VI                    |

|          | The "SmartFusion cSoC Block Diagram" was revised.                                                                                                                                                         | IV                    |

|          | The "Datasheet Categories" section was updated, referencing the "SmartFusion cSoC Block Diagram" table, which is new.                                                                                     | 1-4, IV               |

|          | The "VCCI" parameter was renamed to "VCCxxxxIOBx."<br>"Advanced I/Os" were renamed to "FPGA I/Os."                                                                                                        | N/A                   |

|          | Generic pin names that represent multiple pins were standardized with a lower case x as a placeholder. For example, VAREFx designates VAREF0, VAREF1, and VAREF2. Modes were renamed as follows:          |                       |

|          | Operating mode was renamed to SoC mode.                                                                                                                                                                   |                       |

|          | 32KHz Active mode was renamed to Standby mode.                                                                                                                                                            |                       |

|          | Battery mode was renamed to Time Keeping mode.                                                                                                                                                            |                       |

|          | Table entries have been filled with values as data has become available.                                                                                                                                  |                       |

|          | Table 2-1 • Absolute Maximum Ratings, Table 2-2 • Analog Maximum Ratings, and Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> were revised extensively.                                       | 2-1<br>through<br>2-3 |

|          | Device names were updated in Table 2-6 • Package Thermal Resistance.                                                                                                                                      | 2-7                   |

|          | Table 2-8 • Power Supplies Configuration was revised extensively.                                                                                                                                         | 2-10                  |

|          | Table 2-11 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings was revised extensively.                                                                                         | 2-11                  |

|          | Removed "Example of Power Calculation."                                                                                                                                                                   | N/A                   |

|          | Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs was revised extensively.                                                                                 | 2-12                  |

|          | Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs was revised extensively.                                                                              | 2-13                  |

|          | The "Power Calculation Methodology" section was revised.                                                                                                                                                  | 2-14                  |

|          | Table 2-83 • Electrical Characteristics of the RC Oscillator was revised extensively.                                                                                                                     | 2-61                  |

|          | Table 2-85 • Electrical Characteristics of the Low Power Oscillator was revised extensively.                                                                                                              | 2-62                  |

|          | The parameter t <sub>RSTBQ</sub> was changed to T <sub>C2CWRH</sub> in Table 2-87 • RAM4K9.                                                                                                               | 2-69                  |

|          | The 12-bit mode row for integral non-linearity was removed from Table 2-95 • ADC Specifications. The typical value for 10-bit mode was revised. The table note was punctuated correctly to make it clear. | 2-81                  |

|          | Figure 37-34 • Write Access after Write onto Same Address, Figure 37-34 • Read Access after Write onto Same Address, and Figure 37-34 • Write Access after Read onto Same Address were deleted.           | N/A                   |

|          | Table 2-99 • Voltage Regulator was revised extensively.                                                                                                                                                   | 2-87                  |

|          | The "Serial Peripheral Interface (SPI) Characteristics" section and "Inter-Integrated Circuit ( $I^2C$ ) Characteristics" section are new.                                                                | 2-89,<br>2-91         |