Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

-XF

| Product Status          | Active                                                                      |

|-------------------------|-----------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                             |

| Flash Size              | 256KB                                                                       |

| RAM Size                | 64KB                                                                        |

| Peripherals             | DMA, POR, WDT                                                               |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                        |

| Speed                   | 80MHz                                                                       |

| Primary Attributes      | ProASIC®3 FPGA, 200K Gates, 4608 D-Flip-Flops                               |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                          |

| Package / Case          | 256-LBGA                                                                    |

| Supplier Device Package | 256-FPBGA (17x17)                                                           |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f200m3f-fgg256i |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

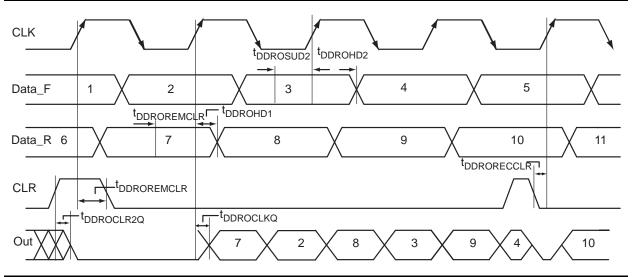

SmartFusion DC and Switching Characteristics

## **Timing Characteristics**

# Table 2-77 • Output DDR Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                           | -1   | Units |

|-------------------------|-------------------------------------------------------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.71 | ns    |

| t <sub>DDROSUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.38 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.38 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.81 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.23 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.22 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width High for the Output DDR     | 0.36 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output DDR      | 0.32 | ns    |

| F <sub>DDOMAX</sub>     | Maximum Frequency for the Output DDR                  | 350  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

SmartFusion Customizable System-on-Chip (cSoC)

| M11         M12         M13       S         M14       M15         M15       SF         M16       S         N1       GF         N2       S         N3       S         N4       S         N5       S         N6       S         N7       S         N8       S         N9       S         N10       S         N11       S         N12       S         N13       S         N14       S | A2F060 Function<br>ADC6<br>ADC5<br>SPI_0_SS/GPIO_19<br>VCCMSSIOB2<br>PI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>PIO_8/IO25RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0<br>CNDAO                                   | A2F200 FunctionTM2CM2SPI_0_SS/GPIO_19VCCMSSIOB2SPI_0_CLK/GPIO_18SPI_0_DI/GPIO_17MAC_RXD[1]/IO53RSB4V0VCCMSSIOB4VCC15AVCC33APABPS3TM1GND33ADC0VCC33ADC1ADC5CM3                                | A2F500 Function<br>TM2<br>CM2<br>SPI_0_SS/GPIO_19<br>VCCMSSIOB2<br>SPI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>MAC_RXD[1]/IO62RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M12         M12         M13       S         M14       M15         M15       SF         M16       S         N1       GF         N2       M14         N3       M14         N5       M16         N7       M18         N9       M10         N11       M12         N13       M14         N15       M14         N16       S                                                              | ADC5         SPI_0_SS/GPIO_19         VCCMSSIOB2         PI_0_CLK/GPIO_18         SPI_0_DI/GPIO_17         PIO_8/IO25RSB4V0         VCCMSSIOB4         VCC15A         VCC33AP         NC         ADC4         NC         VCC33ADC0         ADC8         CM0 | CM2<br>SPI_0_SS/GPIO_19<br>VCCMSSIOB2<br>SPI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>MAC_RXD[1]/IO53RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5 | CM2<br>SPI_0_SS/GPIO_19<br>VCCMSSIOB2<br>SPI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>MAC_RXD[1]/IO62RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                           |

| M13       S         M14       M15         M15       SF         M16       S         N1       GF         N2       M16         N2       M17         N3       M14         N5       M16         N7       M17         N8       M10         N11       M12         N13       M14         N15       M16         N16       S                                                                 | SPI_0_SS/GPIO_19         VCCMSSIOB2         PI_0_CLK/GPIO_18         SPI_0_DI/GPIO_17         PIO_8/I025RSB4V0         VCCMSSIOB4         VCC15A         VCC33AP         NC         ADC4         NC         VCC33ADC0         ADC8         CM0              | SPI_0_SS/GPIO_19VCCMSSIOB2SPI_0_CLK/GPIO_18SPI_0_DI/GPIO_17MAC_RXD[1]/IO53RSB4V0VCCMSSIOB4VCC15AVCC33APABPS3TM1GND33ADC0VCC33ADC1ADC5                                                        | SPI_0_SS/GPIO_19<br>VCCMSSIOB2<br>SPI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>MAC_RXD[1]/IO62RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                  |

| M14         M15       SF         M16       S         N1       GF         N2       N3         N4       N5         N6       N7         N8       N9         N10       N11         N12       N13         N14       S         N15       S         N16       S                                                                                                                           | VCCMSSIOB2<br>PI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>PIO_8/IO25RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                   | VCCMSSIOB2SPI_0_CLK/GPIO_18SPI_0_DI/GPIO_17MAC_RXD[1]/IO53RSB4V0VCCMSSIOB4VCC15AVCC33APABPS3TM1GND33ADC0VCC33ADC1ADC5                                                                        | VCCMSSIOB2<br>SPI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>MAC_RXD[1]/IO62RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                      |

| M15         SI           M16         S           N1         GI           N2         N           N3         N           N4         N           N5         N           N6         N           N7         N           N8         N           N10         N11           N12         N13           N13         N14           N15         S           N16         S                      | PI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>PIO_8/IO25RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                 | SPI_0_CLK/GPIO_18SPI_0_DI/GPIO_17MAC_RXD[1]/IO53RSB4V0VCCMSSIOB4VCC15AVCC33APABPS3TM1GND33ADC0VCC33ADC1ADC5                                                                                  | SPI_0_CLK/GPIO_18<br>SPI_0_DI/GPIO_17<br>MAC_RXD[1]/IO62RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                    |

| M16       S         N1       GF         N2       N         N3       N         N4       N         N5       N         N6       N         N7       N         N8       N         N10       N11         N12       N13         N14       N15         N16       S                                                                                                                         | SPI_0_DI/GPIO_17<br>PIO_8/IO25RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                     | SPI_0_DI/GPIO_17MAC_RXD[1]/IO53RSB4V0VCCMSSIOB4VCC15AVCC33APABPS3TM1GND33ADC0VCC33ADC1ADC5                                                                                                   | SPI_0_DI/GPIO_17<br>MAC_RXD[1]/IO62RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                         |

| N1         GF           N2                                                                                                                                                                                                                                                                                                                                                         | PIO_8/IO25RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                         | MAC_RXD[1]/IO53RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                   | MAC_RXD[1]/IO62RSB4V0<br>VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                             |

| N2         N3         N4         N5         N6         N7         N8         N9         N10         N11         N12         N13         N14         N15         N16         S                                                                                                                                                                                                      | VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                                             | VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                            | VCCMSSIOB4<br>VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                      |

| N3         N4         N5         N6         N7         N8         N9         N10         N11         N12         N13         N14         N15         N16                                                                                                                                                                                                                           | VCC15A<br>VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                                                           | VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                          | VCC15A<br>VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                                    |

| N4         N5         N6         N7         N8         N9         N10         N11         N12         N13         N14         N16         S                                                                                                                                                                                                                                        | VCC33AP<br>NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                                                                     | VCC33APABPS3TM1GND33ADC0VCC33ADC1ADC5                                                                                                                                                        | VCC33AP<br>ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                                              |

| N5           N6           N7           N8           N9           N10           N11           N12           N13           N14           N16           S                                                                                                                                                                                                                             | NC<br>ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                                                                                | ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                               | ABPS3<br>TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                                                         |

| N6           N7           N8           N9           N10           N11           N12           N13           N14           N15           N16         S                                                                                                                                                                                                                              | ADC4<br>NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                                                                                      | TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                                        | TM1<br>GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                                                                  |

| N7           N8           N9           N10           N11           N12           N13           N14           N15           N16         S                                                                                                                                                                                                                                           | NC<br>VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                                                                                              | GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                                               | GND33ADC0<br>VCC33ADC1<br>ADC5                                                                                                                                                                                         |

| N8           N9           N10           N11           N12           N13           N14           N15           N16         S                                                                                                                                                                                                                                                        | VCC33ADC0<br>ADC8<br>CM0                                                                                                                                                                                                                                    | VCC33ADC1<br>ADC5                                                                                                                                                                            | VCC33ADC1<br>ADC5                                                                                                                                                                                                      |

| N9           N10           N11           N12           N13           N14           N15           N16         S                                                                                                                                                                                                                                                                     | ADC8<br>CM0                                                                                                                                                                                                                                                 | ADC5                                                                                                                                                                                         | ADC5                                                                                                                                                                                                                   |

| N10           N11           N12           N13           N14           N15           N16                                                                                                                                                                                                                                                                                            | CM0                                                                                                                                                                                                                                                         |                                                                                                                                                                                              |                                                                                                                                                                                                                        |

| N11           N12           N13           N14           N15           N16                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                             | CM3                                                                                                                                                                                          |                                                                                                                                                                                                                        |

| N12           N13           N14           N15           N16                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                             |                                                                                                                                                                                              | CM3                                                                                                                                                                                                                    |

| N13<br>N14<br>N15<br>N16 S                                                                                                                                                                                                                                                                                                                                                         | GNDAQ                                                                                                                                                                                                                                                       | GNDAQ                                                                                                                                                                                        | GNDAQ                                                                                                                                                                                                                  |

| N14<br>N15<br>N16 S                                                                                                                                                                                                                                                                                                                                                                | VAREFOUT                                                                                                                                                                                                                                                    | VAREFOUT                                                                                                                                                                                     | VAREFOUT                                                                                                                                                                                                               |

| N15<br>N16 S                                                                                                                                                                                                                                                                                                                                                                       | NC                                                                                                                                                                                                                                                          | GNDSDD1                                                                                                                                                                                      | GNDSDD1                                                                                                                                                                                                                |

| N16 S                                                                                                                                                                                                                                                                                                                                                                              | NC                                                                                                                                                                                                                                                          | VCC33SDD1                                                                                                                                                                                    | VCC33SDD1                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                    | GND                                                                                                                                                                                                                                                         | GND                                                                                                                                                                                          | GND                                                                                                                                                                                                                    |

| P1                                                                                                                                                                                                                                                                                                                                                                                 | PI_0_DO/GPIO_16                                                                                                                                                                                                                                             | SPI_0_DO/GPIO_16                                                                                                                                                                             | SPI_0_DO/GPIO_16                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                    | GNDSDD0                                                                                                                                                                                                                                                     | GNDSDD0                                                                                                                                                                                      | GNDSDD0                                                                                                                                                                                                                |

| P2                                                                                                                                                                                                                                                                                                                                                                                 | VCC33SDD0                                                                                                                                                                                                                                                   | VCC33SDD0                                                                                                                                                                                    | VCC33SDD0                                                                                                                                                                                                              |

| P3                                                                                                                                                                                                                                                                                                                                                                                 | VCC33N                                                                                                                                                                                                                                                      | VCC33N                                                                                                                                                                                       | VCC33N                                                                                                                                                                                                                 |

| P4                                                                                                                                                                                                                                                                                                                                                                                 | GNDA                                                                                                                                                                                                                                                        | GNDA                                                                                                                                                                                         | GNDA                                                                                                                                                                                                                   |

| P5                                                                                                                                                                                                                                                                                                                                                                                 | GNDAQ                                                                                                                                                                                                                                                       | GNDAQ                                                                                                                                                                                        | GNDAQ                                                                                                                                                                                                                  |

| P6                                                                                                                                                                                                                                                                                                                                                                                 | NC                                                                                                                                                                                                                                                          | CM1                                                                                                                                                                                          | CM1                                                                                                                                                                                                                    |

| P7                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                             | ADC2                                                                                                                                                                                         | ADC2                                                                                                                                                                                                                   |

| P8                                                                                                                                                                                                                                                                                                                                                                                 | NC                                                                                                                                                                                                                                                          |                                                                                                                                                                                              | VCC15ADC0                                                                                                                                                                                                              |

| P9                                                                                                                                                                                                                                                                                                                                                                                 | NC<br>NC                                                                                                                                                                                                                                                    | VCC15ADC0                                                                                                                                                                                    | VOOTSADOO                                                                                                                                                                                                              |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                   | Changes                                                                                                                                                                                                                                                             | Page                   |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Revision 7                 | Usage instructions, such as how to handle the pin when unused, were added for the                                                                                                                                                                                   | 5-2                    |

| (continued)                | following supply pins (SAR 29769):<br>"VCC15A"                                                                                                                                                                                                                      | through                |

|                            |                                                                                                                                                                                                                                                                     | 5-3                    |

|                            | "VCC15ADC0" through "VCC15ADC2"                                                                                                                                                                                                                                     |                        |

|                            | "VCC33ADC0" through "VCC33ADC2"<br>"VCC33AP"                                                                                                                                                                                                                        |                        |

|                            |                                                                                                                                                                                                                                                                     |                        |

|                            | "VCC33ADC2"<br>"VCCLPXTAL"<br>"VCCMAINXTAL"                                                                                                                                                                                                                         |                        |

|                            |                                                                                                                                                                                                                                                                     |                        |

|                            |                                                                                                                                                                                                                                                                     |                        |

|                            |                                                                                                                                                                                                                                                                     |                        |

|                            |                                                                                                                                                                                                                                                                     |                        |

|                            |                                                                                                                                                                                                                                                                     |                        |

|                            | "VDDBAT"                                                                                                                                                                                                                                                            |                        |

|                            | The "IO" description was revised to clarify the definitions of u, I/O pair, and w, differential pair (SAR 31147). Information on configuration of unused I/Os (including unused MSS I/Os, SAR 26891) was added (SAR 32643).                                         | 5-6                    |

|                            | Usage instructions were added for the following pins (SAR 29769):                                                                                                                                                                                                   | 5-9                    |

|                            | "MSS_RESET_N"                                                                                                                                                                                                                                                       | through                |

|                            | "TCK"                                                                                                                                                                                                                                                               | 5-13                   |

|                            | "TMS"                                                                                                                                                                                                                                                               |                        |

|                            | "TRSTB"                                                                                                                                                                                                                                                             |                        |

|                            | "MAC_CLK"                                                                                                                                                                                                                                                           |                        |

|                            | Package names used in the "Pin Assignment Tables" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 27395).                                                                                                                  | 5-18                   |

|                            | The pin assignments for A2F060 for "TQ144" and "FG256" have been revised due to the device status change from advance to preliminary (SAR 33068).                                                                                                                   | 5-18,<br>5-42          |

|                            | The "TQ144" and "FG256" pin assignment sections previously compared functions between A2F060/A2F200 devices in one table and A2F200/A2F500 in a separate table. Functions for all three devices have now been combined into one table for each package (SAR 33072). |                        |

|                            | The "PQ208" pin table was revised for A2F500 to remove EMC functions, which are not available for this device/package combination (SAR 33041).                                                                                                                      | 5-34                   |

| Revision 6<br>(March 2011) | The "PQ208" package was added to product tables and "Product Ordering Codes" for A2F200 and A2F500 (SAR 31005).                                                                                                                                                     | 111                    |

|                            | The "Package I/Os: MSS + FPGA I/Os" table was revised to add the CS288 package for A2F060 and the PQ208 package for A2F200 and A2F500. A row was added for shared analog inputs (SAR 31034).                                                                        | Ш                      |

|                            | The "SmartFusion cSoC Device Status" table was updated (SAR 31084).                                                                                                                                                                                                 | Ш                      |

|                            | VCCESRAM was added to Table 2-1 • Absolute Maximum Ratings, Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , Table 2-8 • Power Supplies Configuration, and the "Supply Pins" table (SAR 31035).                                                        | 2-1, 2-3,<br>2-10, 5-1 |

|                            | The following note was removed from Table 2-8 • Power Supplies Configuration (SAR 30984):                                                                                                                                                                           | 2-10                   |

|                            | "Current monitors and temperature monitors should not be used when Power-Down and/or Sleep mode are required by the application."                                                                                                                                   |                        |

Datasheet Information

| Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Changes                                                                                                                                                                                                                                                                                                                                                                                                | Page          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 6<br>(continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Dynamic power values were updated in the following tables. The table subtitles changed where FPGA I/O banks were involved to note "I/O assigned to EMC I/O pins" (SAR 30987).                                                                                                                                                                                                                          | 2-10          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 2-10 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings                                                                                                                                                                                                                                                                                                               | 2-11          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Table 2-13 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings.                                                                                                                                                                                                                                                                                                             |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The "Timing Model" was updated (SAR 30986).                                                                                                                                                                                                                                                                                                                                                            | 2-19          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Values in the timing tables for the following sections were updated. Table subtitles were updated for FPGA I/O banks to note "I/O assigned to EMC I/O pins" (SAR 30986).                                                                                                                                                                                                                               |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "Overview of I/O Performance" section: Table 2-24, Table 2-25                                                                                                                                                                                                                                                                                                                                          | 2-23          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "Detailed I/O DC Characteristics" section: Table 2-38, Table 2-39, Table 2-40, Table 2-44, Table 2-45, Table 2-46, Table 2-50, Table 2-51, Table 2-52, Table 2-56, Table 2-57, Table 2-58, Table 2-61, Table 2-62                                                                                                                                                                                      | 2-26          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "LVDS" section: Table 2-65                                                                                                                                                                                                                                                                                                                                                                             | 2-40          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "LVPECL" section: Table 2-68                                                                                                                                                                                                                                                                                                                                                                           | 2-42          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "Global Tree Timing Characteristics" section: Table 2-80, Table 2-81                                                                                                                                                                                                                                                                                                                                   | 2-59          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The "PQ208" section and pin tables are new (SAR 31005).                                                                                                                                                                                                                                                                                                                                                | 5-34          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Global clocks were removed from the A2F060 pin table for the "CS288" and "FG256" packages, resulting in changed function names for affected pins (SAR 31033).                                                                                                                                                                                                                                          | 5-43          |

| Revision 5<br>(December 2010)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 2-2 • Analog Maximum Ratings was revised. The recommended CM[n] pad voltage (relative to ground) was changed from -11 to -0.3 (SAR 28219).                                                                                                                                                                                                                                                       | 2-2           |

| <ul> <li>to change the values for 100°C.</li> <li>Power-down and Sleep modes, and all associated note<br/>Table 2-8 • Power Supplies Configuration (SAR 29479),<br/>renamed to IDC1 and IDC2 (SAR 29478). These modes are<br/>note was added to the table stating that current monitors a<br/>should not be used when Power-down and/or Sleep mod<br/>application.</li> <li>The "Power-Down and Sleep Mode Implementation" sec<br/>29479).</li> <li>Values for PAC9 and PAC10 for LVDS and LVPECL were<br/>Summary of I/O Input Buffer Power (per pin) – Default I/O<br/>Table 2-12 • Summary of I/O Output Buffer Power (per pin<br/>Settings*.</li> <li>Values for PAC1 through PAC4, PDC1, and PDC2 wer<br/>Table 2-14 • Different Components Contributing to Dynamic<br/>SmartFusion cSoCs and Table 2-15 • Different Components<br/>Power Consumption in SmartFusion cSoCs</li> <li>The equation for "Total Dynamic Power Consumption—P<sub>D</sub><br/>revised to add P<sub>MSS</sub>. The "Microcontroller Subsystem Dyna<br/>section is new (SAR 29462).</li> <li>Information in Table 2-24 • Summary of I/O Timing Character<br/>Settings (applicable to FPGA I/O banks) and Table 2-25 •</li> </ul> | Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays was revised to change the values for 100°C.                                                                                                                                                                                                                                                                                     | 2-9           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power-down and Sleep modes, and all associated notes, were removed from Table 2-8 • Power Supplies Configuration (SAR 29479). IDC3 and IDC4 were renamed to IDC1 and IDC2 (SAR 29478). These modes are no longer supported. A note was added to the table stating that current monitors and temperature monitors should not be used when Power-down and/or Sleep mode are required by the application. | 2-10          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The "Power-Down and Sleep Mode Implementation" section was deleted (SAR 29479).                                                                                                                                                                                                                                                                                                                        | N/A           |