Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Active                                                                      |

|-------------------------|-----------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                             |

| Flash Size              | 256KB                                                                       |

| RAM Size                | 64KB                                                                        |

| Peripherals             | DMA, POR, WDT                                                               |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                        |

| Speed                   | 80MHz                                                                       |

| Primary Attributes      | ProASIC®3 FPGA, 200K Gates, 4608 D-Flip-Flops                               |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                          |

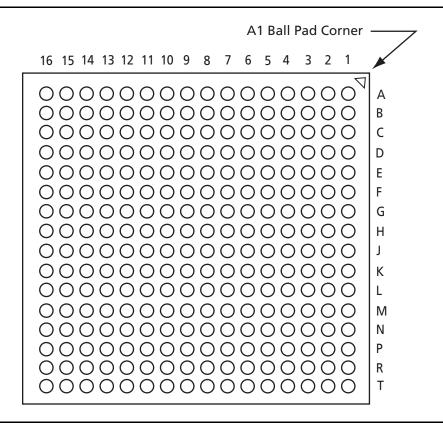

| Package / Case          | 484-BGA                                                                     |

| Supplier Device Package | 484-FPBGA (23x23)                                                           |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f200m3f-fgg484i |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table of Contents

| Datasheet Categories                                                                                 |

|------------------------------------------------------------------------------------------------------|

| Microsemi SoC Products Group Safety Critical, Life Support, and High-Reliability Applications Policy |

SmartFusion Customizable System-on-Chip (cSoC)

$$P = \frac{T_J - T_A}{\theta_{JA}} = \frac{100^{\circ}C - 70^{\circ}C}{17.00 \text{ W}} = 1.76 \text{ W}$$

EQ 6

The 1.76 W power is less than the required 3.00 W. The design therefore requires a heat sink, or the airflow where the device is mounted should be increased. The design's total junction-to-air thermal resistance requirement can be estimated by EQ 7:

$$\theta_{JA(total)} = \frac{T_J - T_A}{P} = \frac{100^{\circ}C - 70^{\circ}C}{3.00 \text{ W}} = 10.00^{\circ}\text{C/W}$$

EQ 7

Determining the heat sink's thermal performance proceeds as follows:

$$\theta_{JA(TOTAL)} = \theta_{JC} + \theta_{CS} + \theta_{SA}$$

EQ 8

where

$$\theta_{JA} = 0.37^{\circ}C/W$$

Thermal resistance of the interface material between the case and the heat sink, usually provided by the thermal interface manufacturer

$\theta_{SA}$  = Thermal resistance of the heat sink in °C/W

$\theta_{\text{SA}}$

$$\theta_{SA} = \theta_{JA(TOTAL)} - \theta_{JC} - \theta_{CS}$$

$$EQ 9$$

$$= 13.33^{\circ}C/W - 8.28^{\circ}C/W - 0.37^{\circ}C/W = 5.01^{\circ}C/W$$

A heat sink with a thermal resistance of 5.01°C/W or better should be used. Thermal resistance of heat sinks is a function of airflow. The heat sink performance can be significantly improved with increased airflow.

Carefully estimating thermal resistance is important in the long-term reliability of an FPGA. Design engineers should always correlate the power consumption of the device with the maximum allowable power dissipation of the package selected for that device.

Note: The junction-to-air and junction-to-board thermal resistances are based on JEDEC standard (JESD-51) and assumptions made in building the model. It may not be realized in actual application and therefore should be used with a degree of caution. Junction-to-case thermal resistance assumes that all power is dissipated through the case.

#### **Temperature and Voltage Derating Factors**

Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays<br/>(normalized to T<sub>J</sub> = 85°C, worst-case VCC = 1.425 V)

| Array              | Junction Temperature (°C) |      |      |      |      |       |  |  |  |  |

|--------------------|---------------------------|------|------|------|------|-------|--|--|--|--|

| Voltage VCC<br>(V) | –40°C                     | 0°C  | 25°C | 70°C | 85°C | 100°C |  |  |  |  |

| 1.425              | 0.86                      | 0.91 | 0.93 | 0.98 | 1.00 | 1.02  |  |  |  |  |

| 1.500              | 0.81                      | 0.86 | 0.88 | 0.93 | 0.95 | 0.96  |  |  |  |  |

| 1.575              | 0.78                      | 0.83 | 0.85 | 0.90 | 0.91 | 0.93  |  |  |  |  |

Microsemi

1

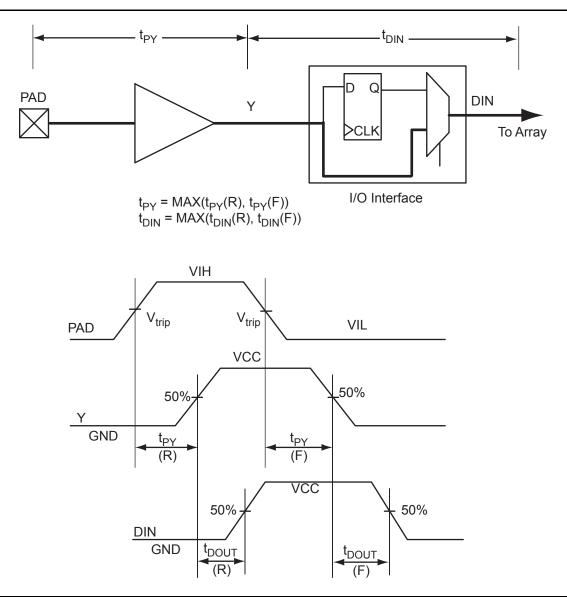

Figure 2-3 • Input Buffer Timing Model and Delays (example)

### **Detailed I/O DC Characteristics**

#### Table 2-26 • Input Capacitance

| Symbol          | Definition                         | Conditions                       | Min. | Max. | Units |

|-----------------|------------------------------------|----------------------------------|------|------|-------|

| C <sub>IN</sub> | Input capacitance                  | V <sub>IN</sub> = 0, f = 1.0 MHz |      | 8    | pF    |

| CINCLK          | Input capacitance on the clock pin | V <sub>IN</sub> = 0, f = 1.0 MHz |      | 8    | pF    |

#### Table 2-27 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to FPGA I/O Banks

| Standard                   | Drive Strength              | $R_{PULL-DOWN}$ $(\Omega)^2$ | ${\sf R}_{\sf PULL-UP} \ (\Omega)^3$ |

|----------------------------|-----------------------------|------------------------------|--------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 100                          | 300                                  |

|                            | 4 mA                        | 100                          | 300                                  |

|                            | 6 mA                        | 50                           | 150                                  |

|                            | 8 mA                        | 50                           | 150                                  |

|                            | 12 mA                       | 25                           | 75                                   |

|                            | 16 mA                       | 17                           | 50                                   |

|                            | 24 mA                       | 11                           | 33                                   |

| 2.5 V LVCMOS               | 2 mA                        | 100                          | 200                                  |

|                            | 4 mA                        | 100                          | 200                                  |

|                            | 6 mA                        | 50                           | 100                                  |

|                            | 8 mA                        | 50                           | 100                                  |

|                            | 12 mA                       | 25                           | 50                                   |

|                            | 16 mA                       | 20                           | 40                                   |

|                            | 24 mA                       | 11                           | 22                                   |

| 1.8 V LVCMOS               | 2 mA                        | 200                          | 225                                  |

|                            | 4 mA                        | 100                          | 112                                  |

|                            | 6 mA                        | 50                           | 56                                   |

|                            | 8 mA                        | 50                           | 56                                   |

|                            | 12 mA                       | 20                           | 22                                   |

|                            | 16 mA                       | 20                           | 22                                   |

| 1.5 V LVCMOS               | 2 mA                        | 200                          | 224                                  |

|                            | 4 mA                        | 100                          | 112                                  |

|                            | 6 mA                        | 67                           | 75                                   |

|                            | 8 mA                        | 33                           | 37                                   |

|                            | 12 mA                       | 33                           | 37                                   |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 25                           | 75                                   |

Notes:

1. These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website (also generated by the SoC Products Group Libero SoC toolset).

2. R<sub>(PULL-DOWN-MAX)</sub> = (V<sub>OLspec</sub>) / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (V<sub>CCImax</sub> - V<sub>OHspec</sub>) / I<sub>OHspec</sub>

#### Table 2-28 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to MSS I/O Banks

| Standard                   | Drive Strength | $R_{PULL	ext{-}DOWN} \ (\Omega)^2$ | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|----------------------------|----------------|------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 8mA            | 50                                 | 150                                      |

| 2.5 V LVCMOS               | 8 mA           | 50                                 | 100                                      |

| 1.8 V LVCMOS               | 4 mA           | 100                                | 112                                      |

| 1.5 V LVCMOS               | 2 mA           | 200                                | 224                                      |

Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website.

- 2. R<sub>(PULL-DOWN-MAX)</sub> = (V<sub>OLspec</sub>) / I<sub>OLspec</sub>

- 3. R<sub>(PULL-UP-MAX)</sub> = (V<sub>CCImax</sub> V<sub>OHspec</sub>) / I<sub>OHspec</sub>

# Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|             | R <sub>(WEAK P</sub><br>(Ω | PULL-UP) <sup>1</sup><br>2) | R <sub>(WEAK PULL-DOWN)</sub> <sup>2</sup><br>(Ω) |       |  |

|-------------|----------------------------|-----------------------------|---------------------------------------------------|-------|--|

| VCCxxxxlOBx | Min.                       | Max.                        | Min.                                              | Max.  |  |

| 3.3 V       | 10 k                       | 45 k                        | 10 k                                              | 45 k  |  |

| 2.5 V       | 11 k                       | 55 k                        | 12 k                                              | 74 k  |  |

| 1.8 V       | 18 k                       | 70 k                        | 17 k                                              | 110 k |  |

| 1.5 V       | 19 k                       | 90 k                        | 19 k                                              | 140 k |  |

Notes:

1. R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

2. R<sub>(WEAK PULL-DOWN-MAX)</sub> = (VOLspec) / I<sub>(WEAK PULL-DOWN-MIN)</sub>

#### Table 2-30 • I/O Short Currents I<sub>OSH</sub>/I<sub>OSL</sub> Applicable to FPGA I/O Banks

|                            | Drive Strength              | I <sub>OSL</sub> (mA) <sup>*</sup> | l <sub>OSH</sub> (mA) <sup>*</sup> |

|----------------------------|-----------------------------|------------------------------------|------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 27                                 | 25                                 |

|                            | 4 mA                        | 27                                 | 25                                 |

|                            | 6 mA                        | 54                                 | 51                                 |

|                            | 8 mA                        | 54                                 | 51                                 |

|                            | 12 mA                       | 109                                | 103                                |

|                            | 16 mA                       | 127                                | 132                                |

|                            | 24 mA                       | 181                                | 268                                |

| 2.5 V LVCMOS               | 2 mA                        | 18                                 | 16                                 |

|                            | 4 mA                        | 18                                 | 16                                 |

|                            | 6 mA                        | 37                                 | 32                                 |

|                            | 8 mA                        | 37                                 | 32                                 |

|                            | 12 mA                       | 74                                 | 65                                 |

|                            | 16 mA                       | 87                                 | 83                                 |

|                            | 24 mA                       | 124                                | 169                                |

| 1.8 V LVCMOS               | 2 mA                        | 11                                 | 9                                  |

|                            | 4 mA                        | 22                                 | 17                                 |

|                            | 6 mA                        | 44                                 | 35                                 |

|                            | 8 mA                        | 51                                 | 45                                 |

|                            | 12 mA                       | 74                                 | 91                                 |

|                            | 16 mA                       | 74                                 | 91                                 |

| 1.5 V LVCMOS               | 2 mA                        | 16                                 | 13                                 |

|                            | 4 mA                        | 33                                 | 25                                 |

|                            | 6 mA                        | 39                                 | 32                                 |

|                            | 8 mA                        | 55                                 | 66                                 |

|                            | 12 mA                       | 55                                 | 66                                 |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 109                                | 103                                |

*Note:*  $^{*}T_{J} = 85^{\circ}C.$

#### Table 2-31 • I/O Short Currents I<sub>OSH</sub>/I<sub>OSL</sub> Applicable to MSS I/O Banks

|                            | Drive Strength | I <sub>OSL</sub> (mA)* | I <sub>OSH</sub> (mA)* |

|----------------------------|----------------|------------------------|------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 8 mA           | 54                     | 51                     |

| 2.5 V LVCMOS               | 8 mA           | 37                     | 32                     |

| 1.8 V LVCMOS               | 4 mA           | 22                     | 17                     |

| 1.5 V LVCMOS               | 2 mA           | 16                     | 13                     |

*Note:*  $^{*}T_{J} = 85^{\circ}C$

### 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

### 1.8 V LVCMOS

Low-voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for generalpurpose 1.8 V applications. It uses a 1.8 V input buffer and a push-pull output buffer.

#### Table 2-47 • Minimum and Maximum DC Input and Output Levels

| 1.8 V<br>LVCMOS   |           | VIL                   | VIH                   |           | VOL       | VOH                   | I <sub>OL</sub> | I <sub>ОН</sub> | I <sub>OSL</sub>        | I <sub>OSH</sub>        | Ι <sub>ΙL</sub> | I <sub>IH</sub> |

|-------------------|-----------|-----------------------|-----------------------|-----------|-----------|-----------------------|-----------------|-----------------|-------------------------|-------------------------|-----------------|-----------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V             | Min.<br>V             | Max.<br>V | Max.<br>V | Min.<br>V             | mA              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA²             | μA²             |

| 2 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 2               | 2               | 11                      | 9                       | 15              | 15              |

| 4 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 4               | 4               | 22                      | 17                      | 15              | 15              |

| 6 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 6               | 6               | 44                      | 35                      | 15              | 15              |

| 8 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 8               | 8               | 51                      | 45                      | 15              | 15              |

| 12 mA             | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 12              | 12              | 74                      | 91                      | 15              | 15              |

| 16 mA             | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 1.9       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 16              | 16              | 74                      | 91                      | 15              | 15              |

#### Applicable to FPGA I/O Banks

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Software default selection highlighted in gray.

#### Table 2-48 • Minimum and Maximum DC Input and Output Levels Applicable to MSS I/O Banks

| 1.8 V<br>LVCMOS   |           | VIL                   | VIH                   |           | VOL       | VOH                   | I <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>OSH</sub>        | IIL | IIH |

|-------------------|-----------|-----------------------|-----------------------|-----------|-----------|-----------------------|-----------------|-----------------|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V             | Min.<br>V             | Max.<br>V | Max.<br>V | Min.<br>V             | mA              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 4 mA              | -0.3      | 0.35 *<br>VCCxxxxIOBx | 0.65 *<br>VCCxxxxIOBx | 3.6       | 0.45      | VCCxxxxIOBx<br>- 0.45 | 4               | 4               | 22                      | 17                      | 15  | 15  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Software default selection highlighted in gray.

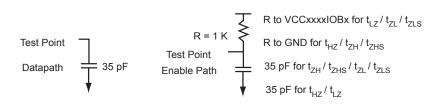

#### Table 2-49 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------------------|------------------------|

| 0             | 1.8            | 0.9                  | -                           | 35                     |

\* Measuring point = V<sub>trip.</sub> See Table 2-22 on page 2-24 for a complete table of trip points.

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>ОНD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| tosue                 | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| tOESUE                | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

#### Table 2-70 • Parameter Definition and Measuring Nodes

\* See Figure 2-15 on page 2-46 for more information.

#### **Timing Characteristics**

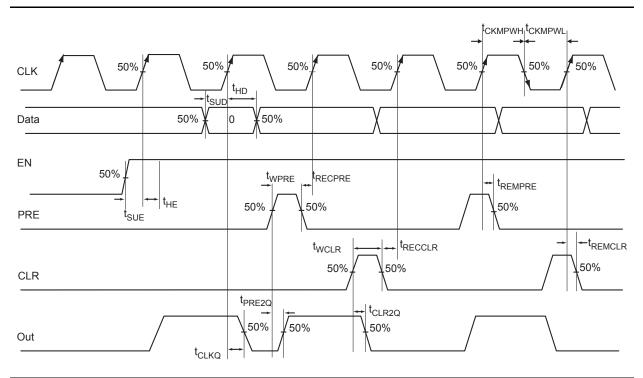

#### Table 2-79 • Register Delays

#### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.56 | 0.67 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.44 | 0.52 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.46 | 0.55 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.41 | 0.49 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.41 | 0.49 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.23 | 0.27 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | 0.27 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.22 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.22 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.32 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.36 | ns    |

*Note:* For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## static Microsemi.

SmartFusion DC and Switching Characteristics

#### *Table 2-88* • RAM512X18

| Parameter             | Description                                                                                                        | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.30 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.09 | 0.11 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.06 | 0.07 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.19 | 0.22 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained, WMODE = 0)                                                    | 2.19 | 2.63 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     | 0.91 | 1.09 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—applicable to opening edge |      | 0.43 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—applicable to opening edge | 0.44 | 0.50 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on RD (flow-through)                                                                     | 0.94 | 1.12 | ns    |

|                       | RESET Low to data out Low on RD (pipelined)                                                                        | 0.94 | 1.12 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.35 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.52 | 1.83 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          | 0.22 | 0.22 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.28 | 3.28 | ns    |

| F <sub>MAX</sub>      | Maximum clock frequency                                                                                            | 305  | 305  | MHz   |

Notes:

1. For more information, refer to the Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs application note.

2. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

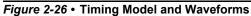

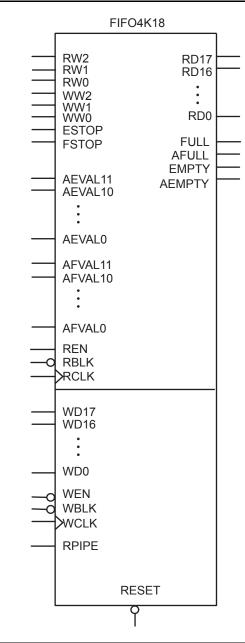

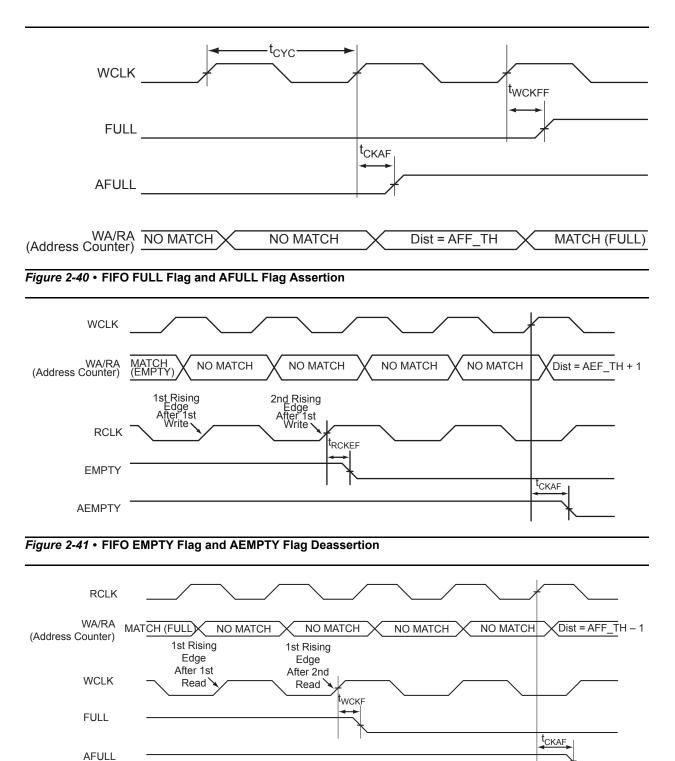

### FIFO

Figure 2-35 • FIFO Model

# **Programmable Analog Specifications**

### **Current Monitor**

Unless otherwise noted, current monitor performance is specified at 25°C with nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 91 Ksps, after digital compensation. All results are based on averaging over 16 samples.

Table 2-93 • Current Monitor Performance Specification

| Specification                                                  | Test Conditions                                                                              | Min.   | Typical           | Max.             | Units                   |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------|-------------------|------------------|-------------------------|

| Input voltage range (for driving ADC over full range)          |                                                                                              | 0 – 48 | 0 – 50            | 1 – 51           | mV                      |

| Analog gain                                                    | From the differential voltage across the input pads to the ADC input                         |        | 50                |                  | V/V                     |

| Input referred offset voltage                                  | Input referred offset voltage                                                                | 0      | 0.1               | 0.5              | mV                      |

|                                                                | -40°C to +100°C                                                                              | 0      | 0.1               | 0.5              | mV                      |

| Gain error                                                     | Slope of BFSL vs. 50 V/V                                                                     |        | ±0.1              | ±0.5             | % nom.                  |

|                                                                | -40°C to +100°C                                                                              |        |                   | ±0.5             | % nom.                  |

| Overall Accuracy                                               | Peak error from ideal transfer function, 25°C                                                |        | ±(0.1 +<br>0.25%) | ±(0.4 +<br>1.5%) | mV plus<br>%<br>reading |

| Input referred noise                                           | 0 VDC input (no output averaging)                                                            | 0.3    | 0.4               | 0.5              | mVrms                   |

| Common-mode rejection ratio                                    | 0 V to 12 VDC common-mode voltage                                                            | -86    | -87               |                  | dB                      |

| Analog settling time                                           | To 0.1% of final value (with ADC load)                                                       |        |                   |                  |                         |

|                                                                | From CM_STB (High)                                                                           | 5      |                   |                  | μs                      |

|                                                                | From ADC_START (High)                                                                        | 5      |                   | 200              | μs                      |

| Input capacitance                                              |                                                                                              |        | 8                 |                  | pF                      |

| Input biased current                                           | CM[n] or TM[n] pad,<br>40°C to +100°C over maximum input<br>voltage range (plus is into pad) |        |                   |                  |                         |

|                                                                | Strobe = 0; IBIAS on CM[n]                                                                   |        | 0                 |                  | μA                      |

|                                                                | Strobe = 1; IBIAS on CM[n]                                                                   |        | 1                 |                  | μA                      |

|                                                                | Strobe = 0; IBIAS on TM[n]                                                                   |        | 2                 |                  | μA                      |

|                                                                | Strobe = 1; IBIAS on TM[n]                                                                   |        | 1                 |                  | μA                      |

| Power supply rejection ratio                                   | DC (0 – 10 KHz)                                                                              | 41     | 42                |                  | dB                      |

| •                                                              | VCC33A                                                                                       |        | 150               |                  | μA                      |

| monitor power supply current requirements (per current monitor | VCC33AP                                                                                      |        | 140               |                  | μA                      |

| instance, not including ADC or<br>VAREFx)                      | VCC15A                                                                                       |        | 50                |                  | μA                      |

Note: Under no condition should the TM pad ever be greater than 10 mV above the CM pad. This restriction is applicable only if current monitor is used.

## **Global I/O Naming Conventions**

Gmn (Gxxx) refers to Global I/Os. These Global I/Os are used to connect the input to global networks. Global networks have high fanout and low skew. The naming convention for Global I/Os is as follows:

G = Global

m = Global pin location associated with each CCC on the device:

- A (northwest corner)

- B (northeast corner)

- C (east middle)

- D (southeast corner)

- E (southwest corner)

- F (west middle)

n = Global input MUX and pin number of the associated Global location m—A0, A1, A2, B0, B1, B2, C0, C1, or C2.

Global (GL) I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities.

Unused GL pins are configured as inputs with pull-up resistors. See more detailed descriptions of global I/O connectivity in the clocking resources chapter of the *SmartFusion FPGA Fabric User's Guide* and the clock conditioning circuitry chapter of the *SmartFusion Microcontroller Subsystem User's Guide*.

All inputs other than GC/GF are direct inputs into the quadrant clocks. The inputs to the global network are multiplexed, and only one input can be used as a global input. For example, if GAA0 is used as a quadrant global input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs other than GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. For more details, refer to the Global Input Selections section of the SmartFusion Fabric User Guide.

| Name   | Туре   | Polarity/B<br>us Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_x | In/out |                       | Microcontroller Subsystem (MSS) General Purpose I/O (GPIO). The MSS GPIO pin<br>functions as an input, output, tristate, or bidirectional buffer with configurable interrupt<br>generation and Schmitt trigger support. Input and output signal levels are compatible<br>with the I/O standard selected.                                                                                                                                                                                                                      |

|        |        |                       | Unused GPIO pins are tristated and do not include pull-up or pull-down resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |        |                       | During power-up, the used GPIO pins are tristated with no pull-up or pull-down resistors until Sys boot configures them.                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |        |                       | Some of these pins are also multiplexed with integrated peripherals in the MSS (SPI, I <sup>2</sup> C, and UART). These pins are located in Bank-2 (GPIO_16 to GPIO_31) for A2F060, A2F200, and A2F500 devices.                                                                                                                                                                                                                                                                                                               |

|        |        |                       | GPIOs can be routed to dedicated I/O buffers (MSSIOBUF) or in some cases to the FPGA fabric interface through an IOMUX. This allows GPIO pins to be multiplexed as either I/Os for the FPGA fabric, the ARM <sup>®</sup> Cortex-M3 or for given integrated MSS peripherals. The MSS peripherals are not multiplexed with each other; they are multiplexed only with the GPIO block. For more information, see the General Purpose I/O Block (GPIO) section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| IO     | In/out |                       | FPGA user I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## **User Pins**

|            | PQ208              |                    |  |

|------------|--------------------|--------------------|--|

| Pin Number | A2F200             | A2F500             |  |

| 94         | ABPS5              | ABPS5              |  |

| 95         | ABPS4              | ABPS4              |  |

| 96         | GNDAQ              | GNDAQ              |  |

| 97         | GNDA               | GNDA               |  |

| 98         | NC                 | NC                 |  |

| 99         | GNDVAREF           | GNDVAREF           |  |

| 100        | VAREFOUT           | VAREFOUT           |  |

| 101        | PU_N               | PU_N               |  |

| 102        | VCC33A             | VCC33A             |  |

| 103        | PTEM               | PTEM               |  |

| 104        | PTBASE             | PTBASE             |  |

| 105        | SPI_0_DO/GPIO_16   | SPI_0_DO/GPIO_16   |  |

| 106        | SPI_0_DI/GPIO_17   | SPI_0_DI/GPIO_17   |  |

| 107        | SPI_0_CLK/GPIO_18  | SPI_0_CLK/GPIO_18  |  |

| 108        | SPI_0_SS/GPIO_19   | SPI_0_SS/GPIO_19   |  |

| 109        | UART_0_RXD/GPIO_21 | UART_0_RXD/GPIO_21 |  |

| 110        | UART_0_TXD/GPIO_20 | UART_0_TXD/GPIO_20 |  |

| 111        | UART_1_RXD/GPIO_29 | UART_1_RXD/GPIO_29 |  |

| 112        | UART_1_TXD/GPIO_28 | UART_1_TXD/GPIO_28 |  |

| 113        | VCC                | VCC                |  |

| 114        | VCCMSSIOB2         | VCCMSSIOB2         |  |

| 115        | GND                | GND                |  |

| 116        | I2C_1_SDA/GPIO_30  | I2C_1_SDA/GPIO_30  |  |

| 117        | I2C_1_SCL/GPIO_31  | I2C_1_SCL/GPIO_31  |  |

| 118        | I2C_0_SDA/GPIO_22  | I2C_0_SDA/GPIO_22  |  |

| 119        | I2C_0_SCL/GPIO_23  | I2C_0_SCL/GPIO_23  |  |

| 120        | GNDENVM            | GNDENVM            |  |

| 121        | VCCENVM            | VCCENVM            |  |

| 122        | JTAGSEL            | JTAGSEL            |  |

| 123        | ТСК                | тск                |  |

| 124        | TDI                | TDI                |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

## FG256

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin   |                       | FG256                      |                            |

|-------|-----------------------|----------------------------|----------------------------|

| No.   | A2F060 Function       | A2F200 Function            | A2F500 Function            |

| D15   | GCA1/IO20PDB0V0       | IO24NDB1V0                 | IO33NDB1V0                 |

| D16   | VCCFPGAIOB1           | VCCFPGAIOB1                | VCCFPGAIOB1                |

| E1    | EMC_DB[13]/IO44PDB5V0 | EMC_DB[13]/GAC2/IO70PDB5V0 | EMC_DB[13]/GAC2/IO87PDB5V0 |

| E2    | EMC_DB[12]/IO44NDB5V0 | EMC_DB[12]/IO70NDB5V0      | EMC_DB[12]/IO87NDB5V0      |

| E3    | GFA2/IO42PDB5V0       | GFA2/IO68PDB5V0            | GFA2/IO85PDB5V0            |

| E4    | EMC_DB[10]/IO43NPB5V0 | EMC_DB[10]/IO69NPB5V0      | EMC_DB[10]/IO86NPB5V0      |

| E5    | GNDQ                  | GNDQ                       | GNDQ                       |

| E6    | GND                   | GND                        | GND                        |

| E7    | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |

| E8    | GND                   | GND                        | GND                        |

| E9    | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |

| E10   | GND                   | GND                        | GND                        |

| E11   | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |

| E12   | GCB2/IO22PDB1V0       | GCA1/IO28PDB1V0            | GCA1/IO36PDB1V0 *          |

| E13   | VCCFPGAIOB1           | VCCFPGAIOB1                | VCCFPGAIOB1                |

| E14   | GCA2/IO21PDB1V0       | GCB1/IO27PDB1V0            | GCB1/IO34PDB1V0            |

| E15   | GCC2/IO23PDB1V0       | GDC1/IO29PDB1V0            | GDC1/IO38PDB1V0            |

| E16   | IO23NDB1V0            | GDC0/IO29NDB1V0            | GDC0/IO38NDB1V0            |

| F1    | EMC_DB[9]/IO40PDB5V0  | EMC_DB[9]/GEC1/IO63PDB5V0  | EMC_DB[9]/GEC1/IO80PDB5V0  |

| F2    | GND                   | GND                        | GND                        |

| F3    | GFB2/IO42NDB5V0       | GFB2/IO68NDB5V0            | GFB2/IO85NDB5V0            |

| F4    | VCCFPGAIOB5           | VCCFPGAIOB5                | VCCFPGAIOB5                |

| F5    | EMC_DB[11]/IO43PPB5V0 | EMC_DB[11]/IO69PPB5V0      | EMC_DB[11]/IO86PPB5V0      |

| F6    | VCCFPGAIOB5           | VCCFPGAIOB5                | VCCFPGAIOB5                |

| F7    | GND                   | GND                        | GND                        |

| F8    | VCC                   | VCC                        | VCC                        |

| F9    | GND                   | GND                        | GND                        |

| F10   | VCC                   | VCC                        | VCC                        |

| F11   | GND                   | GND                        | GND                        |

| F12   | IO22NDB1V0            | GCA0/IO28NDB1V0            | GCA0/IO36NDB1V0 *          |

| F13   | NC                    | GNDQ                       | GNDQ                       |

| Notes |                       | ·                          |                            |

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin    |                      | FG256                     |                           |

|--------|----------------------|---------------------------|---------------------------|

| No.    | A2F060 Function      | A2F200 Function           | A2F500 Function           |

| H13    | TDO                  | TDO                       | TDO                       |

| H14    | TDI                  | TDI                       | TDI                       |

| H15    | JTAGSEL              | JTAGSEL                   | JTAGSEL                   |

| H16    | GND                  | GND                       | GND                       |

| J1     | EMC_DB[4]/IO38NPB5V0 | EMC_DB[4]/GEA0/IO61NPB5V0 | EMC_DB[4]/GEA0/IO78NPB5V0 |

| J2     | EMC_DB[3]/IO37PDB5V0 | EMC_DB[3]/GEC2/IO60PDB5V0 | EMC_DB[3]/GEC2/IO77PDB5V0 |

| J3     | EMC_DB[2]/IO37NDB5V0 | EMC_DB[2]/IO60NDB5V0      | EMC_DB[2]/IO77NDB5V0      |

| J4     | GNDRCOSC             | GNDRCOSC                  | GNDRCOSC                  |

| J5     | NC                   | GNDQ                      | GNDQ                      |

| J6     | GND                  | GND                       | GND                       |

| J7     | VCC                  | VCC                       | VCC                       |

| J8     | GND                  | GND                       | GND                       |

| J9     | VCC                  | VCC                       | VCC                       |

| J10    | GND                  | GND                       | GND                       |

| J11    | VCCMSSIOB2           | VCCMSSIOB2                | VCCMSSIOB2                |

| J12    | I2C_0_SCL/GPIO_23    | I2C_0_SCL/GPIO_23         | I2C_0_SCL/GPIO_23         |

| J13    | I2C_0_SDA/GPIO_22    | I2C_0_SDA/GPIO_22         | I2C_0_SDA/GPIO_22         |

| J14    | I2C_1_SCL/GPIO_31    | I2C_1_SCL/GPIO_31         | I2C_1_SCL/GPIO_31         |

| J15    | VCCMSSIOB2           | VCCMSSIOB2                | VCCMSSIOB2                |

| J16    | I2C_1_SDA/GPIO_30    | I2C_1_SDA/GPIO_30         | I2C_1_SDA/GPIO_30         |

| K1     | GPIO_1/IO32RSB4V0    | MAC_MDIO/IO49RSB4V0       | MAC_MDIO/IO58RSB4V0       |

| K2     | GPIO_0/IO33RSB4V0    | MAC_MDC/IO48RSB4V0        | MAC_MDC/IO57RSB4V0        |

| K3     | VCCMSSIOB4           | VCCMSSIOB4                | VCCMSSIOB4                |

| K4     | MSS_RESET_N          | MSS_RESET_N               | MSS_RESET_N               |

| K5     | VCCRCOSC             | VCCRCOSC                  | VCCRCOSC                  |

| K6     | VCCMSSIOB4           | VCCMSSIOB4                | VCCMSSIOB4                |

| K7     | GND                  | GND                       | GND                       |

| K8     | VCC                  | VCC                       | VCC                       |

| K9     | GND                  | GND                       | GND                       |

| K10    | VCC                  | VCC                       | VCC                       |

| K11    | GND                  | GND                       | GND                       |

| Notes: |                      | •                         | •                         |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin | FG256           |                 |                 |  |

|-----|-----------------|-----------------|-----------------|--|

| No. | A2F060 Function | A2F200 Function | A2F500 Function |  |

| Т9  | VAREF0          | VAREF1          | VAREF1          |  |

| T10 | ABPS0           | ABPS6           | ABPS6           |  |

| T11 | NC              | ABPS5           | ABPS5           |  |

| T12 | NC              | SDD1            | SDD1            |  |

| T13 | GNDVAREF        | GNDVAREF        | GNDVAREF        |  |

| T14 | GNDMAINXTAL     | GNDMAINXTAL     | GNDMAINXTAL     |  |

| T15 | VCCLPXTAL       | VCCLPXTAL       | VCCLPXTAL       |  |

| T16 | PU_N            | PU_N            | PU_N            |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                 | Page             |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 3                 | Two notes were added to the "Supply Pins" table (SAR 27109):                                                                                                                                                                                                                                                                            | 5-1              |

| (continued)                | <ol> <li>The following supplies should be connected together while following proper noise<br/>filtering practices: VCC33A, VCC33ADCx, VCC33AP, VCC33SDDx, VCCMAINXTAL,<br/>and VCCLPXTAL.</li> </ol>                                                                                                                                    |                  |

|                            | <ol> <li>The following 1.5 V supplies should be connected together while following proper<br/>noise filtering practices: VCC, VCC15A, and VCC15ADCx.</li> </ol>                                                                                                                                                                         |                  |

|                            | The descriptions for the "VCC33N", "NCAP", and "PCAP" pins were revised to include information on what to do if analog SCB features and SDDs are not used (SAR 26744).                                                                                                                                                                  | 5-2, 5-9,<br>5-9 |

|                            | Information was added to the "User Pins" table regarding tristating of used and unused GPIO pins. The IO portion of the table was revised to state that unused I/O pins are disabled by Libero IDE software and include a weak pull-up resistor (SAR 26890). Information was added regarding behavior of used I/O pins during power-up. | 5-6              |

|                            | The type for "EMC_RW_N" was changed from In/out to Out (SAR 25113).                                                                                                                                                                                                                                                                     | 5-12             |

|                            | A note was added to the "Analog Front-End (AFE)" table stating that unused analog inputs should be grounded (SAR 26744).                                                                                                                                                                                                                | 5-14             |

|                            | The "TQ144" section is new, with pin tables for A2F200 and A2F500 (SAR 27044).                                                                                                                                                                                                                                                          | 5-18             |

|                            | The "FG256" pin table was replaced and now includes "Handling When Unused" information (SAR 27709).                                                                                                                                                                                                                                     | 5-42             |

| Revision 2<br>(May 2010)   | Embedded nonvolatile flash memory (eNVM) was changed from "64 to 512 Kbytes" to "128 to 512 Kbytes" in the "Microcontroller Subsystem (MSS)" section and "SmartFusion cSoC Family Product Table" (SAR 26005).                                                                                                                           | I, II            |

|                            | The main oscillator range of values was changed to "32 KHz to 20 MHz" in the "Microcontroller Subsystem (MSS)" section and the "SmartFusion cSoC Family Product Table" (SAR 24906).                                                                                                                                                     | I, II            |

|                            | The value for $t_{PD}$ was changed from 50 ns to 15 ns for the high-speed voltage comparators listed in the "Analog Front-End (AFE)" section (SAR 26005).                                                                                                                                                                               | I                |

|                            | The number of PLLs for A2F200 was changed from 2 to 1 in the "SmartFusion cSoC Family Product Table" (SAR 25093).                                                                                                                                                                                                                       | П                |

|                            | Values for direct analog input, total analog input, and total I/Os were updated for the FG256 package, A2F060, in the "Package I/Os: MSS + FPGA I/Os" table. The Max. column was removed from the table (SAR 26005).                                                                                                                    | Ш                |

|                            | The Speed Grade section of the "Product Ordering Codes" table was revised (SAR 25257).                                                                                                                                                                                                                                                  | VI               |

| Revision 1<br>(March 2010) | The "Product Ordering Codes" table was revised to add "blank" as an option for lead-<br>free packaging and application (junction temperature range).                                                                                                                                                                                    | VI               |

|                            | Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> was revised. Ta (ambient temperature) was replaced with $T_J$ (junction temperature).                                                                                                                                                                                       | 2-3              |

|                            | PDC5 was deleted from Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs.                                                                                                                                                                                                              | 2-13             |

|                            | The formulas in the footnotes for Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances were revised.                                                                                                                                                                                                                                     | 2-27             |

|                            | The values for input biased current were revised in Table 2-93 • Current Monitor Performance Specification.                                                                                                                                                                                                                             | 2-78             |

| Revision 0<br>(March 2010) | The "Analog Front-End (AFE)" section was updated to change the throughput for 10-<br>bit mode from 600 Ksps to 550 Ksps.                                                                                                                                                                                                                | Ι                |