# E·XFL

#### Microchip Technology - <u>A2F200M3F-PQ208 Datasheet</u>

Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Detuns                  |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                  |

| Architecture            | MCU, FPGA                                                                 |

| Core Processor          | ARM® Cortex®-M3                                                           |

| Flash Size              | 256KB                                                                     |

| RAM Size                | 64KB                                                                      |

| Peripherals             | DMA, POR, WDT                                                             |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                      |

| Speed                   | 80MHz                                                                     |

| Primary Attributes      | ProASIC®3 FPGA, 200K Gates, 4608 D-Flip-Flops                             |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                           |

| Package / Case          | 208-BFQFP                                                                 |

| Supplier Device Package | 208-PQFP (28x28)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f200m3f-pq208 |

|                         |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

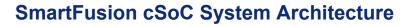

Note: Architecture for A2F200

$$P = \frac{T_J - T_A}{\theta_{JA}} = \frac{100^{\circ}C - 70^{\circ}C}{17.00 \text{ W}} = 1.76 \text{ W}$$

EQ 6

The 1.76 W power is less than the required 3.00 W. The design therefore requires a heat sink, or the airflow where the device is mounted should be increased. The design's total junction-to-air thermal resistance requirement can be estimated by EQ 7:

$$\theta_{JA(total)} = \frac{T_J - T_A}{P} = \frac{100^{\circ}C - 70^{\circ}C}{3.00 \text{ W}} = 10.00^{\circ}\text{C/W}$$

EQ 7

Determining the heat sink's thermal performance proceeds as follows:

$$\theta_{JA(TOTAL)} = \theta_{JC} + \theta_{CS} + \theta_{SA}$$

EQ 8

where

$$\theta_{JA} = 0.37^{\circ}C/W$$

Thermal resistance of the interface material between the case and the heat sink, usually provided by the thermal interface manufacturer

$\theta_{SA}$  = Thermal resistance of the heat sink in °C/W

$\theta_{\text{SA}}$

$$\theta_{SA} = \theta_{JA(TOTAL)} - \theta_{JC} - \theta_{CS}$$

$$EQ 9$$

$$= 13.33^{\circ}C/W - 8.28^{\circ}C/W - 0.37^{\circ}C/W = 5.01^{\circ}C/W$$

A heat sink with a thermal resistance of 5.01°C/W or better should be used. Thermal resistance of heat sinks is a function of airflow. The heat sink performance can be significantly improved with increased airflow.

Carefully estimating thermal resistance is important in the long-term reliability of an FPGA. Design engineers should always correlate the power consumption of the device with the maximum allowable power dissipation of the package selected for that device.

Note: The junction-to-air and junction-to-board thermal resistances are based on JEDEC standard (JESD-51) and assumptions made in building the model. It may not be realized in actual application and therefore should be used with a degree of caution. Junction-to-case thermal resistance assumes that all power is dissipated through the case.

#### **Temperature and Voltage Derating Factors**

Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays<br/>(normalized to T<sub>J</sub> = 85°C, worst-case VCC = 1.425 V)

| Array              | Junction Temperature (°C) |      |      |      |      |       |  |  |  |  |  |

|--------------------|---------------------------|------|------|------|------|-------|--|--|--|--|--|

| Voltage VCC<br>(V) | –40°C                     | 0°C  | 25°C | 70°C | 85°C | 100°C |  |  |  |  |  |

| 1.425              | 0.86                      | 0.91 | 0.93 | 0.98 | 1.00 | 1.02  |  |  |  |  |  |

| 1.500              | 0.81                      | 0.86 | 0.88 | 0.93 | 0.95 | 0.96  |  |  |  |  |  |

| 1.575              | 0.78                      | 0.83 | 0.85 | 0.90 | 0.91 | 0.93  |  |  |  |  |  |

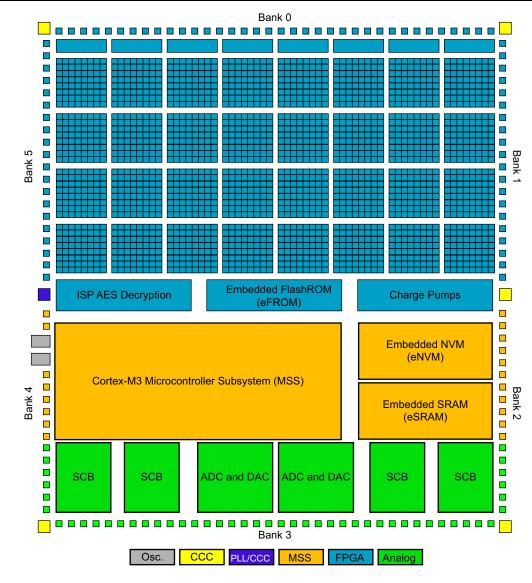

Figure 2-4 • Output Buffer Model and Delays (example)

#### Table 2-24 • Summary of I/O Timing Characteristics—Software Default Settings

-1 Speed Grade, Worst Commercial-Case Conditions:  $T_J = 85^{\circ}C$ , Worst Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx (per standard)

| Applicable to FPGA I/O Banks, Assigned to EMC I/O Pins |

|--------------------------------------------------------|

|--------------------------------------------------------|

| I/O Standard                  | Drive Strength    | Slew Rate | Capacitive Load (pF) | External Resistor ( $\Omega$ ) | t <sub>DOUT</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>PY</sub> (ns) | t <sub>EoUT</sub> (ns) | t <sub>ZL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | t <sub>ZLS</sub> (ns) | t <sub>ZHS</sub> (ns) | Units |

|-------------------------------|-------------------|-----------|----------------------|--------------------------------|------------------------|----------------------|-----------------------|----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA             | High      | 35                   | -                              | 0.50                   | 2.81                 | 0.03                  | 0.81                 | 0.32                   | 2.86                 | 2.23                 | 2.55                 | 2.82                 | 4.58                  | 3.94                  | ns    |

| 2.5 V LVCMOS                  | 12 mA             | High      | 35                   | -                              | 0.50                   | 2.73                 | 0.03                  | 1.03                 | 0.32                   | 2.88                 | 2.69                 | 2.62                 | 2.70                 | 4.60                  | 4.41                  | ns    |

| 1.8 V LVCMOS                  | 12 mA             | High      | 35                   | -                              | 0.50                   | 2.81                 | 0.03                  | 0.95                 | 0.32                   | 2.87                 | 2.38                 | 2.92                 | 3.18                 | 4.58                  | 4.10                  | ns    |

| 1.5 V LVCMOS                  | 12 mA             | High      | 35                   | -                              | 0.50                   | 3.24                 | 0.03                  | 1.12                 | 0.32                   | 3.30                 | 2.79                 | 3.10                 | 3.27                 | 5.02                  | 4.50                  | ns    |

| 3.3 V PCI                     | Per PCI spec      | High      | 10                   | 25 <sup>1</sup>                | 0.50                   | 2.11                 | 0.03                  | 0.68                 | 0.32                   | 2.15                 | 1.57                 | 2.55                 | 2.82                 | 3.87                  | 3.28                  | ns    |

| 3.3 V PCI-X                   | Per PCI-X<br>spec | High      | 10                   | 25 <sup>1</sup>                | 0.50                   | 2.11                 | 0.03                  | 0.64                 | 0.32                   | 2.15                 | 1.57                 | 2.55                 | 2.82                 | 3.87                  | 3.28                  | ns    |

| LVDS                          | 24 mA             | High      | -                    | _                              | 0.50                   | 1.53                 | 0.03                  | 1.55                 | _                      | -                    | -                    | -                    | _                    | _                     | -                     | ns    |

| LVPECL                        | 24 mA             | High      | _                    | _                              | 0.50                   | 1.46                 | 0.03                  | 1.46                 | _                      | _                    | _                    | _                    | _                    | _                     | -                     | ns    |

Notes:

1. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-10 on page 2-39 for connectivity. This resistor is not required during normal operation.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings

-1 Speed Grade, Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx (per standard)

| I/O Standard                  | Drive Strength | Slew Rate | Capacitive Load (pF) | External Resistor | t <sub>bour</sub> (ns) | t <sub>DP</sub> (ns) | t <sub>DIN</sub> (ns) | t <sub>pY</sub> (ns) | t <sub>pYS</sub> (ns) | t <sub>EOUT</sub> (ns) | t <sub>zL</sub> (ns) | t <sub>ZH</sub> (ns) | t <sub>LZ</sub> (ns) | t <sub>HZ</sub> (ns) | Units |

|-------------------------------|----------------|-----------|----------------------|-------------------|------------------------|----------------------|-----------------------|----------------------|-----------------------|------------------------|----------------------|----------------------|----------------------|----------------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA           | High      | 10                   | -                 | 0.18                   | 1.92                 | 0.07                  | 0.78                 | 1.09                  | 0.18                   | 1.96                 | 1.55                 | 1.83                 | 2.04                 | ns    |

| 2.5 V LVCMOS                  | 8 mA           | High      | 10                   | -                 | 0.18                   | 1.96                 | 0.07                  | 0.99                 | 1.16                  | 0.18                   | 2.00                 | 1.82                 | 1.82                 | 1.93                 | ns    |

| 1.8 V LVCMOS                  | 4 mA           | High      | 10                   | 1                 | 0.18                   | 2.31                 | 0.07                  | 0.91                 | 1.37                  | 0.18                   | 2.35                 | 2.27                 | 1.84                 | 1.87                 | ns    |

| 1.5 V LVCMOS                  | 2 mA           | High      | 10                   | -                 | 0.18                   | 2.70                 | 0.07                  | 1.07                 | 1.55                  | 0.18                   | 2.75                 | 2.67                 | 1.87                 | 1.85                 | ns    |

Notes:

1. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-10 on page 2-39 for connectivity. This resistor is not required during normal operation.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### **Output Register**

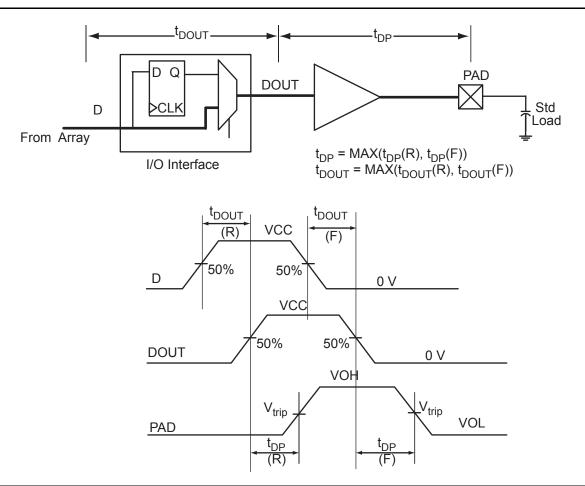

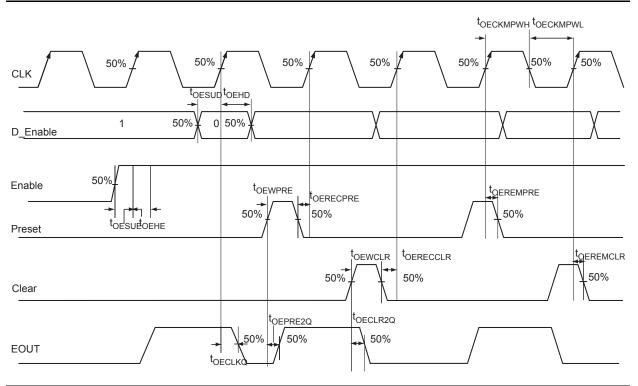

#### Figure 2-17 • Output Register Timing Diagram

#### **Timing Characteristics**

# Table 2-72 • Output Data Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -1   | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 0.60 | 0.72 | ns    |

| tosud                | Data Setup Time for the Output Data Register                         | 0.32 | 0.38 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00 | ns    |

| t <sub>OSUE</sub>    | Enable Setup Time for the Output Data Register                       | 0.44 | 0.53 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.82 | 0.98 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.82 | 0.98 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.23 | 0.27 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.23 | 0.27 | ns    |

| towclr               | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.22 | 0.22 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.22 | 0.22 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.36 | 0.36 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.32 | 0.32 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

#### **Output Enable Register**

Figure 2-18 • Output Enable Register Timing Diagram

#### **Timing Characteristics**

Table 2-73 • Output Enable Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.45 | 0.54 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.32 | 0.38 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.53 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.68 | 0.81 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.68 | 0.81 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.23 | 0.27 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.23 | 0.27 | ns    |

| tOEWCLR               | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.22 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.22 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.36 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.32 | 0.32 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

SmartFusion DC and Switching Characteristics

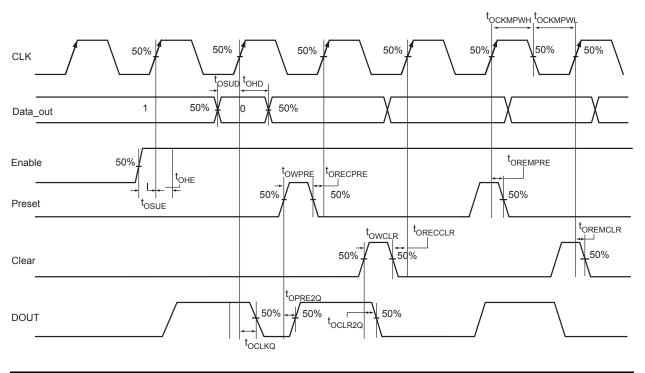

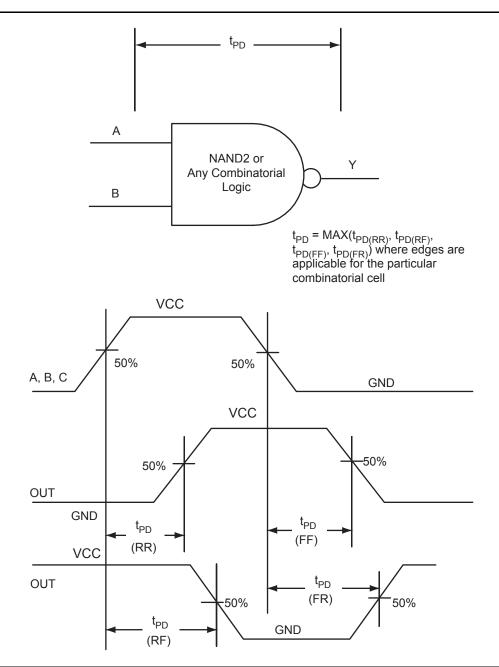

Figure 2-24 • Timing Model and Waveforms

### **Microsemi**.

SmartFusion DC and Switching Characteristics

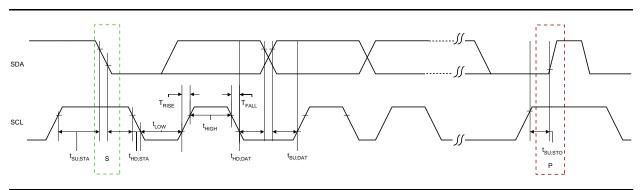

#### Table 2-101 • I<sup>2</sup>C Characteristics Commercial Case Conditions: T<sub>J</sub> = 85°C, V<sub>DD</sub> = 1.425 V, –1 Speed Grade (continued)

| Parameter           | Definition                   | Definition Condition      |    |    |  |

|---------------------|------------------------------|---------------------------|----|----|--|

| t <sub>SU;STO</sub> | STOP setup time <sup>3</sup> | setup time <sup>3</sup> – |    |    |  |

| t <sub>FILT</sub>   | Maximum spike width filtered | -                         | 50 | ns |  |

Notes:

- 1. These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

- These values are provided for a load of 100 pF and 400 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&Itemid=489&Iang=en&view=salescontact.

- 3. For allowable Pclk configurations, refer to the Inter-Integrated Circuit (I<sup>2</sup>C) Peripherals section in the SmartFusion Microcontroller Subsystem User's Guide.

Figure 2-48 • I2C Timing Parameter Definition

Emcraft Systems provides porting of the open-source U-boot firmware and uClinux<sup>™</sup> kernel to the SmartFusion cSoC, a Linux<sup>®</sup>-based cross-development framework, and other complementary components. Combined with the release of its A2F-Linux Evaluation Kit, this provides a low-cost platform for evaluation and development of Linux (uClinux) on the Cortex-M3 CPU core of the Microsemi SmartFusion cSoC.

• Emcraft Linux on Microsemi's SmartFusion cSoC

Keil offers the RTX Real-Time Kernel as a royalty-free, deterministic RTOS designed for ARM and Cortex-M devices. It allows you to create programs that simultaneously perform multiple functions and helps to create applications which are better structured and more easily maintained.

- The RTX Real-Time Kernel is included with MDK-ARM. Download the Evaluation version of Keil MDK-ARM.

- RTX source code is available as part of Keil/ARM Real-Time Library (RL-ARM), a group of tightlycoupled libraries designed to solve the real-time and communication challenges of embedded systems based on ARM-powered microcontroller devices. The RL-ARM library now supports SmartFusion cSoCs and designers with additional key features listed in the "Middleware" section on page 3-5.

Micrium supports SmartFusion cSoCs with the company's flagship  $\mu$ C/OS family, recognized for a variety of features and benefits, including unparalleled reliability, performance, dependability, impeccable source code and vast documentation. Micrium supports the following products for SmartFusion cSoCs and continues to work with Microsemi on additional projects.

- SmartFusion Quickstart Guide for Micrium µC/OS-III Examples

- Design Files

µC/OS-III™, Micrium's newest RTOS, is designed to save time on your next embedded project and puts greater control of the software in your hands.

RoweBots provides an ultra tiny Linux-compatible RTOS called Unison for SmartFusion. Unison consists of a set of modular software components, which, like Linux, are either free or commercially licensed. Unison offers POSIX<sup>®</sup> and Linux compatibility with hard real-time performance, complete I/O modules and an easily understood environment for device driver programming. Seamless integration with FPGA and analog features are fast and easy.

- Unison V4-based products include a free Unison V4 Linux and POSIX-compatible kernel with serial I/O, file system, six demonstration programs, upgraded documentation and source code for Unison V4, and free (for non-commercial use) Unison V4 TCP/IP server. Commercial license upgrade is available for Unison V4 TCP/IP server with three demonstration programs, DHCP client and source code.

- Unison V5-based products include commercial Unison V5 Linux- and POSIX-compatible kernel with serial I/O, file system, extensive feature set, full documentation, source code and more than 20 demonstration programs, Unison V5 TCP/IPv4 with extended feature set, sockets interface, multiple network interfaces, PPP support, DHCP client, documentation, source code and six demonstration programs, and multiple other features.

### Middleware

Microsemi has ported both uIP and IwIP for Ethernet support as well as including TFTP file service.

- SmartFusion Webserver Demo Using uIP and FreeRTOS

- SmartFusion: Running Webserver, TFTP on IwIP TCP/IP Stack Application Note

The Keil/ARM Real-Time Library (RL-ARM)<sup>1</sup>, in addition to RTX source, includes the following:

RL-TCPnet (TCP/IP) – The Keil RL-TCPnet library, supporting full TCP/IP and UDP protocols, is a full networking suite specifically written for small ARM and Cortex-M processor-based microcontrollers. TCPnet is now ported to and supports SmartFusion Cortex-M3. It is highly optimized, has a small code footprint, and gives excellent performance, providing a wide range of application level protocols and examples such as FTP, SNMP, SOAP and AJAX. An HTTP server example of TCPnet working in a SmartFusion design is available.

<sup>1.</sup> The CAN and USB functions within RL-ARM are not supported for SmartFusion cSoC.

Pin Descriptions

| Name  | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VJTAG | Supply | Digital supply to the JTAG controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       |        | SmartFusion cSoCs have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the $V_{JTAG}$ pin together with the TRSTB pin could be tied to GND. Note that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a SmartFusion cSoC is in a JTAG chain of interconnected boards and it is desired to power down the board containing the device, this can be done provided both VJTAG and VCC to the device remain powered; otherwise, JTAG signals will not be able to transition the device, even in bypass mode. See "JTAG Pins" section on page 5-10. |

| VPP   | Supply | Digital programming circuitry supply<br>SmartFusion cSoCs support single-voltage in-system programming (ISP) of the<br>configuration flash, embedded FlashROM (eFROM), and embedded nonvolatile<br>memory (eNVM).<br>For programming, VPP should be in the 3.3 V $\pm$ 5% range. During normal device<br>operation, VPP can be left floating or can be tied to any voltage between 0 V and 3.6 V.<br>When the VPP pin is tied to ground, it shuts off the charge pump circuitry, resulting in no<br>sources of oscillation from the charge pump circuitry. For proper programming, 0.01µF,<br>and 0.1µF to 1µF capacitors, (both rated at 16 V) are to be connected in parallel across<br>VPP and GND, and positioned as close to the FPGA pins as possible.                                                                                                        |

Notes:

1. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. For more details on VCCPLLx capacitor recommendations, refer to the application note AC359, SmartFusion cSoC Board Design Guidelines, the "PLL Power Supply Decoupling Scheme" section.

### **Global I/O Naming Conventions**

Gmn (Gxxx) refers to Global I/Os. These Global I/Os are used to connect the input to global networks. Global networks have high fanout and low skew. The naming convention for Global I/Os is as follows:

G = Global

m = Global pin location associated with each CCC on the device:

- A (northwest corner)

- B (northeast corner)

- C (east middle)

- D (southeast corner)

- E (southwest corner)

- F (west middle)

n = Global input MUX and pin number of the associated Global location m—A0, A1, A2, B0, B1, B2, C0, C1, or C2.

Global (GL) I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities.

Unused GL pins are configured as inputs with pull-up resistors. See more detailed descriptions of global I/O connectivity in the clocking resources chapter of the *SmartFusion FPGA Fabric User's Guide* and the clock conditioning circuitry chapter of the *SmartFusion Microcontroller Subsystem User's Guide*.

All inputs other than GC/GF are direct inputs into the quadrant clocks. The inputs to the global network are multiplexed, and only one input can be used as a global input. For example, if GAA0 is used as a quadrant global input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs other than GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. For more details, refer to the Global Input Selections section of the SmartFusion Fabric User Guide.

| Name   | Туре   | Polarity/B<br>us Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_x | In/out |                       | Microcontroller Subsystem (MSS) General Purpose I/O (GPIO). The MSS GPIO pin<br>functions as an input, output, tristate, or bidirectional buffer with configurable interrupt<br>generation and Schmitt trigger support. Input and output signal levels are compatible<br>with the I/O standard selected.                                                                                                                                                                                                                      |

|        |        |                       | Unused GPIO pins are tristated and do not include pull-up or pull-down resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |        |                       | During power-up, the used GPIO pins are tristated with no pull-up or pull-down resistors until Sys boot configures them.                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |        |                       | Some of these pins are also multiplexed with integrated peripherals in the MSS (SPI, I <sup>2</sup> C, and UART). These pins are located in Bank-2 (GPIO_16 to GPIO_31) for A2F060, A2F200, and A2F500 devices.                                                                                                                                                                                                                                                                                                               |

|        |        |                       | GPIOs can be routed to dedicated I/O buffers (MSSIOBUF) or in some cases to the FPGA fabric interface through an IOMUX. This allows GPIO pins to be multiplexed as either I/Os for the FPGA fabric, the ARM <sup>®</sup> Cortex-M3 or for given integrated MSS peripherals. The MSS peripherals are not multiplexed with each other; they are multiplexed only with the GPIO block. For more information, see the General Purpose I/O Block (GPIO) section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| IO     | In/out |                       | FPGA user I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### **User Pins**

### User I/O Naming Conventions

The naming convention used for each FPGA user I/O is Gmn/IOuxwByVz, where:

**Gmn** is only used for I/Os that also have CCC access—i.e., global pins. Refer to the "Global I/O Naming Conventions" section on page 5-6.

$\mathbf{u} = I/O$  pair number in bank, starting at 00 from the northwest I/O bank and proceeding in a clockwise direction.

x = P (positive) or N (negative) or S (single-ended) or R (regular, single-ended).

$\mathbf{w} = D$  (Differential Pair), P (Pair), or S (Single-Ended). D (Differential Pair) if both members of the pair are bonded out to adjacent pins or are separated only by one GND or NC pin; P (Pair) if both members of the pair are bonded out but do not meet the adjacency requirement; or S (Single-Ended) if the I/O pair is not bonded out. For Differential Pairs (D), adjacency for ball grid packages means only vertical or horizontal. Diagonal adjacency does not meet the requirements for a true differential pair.

B = Bank

y = Bank number starting at 0 from northwest I/O bank and incrementing clockwise.

V = Reference voltage

**z** = VREF mini bank number.

The FPGA user I/O pin functions as an input, output, tristate or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected. Unused I/O pins are disabled by Libero SoC software and include a weak pull-up resistor. During power-up, the used I/O pins are tristated with no pull-up or pull-down resistors until I/O enable (there is a delay after voltage stabilizes, and different I/O banks power up sequentially to avoid a surge of ICCI).

Unused I/Os are configured as follows:

- Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- Weak pull-up is programmed

Some of these pins are also multiplexed with integrated peripherals in the MSS (Ethernet MAC and external memory controller).

All unused MSS I/Os are tristated by default (with output buffer disabled). However, you can configure it as weak pull-up or pull-down by using Libero SoC I/O attributor window. The Schmitt trigger is disabled. Essentially, I/Os have the reset values as defined in Table 19-25 IOMUX\_n\_CR, in the *SmartFusion Microcontroller Subsystem User's Guide*.

By default, during programming I/Os become tristated and weakly pulled up to VCCxxxxIOBx. You can modify the I/O states during programming in FlashPro. For more details, refer to "Specifying I/O States During Programming" on page 1-3. With the VCCI and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os are instantly configured to the desired user configuration. For more information, see the SmartFusion FPGA User I/Os section in the *SmartFusion FPGA Fabric User's Guide*.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

| Name        | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCAP        |      | 1                 | Negative capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |      |                   | This is the negative terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. Analog charge pump capacitors are not needed if none of the analog SCB features are used and none of the SDDs are used. In that case it should be left unconnected.                                                                                                                                                                                                                                                                                                       |

| PCAP        |      | 1                 | Positive Capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |      |                   | This is the positive terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. If this pin is not used, it must be left unconnected/floating. In this case, no capacitor is needed. Analog charge pump capacitors are not needed if none of the analog SCB features are used, and none of the SDDs are used.                                                                                                                                                                                                                                             |

| PTBASE      |      | 1                 | Pass transistor base connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |      |                   | This is the control signal of the voltage regulator. This pin should be connected to the base of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PTEM        |      | 1                 | Pass transistor emitter connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |      |                   | This is the feedback input of the voltage regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |      |                   | This pin should be connected to the emitter of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MSS_RESET_N |      | Low               | Low Reset signal which can be used as an external reset and can also<br>be used as a system level reset under control of the Cortex-M3<br>processor. MSS_RESET_N is an output asserted low after power-on<br>reset. The direction of MSS_RESET_N changes during the execution<br>of the Microsemi System Boot when chip-level reset is enabled. The<br>Microsemi System Boot reconfigures MSS_RESET_N to become a<br>reset input signal when chip-level reset is enabled. It has an internal<br>pull-up so it can be left floating. In the current software, the<br>MSS_RESET_N is modeled as an external input signal only. |

| PU_N        | In   | Low               | Push-button is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### Table 5-1 • Recommended Tie-Off Values for the TCK and TRST Pins

| VJTAG          | Tie-Off Resistance <sup>1, 2</sup> |

|----------------|------------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                      |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                      |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ                      |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                      |

Notes:

1. The TCK pin can be pulled up/down.

2. The TRST pin can only be pulled down.

1. Equivalent parallel resistance if more than one device is on JTAG chain.

Pin Descriptions

## Analog Front-End (AFE)

|       |      |                                                                                                                                                                             | Associated With |      |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|

| Name  | Туре | Description                                                                                                                                                                 | ADC/SDD         | SCB  |

| ABPS0 | In   | SCB 0 / active bipolar prescaler input 1.<br>See the Active Bipolar Prescaler (ABPS) section in the <i>SmartFusion</i><br><i>Programmable Analog User's Guide</i> .         | ADC0            | SCB0 |

| ABPS1 | In   | SCB 0 / active bipolar prescaler Input 2                                                                                                                                    | ADC0            | SCB0 |

| ABPS2 | In   | SCB 1 / active bipolar prescaler Input 1                                                                                                                                    | ADC0            | SCB1 |

| ABPS3 | In   | SCB 1 / active bipolar prescaler Input 2                                                                                                                                    | ADC0            | SCB1 |

| ABPS4 | In   | SCB 2 / active bipolar prescaler Input 1                                                                                                                                    | ADC1            | SCB2 |

| ABPS5 | In   | SCB 2 / active bipolar prescaler Input 2                                                                                                                                    | ADC1            | SCB2 |

| ABPS6 | In   | SCB 3 / active bipolar prescaler Input 1                                                                                                                                    | ADC1            | SCB3 |

| ABPS7 | In   | SCB 3 / active bipolar prescaler input 2                                                                                                                                    | ADC1            | SCB3 |

| ABPS8 | In   | SCB 4 / active bipolar prescaler input 1                                                                                                                                    | ADC2            | SCB4 |

| ABPS9 | In   | SCB 4 / active bipolar prescaler input 2                                                                                                                                    | ADC2            | SCB4 |

| ADC0  | In   | ADC 0 direct input 0 / FPGA Input.<br>See the "Sigma-Delta Digital-to-Analog Converter (DAC)" section in<br>the <i>SmartFusion Programmable Analog User's Guide</i> .       | ADC0            | SCB0 |

| ADC1  | In   | ADC 0 direct input 1 / FPGA input                                                                                                                                           | ADC0            | SCB0 |

| ADC2  | In   | ADC 0 direct input 2 / FPGA input                                                                                                                                           | ADC0            | SCB1 |

| ADC3  | In   | ADC 0 direct input 3 / FPGA input                                                                                                                                           | ADC0            | SCB1 |

| ADC4  | In   | ADC 1 direct input 0 / FPGA input                                                                                                                                           | ADC1            | SCB2 |

| ADC5  | In   | ADC 1 direct input 1 / FPGA input                                                                                                                                           | ADC1            | SCB2 |

| ADC6  | In   | ADC 1 direct input 2 / FPGA input                                                                                                                                           | ADC1            | SCB3 |

| ADC7  | In   | ADC 1 direct input 3 / FPGA input                                                                                                                                           | ADC1            | SCB3 |

| ADC8  | In   | ADC 2 direct input 0 / FPGA input                                                                                                                                           | ADC2            | SCB4 |

| ADC9  | In   | ADC 2 direct input 1 / FPGA input                                                                                                                                           | ADC2            | SCB4 |

| ADC10 | In   | ADC 2 direct input 2 / FPGA input                                                                                                                                           | ADC2            | N/A  |

| ADC11 | In   | ADC 2 direct input 3 / FPGA input                                                                                                                                           | ADC2            | N/A  |

| CM0   | In   | SCB 0 / high side of current monitor / comparator<br>Positive input. See the Current Monitor section in the <i>SmartFusion</i><br><i>Programmable Analog User's Guide</i> . | ADC0            | SCB0 |

| CM1   | In   | SCB 1 / high side of current monitor / comparator. Positive input.                                                                                                          | ADC0            | SCB1 |

| CM2   | In   | SCB 2 / high side of current monitor / comparator. Positive input.                                                                                                          | ADC1            | SCB2 |

| CM3   | In   | SCB 3 / high side of current monitor / comparator. Positive input.                                                                                                          | ADC1            | SCB3 |

| CM4   | In   | SCB 4 / high side of current monitor / comparator. Positive input.                                                                                                          | ADC2            | SCB4 |

Note: Unused analog inputs should be grounded. This aids in shielding and prevents an undesired coupling path.

|            | TQ144             |  |

|------------|-------------------|--|

| Pin Number | A2F060 Function   |  |

| 1          | VCCPLL0           |  |

| 2          | VCOMPLA0          |  |

| 3          | GNDQ              |  |

| 4          | GFA2/IO42PDB5V0   |  |

| 5          | GFB2/IO42NDB5V0   |  |

| 6          | GFC2/IO41PDB5V0   |  |

| 7          | IO41NDB5V0        |  |

| 8          | VCC               |  |

| 9          | GND               |  |

| 10         | VCCFPGAIOB5       |  |

| 11         | IO38PDB5V0        |  |

| 12         | IO38NDB5V0        |  |

| 13         | IO36PDB5V0        |  |

| 14         | IO36NDB5V0        |  |

| 15         | GND               |  |

| 16         | GNDRCOSC          |  |

| 17         | VCCRCOSC          |  |

| 18         | MSS_RESET_N       |  |

| 19         | GPIO_0/IO33RSB4V0 |  |

| 20         | GPIO_1/IO32RSB4V0 |  |

| 21         | GPIO_2/IO31RSB4V0 |  |

| 22         | GPIO_3/IO30RSB4V0 |  |

| 23         | GPIO_4/IO29RSB4V0 |  |

| 24         | GND               |  |

| 25         | VCCMSSIOB4        |  |

| 26         | VCC               |  |

| 27         | GPIO_5/IO28RSB4V0 |  |

| 28         | GPIO_6/IO27RSB4V0 |  |

| 29         | GPIO_7/IO26RSB4V0 |  |

| 30         | GPIO_8/IO25RSB4V0 |  |

| 31         | VCCESRAM          |  |

| 32         | GNDSDD0           |  |

| 33         | VCC33SDD0         |  |

| 34         | VCC15A            |  |

| 35         | PCAP              |  |

| 36         | NCAP              |  |

| TQ144                      |                 |  |  |

|----------------------------|-----------------|--|--|

| Pin Number A2F060 Function |                 |  |  |

| 109                        | VPP             |  |  |

| 110                        | GNDQ            |  |  |

| 111                        | GCA1/IO20PDB0V0 |  |  |

| 112                        | GCA0/IO20NDB0V0 |  |  |

| 113                        | GCB1/IO19PDB0V0 |  |  |

| 114                        | GCB0/IO19NDB0V0 |  |  |

| 115                        | GCC1/IO18PDB0V0 |  |  |

| 116                        | GCC0/IO18NDB0V0 |  |  |

| 117                        | VCCFPGAIOB0     |  |  |

| 118                        | GND             |  |  |

| 119                        | VCC             |  |  |

| 120                        | IO14PDB0V0      |  |  |

| 121                        | IO14NDB0V0      |  |  |

| 122                        | IO13NSB0V0      |  |  |

| 123                        | IO11PDB0V0      |  |  |

| 124                        | IO11NDB0V0      |  |  |

| 125                        | IO09PDB0V0      |  |  |

| 126                        | IO09NDB0V0      |  |  |

| 127                        | VCCFPGAIOB0     |  |  |

| 128                        | GND             |  |  |

| 129                        | IO07PDB0V0      |  |  |

| 130                        | IO07NDB0V0      |  |  |

| 131                        | IO06PDB0V0      |  |  |

| 132                        | IO06NDB0V0      |  |  |

| 133                        | IO05PDB0V0      |  |  |

| 134                        | IO05NDB0V0      |  |  |

| 135                        | IO03PDB0V0      |  |  |

| 136                        | IO03NDB0V0      |  |  |

| 137                        | VCCFPGAIOB0     |  |  |

| 138                        | GND             |  |  |

| 139                        | VCC             |  |  |

| 140                        | IO01PDB0V0      |  |  |

| 141                        | IO01NDB0V0      |  |  |

| 142                        | IO00PDB0V0      |  |  |

| 143                        | IO00NDB0V0      |  |  |

| 144                        | GNDQ            |  |  |

| Pin  | CS288                 |                            |                            |  |

|------|-----------------------|----------------------------|----------------------------|--|

| No.  | A2F060 Function       | A2F200 Function            | A2F500 Function            |  |

| AA11 | ADC9                  | ADC6                       | ADC6                       |  |

| AA12 | ABPS1                 | ABPS7                      | ABPS7                      |  |

| AA13 | ADC6                  | TM2                        | TM2                        |  |

| AA14 | NC                    | ABPS4                      | ABPS4                      |  |

| AA15 | NC                    | SDD1                       | SDD1                       |  |

| AA16 | GNDVAREF              | GNDVAREF                   | GNDVAREF                   |  |

| AA17 | VAREFOUT              | VAREFOUT                   | VAREFOUT                   |  |

| AA18 | PU_N                  | PU_N                       | PU_N                       |  |

| AA19 | VCC33A                | VCC33A                     | VCC33A                     |  |

| AA20 | PTEM                  | PTEM                       | PTEM                       |  |

| AA21 | GND                   | GND                        | GND                        |  |

| B1   | GND                   | GND                        | GND                        |  |

| B21  | IO17PDB0V0            | GBB2/IO20NDB1V0            | GBB2/IO27NDB1V0            |  |

| C1   | EMC_DB[15]/IO45PDB5V0 | EMC_DB[15]/GAA2/IO71PDB5V0 | EMC_DB[15]/GAA2/IO88PDB5V0 |  |

| C3   | VCOMPLA0              | VCOMPLA                    | VCOMPLA0                   |  |

| C4   | VCCPLL0               | VCCPLL                     | VCCPLL0                    |  |

| C5   | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |  |

| C6   | EMC_AB[1]/IO04PPB0V0  | EMC_AB[1]/IO04PPB0V0       | EMC_AB[1]/IO06PPB0V0       |  |

| C7   | GND                   | GND                        | GND                        |  |

| C8   | EMC_OEN0_N/IO03NDB0V0 | EMC_OEN0_N/IO03NDB0V0      | EMC_OEN0_N/IO08NDB0V0      |  |

| C9   | EMC_AB[2]/IO05NDB0V0  | EMC_AB[2]/IO05NDB0V0       | EMC_AB[2]/IO09NDB0V0       |  |

| C10  | EMC_AB[5]/IO06PDB0V0  | EMC_AB[5]/IO06PDB0V0       | EMC_AB[5]/IO10PDB0V0       |  |

| C11  | VCCFPGAIOB0           | VCCFPGAIOB0                | VCCFPGAIOB0                |  |

| C12  | EMC_AB[9]/IO08PPB0V0  | EMC_AB[9]/IO08PPB0V0       | EMC_AB[9]/IO13PPB0V0       |  |

| C13  | EMC_AB[15]/IO11PPB0V0 | EMC_AB[15]/IO11PPB0V0      | EMC_AB[15]/IO15PPB0V0      |  |

| C14  | EMC_AB[19]/IO13PDB0V0 | EMC_AB[19]/IO13PDB0V0      | EMC_AB[19]/IO18PDB0V0      |  |

| C15  | GND                   | GND                        | GND                        |  |

| C16  | EMC_AB[22]/IO15NDB0V0 | EMC_AB[22]/IO15NDB0V0      | EMC_AB[22]/IO19NDB0V0      |  |

| C17  | EMC_AB[23]/IO15PDB0V0 | EMC_AB[23]/IO15PDB0V0      | EMC_AB[23]/IO19PDB0V0      |  |

| C18  | NC                    | NC                         | VCCPLL1                    |  |

| C19  | NC                    | NC                         | VCOMPLA1                   |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

| Pin FG256 |                   |                       |                       |

|-----------|-------------------|-----------------------|-----------------------|

| No.       | A2F060 Function   | A2F200 Function       | A2F500 Function       |

| M11       | ADC6              | TM2                   | TM2                   |

| M12       | ADC5              | CM2                   | CM2                   |

| M13       | SPI_0_SS/GPIO_19  | SPI_0_SS/GPIO_19      | SPI_0_SS/GPIO_19      |

| M14       | VCCMSSIOB2        | VCCMSSIOB2            | VCCMSSIOB2            |

| M15       | SPI_0_CLK/GPIO_18 | SPI_0_CLK/GPIO_18     | SPI_0_CLK/GPIO_18     |

| M16       | SPI_0_DI/GPIO_17  | SPI_0_DI/GPIO_17      | SPI_0_DI/GPIO_17      |

| N1        | GPIO_8/IO25RSB4V0 | MAC_RXD[1]/IO53RSB4V0 | MAC_RXD[1]/IO62RSB4V0 |

| N2        | VCCMSSIOB4        | VCCMSSIOB4            | VCCMSSIOB4            |

| N3        | VCC15A            | VCC15A                | VCC15A                |

| N4        | VCC33AP           | VCC33AP               | VCC33AP               |

| N5        | NC                | ABPS3                 | ABPS3                 |

| N6        | ADC4              | TM1                   | TM1                   |

| N7        | NC                | GND33ADC0             | GND33ADC0             |

| N8        | VCC33ADC0         | VCC33ADC1             | VCC33ADC1             |

| N9        | ADC8              | ADC5                  | ADC5                  |

| N10       | CM0               | CM3                   | CM3                   |

| N11       | GNDAQ             | GNDAQ                 | GNDAQ                 |

| N12       | VAREFOUT          | VAREFOUT              | VAREFOUT              |

| N13       | NC                | GNDSDD1               | GNDSDD1               |

| N14       | NC                | VCC33SDD1             | VCC33SDD1             |

| N15       | GND               | GND                   | GND                   |

| N16       | SPI_0_DO/GPIO_16  | SPI_0_DO/GPIO_16      | SPI_0_DO/GPIO_16      |

| P1        | GNDSDD0           | GNDSDD0               | GNDSDD0               |

| P2        | VCC33SDD0         | VCC33SDD0             | VCC33SDD0             |

| P3        | VCC33N            | VCC33N                | VCC33N                |

| P4        | GNDA              | GNDA                  | GNDA                  |

| P5        | GNDAQ             | GNDAQ                 | GNDAQ                 |

| P6        | NC                | CM1                   | CM1                   |

| P7        | NC                | ADC2                  | ADC2                  |

| P8        | NC                | VCC15ADC0             | VCC15ADC0             |

| P9        | ADC9              | ADC6                  | ADC6                  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

# 6 – Datasheet Information

### **List of Changes**

The following table shows important changes made in this document for each revision.

| Revision                       | Changes                                                                                                                                                                                                                                                                                                                        | Page  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Revision 13<br>(March 2015)    | Updated Unused MSS I/O Configuration information in "User I/O Naming Conventions" (SAR 62994).                                                                                                                                                                                                                                 | 5-7   |

|                                | Updated Table 2-90: "eNVM Block Timing, Worst Commercial Case Conditions: $T_J = 85^{\circ}$ C, VCC = 1.425 V".                                                                                                                                                                                                                | 2-76  |

|                                | Changed the maximum clock frequency for the control logic – 5 cycles to 50 MHz for A2F060 and A2F200 devices (SAR 63920).                                                                                                                                                                                                      |       |

|                                | Added the following Note:                                                                                                                                                                                                                                                                                                      |       |

|                                | "Moving from 5:1:1:1 mode to 6:1:1:1 mode results in throughput change that is dependent on the system functionality. When the Cortex-M3 code is executed from eNVM - with sequential firmware (sequential address reads), the throughput reduction can be around 10%" (SAR 63920).                                            |       |

| Revision 12<br>(November 2013) | CS288 package dimensions added to "SmartFusion cSoC Package Sizes Dimensions" table (SAR 43730).                                                                                                                                                                                                                               | 1-111 |

|                                | Added "Typical Programming and Erase Times" table (SAR 43732).                                                                                                                                                                                                                                                                 | 4-9   |

|                                | Definition of Ethernet MAC clarified in the "General Description" section (SAR 50083).                                                                                                                                                                                                                                         | 1-1   |

|                                | Clarified GC and GF global inputs in "Global I/O Naming Conventions" section and link to SF Fabric UG added (SAR 42802).                                                                                                                                                                                                       | 5-6   |

| Revision 11                    | Modified the description for VAREF0 in the "User-Defined Supply Pins" (SAR 30204).                                                                                                                                                                                                                                             | 5-5   |

| (September 2013)               | Updated the "Pin Assignment Tables" section with a note for A2F500, all packages with GCAx saying: "Signal assigned to those pins as a CLKBUF or CLKBUF_LVPECL or CLKBUF_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal (SAR 45985). | 5-18  |