Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Active                                                                       |

| Architecture            | MCU, FPGA                                                                    |

| Core Processor          | ARM® Cortex®-M3                                                              |

| Flash Size              | 512KB                                                                        |

| RAM Size                | 64KB                                                                         |

| Peripherals             | DMA, POR, WDT                                                                |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                         |

| Speed                   | 100MHz                                                                       |

| Primary Attributes      | ProASIC®3 FPGA, 500K Gates, 11520 D-Flip-Flops                               |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                           |

| Package / Case          | 288-TFBGA, CSPBGA                                                            |

| Supplier Device Package | 288-CSP (11x11)                                                              |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f500m3g-1csg288i |

|                         |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Microsemi**.

SmartFusion Customizable System-on-Chip (cSoC)

# SmartFusion cSoC Family Product Table

|                                    |                                                      | A2F060                                    |       |       | A2F        | 200        |       |       | A2F     | 500       |          |  |

|------------------------------------|------------------------------------------------------|-------------------------------------------|-------|-------|------------|------------|-------|-------|---------|-----------|----------|--|

| FPGA Fabric                        | TQ144                                                | CS288                                     | FG256 | PQ208 | CS288      | FG256      | FG484 | PQ208 | CS288   | FG256     | FG484    |  |

| System Gates                       |                                                      | 60,000                                    |       |       | 200        | ,000       |       |       | 500     | ,000      |          |  |

| Tiles (D-flip-flops)               |                                                      | 1,536                                     |       |       | 4,6        | 808        |       |       | 11,     | 520       |          |  |

| RAM Blocks (4,608 bits)            |                                                      | 8                                         |       |       | 8          | 3          |       |       | 2       | 4         |          |  |

|                                    |                                                      | A2F060                                    |       |       | A2F        | 200        |       |       | A2F500  |           |          |  |

| Microcontroller Subsystem (MSS)    | TQ144                                                | TQ144 CS288 FG256 PQ208 CS288 FG256 FG484 |       | PQ208 | CS288      | FG256      | FG484 |       |         |           |          |  |

| Flash (Kbytes)                     | 128                                                  |                                           |       | 256   |            |            |       |       | 51      | 12        |          |  |

| SRAM (Kbytes)                      | 16                                                   |                                           |       |       | 6          | 4          |       |       | 6       | 4         |          |  |

| Cortex-M3 processor with MPU       | Yes                                                  |                                           |       |       | Ye         | es         |       |       | Ye      | es        |          |  |

| 10/100 Ethernet MAC                | No                                                   |                                           |       |       | Ye         | es         |       |       | Ye      | es        |          |  |

| External Memory Controller (EMC)   | <ul> <li>26-/16-bit</li> <li>address/data</li> </ul> |                                           |       | 26-b  | oit addres | s,16-bit o | data  | -     | 26-/16- | bit addre | ess/data |  |

| DMA                                |                                                      | 8 Ch 8 Ch                                 |       |       |            | 8 Ch       |       |       |         |           |          |  |

| l <sup>2</sup> C                   | 2                                                    |                                           |       |       | 2          | 2          |       |       |         | 2         |          |  |

| SPI                                | 1                                                    |                                           | 2     | 1     |            | 2          |       | 1     | 1 2     |           |          |  |

| 16550 UART                         |                                                      | 2                                         |       | 2     |            |            |       |       | 2       | 2         |          |  |

| 32-Bit Timer                       |                                                      | 2                                         |       |       | 2          | 2          |       | 2     |         | 2         |          |  |

| PLL                                |                                                      | 1                                         |       |       |            | 1          |       | 1     | 2       | 1         | 2        |  |

| 32 KHz Low Power Oscillator        |                                                      | 1                                         |       |       | ,          | 1          |       |       |         | 1         |          |  |

| 100 MHz On-Chip RC Oscillator      |                                                      | 1                                         |       |       |            | 1          |       |       |         | 1         |          |  |

| Main Oscillator (32 KHz to 20 MHz) |                                                      | 1                                         |       |       |            | 1          |       |       |         | 1         |          |  |

|                                    |                                                      | A2F060                                    |       |       | A2F        | 200        |       |       | A2F     | 500       |          |  |

| Programmable Analog                | TQ144                                                | CS288                                     | FG256 | PQ208 | CS288      | FG256      | FG484 | PQ208 | CS288   | FG256     | FG484    |  |

| ADCs (8-/10-/12-bit SAR)           |                                                      | 1                                         |       | 2     |            | 2          |       |       | 2       |           | 3        |  |

| DACs (8-/16-/24-bit sigma-delta)   | 1                                                    |                                           |       | 2     | 2          |            |       | 2     |         | 3         |          |  |

| Signal Conditioning Blocks (SCBs)  |                                                      | 1                                         |       |       | 4          |            |       |       | 4       |           | 5        |  |

| Comparator*                        |                                                      | 2                                         |       |       | 8          |            |       |       | 8       |           |          |  |

| Current Monitors*                  | 1                                                    |                                           |       | 4     |            |            | 4     |       |         | 5         |          |  |

| Temperature Monitors*              | 1                                                    |                                           |       | 4     |            |            | 4     |       |         | 5         |          |  |

| Bipolar High Voltage Monitors*     |                                                      | 2                                         |       |       | 8          | 3          |       | 8     |         |           | 10       |  |

Note: \*These functions share I/O pins and may not all be available at the same time. See the "Analog Front-End Overview" section in the http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130925 for details.

# Package I/Os: MSS + FPGA I/Os

| Device                  | A2F060 <sup>1</sup> |                 |                 |       | A2F   | <b>200</b> <sup>2</sup> |       | A2F500 <sup>2</sup> |       |       |       |

|-------------------------|---------------------|-----------------|-----------------|-------|-------|-------------------------|-------|---------------------|-------|-------|-------|

| Package                 | TQ144               | CS288           | FG256           | PQ208 | CS288 | FG256                   | FG484 | PQ208               | CS288 | FG256 | FG484 |

| Direct Analog Inputs    | 11                  | 11              | 11              | 8     | 8     | 8                       | 8     | 8                   | 8     | 8     | 12    |

| Shared Analog Inputs    | 4                   | 4               | 4               | 16    | 16    | 16                      | 16    | 16                  | 16    | 16    | 20    |

| Total Analog Inputs     | 15                  | 15              | 15              | 24    | 24    | 24                      | 24    | 24                  | 24    | 24    | 32    |

| Analog Outputs          | 1                   | 1               | 1               | 1     | 2     | 2                       | 2     | 1                   | 2     | 2     | 3     |

| MSS I/Os <sup>3,4</sup> | 21 <sup>5</sup>     | 28 <sup>5</sup> | 26 <sup>5</sup> | 22    | 31    | 25                      | 41    | 22                  | 31    | 25    | 41    |

| FPGA I/Os               | 33 <sup>6</sup>     | 68              | 66              | 66    | 78    | 66                      | 94    | 66 <sup>6</sup>     | 78    | 66    | 128   |

| Total I/Os              | 70                  | 112             | 108             | 113   | 135   | 117                     | 161   | 113                 | 135   | 117   | 204   |

### Notes:

1. There are no LVTTL capable direct inputs available on A2F060 devices.

2. These pins are shared between direct analog inputs to the ADCs and voltage/current/temperature monitors.

3. 16 MSS I/Os are multiplexed and can be used as FPGA I/Os, if not needed for MSS. These I/Os support Schmitt triggers and support only LVTTL and LVCMOS (1.5 / 1.8 / 2.5, 3.3 V) standards.

4. 9 MSS I/Os are primarily for 10/100 Ethernet MAC and are also multiplexed and can be used as FPGA I/Os if Ethernet MAC is not used in a design. These I/Os support Schmitt triggers and support only LVTTL and LVCMOS (1.5 / 1.8 / 2.5, 3.3 V standards.

5. 10/100 Ethernet MAC is not available on A2F060.

6. EMC is not available on the A2F500 PQ208 and A2F060 TQ144 package.

### Table 1 • SmartFusion cSoC Package Sizes Dimensions

| Package                         | TQ144   | PQ208   | CS288   | FG256   | FG484   |

|---------------------------------|---------|---------|---------|---------|---------|

| Length × Width (mm\mm)          | 20 × 20 | 28 × 28 | 11 × 11 | 17 × 17 | 23 × 23 |

| Nominal Area (mm <sup>2</sup> ) | 400     | 784     | 121     | 289     | 529     |

| Pitch (mm)                      | 0.5     | 0.5     | 0.5     | 1.0     | 1.0     |

| Height (mm)                     | 1.40    | 3.40    | 1.05    | 1.60    | 2.23    |

# SmartFusion cSoC Device Status

| Device | Status                                 |

|--------|----------------------------------------|

| A2F060 | Preliminary: CS288, FG256, TQ144       |

| A2F200 | Production: CS288, FG256, FG484, PQ208 |

| A2F500 | Production: CS288, FG256, FG484, PQ208 |

This enables reduction or complete removal of expensive voltage monitor and brownout detection devices from the PCB design. Flash-based SmartFusion cSoCs simplify total system design and reduce cost and design risk, while increasing system reliability.

### Immunity to Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O configuration behavior in an unpredictable way.

Another source of radiation-induced firm errors is alpha particles. For alpha radiation to cause a soft or firm error, its source must be in very close proximity to the affected circuit. The alpha source must be in the package molding compound or in the die itself. While low-alpha molding compounds are being used increasingly, this helps reduce but does not entirely eliminate alpha-induced firm errors.

Firm errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not occur in SmartFusion cSoCs. Once it is programmed, the flash cell configuration element of SmartFusion cSoCs cannot be altered by high energy neutrons and is therefore immune to errors from them. Recoverable (or soft) errors occur in the user data SRAMs of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

## Specifying I/O States During Programming

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User's Guide* for more information.

Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

The I/Os are controlled by the JTAG Boundary Scan register during programming, except for the analog pins (AC, AT and AV). The Boundary Scan register of the AG pin can be used to enable/disable the gate driver in software v9.0.

- 1. Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- 2. From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the Specify I/O States During Programming button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-1 on page 1-4).

- Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

1 - I/O is set to drive out logic High

0 - I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming

Z -Tri-State: I/O is tristated

# 2 – SmartFusion DC and Switching Characteristics

# **General Specifications**

## **Operating Conditions**

Stresses beyond the operating conditions listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-3 on page 2-3 is not implied.

| Symbol                        | Parameter                                                | Limits                                                                                                                                                          | Units |

|-------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| VCC                           | DC core supply voltage                                   | –0.3 to 1.65                                                                                                                                                    | V     |

| VJTAG                         | JTAG DC voltage                                          | –0.3 to 3.75                                                                                                                                                    | V     |

| VPP                           | Programming voltage                                      | –0.3 to 3.75                                                                                                                                                    | V     |

| VCCPLLx                       | Analog power supply (PLL)                                | –0.3 to 1.65                                                                                                                                                    | V     |

| VCCFPGAIOBx                   | DC FPGA I/O buffer supply voltage                        | –0.3 to 3.75                                                                                                                                                    | V     |

| VCCMSSIOBx                    | DC MSS I/O buffer supply voltage                         | –0.3 to 3.75                                                                                                                                                    | V     |

| VI                            | I/O input voltage                                        | –0.3 V to 3.6 V                                                                                                                                                 | V     |

|                               |                                                          | (when I/O hot insertion mode is enabled)<br>-0.3 V to (VCCxxxxIOBx + 1 V) or 3.6 V,<br>whichever voltage is lower (when I/O hot-<br>insertion mode is disabled) |       |

| VCC33A                        | Analog clean 3.3 V supply to the analog circuitry        | -0.3 to 3.75                                                                                                                                                    | V     |

| VCC33ADCx                     | Analog 3.3 V supply to ADC                               | -0.3 to 3.75                                                                                                                                                    | V     |

| VCC33AP                       | Analog clean 3.3 V supply to the charge pump             | -0.3 to 3.75                                                                                                                                                    | V     |

| VCC33SDDx                     | Analog 3.3 V supply to the sigma-delta DAC               | -0.3 to 3.75                                                                                                                                                    | V     |

| VAREFx                        | Voltage reference for ADC                                | 1.0 to 3.75                                                                                                                                                     | V     |

| VCCRCOSC                      | Analog supply to the integrated RC oscillator            | -0.3 to 3.75                                                                                                                                                    | V     |

| VDDBAT                        | External battery supply                                  | -0.3 to 3.75                                                                                                                                                    | V     |

| VCCMAINXTAL                   | Analog supply to the main crystal oscillator             | -0.3 to 3.75                                                                                                                                                    | V     |

| VCCLPXTAL                     | Analog supply to the low power 32 kHz crystal oscillator | –0.3 to 3.75                                                                                                                                                    | V     |

| VCCENVM                       | Embedded nonvolatile memory supply                       | -0.3 to 1.65                                                                                                                                                    | V     |

| VCCESRAM                      | Embedded SRAM supply                                     | –0.3 to 1.65                                                                                                                                                    | V     |

| VCC15A                        | Analog 1.5 V supply to the analog circuitry              | -0.3 to 1.65                                                                                                                                                    | V     |

| VCC15ADCx                     | Analog 1.5 V supply to the ADC                           | -0.3 to 1.65                                                                                                                                                    | V     |

| T <sub>STG</sub> <sup>1</sup> | Storage temperature                                      | –65 to +150                                                                                                                                                     | °C    |

| T <sub>J</sub> <sup>1</sup>   | Junction temperature                                     | 125                                                                                                                                                             | °C    |

#### Table 2-1 • Absolute Maximum Ratings

Notes:

1. For flash programming and retention maximum limits, refer to Table 2-4 on page 2-4. For recommended operating conditions, refer to Table 2-3 on page 2-3.

2. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-5 on page 2-4.

### Standby Mode

$P_{DYN} = P_{RC-OSC} + P_{LPXTAL-OSC}$

### Time Keeping Mode

$P_{DYN} = P_{LPXTAL-OSC}$

### **Global Clock Dynamic Contribution**—**P**<sub>CLOCK</sub>

#### SoC Mode

$P_{CLOCK} = (P_{AC1} + N_{SPINE} * P_{AC2} + N_{ROW} * PAC3 + N_{S-CELL} * P_{AC4}) * F_{CLK}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Device Architecture" chapter of the *SmartFusion FPGA Fabric User's Guide.*

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Device Architecture" chapter of the *SmartFusion FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

#### Standby Mode and Time Keeping Mode

$P_{CLOCK} = 0 W$

### Sequential Cells Dynamic Contribution—P<sub>S-CELL</sub>

#### SoC Mode

$P_{S-CELL} = N_{S-CELL} * (P_{AC5} + (\alpha_1 / 2) * P_{AC6}) * F_{CLK}$

$N_{S-CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Time Keeping Mode

$P_{S-CELL} = 0 W$

### Combinatorial Cells Dynamic Contribution—P<sub>C-CELL</sub>

#### SoC Mode

$P_{C-CELL} = N_{C-CELL} * (\alpha_1 / 2) * P_{AC7} * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Time Keeping Mode

$P_{C-CELL} = 0 W$

### Routing Net Dynamic Contribution—P<sub>NET</sub>

### SoC Mode

$\mathsf{P}_{\mathsf{NET}} = (\mathsf{N}_{\mathsf{S}\text{-}\mathsf{CELL}} + \mathsf{N}_{\mathsf{C}\text{-}\mathsf{CELL}}) * (\alpha_1 / 2) * \mathsf{P}_{\mathsf{AC8}} * \mathsf{F}_{\mathsf{CLK}}$

N<sub>S-CELL</sub> is the number VersaTiles used as sequential modules in the design.

$N_{C\mbox{-}C\mbox{-}E\mbox{LL}}$  is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-17 on page 2-18.

F<sub>CLK</sub> is the frequency of the clock driving the logic including these nets.

# **User I/O Characteristics**

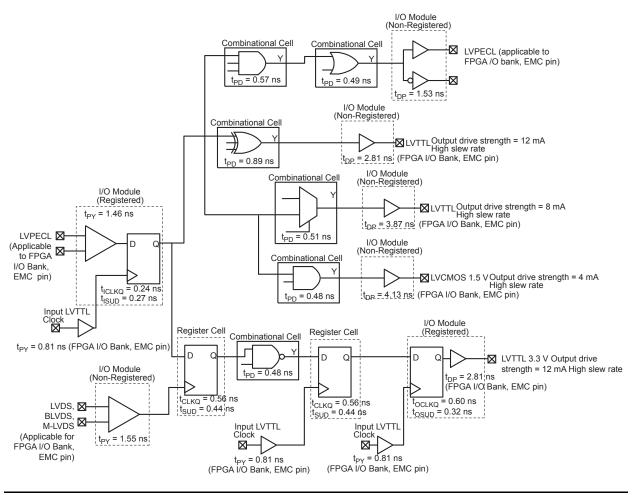

# **Timing Model**

Figure 2-2 • Timing Model Operating Conditions: –1 Speed, Commercial Temperature Range (T<sub>J</sub> = 85°C), Worst Case VCC = 1.425 V

### Timing Characteristics

### Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 7.20            | 0.04             | 0.97            | 0.39              | 7.34            | 6.18            | 2.52            | 2.46            | 9.39             | 8.23             | ns    |

|                   | -1             | 0.50              | 6.00            | 0.03             | 0.81            | 0.32              | 6.11            | 5.15            | 2.10            | 2.05            | 7.83             | 6.86             | ns    |

| 8 mA              | Std.           | 0.60              | 4.64            | 0.04             | 0.97            | 0.39              | 4.73            | 3.84            | 2.85            | 3.02            | 6.79             | 5.90             | ns    |

|                   | -1             | 0.50              | 3.87            | 0.03             | 0.81            | 0.32              | 3.94            | 3.20            | 2.37            | 2.52            | 5.65             | 4.91             | ns    |

| 12 mA             | Std.           | 0.60              | 3.37            | 0.04             | 0.97            | 0.39              | 3.43            | 2.67            | 3.07            | 3.39            | 5.49             | 4.73             | ns    |

|                   | -1             | 0.50              | 2.81            | 0.03             | 0.81            | 0.32              | 2.86            | 2.23            | 2.55            | 2.82            | 4.58             | 3.94             | ns    |

| 16 mA             | Std.           | 0.60              | 3.18            | 0.04             | 0.97            | 0.39              | 3.24            | 2.43            | 3.11            | 3.48            | 5.30             | 4.49             | ns    |

|                   | -1             | 0.50              | 2.65            | 0.03             | 0.81            | 0.32              | 2.70            | 2.03            | 2.59            | 2.90            | 4.42             | 3.74             | ns    |

| 24 mA             | Std.           | 0.60              | 2.93            | 0.04             | 0.97            | 0.39              | 2.99            | 2.03            | 3.17            | 3.83            | 5.05             | 4.09             | ns    |

|                   | -1             | 0.50              | 2.45            | 0.03             | 0.81            | 0.32              | 2.49            | 1.69            | 2.64            | 3.19            | 4.21             | 3.41             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### Table 2-39 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 9.75            | 0.04             | 0.97            | 0.39              | 9.93            | 8.22            | 2.52            | 2.31            | 11.99            | 10.28            | ns    |

|                   | -1             | 0.50              | 8.12            | 0.03             | 0.81            | 0.32              | 8.27            | 6.85            | 2.10            | 1.93            | 9.99             | 8.57             | ns    |

| 8 mA              | Std.           | 0.60              | 6.96            | 0.04             | 0.97            | 0.39              | 7.09            | 5.85            | 2.84            | 2.87            | 9.15             | 7.91             | ns    |

|                   | -1             | 0.50              | 5.80            | 0.03             | 0.81            | 0.32              | 5.91            | 4.88            | 2.37            | 2.39            | 7.62             | 6.59             | ns    |

| 12 mA             | Std.           | 0.60              | 5.35            | 0.04             | 0.97            | 0.39              | 5.45            | 4.58            | 3.06            | 3.23            | 7.51             | 6.64             | ns    |

|                   | -1             | 0.50              | 4.46            | 0.03             | 0.81            | 0.32              | 4.54            | 3.82            | 2.55            | 2.69            | 6.26             | 5.53             | ns    |

| 16 mA             | Std.           | 0.60              | 5.01            | 0.04             | 0.97            | 0.39              | 5.10            | 4.30            | 3.11            | 3.32            | 7.16             | 6.36             | ns    |

|                   | -1             | 0.50              | 4.17            | 0.03             | 0.81            | 0.32              | 4.25            | 3.58            | 2.59            | 2.77            | 5.97             | 5.30             | ns    |

| 24 mA             | Std.           | 0.60              | 4.67            | 0.04             | 0.97            | 0.39              | 4.75            | 4.28            | 3.16            | 3.66            | 6.81             | 6.34             | ns    |

|                   | -1             | 0.50              | 3.89            | 0.03             | 0.81            | 0.32              | 3.96            | 3.57            | 2.64            | 3.05            | 5.68             | 5.28             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### Table 2-40 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 8 mA              | Std.           | 0.22              | 2.31            | 0.09             | 0.94            | 1.30             | 0.22              | 2.35            | 1.86            | 2.20            | 2.45            | ns    |

|                   | -1             | 0.18              | 1.92            | 0.07             | 0.78            | 1.09             | 0.18              | 1.96            | 1.55            | 1.83            | 2.04            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Microsemi 5

SmartFusion DC and Switching Characteristics

### Table 2-52 • 1.8 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to MSS I/O Banks

|                   | pplicable      |                   | Dunks           |                  |                 |                  |                   |                 |                 |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>Zł</sub> |

| 4 mA              | Std.           | 0.22              | 2.77            | 0.09             | 1.09            | 1.64             | 0.22              | 2.82            | 2.7             |

| ength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> |

|-------|-------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|

| A     | Std.  | 0.22              | 2.77            | 0.09             | 1.09            | 1.64             | 0.22              | 2.82            | 2.72            | 2.21            |

|       | –1    | 0.18              | 2.31            | 0.07             | 0.91            | 1.37             | 0.18              | 2.35            | 2.27            | 1.84            |

|       |       |                   |                 |                  |                 |                  |                   |                 |                 |                 |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

Units

ns

ns

t<sub>HZ</sub>

2.25

1.87

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| tOESUD                | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                 | К, Н                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | К, Н                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

### Table 2-69 • Parameter Definition and Measuring Nodes

\* See Figure 2-14 on page 2-44 for more information.

# 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

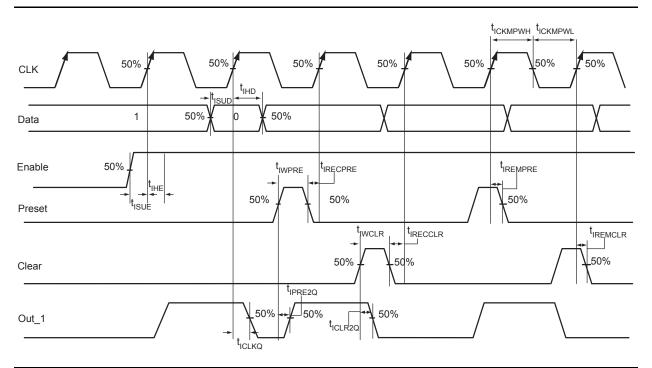

## Input Register

### **Timing Characteristics**

# Table 2-71 • Input Data Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.24 | 0.29 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.27 | 0.32 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.38 | 0.45 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.46 | 0.55 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.46 | 0.55 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.23 | 0.27 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.23 | 0.27 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.22 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.22 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.36 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.32 | ns    |

*Note:* For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

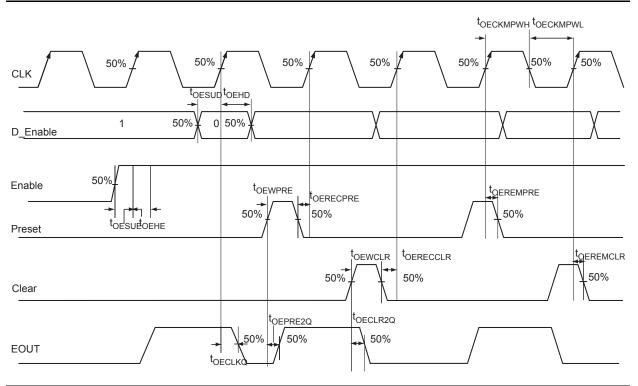

### **Output Enable Register**

Figure 2-18 • Output Enable Register Timing Diagram

### **Timing Characteristics**

Table 2-73 • Output Enable Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.45 | 0.54 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.32 | 0.38 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.53 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.68 | 0.81 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.68 | 0.81 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.23 | 0.27 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.23 | 0.27 | ns    |

| tOEWCLR               | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.22 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.22 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.36 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.32 | 0.32 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## **Timing Characteristics**

|                    | mercial-Case Conditions   | <b>,</b>        | 1    |      |       |

|--------------------|---------------------------|-----------------|------|------|-------|

| Combinatorial Cell | Equation                  | Parameter       | -1   | Std. | Units |

| INV                | Y = !A                    | t <sub>PD</sub> | 0.41 | 0.49 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.48 | 0.57 | ns    |

| NAND2              | Y = !(A ⋅ B)              | t <sub>PD</sub> | 0.48 | 0.57 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.49 | 0.59 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.49 | 0.59 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 0.75 | 0.90 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 0.71 | 0.85 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 0.89 | 1.07 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 0.51 | 0.62 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 0.57 | 0.68 | ns    |

#### Table 2-78 • Combinatorial Cell Propagation Delays Worst Commercial-Case Conditions: T = 85°C. Worst-Case VCC = 1.425 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### VersaTile Specifications as a Sequential Module

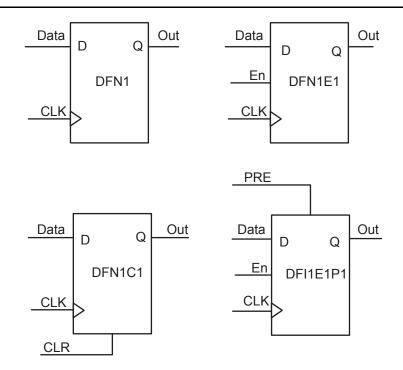

The SmartFusion library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the *IGLOO/e, Fusion, ProASIC3/E, and SmartFusion Macro Library Guide*.

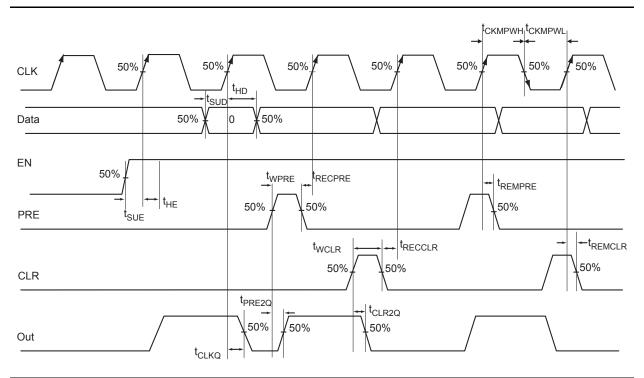

Figure 2-25 • Sample of Sequential Cells

### **Timing Characteristics**

### Table 2-79 • Register Delays

### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.56 | 0.67 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.44 | 0.52 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.46 | 0.55 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.41 | 0.49 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.41 | 0.49 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.23 | 0.27 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | 0.27 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.22 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.22 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.32 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.36 | ns    |

*Note:* For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

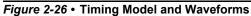

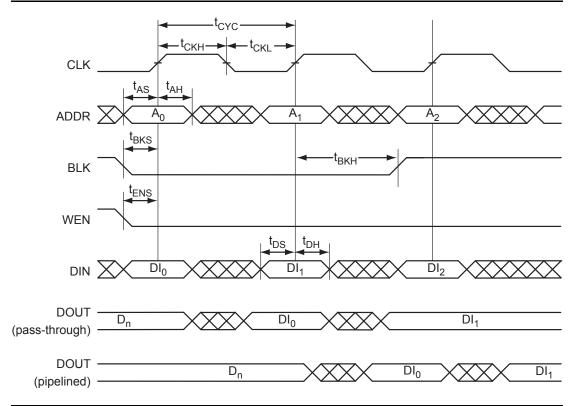

Figure 2-32 • RAM Write, Output Retained. Applicable to both RAM4K9 and RAM512x18.

Figure 2-33 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 only.

# **Serial Peripheral Interface (SPI) Characteristics**

This section describes the DC and switching of the SPI interface. Unless otherwise noted, all output characteristics given for a 35 pF load on the pins and all sequential timing characteristics are related to SPI\_x\_CLK. For timing parameter definitions, refer to Figure 2-47 on page 2-90.

| Symbol | Description and Condition                                      | A2F060 | A2F200 | A2F500 | Unit |  |  |

|--------|----------------------------------------------------------------|--------|--------|--------|------|--|--|

| sp1    | SPI_x_CLK minimum period                                       |        |        | L      |      |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 20     | NA     | 20     | ns   |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 40     | 40     | 40     | ns   |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 80     | 80     | 80     | ns   |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.64   | 0.64   | 0.64   | μs   |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 1.28   | 1.28   | 1.28   | μs   |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 2.56   | 2.56   | 2.56   | μs   |  |  |

| sp2    | SPI_x_CLK minimum pulse width high                             |        |        |        |      |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | us   |  |  |

| sp3    | SPI_x_CLK minimum pulse width low                              |        |        |        |      |  |  |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |  |  |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |  |  |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |  |  |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |  |  |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |  |  |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |  |  |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |  |  |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | μs   |  |  |

| sp4    | SPI_x_CLK, SPI_x_DO, SPI_x_SS rise time (10%-90%) <sup>1</sup> | 4.7    | 4.7    | 4.7    | ns   |  |  |

| sp5    | SPI_x_CLK, SPI_x_DO, SPI_x_SS fall time (10%-90%) <sup>1</sup> | 3.4    | 3.4    | 3.4    | ns   |  |  |

### Table 2-100 • SPI Characteristics

Commercial Case Conditions: T<sub>J</sub> = 85°C, VDD = 1.425 V, -1 Speed Grade

Notes:

These values are provided for a load of 35 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

2. For allowable pclk configurations, refer to the Serial Peripheral Interface Controller section in the SmartFusion Microcontroller Subsystem User's Guide.

|            | TQ144             |

|------------|-------------------|

| Pin Number | A2F060 Function   |

| 1          | VCCPLL0           |

| 2          | VCOMPLA0          |

| 3          | GNDQ              |

| 4          | GFA2/IO42PDB5V0   |

| 5          | GFB2/IO42NDB5V0   |

| 6          | GFC2/IO41PDB5V0   |

| 7          | IO41NDB5V0        |

| 8          | VCC               |

| 9          | GND               |

| 10         | VCCFPGAIOB5       |

| 11         | IO38PDB5V0        |

| 12         | IO38NDB5V0        |

| 13         | IO36PDB5V0        |

| 14         | IO36NDB5V0        |

| 15         | GND               |

| 16         | GNDRCOSC          |

| 17         | VCCRCOSC          |

| 18         | MSS_RESET_N       |

| 19         | GPIO_0/IO33RSB4V0 |

| 20         | GPIO_1/IO32RSB4V0 |

| 21         | GPIO_2/IO31RSB4V0 |

| 22         | GPIO_3/IO30RSB4V0 |

| 23         | GPIO_4/IO29RSB4V0 |

| 24         | GND               |

| 25         | VCCMSSIOB4        |

| 26         | VCC               |

| 27         | GPIO_5/IO28RSB4V0 |

| 28         | GPIO_6/IO27RSB4V0 |

| 29         | GPIO_7/IO26RSB4V0 |

| 30         | GPIO_8/IO25RSB4V0 |

| 31         | VCCESRAM          |

| 32         | GNDSDD0           |

| 33         | VCC33SDD0         |

| 34         | VCC15A            |

| 35         | PCAP              |

| 36         | NCAP              |

# PQ208

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

|            | FG484                     |                           |  |  |

|------------|---------------------------|---------------------------|--|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |  |

| F17        | NC                        | IO25PPB1V0                |  |  |

| F18        | VCCFPGAIOB1               | VCCFPGAIOB1               |  |  |

| F19        | IO23NDB1V0                | IO28NDB1V0                |  |  |

| F20        | NC                        | IO31PDB1V0                |  |  |

| F21        | NC                        | IO31NDB1V0                |  |  |

| F22        | IO22PDB1V0                | IO32PDB1V0                |  |  |

| G1         | GND                       | GND                       |  |  |

| G2         | GFB0/IO65NPB5V0           | GFB0/IO82NPB5V0           |  |  |

| G3         | EMC_DB[9]/GEC1/IO63PDB5V0 | EMC_DB[9]/GEC1/IO80PDB5V0 |  |  |

| G4         | GFC1/IO66PPB5V0           | GFC1/IO83PPB5V0           |  |  |

| G5         | EMC_DB[11]/IO69PPB5V0     | EMC_DB[11]/IO86PPB5V0     |  |  |

| G6         | GNDQ                      | GNDQ                      |  |  |

| G7         | NC                        | NC                        |  |  |

| G8         | GND                       | GND                       |  |  |

| G9         | VCCFPGAIOB0               | VCCFPGAIOB0               |  |  |

| G10        | GND                       | GND                       |  |  |

| G11        | VCCFPGAIOB0               | VCCFPGAIOB0               |  |  |

| G12        | GND                       | GND                       |  |  |

| G13        | VCCFPGAIOB0               | VCCFPGAIOB0               |  |  |

| G14        | GND                       | GND                       |  |  |

| G15        | VCCFPGAIOB0               | VCCFPGAIOB0               |  |  |

| G16        | GNDQ                      | GNDQ                      |  |  |

| G17        | NC                        | IO26PDB1V0                |  |  |

| G18        | NC                        | IO26NDB1V0                |  |  |

| G19        | GCA2/IO23PDB1V0           | GCA2/IO28PDB1V0 *         |  |  |

| G20        | IO24NDB1V0                | IO33NDB1V0                |  |  |

| G21        | GCB2/IO24PDB1V0           | GCB2/IO33PDB1V0           |  |  |

| G22        | GND                       | GND                       |  |  |

| H1         | EMC_DB[7]/GEB1/IO62PDB5V0 | EMC_DB[7]/GEB1/IO79PDB5V0 |  |  |

| H2         | VCCFPGAIOB5               | VCCFPGAIOB5               |  |  |

| H3         | EMC_DB[8]/GEC0/IO63NDB5V0 | EMC_DB[8]/GEC0/IO80NDB5V0 |  |  |

| H4         | GND                       | GND                       |  |  |

| H5         | GFC0/IO66NPB5V0           | GFC0/IO83NPB5V0           |  |  |

| H6         | GFA1/IO64PDB5V0           | GFA1/IO81PDB5V0           |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

| Revision                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page         |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 8<br>(continued)   | The description of "In-application programming (IAP)" methodology was changed to state the difference for A2F060 and A2F500 compared to A2F200 (SAR 37808).                                                                                                                                                                                                                                                                                                                                 | 4-7          |

|                             | The "Global I/O Naming Conventions" section is new (SARs 28996, 31147). The description for IO "User Pins" was revised accordingly and moved out of the table and into a new section: "User I/O Naming Conventions".                                                                                                                                                                                                                                                                        | 5-6, 5-6     |

|                             | The descriptions for "MAINXIN" and "MAINXOUT" were revised to state how they should be handled if using an external RC network or clock input (SAR 32594).                                                                                                                                                                                                                                                                                                                                  | 5-8          |

|                             | The description and type was revised for the "MSS_RESET_N" pin (SAR 34133).                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-9          |

|                             | The "TQ144" section and pin table for A2F060 are new (SAR 36246).                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-18         |

| Revision 7<br>(August 2011) | The title of the datasheet was changed from SmartFusion Intelligent Mixed Signal FPGAs to SmartFusion Customizable System-on-Chip (cSoC). Terminology throughout was changed accordingly. The term cSoC defines a category of devices that include at least FPGA fabric and a processor subsystem of some sort. It can also include any of the following: analog, SerDes, ASIC blocks, customer specific IP, or application-specific IP. SmartFusion is Microsemi's first cSoC (SAR 33071). | N/A          |

|                             | The "SmartFusion cSoC Family Product Table" was revised to remove the note stating that the A2F060 device is under definition and subject to change (SAR 33070). A note was added for EMC, stating that it is not available on A2F500 for the PQ208 package (SAR 33041).                                                                                                                                                                                                                    | II           |

|                             | The "SmartFusion cSoC Device Status" table was revised. The status for A2F060 CS288 and FG256 moved from Advance to Preliminary. A2F200 PQ208 and A2F500 PQ208 moved from Advance to Production (SAR 33069).                                                                                                                                                                                                                                                                                | Ш            |

|                             | The "Package I/Os: MSS + FPGA I/Os" table was revised. The number of direct analog inputs for A2F060 packages increased from 6 to 11. The number of MSS I/Os for the A2F060 FG256 package increased from 25 to 26 (SAR 33070). A note was added stating that EMC is not available for the A2F500 PQ208 package (SAR 33041).                                                                                                                                                                 | III          |

|                             | The note associated with the "SmartFusion cSoC System Architecture" diagram was corrected from "Architecture for A2F500" to "Architecture for A2F200" (SAR 32578).                                                                                                                                                                                                                                                                                                                          | V            |

|                             | The Licensed DPA Logo was added to the "Product Ordering Codes" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 32151).                                                                                                                                                                                                                                                                   | VI           |

|                             | The "Security" section and "Secure Programming" section were updated to clarify that although no existing security measures can give an absolute guarantee, SmartFusion cSoCs implement the best security available in the industry (SAR 32865).                                                                                                                                                                                                                                            | 1-2, 4-9     |

|                             | Storage temperature, $T_{STG}$ , and junction temperature, $T_J$ , were added to Table 2-1 • Absolute Maximum Ratings (SAR 30863).                                                                                                                                                                                                                                                                                                                                                          | 2-1          |

|                             | AC/DC characteristics for A2F060 were added to the "SmartFusion DC and Switching Characteristics" chapter (SAR 33132). The following tables were updated:                                                                                                                                                                                                                                                                                                                                   |              |

|                             | Table 2-14 • Different Components Contributing to Dynamic Power Consumption inSmartFusion cSoCs                                                                                                                                                                                                                                                                                                                                                                                             | 2-12         |

|                             | Table 2-15 • Different Components Contributing to the Static Power Consumption inSmartFusion cSoCs                                                                                                                                                                                                                                                                                                                                                                                          | 2-13         |

|                             | Table 2-90 • eNVM Block Timing, Worst Commercial Case Conditions: T_J = 85°C, VCC = 1.425 V                                                                                                                                                                                                                                                                                                                                                                                                 | 2-76         |

|                             | Table 2-98 • Analog Sigma-Delta DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-85<br>2-89 |

|                             | Table 2-100 • SPI Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                 | Page             |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 3                 | Two notes were added to the "Supply Pins" table (SAR 27109):                                                                                                                                                                                                                                                                            | 5-1              |

| (continued)                | <ol> <li>The following supplies should be connected together while following proper noise<br/>filtering practices: VCC33A, VCC33ADCx, VCC33AP, VCC33SDDx, VCCMAINXTAL,<br/>and VCCLPXTAL.</li> </ol>                                                                                                                                    |                  |

|                            | <ol> <li>The following 1.5 V supplies should be connected together while following proper<br/>noise filtering practices: VCC, VCC15A, and VCC15ADCx.</li> </ol>                                                                                                                                                                         |                  |

|                            | The descriptions for the "VCC33N", "NCAP", and "PCAP" pins were revised to include information on what to do if analog SCB features and SDDs are not used (SAR 26744).                                                                                                                                                                  | 5-2, 5-9,<br>5-9 |

|                            | Information was added to the "User Pins" table regarding tristating of used and unused GPIO pins. The IO portion of the table was revised to state that unused I/O pins are disabled by Libero IDE software and include a weak pull-up resistor (SAR 26890). Information was added regarding behavior of used I/O pins during power-up. | 5-6              |

|                            | The type for "EMC_RW_N" was changed from In/out to Out (SAR 25113).                                                                                                                                                                                                                                                                     | 5-12             |

|                            | A note was added to the "Analog Front-End (AFE)" table stating that unused analog inputs should be grounded (SAR 26744).                                                                                                                                                                                                                | 5-14             |

|                            | The "TQ144" section is new, with pin tables for A2F200 and A2F500 (SAR 27044).                                                                                                                                                                                                                                                          | 5-18             |

|                            | The "FG256" pin table was replaced and now includes "Handling When Unused" information (SAR 27709).                                                                                                                                                                                                                                     | 5-42             |

| Revision 2<br>(May 2010)   | Embedded nonvolatile flash memory (eNVM) was changed from "64 to 512 Kbytes" to "128 to 512 Kbytes" in the "Microcontroller Subsystem (MSS)" section and "SmartFusion cSoC Family Product Table" (SAR 26005).                                                                                                                           | I, II            |

|                            | The main oscillator range of values was changed to "32 KHz to 20 MHz" in the "Microcontroller Subsystem (MSS)" section and the "SmartFusion cSoC Family Product Table" (SAR 24906).                                                                                                                                                     | I, II            |

|                            | The value for $t_{PD}$ was changed from 50 ns to 15 ns for the high-speed voltage comparators listed in the "Analog Front-End (AFE)" section (SAR 26005).                                                                                                                                                                               | I                |

|                            | The number of PLLs for A2F200 was changed from 2 to 1 in the "SmartFusion cSoC Family Product Table" (SAR 25093).                                                                                                                                                                                                                       | П                |

|                            | Values for direct analog input, total analog input, and total I/Os were updated for the FG256 package, A2F060, in the "Package I/Os: MSS + FPGA I/Os" table. The Max. column was removed from the table (SAR 26005).                                                                                                                    | Ш                |

|                            | The Speed Grade section of the "Product Ordering Codes" table was revised (SAR 25257).                                                                                                                                                                                                                                                  | VI               |