Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

-XF

| Details                 |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Active                                                                     |

| Architecture            | MCU, FPGA                                                                  |

| Core Processor          | ARM® Cortex®-M3                                                            |

| Flash Size              | 512KB                                                                      |

| RAM Size                | 64KB                                                                       |

| Peripherals             | DMA, POR, WDT                                                              |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                       |

| Speed                   | 100MHz                                                                     |

| Primary Attributes      | ProASIC®3 FPGA, 500K Gates, 11520 D-Flip-Flops                             |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                            |

| Package / Case          | 256-LBGA                                                                   |

| Supplier Device Package | 256-FPBGA (17x17)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f500m3g-1fg256 |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

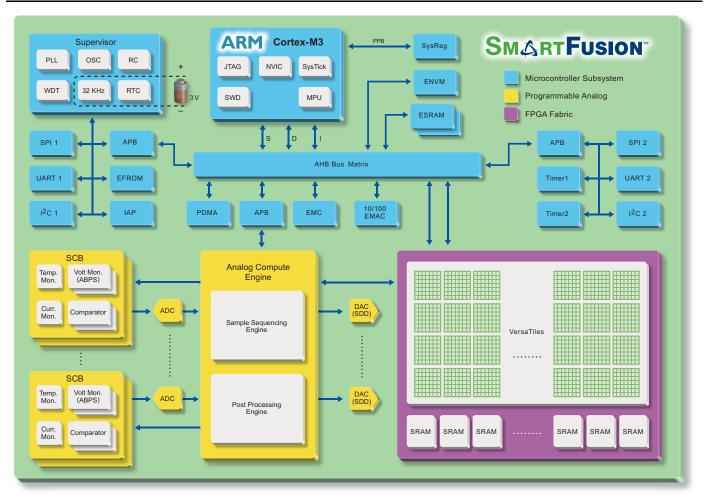

# SmartFusion cSoC Block Diagram

#### Legend:

SDD – Sigma-delta DAC SCB – Signal conditioning block PDMA – Peripheral DMA IAP – In-application programming ABPS – Active bipolar prescaler WDT – Watchdog Timer

SWD – Serial Wire Debug

|           |                                                      | Power Supply                |        | Device |        |        |       |

|-----------|------------------------------------------------------|-----------------------------|--------|--------|--------|--------|-------|

| Parameter | Definition                                           | Name                        | Domain | A2F060 | A2F200 | A2F500 | Units |

| PAC24     | Current Monitor Power Contribution                   | See Table 2-93 on page 2-78 | -      |        | 1.03   |        | mW    |

| PAC25     | ABPS Power Contribution                              | See Table 2-96 on page 2-82 | -      |        | 0.70   |        | mW    |

| PAC26     | Sigma-Delta DAC Power<br>Contribution <sup>2</sup>   | See Table 2-98 on page 2-85 | -      |        | 0.58   |        | mW    |

| PAC27     | Comparator Power Contribution                        | See Table 2-97 on page 2-84 | -      |        | 1.02   |        | mW    |

| PAC28     | Voltage Regulator Power<br>Contribution <sup>3</sup> | See Table 2-99 on page 2-87 | -      |        | 36.30  |        | mW    |

#### Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs

Notes:

1. For a different use of MSS peripherals and resources, refer to SmartPower.

2. Assumes Input = Half Scale Operation mode.

3. Assumes 100 mA load on 1.5 V domain.

#### Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs

|           |                                                                      | Power Supp                 | ly                                           |        | Device  |        |       |

|-----------|----------------------------------------------------------------------|----------------------------|----------------------------------------------|--------|---------|--------|-------|

| Parameter | Definition                                                           | Name                       | Domain                                       | A2F060 | A2F200  | A2F200 | Units |

| PDC1      | Core static power contribution in SoC mode                           | VCC                        | 1.5 V                                        | 11.10  | 23.70   | 37.95  | mW    |

| PDC2      | Device static power contribution in<br>Standby Mode                  | See Table 2-8 on page 2-10 | _                                            | 11.10  | 23.70   | 37.95  | mW    |

| PDC3      | Device static power contribution in<br>Time Keeping mode             | See Table 2-8 on page 2-10 | 3.3 V                                        | 33.00  | 33.00   | 33.00  | μW    |

| PDC7      | Static contribution per input pin (standard dependent contribution)  | VCCxxxxIOBx/VCC            | CC See Table 2-10 and Table 2-11 on page     |        | e 2-11. |        |       |

| PDC8      | Static contribution per output pin (standard dependent contribution) | VCCxxxxIOBx/VCC            | C See Table 2-12 and Table 2-13 on page 2-11 |        | e 2-11. |        |       |

| PDC9      | Static contribution per PLL                                          | VCC                        | 1.5 V                                        | 2.55   | 2.55    | 2.55   | mW    |

Table 2-16 • eNVM Dynamic Power Consumption

| Parameter   | Description                     | Condition      | Min. | Тур.      | Max.        | Units  |

|-------------|---------------------------------|----------------|------|-----------|-------------|--------|

| eNVM System | eNVM array operating power      | Idle           |      | 795       |             | μA     |

|             |                                 | Read operation | See  | Table 2-1 | 4 on page 2 | -12.   |

|             |                                 | Erase          |      | 900       |             | μA     |

|             |                                 | Write          |      | 900       |             | μA     |

| PNVMCTRL    | eNVM controller operating power |                |      | 20        |             | µW/MHz |

| Table 2-21 • Summary of Maximum and Minimum DC Input Levels |

|-------------------------------------------------------------|

| Applicable to Commercial Conditions in all I/O Bank Types   |

|                            | Commercial      |                 |  |

|----------------------------|-----------------|-----------------|--|

|                            | I <sub>IL</sub> | I <sub>IH</sub> |  |

| DC I/O Standards           | μΑ              | μΑ              |  |

| 3.3 V LVTTL / 3.3 V LVCMOS | 15              | 15              |  |

| 2.5 V LVCMOS               | 15              | 15              |  |

| 1.8 V LVCMOS               | 15              | 15              |  |

| 1.5 V LVCMOS               | 15              | 15              |  |

| 3.3 V PCI                  | 15              | 15              |  |

| 3.3 V PCI-X                | 15              | 15              |  |

# Summary of I/O Timing Characteristics – Default I/O Software Settings

| Standard                   | Measuring Trip Point (V <sub>trip</sub> ) |

|----------------------------|-------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 1.4 V                                     |

| 2.5 V LVCMOS               | 1.2 V                                     |

| 1.8 V LVCMOS               | 0.90 V                                    |

| 1.5 V LVCMOS               | 0.75 V                                    |

| 3.3 V PCI                  | 0.285 * VCCxxxxIOBx (RR)                  |

|                            | 0.615 * VCCxxxxIOBx (FF)                  |

| 3.3 V PCI-X                | 0.285 * VCCxxxxIOBx (RR)                  |

|                            | 0.615 * VCCxxxxIOBx (FF)                  |

| LVDS                       | Cross point                               |

| LVPECL                     | Cross point                               |

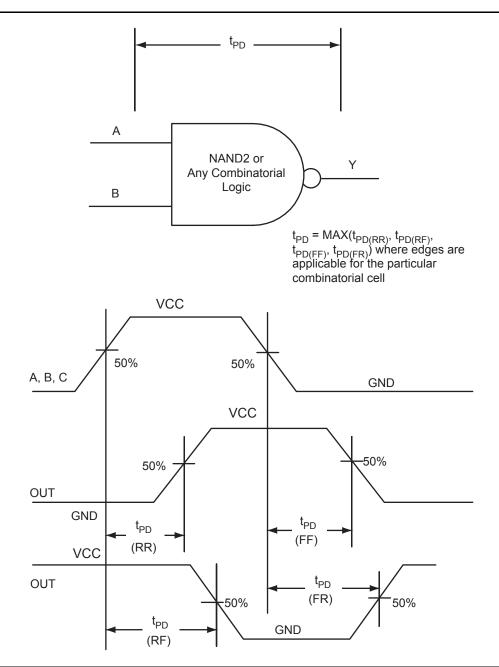

#### Table 2-23 • I/O AC Parameter Definitions

| Parameter         | Parameter Definition                                                        |  |

|-------------------|-----------------------------------------------------------------------------|--|

| t <sub>DP</sub>   | Data to pad delay through the output buffer                                 |  |

| t <sub>PY</sub>   | Pad to data delay through the input buffer                                  |  |

| t <sub>DOUT</sub> | Data to output buffer delay through the I/O interface                       |  |

| t <sub>EOUT</sub> | Enable to output buffer tristate control delay through the I/O interface    |  |

| t <sub>DIN</sub>  | Input buffer to data delay through the I/O interface                        |  |

| t <sub>HZ</sub>   | Enable to pad delay through the output buffer—High to Z                     |  |

| t <sub>ZH</sub>   | Enable to pad delay through the output buffer—Z to High                     |  |

| t <sub>LZ</sub>   | Enable to pad delay through the output buffer—Low to Z                      |  |

| t <sub>ZL</sub>   | Enable to pad delay through the output buffer—Z to Low                      |  |

| t <sub>ZHS</sub>  | Enable to pad delay through the output buffer with delayed enable—Z to High |  |

| t <sub>ZLS</sub>  | Enable to pad delay through the output buffer with delayed enable—Z to Low  |  |

#### Table 2-28 • I/O Output Buffer Maximum Resistances<sup>1</sup> Applicable to MSS I/O Banks

| Standard                   | Drive Strength | $R_{PULL	ext{-}DOWN} \ (\Omega)^2$ | R <sub>PULL-UP</sub><br>(Ω) <sup>3</sup> |

|----------------------------|----------------|------------------------------------|------------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 8mA            | 50                                 | 150                                      |

| 2.5 V LVCMOS               | 8 mA           | 50                                 | 100                                      |

| 1.8 V LVCMOS               | 4 mA           | 100                                | 112                                      |

| 1.5 V LVCMOS               | 2 mA           | 200                                | 224                                      |

Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website.

- 2. R<sub>(PULL-DOWN-MAX)</sub> = (V<sub>OLspec</sub>) / I<sub>OLspec</sub>

- 3. R<sub>(PULL-UP-MAX)</sub> = (V<sub>CCImax</sub> V<sub>OHspec</sub>) / I<sub>OHspec</sub>

# Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|             | R <sub>(WEAK PULL-UP)</sub> 1<br>(Ω) |      | R <sub>(WEAK PU</sub> | LL-DOWN) <sup>2</sup><br>2) |

|-------------|--------------------------------------|------|-----------------------|-----------------------------|

| VCCxxxxlOBx | Min.                                 | Max. | Min.                  | Max.                        |

| 3.3 V       | 10 k                                 | 45 k | 10 k                  | 45 k                        |

| 2.5 V       | 11 k                                 | 55 k | 12 k                  | 74 k                        |

| 1.8 V       | 18 k                                 | 70 k | 17 k                  | 110 k                       |

| 1.5 V       | 19 k                                 | 90 k | 19 k                  | 140 k                       |

Notes:

1. R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

2. R<sub>(WEAK PULL-DOWN-MAX)</sub> = (VOLspec) / I<sub>(WEAK PULL-DOWN-MIN)</sub>

The length of time an I/O can withstand  $I_{OSH}/I_{OSL}$  events depends on the junction temperature. The reliability data below is based on a 3.3 V, 12 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than 2200 operation hours to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

Table 2-32 • Duration of Short Circuit Event before Failure

| Temperature | Time before Failure |

|-------------|---------------------|

| –40°C       | > 20 years          |

| 0°C         | > 20 years          |

| 25°C        | > 20 years          |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

### Table 2-33 • Schmitt Trigger Input Hysteresis

#### Hysteresis Voltage Value (typical) for Schmitt Mode Input Buffers

| Input Buffer Configuration                                | Hysteresis Value (typical) |

|-----------------------------------------------------------|----------------------------|

| 3.3 V LVTTL / LVCMOS / PCI / PCI-X (Schmitt trigger mode) | 240 mV                     |

| 2.5 V LVCMOS (Schmitt trigger mode)                       | 140 mV                     |

| 1.8 V LVCMOS (Schmitt trigger mode)                       | 80 mV                      |

| 1.5 V LVCMOS (Schmitt trigger mode)                       | 60 mV                      |

#### Table 2-34 • I/O Input Rise Time, Fall Time, and Related I/O Reliability

| Input Buffer                  | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.) | Reliability      |

|-------------------------------|-----------------------------|-----------------------------|------------------|

| LVTTL/LVCMOS                  | No requirement              | 10 ns *                     | 20 years (100°C) |

| LVDS/B-LVDS/<br>M-LVDS/LVPECL | No requirement              | 10 ns *                     | 10 years (100°C) |

Note: \*The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi SoC Products Group recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

#### **Timing Characteristics**

Table 2-50 • 1.8 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| e                 | orado          | 50001             | ٩UP             | SDIN             | ΥP Γ            | LOOI              | •2L             | •ZH             | ۴LZ             | ٩٢              | ·2L5             | ·2H5             | 0     |

| 2 mA              | Std.           | 0.60              | 11.06           | 0.04             | 1.14            | 0.39              | 8.61            | 11.06           | 2.61            | 1.59            | 10.67            | 13.12            | ns    |

|                   | –1             | 0.50              | 9.22            | 0.03             | 0.95            | 0.32              | 7.17            | 9.22            | 2.18            | 1.33            | 8.89             | 10.93            | ns    |

| 4 mA              | Std.           | 0.60              | 6.46            | 0.04             | 1.14            | 0.39              | 5.53            | 6.46            | 3.04            | 2.66            | 7.59             | 8.51             | ns    |

|                   | –1             | 0.50              | 5.38            | 0.03             | 0.95            | 0.32              | 4.61            | 5.38            | 2.54            | 2.22            | 6.33             | 7.10             | ns    |

| 6 mA              | Std.           | 0.60              | 4.16            | 0.04             | 1.14            | 0.39              | 3.99            | 4.16            | 3.34            | 3.18            | 6.05             | 6.22             | ns    |

|                   | -1             | 0.50              | 3.47            | 0.03             | 0.95            | 0.32              | 3.32            | 3.47            | 2.78            | 2.65            | 5.04             | 5.18             | ns    |

| 8 mA              | Std.           | 0.60              | 3.69            | 0.04             | 1.14            | 0.39              | 3.76            | 3.67            | 3.40            | 3.31            | 5.81             | 5.73             | ns    |

|                   | -1             | 0.50              | 3.07            | 0.03             | 0.95            | 0.32              | 3.13            | 3.06            | 2.84            | 2.76            | 4.85             | 4.78             | ns    |

| 12 mA             | Std.           | 0.60              | 3.38            | 0.04             | 1.14            | 0.39              | 3.44            | 2.86            | 3.50            | 3.82            | 5.50             | 4.91             | ns    |

|                   | -1             | 0.50              | 2.81            | 0.03             | 0.95            | 0.32              | 2.87            | 2.38            | 2.92            | 3.18            | 4.58             | 4.10             | ns    |

| 16 mA             | Std.           | 0.60              | 3.38            | 0.04             | 1.14            | 0.39              | 3.44            | 2.86            | 3.50            | 3.82            | 5.50             | 4.91             | ns    |

|                   | –1             | 0.50              | 2.81            | 0.03             | 0.95            | 0.32              | 2.87            | 2.38            | 2.92            | 3.18            | 4.58             | 4.10             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-51 • 1.8 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.60              | 14.24           | 0.04             | 1.14            | 0.39              | 13.47           | 14.24           | 2.62            | 1.54            | 15.53            | 16.30            | ns    |

|                   | -1             | 0.50              | 11.87           | 0.03             | 0.95            | 0.32              | 11.23           | 11.87           | 2.18            | 1.28            | 12.94            | 13.59            | ns    |

| 4 mA              | Std.           | 0.60              | 9.74            | 0.04             | 1.14            | 0.39              | 9.92            | 9.62            | 3.05            | 2.57            | 11.98            | 11.68            | ns    |

|                   | -1             | 0.50              | 8.11            | 0.03             | 0.95            | 0.32              | 8.26            | 8.02            | 2.54            | 2.14            | 9.98             | 9.74             | ns    |

| 6 mA              | Std.           | 0.60              | 7.67            | 0.04             | 1.14            | 0.39              | 7.81            | 7.24            | 3.34            | 3.08            | 9.87             | 9.30             | ns    |

|                   | -1             | 0.50              | 6.39            | 0.03             | 0.95            | 0.32              | 6.51            | 6.03            | 2.79            | 2.56            | 8.23             | 7.75             | ns    |

| 8 mA              | Std.           | 0.60              | 7.15            | 0.04             | 1.14            | 0.39              | 7.29            | 6.75            | 3.41            | 3.21            | 9.34             | 8.80             | ns    |

|                   | -1             | 0.50              | 5.96            | 0.03             | 0.95            | 0.32              | 6.07            | 5.62            | 2.84            | 2.68            | 7.79             | 7.34             | ns    |

| 12 mA             | Std.           | 0.60              | 6.76            | 0.04             | 1.14            | 0.39              | 6.89            | 6.75            | 3.50            | 3.70            | 8.95             | 8.81             | ns    |

|                   | -1             | 0.50              | 5.64            | 0.03             | 0.95            | 0.32              | 5.74            | 5.62            | 2.92            | 3.08            | 7.46             | 7.34             | ns    |

| 16 mA             | Std.           | 0.60              | 6.76            | 0.04             | 1.14            | 0.39              | 6.89            | 6.75            | 3.50            | 3.70            | 8.95             | 8.81             | ns    |

|                   | -1             | 0.50              | 5.64            | 0.03             | 0.95            | 0.32              | 5.74            | 5.62            | 2.92            | 3.08            | 7.46             | 7.34             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Microsemi Š,

SmartFusion DC and Switching Characteristics

#### Table 2-52 • 1.8 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to MSS I/O Banks

|                   | Applicable to mode to Ballike |                   |                 |                  |                 |                  |                   |                 |                 |

|-------------------|-------------------------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|

| Drive<br>Strength | Speed<br>Grade                | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>Zł</sub> |

| 4 mA              | Std.                          | 0.22              | 2.77            | 0.09             | 1.09            | 1.64             | 0.22              | 2.82            | 2.7             |

| ength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> |

|-------|-------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|

| A     | Std.  | 0.22              | 2.77            | 0.09             | 1.09            | 1.64             | 0.22              | 2.82            | 2.72            | 2.21            |

|       | –1    | 0.18              | 2.31            | 0.07             | 0.91            | 1.37             | 0.18              | 2.35            | 2.27            | 1.84            |

|       |       |                   |                 |                  |                 |                  |                   |                 |                 |                 |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

Units

ns

ns

t<sub>HZ</sub>

2.25

1.87

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>ОНD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| tosue                 | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| tOESUE                | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

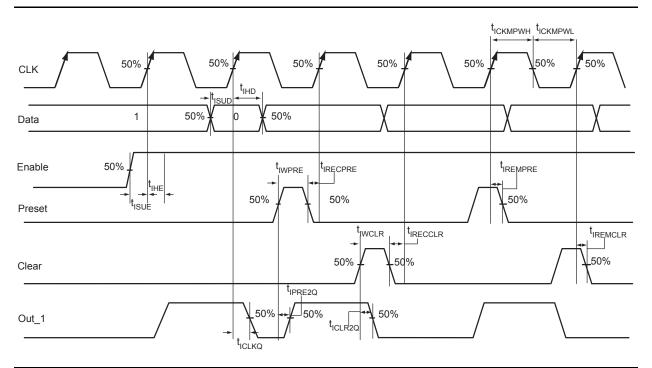

#### Table 2-70 • Parameter Definition and Measuring Nodes

\* See Figure 2-15 on page 2-46 for more information.

## 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

### Input Register

#### **Timing Characteristics**

# Table 2-71 • Input Data Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.24 | 0.29 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.27 | 0.32 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.38 | 0.45 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.46 | 0.55 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.46 | 0.55 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.23 | 0.27 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.23 | 0.27 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.22 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.22 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.36 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.32 | ns    |

*Note:* For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

SmartFusion DC and Switching Characteristics

Figure 2-24 • Timing Model and Waveforms

### **Embedded Design**

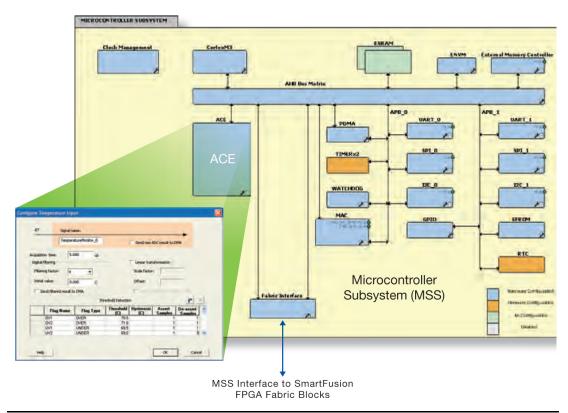

Microsemi offers FREE SoftConsole Eclipse based IDE, which includes the GNU C/C++ compiler and GDB debugger. Microsemi also offers evaluation versions of software from Keil and IAR, with full versions available from respective suppliers.

### **Analog Design**

The MSS configurator provides graphical configuration for current, voltage and temperature monitors, sample sequencing setup and post-processing configuration, as well as DAC output.

The MSS configurator creates a bridge between the FPGA fabric and embedded designers so device configuration can be easily shared between multiple developers.

The MSS configurator includes the following:

- A simple configurator for the embedded designer to control the MSS peripherals and I/Os

- A method to import and view a hardware configuration from the FPGA flow into the embedded flow containing the memory map

- · Automatic generation of drivers for any peripherals or soft IP used in the system configuration

- · Comprehensive analog configuration for the programmable analog components

- Creation of a standard MSS block to be used in SmartDesign for connection of FPGA fabric designs and IP

Figure 3-2 • MSS Configurator

Pin Descriptions

# **Special Function Pins**

| Name     | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                          |

|----------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC       |      |                   | No connect                                                                                                                                                                                                                                                                                                           |

|          |      |                   | This pin is not connected to circuitry within the device. These pins can<br>be driven to any voltage or can be left floating with no effect on the<br>operation of the device.                                                                                                                                       |

| DC       |      |                   | Do not connect.                                                                                                                                                                                                                                                                                                      |

|          |      |                   | This pin should not be connected to any signals on the PCB. These pins should be left unconnected.                                                                                                                                                                                                                   |

| LPXIN    | In   | 1                 | Low power 32 KHz crystal oscillator.                                                                                                                                                                                                                                                                                 |

|          |      |                   | Input from the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXIN pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| LPXOUT   | In   | 1                 | Low power 32 KHz crystal oscillator.                                                                                                                                                                                                                                                                                 |

|          |      |                   | Output to the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXOUT pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| MAINXIN  | In   | 1                 | Main crystal oscillator circuit.                                                                                                                                                                                                                                                                                     |

|          |      |                   | Input to the crystal oscillator circuit. Pin for connecting an external crystal, ceramic resonator, or RC network. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.       |

|          |      |                   | If an external RC network or clock input is used, the RC components are connected to the MAINXIN pin, with MAINXOUT left floating. When the main crystal oscillator is not being used, MAINXIN and MAINXOUT pins can be left floating.                                                                               |

|          |      |                   | For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                         |

| MAINXOUT | Out  | 1                 | Main crystal oscillator circuit.                                                                                                                                                                                                                                                                                     |

|          |      |                   | Output from the crystal oscillator circuit. Pin for connecting external crystal or ceramic resonator. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.                    |

|          |      |                   | If an external RC network or clock input is used, the RC components are connected to the MAINXIN pin, with MAINXOUT left floating. When the main crystal oscillator is not being used, MAINXIN and MAINXOUT pins can be left floating.                                                                               |

|          |      |                   | For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                         |

**CS288** Pin A2F060 Function A2F200 Function A2F500 Function No. VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 A1 A2 GNDQ GNDQ GNDQ A3 EMC CLK/IO00NDB0V0 EMC CLK/GAA0/IO00NDB0V0 EMC CLK/GAA0/IO02NDB0V0 EMC RW N/IO00PDB0V0 EMC RW N/GAA1/IO00PDB0V0 EMC RW N/GAA1/IO02PDB0V0 A4 A5 GND GND GND EMC CS1 N/GAB1/IO01PDB0V0 EMC CS1 N/GAB1/IO05PDB0V0 A6 EMC CS1 N/IO01PDB0V0 A7 EMC CS0 N/IO01NDB0V0 EMC CS0 N/GAB0/IO01NDB0V0 EMC CS0 N/GAB0/IO05NDB0V0 A8 EMC AB[0]/IO04NPB0V0 EMC AB[0]/IO04NPB0V0 EMC AB[0]/IO06NPB0V0 A9 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 EMC AB[4]/IO06NDB0V0 EMC AB[4]/IO06NDB0V0 EMC AB[4]/IO10NDB0V0 A10 A11 EMC AB[8]/IO08NPB0V0 EMC AB[8]/IO08NPB0V0 EMC AB[8]/IO13NPB0V0 A12 EMC AB[14]/IO11NPB0V0 EMC AB[14]/IO11NPB0V0 EMC AB[14]/IO15NPB0V0 A13 GND GND GND EMC AB[18]/IO13NDB0V0 EMC AB[18]/IO13NDB0V0 EMC AB[18]/IO18NDB0V0 A14 EMC AB[24]/IO16NDB0V0 A15 EMC AB[24]/IO16NDB0V0 EMC AB[24]/IO20NDB0V0 A16 EMC AB[25]/IO16PDB0V0 EMC AB[25]/IO16PDB0V0 EMC AB[25]/IO20PDB0V0 A17 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 A18 EMC AB[20]/IO14NDB0V0 EMC AB[20]/IO14NDB0V0 EMC AB[20]/IO21NDB0V0 A19 EMC AB[21]/IO14PDB0V0 EMC AB[21]/IO14PDB0V0 EMC AB[21]/IO21PDB0V0 A20 GNDQ GNDQ GNDQ GND GND GND A21 AA1 ADC1 ABPS1 ABPS1 AA2 **GNDAQ** GNDAQ GNDAQ AA3 GNDA GNDA GNDA AA4 VCC33N VCC33N VCC33N AA5 SDD0 SDD0 SDD0 AA6 ADC0 ABPS0 ABPS0 AA7 **GNDTM0** NC **GNDTM0** AA8 NC ABPS2 ABPS2 AA9 VAREF0 VAREF0 NC AA10 NC GND15ADC0 GND15ADC0

Notes:

🔨 🗇 Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin |                         | FG256                        |                              |

|-----|-------------------------|------------------------------|------------------------------|

| No. | A2F060 Function         | A2F200 Function              | A2F500 Function              |

| A1  | GND                     | GND                          | GND                          |

| A2  | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |

| A3  | EMC_AB[0]/IO04NDB0V0    | EMC_AB[0]/IO04NDB0V0         | EMC_AB[0]/IO06NDB0V0         |

| A4  | EMC_AB[1]/IO04PDB0V0    | EMC_AB[1]/IO04PDB0V0         | EMC_AB[1]/IO06PDB0V0         |

| A5  | GND                     | GND                          | GND                          |

| A6  | EMC_AB[3]/IO05PDB0V0    | EMC_AB[3]/IO05PDB0V0         | EMC_AB[3]/IO09PDB0V0         |

| A7  | EMC_AB[5]/IO06PDB0V0    | EMC_AB[5]/IO06PDB0V0         | EMC_AB[5]/IO10PDB0V0         |

| A8  | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |

| A9  | GND                     | GND                          | GND                          |

| A10 | EMC_AB[14]/IO11NDB0V0   | EMC_AB[14]/IO11NDB0V0        | EMC_AB[14]/IO15NDB0V0        |

| A11 | EMC_AB[15]/IO11PDB0V0   | EMC_AB[15]/IO11PDB0V0        | EMC_AB[15]/IO15PDB0V0        |

| A12 | GND                     | GND                          | GND                          |

| A13 | EMC_AB[20]/IO14NDB0V0   | EMC_AB[20]/IO14NDB0V0        | EMC_AB[20]/IO21NDB0V0        |

| A14 | EMC_AB[24]/IO16NDB0V0   | EMC_AB[24]/IO16NDB0V0        | EMC_AB[24]/IO20NDB0V0        |

| A15 | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |

| A16 | GND                     | GND                          | GND                          |

| B1  | EMC_DB[15]/IO45PDB5V0   | EMC_DB[15]/GAA2/IO71PDB5V0   | EMC_DB[15]/GAA2/IO88PDB5V0   |

| B2  | GND                     | GND                          | GND                          |

| B3  | EMC_BYTEN[1]/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO07PDB0V0 |

| B4  | EMC_OEN0_N/IO03NDB0V0   | EMC_OEN0_N/IO03NDB0V0        | EMC_OEN0_N/IO08NDB0V0        |

| B5  | EMC_OEN1_N/IO03PDB0V0   | EMC_OEN1_N/IO03PDB0V0        | EMC_OEN1_N/IO08PDB0V0        |

| B6  | EMC_AB[2]/IO05NDB0V0    | EMC_AB[2]/IO05NDB0V0         | EMC_AB[2]/IO09NDB0V0         |

| B7  | EMC_AB[4]/IO06NDB0V0    | EMC_AB[4]/IO06NDB0V0         | EMC_AB[4]/IO10NDB0V0         |

| B8  | EMC_AB[9]/IO08PDB0V0    | EMC_AB[9]/IO08PDB0V0         | EMC_AB[9]/IO13PDB0V0         |

| B9  | EMC_AB[12]/IO10NDB0V0   | EMC_AB[12]/IO10NDB0V0        | EMC_AB[12]/IO14NDB0V0        |

| B10 | EMC_AB[13]/IO10PDB0V0   | EMC_AB[13]/IO10PDB0V0        | EMC_AB[13]/IO14PDB0V0        |

| B11 | EMC_AB[16]/IO12NDB0V0   | EMC_AB[16]/IO12NDB0V0        | EMC_AB[16]/IO17NDB0V0        |

| B12 | EMC_AB[18]/IO13NDB0V0   | EMC_AB[18]/IO13NDB0V0        | EMC_AB[18]/IO18NDB0V0        |

| B13 | EMC_AB[21]/IO14PDB0V0   | EMC_AB[21]/IO14PDB0V0        | EMC_AB[21]/IO21PDB0V0        |

| B14 | EMC_AB[25]/IO16PDB0V0   | EMC_AB[25]/IO16PDB0V0        | EMC_AB[25]/IO20PDB0V0        |

| B15 | GND                     | GND                          | GND                          |

#### Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

Pin Descriptions

🔨 Microsemi

| Pin    |                      | FG256                     |                           |  |  |

|--------|----------------------|---------------------------|---------------------------|--|--|

| No.    | A2F060 Function      | A2F200 Function           | A2F500 Function           |  |  |

| F14    | IO21NDB1V0           | GCB0/IO27NDB1V0           | GCB0/IO34NDB1V0           |  |  |

| F15    | GND                  | GND                       | GND                       |  |  |

| F16    | VCCENVM              | VCCENVM                   | VCCENVM                   |  |  |

| G1     | EMC_DB[8]/IO40NDB5V0 | EMC_DB[8]/GEC0/IO63NDB5V0 | EMC_DB[8]/GEC0/IO80NDB5V0 |  |  |

| G2     | EMC_DB[7]/IO39PDB5V0 | EMC_DB[7]/GEB1/IO62PDB5V0 | EMC_DB[7]/GEB1/IO79PDB5V0 |  |  |

| G3     | EMC_DB[6]/IO39NDB5V0 | EMC_DB[6]/GEB0/IO62NDB5V0 | EMC_DB[6]/GEB0/IO79NDB5V0 |  |  |

| G4     | GFC2/IO41PDB5V0      | GFC2/IO67PDB5V0           | GFC2/IO84PDB5V0           |  |  |

| G5     | IO41NDB5V0           | IO67NDB5V0                | IO84NDB5V0                |  |  |

| G6     | GND                  | GND                       | GND                       |  |  |

| G7     | VCC                  | VCC                       | VCC                       |  |  |

| G8     | GND                  | GND                       | GND                       |  |  |

| G9     | VCC                  | VCC                       | VCC                       |  |  |

| G10    | GND                  | GND                       | GND                       |  |  |

| G11    | VCCFPGAIOB1          | VCCFPGAIOB1               | VCCFPGAIOB1               |  |  |

| G12    | VPP                  | VPP                       | VPP                       |  |  |

| G13    | TRSTB                | TRSTB                     | TRSTB                     |  |  |

| G14    | TMS                  | TMS                       | TMS                       |  |  |

| G15    | ТСК                  | ТСК                       | тск                       |  |  |

| G16    | GNDENVM              | GNDENVM                   | GNDENVM                   |  |  |

| H1     | GND                  | GND                       | GND                       |  |  |

| H2     | EMC_DB[5]/IO38PPB5V0 | EMC_DB[5]/GEA1/IO61PPB5V0 | EMC_DB[5]/GEA1/IO78PPB5V0 |  |  |

| H3     | VCCFPGAIOB5          | VCCFPGAIOB5               | VCCFPGAIOB5               |  |  |

| H4     | EMC_DB[1]/IO36PDB5V0 | EMC_DB[1]/GEB2/IO59PDB5V0 | EMC_DB[1]/GEB2/IO76PDB5V0 |  |  |

| H5     | EMC_DB[0]/IO36NDB5V0 | EMC_DB[0]/GEA2/IO59NDB5V0 | EMC_DB[0]/GEA2/IO76NDB5V0 |  |  |

| H6     | VCCFPGAIOB5          | VCCFPGAIOB5               | VCCFPGAIOB5               |  |  |

| H7     | GND                  | GND                       | GND                       |  |  |

| H8     | VCC                  | VCC                       | VCC                       |  |  |

| H9     | GND                  | GND                       | GND                       |  |  |

| H10    | VCC                  | VCC                       | VCC                       |  |  |

| H11    | GND                  | GND                       | GND                       |  |  |

| H12    | VJTAG                | VJTAG                     | VJTAG                     |  |  |

| Notes: |                      | Ц                         | J                         |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | F                          | G484                       |  |  |  |

|------------|----------------------------|----------------------------|--|--|--|

| Pin Number | A2F200 Function            | A2F500 Function            |  |  |  |

| C15        | EMC_AB[17]/IO12PDB0V0      | EMC_AB[17]/IO17PDB0V0      |  |  |  |

| C16        | EMC_AB[24]/IO16NDB0V0      | EMC_AB[24]/IO20NDB0V0      |  |  |  |

| C17        | EMC_AB[22]/IO15NDB0V0      | EMC_AB[22]/IO19NDB0V0      |  |  |  |

| C18        | EMC_AB[23]/IO15PDB0V0      | EMC_AB[23]/IO19PDB0V0      |  |  |  |

| C19        | GBA0/IO19NPB0V0            | GBA0/IO23NPB0V0            |  |  |  |

| C20        | NC                         | NC                         |  |  |  |

| C21        | GBC2/IO21PDB1V0            | GBC2/IO30PDB1V0            |  |  |  |

| C22        | GBB2/IO20NDB1V0            | GBB2/IO27NDB1V0            |  |  |  |

| D1         | GND                        | GND                        |  |  |  |

| D2         | EMC_DB[12]/IO70NDB5V0      | EMC_DB[12]/IO87NDB5V0      |  |  |  |

| D3         | EMC_DB[13]/GAC2/IO70PDB5V0 | EMC_DB[13]/GAC2/IO87PDB5V0 |  |  |  |

| D4         | NC                         | NC                         |  |  |  |

| D5         | NC                         | NC                         |  |  |  |

| D6         | GND                        | GND                        |  |  |  |

| D7         | NC                         | IO00NPB0V0                 |  |  |  |

| D8         | NC                         | IO03NPB0V0                 |  |  |  |

| D9         | GND                        | GND                        |  |  |  |

| D10        | EMC_OEN0_N/IO03NDB0V0      | EMC_OEN0_N/IO08NDB0V0      |  |  |  |

| D11        | EMC_AB[10]/IO09NDB0V0      | EMC_AB[10]/IO11NDB0V0      |  |  |  |

| D12        | EMC_AB[11]/IO09PDB0V0      | EMC_AB[11]/IO11PDB0V0      |  |  |  |

| D13        | EMC_AB[9]/IO08PDB0V0       | EMC_AB[9]/IO13PDB0V0       |  |  |  |

| D14        | GND                        | GND                        |  |  |  |

| D15        | GBC1/IO17PPB0V0            | GBC1/IO22PPB0V0            |  |  |  |

| D16        | EMC_AB[25]/IO16PDB0V0      | EMC_AB[25]/IO20PDB0V0      |  |  |  |

| D17        | GND                        | GND                        |  |  |  |

| D18        | GBA1/IO19PPB0V0            | GBA1/IO23PPB0V0            |  |  |  |

| D19        | NC                         | NC                         |  |  |  |

| D20        | NC                         | NC                         |  |  |  |

| D21        | IO21NDB1V0                 | IO30NDB1V0                 |  |  |  |

| D22        | GND                        | GND                        |  |  |  |

| E1         | GFC2/IO67PPB5V0            | GFC2/IO84PPB5V0            |  |  |  |

| E2         | VCCFPGAIOB5                | VCCFPGAIOB5                |  |  |  |

| E3         | GFA2/IO68PDB5V0            | GFA2/IO85PDB5V0            |  |  |  |

| E4         | GND                        | GND                        |  |  |  |

| Notes:     |                            |                            |  |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

|            | FG484                     |                           |

|------------|---------------------------|---------------------------|

| Pin Number | A2F200 Function           | A2F500 Function           |

| F17        | NC                        | IO25PPB1V0                |

| F18        | VCCFPGAIOB1               | VCCFPGAIOB1               |

| F19        | IO23NDB1V0                | IO28NDB1V0                |

| F20        | NC                        | IO31PDB1V0                |

| F21        | NC                        | IO31NDB1V0                |

| F22        | IO22PDB1V0                | IO32PDB1V0                |

| G1         | GND                       | GND                       |

| G2         | GFB0/IO65NPB5V0           | GFB0/IO82NPB5V0           |

| G3         | EMC_DB[9]/GEC1/IO63PDB5V0 | EMC_DB[9]/GEC1/IO80PDB5V0 |

| G4         | GFC1/IO66PPB5V0           | GFC1/IO83PPB5V0           |

| G5         | EMC_DB[11]/IO69PPB5V0     | EMC_DB[11]/IO86PPB5V0     |

| G6         | GNDQ                      | GNDQ                      |

| G7         | NC                        | NC                        |

| G8         | GND                       | GND                       |

| G9         | VCCFPGAIOB0               | VCCFPGAIOB0               |

| G10        | GND                       | GND                       |

| G11        | VCCFPGAIOB0               | VCCFPGAIOB0               |

| G12        | GND                       | GND                       |

| G13        | VCCFPGAIOB0               | VCCFPGAIOB0               |

| G14        | GND                       | GND                       |

| G15        | VCCFPGAIOB0               | VCCFPGAIOB0               |

| G16        | GNDQ                      | GNDQ                      |

| G17        | NC                        | IO26PDB1V0                |

| G18        | NC                        | IO26NDB1V0                |

| G19        | GCA2/IO23PDB1V0           | GCA2/IO28PDB1V0 *         |

| G20        | IO24NDB1V0                | IO33NDB1V0                |

| G21        | GCB2/IO24PDB1V0           | GCB2/IO33PDB1V0           |

| G22        | GND                       | GND                       |

| H1         | EMC_DB[7]/GEB1/IO62PDB5V0 | EMC_DB[7]/GEB1/IO79PDB5V0 |

| H2         | VCCFPGAIOB5               | VCCFPGAIOB5               |

| H3         | EMC_DB[8]/GEC0/IO63NDB5V0 | EMC_DB[8]/GEC0/IO80NDB5V0 |

| H4         | GND                       | GND                       |

| H5         | GFC0/IO66NPB5V0           | GFC0/IO83NPB5V0           |

| H6         | GFA1/IO64PDB5V0           | GFA1/IO81PDB5V0           |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

Datasheet Information

| Revision                  | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 3<br>(continued) | In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the VDDBAT recommended<br>operating range was changed from "2.97 to 3.63" to "2.7 to 3.63" (SAR 25246).<br>Recommended operating range was changed to "3.15 to 3.45" for the following<br>voltages:<br>VCC33A<br>VCC33ADCx<br>VCC33AP<br>VCC33SDDx<br>VCCMAINXTAL<br>VCCLPXTAL<br>Two notes were added to the table (SAR 27109):<br>1. The following 3.3 V supplies should be connected together while following proper<br>noise filtering practices: VCC33A, VCC33ADCx, VCC33AP, VCC33SDDx,<br>VCCMAINXTAL, and VCCLPXTAL.<br>2. The following 1.5 V supplies should be connected together while following proper | 2-3  |

|                           | noise filtering practices: VCC, VCC15A, and VCC15ADCx.<br>In Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> , the description for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-3  |

|                           | VCCLPXTAL was corrected to change "32 Hz" to "32 KHz" (SAR 27110).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|                           | The "Power Supply Sequencing Requirement" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-4  |

|                           | Table 2-8 • Power Supplies Configuration was revised to change most on/off entries to voltages. Note 5 was added, stating that "on" means proper voltage is applied. The values of 6 $\mu$ A and 16 $\mu$ A were removed for IDC1 and IDC2 for 3.3 V. A note was added for IDC1 and IDC2: "Power mode and Sleep mode are consuming higher current than expected in the current version of silicon. These specifications will be updated when new version of the silicon is available" (SAR 27926).                                                                                                                                                                                  | 2-10 |

|                           | The "Power-Down and Sleep Mode Implementation" section is new (SAR 27178).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-11 |

|                           | A note was added to Table 2-86 • SmartFusion CCC/PLL Specification, pertaining to $f_{out\_CCC}$ , stating that "one of the CCC outputs (GLA0) is used as an MSS clock and is limited to 100 MHz (maximum) by software" (SAR 26388).                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-63 |

|                           | Table 2-90 • eNVM Block Timing, Worst Commercial Case Conditions: $T_J = 85^{\circ}C$ , VCC = 1.425 V was revised. Values were included for A2F200 and A2F500, for -1 and Std. speed grades. A note was added to define 6:1:1:1 and 5:1:1:1 (SAR 26166).                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-76 |

|                           | The units were corrected (mV instead of V) for input referred offset voltage, GDEC[1:0] = 00 in Table 2-96 • ABPS Performance Specifications (SAR 25381).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-82 |

|                           | The test condition values for operating current (ICC33A, typical) were changed in Table 2-99 • Voltage Regulator (SAR 26465).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-87 |

|                           | Figure 2-45 • Typical Output Voltage was revised to add legends for the three curves, stating the load represented by each (SAR 25247).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-88 |

|                           | The "SmartFusion Programming" chapter was moved to this document from the SmartFusion Subsystem Microcontroller User's Guide (SAR 26542). The "Typical Programming and Erase Times" section was added to this chapter.                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-7  |

|                           | Figure 4-1 • TRSTB Logic was revised to change 1.5 V to "VJTAG (1.5 V to 3.3 V nominal)" (SAR 24694).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-8  |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.