# E·XFL

Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                    |

| Architecture            | MCU, FPGA                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                             |

| Flash Size              | 512KB                                                                       |

| RAM Size                | 64KB                                                                        |

| Peripherals             | DMA, POR, WDT                                                               |

| Connectivity            | Ethernet, I <sup>2</sup> C, SPI, UART/USART                                 |

| Speed                   | 100MHz                                                                      |

| Primary Attributes      | ProASIC®3 FPGA, 500K Gates, 11520 D-Flip-Flops                              |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                          |

| Package / Case          | 208-BFQFP                                                                   |

| Supplier Device Package | 208-PQFP (28x28)                                                            |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f500m3g-1pq208i |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Timing Characteristics**

Table 2-50 • 1.8 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| e                 | orado          | 50001             | ٩UP             | SDIN             | Ψř              | LOOI              | •2L             | •ZH             | ۴LZ             | ٩٢              | ·2L5             | ·2H5             | 0     |

| 2 mA              | Std.           | 0.60              | 11.06           | 0.04             | 1.14            | 0.39              | 8.61            | 11.06           | 2.61            | 1.59            | 10.67            | 13.12            | ns    |

|                   | -1             | 0.50              | 9.22            | 0.03             | 0.95            | 0.32              | 7.17            | 9.22            | 2.18            | 1.33            | 8.89             | 10.93            | ns    |

| 4 mA              | Std.           | 0.60              | 6.46            | 0.04             | 1.14            | 0.39              | 5.53            | 6.46            | 3.04            | 2.66            | 7.59             | 8.51             | ns    |

|                   | -1             | 0.50              | 5.38            | 0.03             | 0.95            | 0.32              | 4.61            | 5.38            | 2.54            | 2.22            | 6.33             | 7.10             | ns    |

| 6 mA              | Std.           | 0.60              | 4.16            | 0.04             | 1.14            | 0.39              | 3.99            | 4.16            | 3.34            | 3.18            | 6.05             | 6.22             | ns    |

|                   | -1             | 0.50              | 3.47            | 0.03             | 0.95            | 0.32              | 3.32            | 3.47            | 2.78            | 2.65            | 5.04             | 5.18             | ns    |

| 8 mA              | Std.           | 0.60              | 3.69            | 0.04             | 1.14            | 0.39              | 3.76            | 3.67            | 3.40            | 3.31            | 5.81             | 5.73             | ns    |

|                   | -1             | 0.50              | 3.07            | 0.03             | 0.95            | 0.32              | 3.13            | 3.06            | 2.84            | 2.76            | 4.85             | 4.78             | ns    |

| 12 mA             | Std.           | 0.60              | 3.38            | 0.04             | 1.14            | 0.39              | 3.44            | 2.86            | 3.50            | 3.82            | 5.50             | 4.91             | ns    |

|                   | -1             | 0.50              | 2.81            | 0.03             | 0.95            | 0.32              | 2.87            | 2.38            | 2.92            | 3.18            | 4.58             | 4.10             | ns    |

| 16 mA             | Std.           | 0.60              | 3.38            | 0.04             | 1.14            | 0.39              | 3.44            | 2.86            | 3.50            | 3.82            | 5.50             | 4.91             | ns    |

|                   | –1             | 0.50              | 2.81            | 0.03             | 0.95            | 0.32              | 2.87            | 2.38            | 2.92            | 3.18            | 4.58             | 4.10             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-51 • 1.8 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J$  = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.7 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.60              | 14.24           | 0.04             | 1.14            | 0.39              | 13.47           | 14.24           | 2.62            | 1.54            | 15.53            | 16.30            | ns    |

|                   | -1             | 0.50              | 11.87           | 0.03             | 0.95            | 0.32              | 11.23           | 11.87           | 2.18            | 1.28            | 12.94            | 13.59            | ns    |

| 4 mA              | Std.           | 0.60              | 9.74            | 0.04             | 1.14            | 0.39              | 9.92            | 9.62            | 3.05            | 2.57            | 11.98            | 11.68            | ns    |

|                   | -1             | 0.50              | 8.11            | 0.03             | 0.95            | 0.32              | 8.26            | 8.02            | 2.54            | 2.14            | 9.98             | 9.74             | ns    |

| 6 mA              | Std.           | 0.60              | 7.67            | 0.04             | 1.14            | 0.39              | 7.81            | 7.24            | 3.34            | 3.08            | 9.87             | 9.30             | ns    |

|                   | -1             | 0.50              | 6.39            | 0.03             | 0.95            | 0.32              | 6.51            | 6.03            | 2.79            | 2.56            | 8.23             | 7.75             | ns    |

| 8 mA              | Std.           | 0.60              | 7.15            | 0.04             | 1.14            | 0.39              | 7.29            | 6.75            | 3.41            | 3.21            | 9.34             | 8.80             | ns    |

|                   | -1             | 0.50              | 5.96            | 0.03             | 0.95            | 0.32              | 6.07            | 5.62            | 2.84            | 2.68            | 7.79             | 7.34             | ns    |

| 12 mA             | Std.           | 0.60              | 6.76            | 0.04             | 1.14            | 0.39              | 6.89            | 6.75            | 3.50            | 3.70            | 8.95             | 8.81             | ns    |

|                   | -1             | 0.50              | 5.64            | 0.03             | 0.95            | 0.32              | 5.74            | 5.62            | 2.92            | 3.08            | 7.46             | 7.34             | ns    |

| 16 mA             | Std.           | 0.60              | 6.76            | 0.04             | 1.14            | 0.39              | 6.89            | 6.75            | 3.50            | 3.70            | 8.95             | 8.81             | ns    |

|                   | -1             | 0.50              | 5.64            | 0.03             | 0.95            | 0.32              | 5.74            | 5.62            | 2.92            | 3.08            | 7.46             | 7.34             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

### **Output Enable Register**

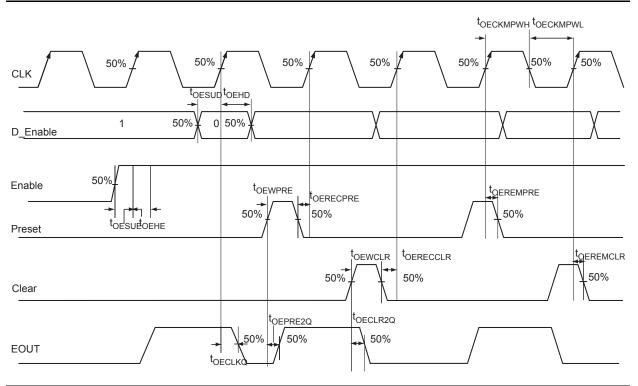

Figure 2-18 • Output Enable Register Timing Diagram

#### **Timing Characteristics**

Table 2-73 • Output Enable Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.45 | 0.54 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.32 | 0.38 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.53 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.68 | 0.81 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.68 | 0.81 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.23 | 0.27 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.23 | 0.27 | ns    |

| tOEWCLR               | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.22 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.22 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.36 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.32 | 0.32 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

| Parameter            | Description           | -1    | Std.  | Units |  |

|----------------------|-----------------------|-------|-------|-------|--|

| t <sub>RSTB2Q</sub>  | Reset to Q (data out) | 26.67 | 30.67 | ns    |  |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency | 19.00 | 21.85 | MHz   |  |

| t <sub>TRSTREM</sub> | ResetB Removal Time   | 0.00  | 0.00  | ns    |  |

| t <sub>TRSTREC</sub> | ResetB Recovery Time  | 0.27  | 0.31  | ns    |  |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse  | TBD   | TBD   | ns    |  |

#### Table 2-92 • JTAG 1532 Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

### **Temperature Monitor**

Unless otherwise noted, temperature monitor performance is specified with a 2N3904 diode-connected bipolar transistor from National Semiconductor or Infineon Technologies, nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 62.5 Ksps. After digital compensation. Unless otherwise noted, the specifications pertain to conditions where the SmartFusion cSoC and the sensing diode are at the same temperature.

| Table 2-94 • Temperature Monitor Performance Specifications |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| Specification                                                  | Test Conditions                                                                                         | Min.  | Typical | Max.   | Units  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|---------|--------|--------|

| Input diode temperature range                                  |                                                                                                         | -55   |         | 150    | °C     |

|                                                                |                                                                                                         | 233.2 |         | 378.15 | K      |

| Temperature sensitivity                                        |                                                                                                         |       | 2.5     |        | mV/K   |

| Intercept                                                      | Extrapolated to 0K                                                                                      |       | 0       |        | V      |

| Input referred temperature offset error                        | At 25°C (298.15K)                                                                                       |       | ±1      | 1.5    | °C     |

| Gain error                                                     | Slope of BFSL vs. 2.5 mV/K                                                                              |       | ±1      | 2.5    | % nom. |

| Overall accuracy                                               | Peak error from ideal transfer function                                                                 |       | ±2      | ±3     | °C     |

| Input referred noise                                           | At 25°C (298.15K) – no output averaging                                                                 |       | 4       |        | °C rms |

| Output current                                                 | Idle mode                                                                                               |       | 100     |        | μA     |

|                                                                | Final measurement phases                                                                                |       | 10      |        | μA     |

| Analog settling time                                           | Measured to 0.1% of final value, (with ADC load)                                                        |       |         |        |        |

|                                                                | From TM_STB (High)                                                                                      | 5     |         |        | μs     |

|                                                                | From ADC_START (High)                                                                                   | 5     |         | 105    | μs     |

| AT parasitic capacitance                                       |                                                                                                         |       |         | 500    | pF     |

| Power supply rejection ratio                                   | DC (0–10 KHz)                                                                                           | 1.2   | 0.7     |        | °C/V   |

| Input referred temperature sensitivity error                   | Variation due to device temperature<br>(–40°C to +100°C). External temperature<br>sensor held constant. |       | 0.005   | 0.008  | °C/°C  |

| Temperature monitor (TM)                                       | VCC33A                                                                                                  |       | 200     |        | μA     |

| operational power supply current requirements (per temperature | VCC33AP                                                                                                 |       | 150     |        | μA     |

| monitor instance, not including ADC or VAREFx)                 | VCC15A                                                                                                  |       | 50      |        | μA     |

Note: All results are based on averaging over 64 samples.

## static Microsemi.

SmartFusion DC and Switching Characteristics

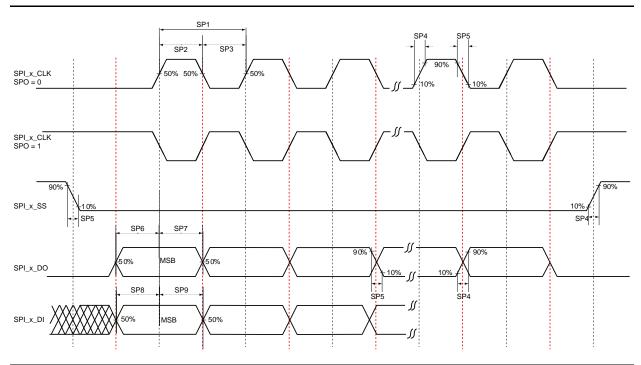

#### Table 2-100 • SPI Characteristics

#### Commercial Case Conditions: T<sub>J</sub> = 85°C, VDD = 1.425 V, -1 Speed Grade (continued)

| Symbol | Description and Condition                           | A2F060 | A2F200 | A2F500 | Unit        |

|--------|-----------------------------------------------------|--------|--------|--------|-------------|

| sp6    | Data from master (SPI_x_DO) setup time <sup>2</sup> | 1      | 1      | 1      | pclk cycles |

| sp7    | Data from master (SPI_x_DO) hold time <sup>2</sup>  | 1      | 1      | 1      | pclk cycles |

| sp8    | SPI_x_DI setup time <sup>2</sup>                    | 1      | 1      | 1      | pclk cycles |

| sp9    | SPI_x_DI hold time <sup>2</sup>                     | 1      | 1      | 1      | pclk cycles |

Notes:

1. These values are provided for a load of 35 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/index.php?option=com\_microsemi&Itemid=489&Iang=en&view=salescontact.

For allowable pclk configurations, refer to the Serial Peripheral Interface Controller section in the SmartFusion Microcontroller Subsystem User's Guide.

# Inter-Integrated Circuit (I<sup>2</sup>C) Characteristics

This section describes the DC and switching of the I C interface. Unless otherwise noted, all output characteristics given are for a 100 pF load on the pins. For timing parameter definitions, refer to Figure 2-48 on page 2-92.

#### Table 2-101 • I<sup>2</sup>C Characteristics

#### Commercial Case Conditions: T<sub>J</sub> = 85°C, V<sub>DD</sub> = 1.425 V, –1 Speed Grade

| Parameter              | Definition                                                  | Condition                                    | Value                       | Unit        |

|------------------------|-------------------------------------------------------------|----------------------------------------------|-----------------------------|-------------|

| V <sub>IL</sub>        | Minimum input low voltage                                   | _                                            | SeeTable 2-36 on page 2-30  | _           |

|                        | Maximum input low voltage                                   | -                                            | See Table 2-36              | -           |

| V <sub>IH</sub>        | Minimum input high voltage                                  | _                                            | See Table 2-36              | -           |

|                        | Maximum input high voltage                                  | _                                            | See Table 2-36              | -           |

| V <sub>OL</sub>        | Maximum output voltage low                                  | I <sub>OL</sub> = 8 mA                       | See Table 2-36              | _           |

| IIL                    | Input current high                                          | _                                            | See Table 2-36              | -           |

| I <sub>IH</sub>        | Input current low                                           | _                                            | See Table 2-36              | -           |

| V <sub>hyst</sub>      | Hysteresis of Schmitt trigger inputs                        | _                                            | See Table 2-33 on page 2-29 | V           |

| T <sub>FALL</sub>      | Fall time <sup>2</sup>                                      | VIHmin to VILMax, C <sub>load</sub> = 400 pF | 15.0                        | ns          |

|                        |                                                             | VIHmin to VILMax, C <sub>load</sub> = 100 pF | 4.0                         | ns          |

| T <sub>RISE</sub>      | Rise time <sup>2</sup>                                      | VILMax to VIHmin, C <sub>load</sub> = 400pF  | 19.5                        | ns          |

|                        |                                                             | VILMax to VIHmin, C <sub>load</sub> = 100pF  | 5.2                         | ns          |

| Cin                    | Pin capacitance                                             | VIN = 0, f = 1.0 MHz                         | 8.0                         | pF          |

| R <sub>pull-up</sub>   | Output buffer maximum pull-<br>down Resistance <sup>1</sup> | _                                            | 50                          | :           |

| R <sub>pull-down</sub> | Output buffer maximum pull-up Resistance <sup>1</sup>       | _                                            | 150                         | :           |

| D <sub>max</sub>       | Maximum data rate                                           | Fast mode                                    | 400                         | Kbps        |

| t <sub>LOW</sub>       | Low period of I2C_x_SCL <sup>3</sup>                        | _                                            | 1                           | pclk cycles |

| t <sub>HIGH</sub>      | High period of I2C_x_SCL <sup>3</sup>                       | _                                            | 1                           | pclk cycles |

| t <sub>HD;STA</sub>    | START hold time <sup>3</sup>                                | _                                            | 1                           | pclk cycles |

| t <sub>SU;STA</sub>    | START setup time <sup>3</sup>                               | _                                            | 1                           | pclk cycles |

| t <sub>HD;DAT</sub>    | DATA hold time <sup>3</sup>                                 | -                                            | 1                           | pclk cycles |

| t <sub>SU;DAT</sub>    | DATA setup time <sup>3</sup>                                | _                                            | 1                           | pclk cycles |

Notes:

1. These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&Itemid=489&Iang=en&view=salescontact.

These values are provided for a load of 100 pF and 400 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/index.php?option=com\_microsemi&Itemid=489&Iang=en&view=salescontact.

3. For allowable Pclk configurations, refer to the Inter-Integrated Circuit (I<sup>2</sup>C) Peripherals section in the SmartFusion Microcontroller Subsystem User's Guide.

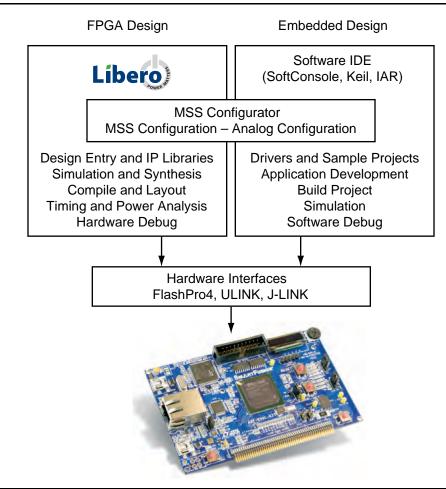

# **3 – SmartFusion Development Tools**

Designing with SmartFusion cSoCs involves three different types of design: FPGA design, embedded design and analog design. These roles can be filled by three different designers, two designers or even a single designer, depending on company structure and project complexity.

# **Types of Design Tools**

Microsemi has developed design tools and flows to meet the needs of these three types of designers so they can work together smoothly on a single project (Figure 3-1).

Figure 3-1 • Three Design Roles

### **FPGA** Design

Libero System-on-Chip (SoC) software is Microsemi's comprehensive software toolset for designing with all Microsemi FPGAs and cSoCs. Libero SoC includes industry-leading synthesis, simulation and debug tools from Synopsys<sup>®</sup> and Mentor Graphics<sup>®</sup>, as well as innovative timing and power optimization and analysis.

### **Embedded Design**

Microsemi offers FREE SoftConsole Eclipse based IDE, which includes the GNU C/C++ compiler and GDB debugger. Microsemi also offers evaluation versions of software from Keil and IAR, with full versions available from respective suppliers.

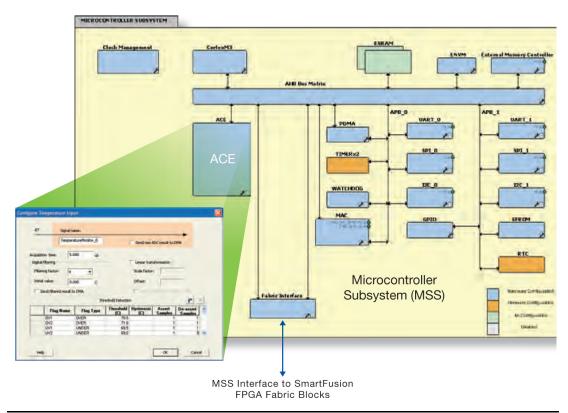

### **Analog Design**

The MSS configurator provides graphical configuration for current, voltage and temperature monitors, sample sequencing setup and post-processing configuration, as well as DAC output.

The MSS configurator creates a bridge between the FPGA fabric and embedded designers so device configuration can be easily shared between multiple developers.

The MSS configurator includes the following:

- A simple configurator for the embedded designer to control the MSS peripherals and I/Os

- A method to import and view a hardware configuration from the FPGA flow into the embedded flow containing the memory map

- · Automatic generation of drivers for any peripherals or soft IP used in the system configuration

- · Comprehensive analog configuration for the programmable analog components

- Creation of a standard MSS block to be used in SmartDesign for connection of FPGA fabric designs and IP

Figure 3-2 • MSS Configurator

## **Global I/O Naming Conventions**

Gmn (Gxxx) refers to Global I/Os. These Global I/Os are used to connect the input to global networks. Global networks have high fanout and low skew. The naming convention for Global I/Os is as follows:

G = Global

m = Global pin location associated with each CCC on the device:

- A (northwest corner)

- B (northeast corner)

- C (east middle)

- D (southeast corner)

- E (southwest corner)

- F (west middle)

n = Global input MUX and pin number of the associated Global location m—A0, A1, A2, B0, B1, B2, C0, C1, or C2.

Global (GL) I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities.

Unused GL pins are configured as inputs with pull-up resistors. See more detailed descriptions of global I/O connectivity in the clocking resources chapter of the *SmartFusion FPGA Fabric User's Guide* and the clock conditioning circuitry chapter of the *SmartFusion Microcontroller Subsystem User's Guide*.

All inputs other than GC/GF are direct inputs into the quadrant clocks. The inputs to the global network are multiplexed, and only one input can be used as a global input. For example, if GAA0 is used as a quadrant global input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs other than GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. For more details, refer to the Global Input Selections section of the SmartFusion Fabric User Guide.

| Name   | Туре   | Polarity/B<br>us Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO_x | In/out |                       | Microcontroller Subsystem (MSS) General Purpose I/O (GPIO). The MSS GPIO pin<br>functions as an input, output, tristate, or bidirectional buffer with configurable interrupt<br>generation and Schmitt trigger support. Input and output signal levels are compatible<br>with the I/O standard selected.                                                                                                                                                                                                                      |

|        |        |                       | Unused GPIO pins are tristated and do not include pull-up or pull-down resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |        |                       | During power-up, the used GPIO pins are tristated with no pull-up or pull-down resistors until Sys boot configures them.                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |        |                       | Some of these pins are also multiplexed with integrated peripherals in the MSS (SPI, I <sup>2</sup> C, and UART). These pins are located in Bank-2 (GPIO_16 to GPIO_31) for A2F060, A2F200, and A2F500 devices.                                                                                                                                                                                                                                                                                                               |

|        |        |                       | GPIOs can be routed to dedicated I/O buffers (MSSIOBUF) or in some cases to the FPGA fabric interface through an IOMUX. This allows GPIO pins to be multiplexed as either I/Os for the FPGA fabric, the ARM <sup>®</sup> Cortex-M3 or for given integrated MSS peripherals. The MSS peripherals are not multiplexed with each other; they are multiplexed only with the GPIO block. For more information, see the General Purpose I/O Block (GPIO) section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| IO     | In/out |                       | FPGA user I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **User Pins**

# **Microsemi**.

SmartFusion Customizable System-on-Chip (cSoC)

| Name             | Туре       | Polarity/<br>Bus Size | Description                                                                                                                                   |  |  |  |  |  |

|------------------|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SPI_1_DO         | Out        | 1                     | Data output. Second SPI.                                                                                                                      |  |  |  |  |  |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |  |  |  |  |  |

| SPI_1_SS         | Out        | 1                     | Slave select (chip select). Second SPI.                                                                                                       |  |  |  |  |  |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |  |  |  |  |  |

| Universal Asynch | hronous Re | eceiver/Trans         | mitter (UART) Peripherals                                                                                                                     |  |  |  |  |  |

| UART_0_RXD       | In         | 1                     | Receive data. First UART.                                                                                                                     |  |  |  |  |  |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |  |  |  |  |  |

| UART_0_TXD       | Out        | 1                     | Transmit data. First UART.                                                                                                                    |  |  |  |  |  |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |  |  |  |  |  |

| UART_1_RXD       | In         | 1                     | Receive data. Second UART.                                                                                                                    |  |  |  |  |  |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |  |  |  |  |  |

| UART_1_TXD       | Out        | 1                     | Transmit data. Second UART.                                                                                                                   |  |  |  |  |  |

|                  |            |                       | Can also be used as an MSS GPIO (see "GPIO_x" on page 5-6).                                                                                   |  |  |  |  |  |

| Ethernet MAC     |            |                       |                                                                                                                                               |  |  |  |  |  |

| MAC_CLK          | In         | Rise                  | Receive clock. 50 MHz ± 50 ppm clock source received from RMII PHY.                                                                           |  |  |  |  |  |

|                  |            |                       | Can be left floating when unused.                                                                                                             |  |  |  |  |  |

| MAC_CRSDV        | In         | High                  | Carrier sense/receive data valid for RMII PHY                                                                                                 |  |  |  |  |  |

|                  |            |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |  |  |  |  |  |

| MAC_MDC          | Out        | Rise                  | RMII management clock                                                                                                                         |  |  |  |  |  |

|                  |            |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |  |  |  |  |  |

| MAC_MDIO         | In/Out     | 1                     | RMII management data input/output                                                                                                             |  |  |  |  |  |

|                  |            |                       | Can also be used as an FPGA User IO (see "IO" on page 5-6).                                                                                   |  |  |  |  |  |

| MAC_RXDx         | In         | 2                     | Ethernet MAC receive data. Data recovered and decoded by PHY. The RXD[0] signal is the least significant bit.                                 |  |  |  |  |  |

|                  |            |                       | Can also be used as an FPGA User I/O (see "IO" on page 5-6).                                                                                  |  |  |  |  |  |

| MAC_RXER         | In         | HIGH                  | Ethernet MAC receive error. If MACRX_ER is asserted during reception, the frame is received and status of the frame is updated with MACRX_ER. |  |  |  |  |  |

|                  |            |                       | Can also be used as an FPGA user I/O (see "IO" on page 5-6).                                                                                  |  |  |  |  |  |

| MAC_TXDx         | Out        | 2                     | Ethernet MAC transmit data. The TXD[0] signal is the least significant bit.                                                                   |  |  |  |  |  |

|                  |            |                       | Can also be used as an FPGA user I/O (see "IO" on page 5-6).                                                                                  |  |  |  |  |  |

| MAC_TXEN         | Out        | HIGH                  | Ethernet MAC transmit enable. When asserted, indicates valid data for the PHY on the TXD port.                                                |  |  |  |  |  |

|                  |            |                       | Can also be used as an FPGA User I/O (see "IO" on page 5-6).                                                                                  |  |  |  |  |  |

Pin Descriptions

# **Analog Front-End Pin-Level Function Multiplexing**

Table 5-2 describes the relationships between the various internal signals found in the analog front-end (AFE) and how they are multiplexed onto the external package pins. Note that, in general, only one function is available for those pads that have numerous functions listed. The exclusion to this rule is when a comparator is used; the ADC can still convert either input side of the comparator.

| Pin   | ADC<br>Channel | DirIn<br>Option | Prescaler | Current<br>Mon. | Temp.<br>Mon. | Compar. | LVTTL      | SDD MUX   | SDD      |

|-------|----------------|-----------------|-----------|-----------------|---------------|---------|------------|-----------|----------|

| ABPS0 | ADC0_CH1       |                 | ABPS0_IN  |                 |               |         |            |           |          |

| ABPS1 | ADC0_CH2       |                 | ABPS1_IN  |                 |               |         |            |           |          |

| ABPS2 | ADC0_CH5       |                 | ABPS2_IN  |                 |               |         |            |           |          |

| ABPS3 | ADC0_CH6       |                 | ABPS3_IN  |                 |               |         |            |           |          |

| ABPS4 | ADC1_CH1       |                 | ABPS4_IN  |                 |               |         |            |           |          |

| ABPS5 | ADC1_CH2       |                 | ABPS5_IN  |                 |               |         |            |           |          |

| ABPS6 | ADC1_CH5       |                 | ABPS6_IN  |                 |               |         |            |           |          |

| ABPS7 | ADC1_CH6       |                 | ABPS7_IN  |                 |               |         |            |           |          |

| ABPS8 | ADC2_CH1       |                 | ABPS8_IN  |                 |               |         |            |           |          |

| ABPS9 | ADC2_CH2       |                 | ABPS9_IN  |                 |               |         |            |           |          |

| ADC0  | ADC0_CH9       | Yes             |           |                 |               | CMP1_P  | LVTTL0_IN  |           |          |

| ADC1  | ADC0_CH10      | Yes             |           |                 |               | CMP1_N  | LVTTL1_IN  | SDDM0_OUT |          |

| ADC2  | ADC0_CH11      | Yes             |           |                 |               | CMP3_P  | LVTTL2_IN  |           |          |

| ADC3  | ADC0_CH12      | Yes             |           |                 |               | CMP3_N  | LVTTL3_IN  | SDDM1_OUT |          |

| ADC4  | ADC1_CH9       | Yes             |           |                 |               | CMP5_P  | LVTTL4_IN  |           |          |

| ADC5  | ADC1_CH10      | Yes             |           |                 |               | CMP5_N  | LVTTL5_IN  | SDDM2_OUT |          |

| ADC6  | ADC1_CH11      | Yes             |           |                 |               | CMP7_P  | LVTTL6_IN  |           |          |

| ADC7  | ADC1_CH12      | Yes             |           |                 |               | CMP7_N  | LVTTL7_IN  | SDDM3_OUT |          |

| ADC8  | ADC2_CH9       | Yes             |           |                 |               | CMP9_P  | LVTTL8_IN  |           |          |

| ADC9  | ADC2_CH10      | Yes             |           |                 |               | CMP9_N  | LVTTL9_IN  | SDDM4_OUT |          |

| ADC10 | ADC2_CH11      | Yes             |           |                 |               |         | LVTTL10_IN |           |          |

| ADC11 | ADC2_CH12      | Yes             |           |                 |               |         | LVTTL11_IN |           |          |

| CM0   | ADC0_CH3       | Yes             |           | CM0_H           |               | CMP0_P  |            |           |          |

| CM1   | ADC0_CH7       | Yes             |           | CM1_H           |               | CMP2_P  |            |           |          |

| CM2   | ADC1_CH3       | Yes             |           | CM2_H           |               | CMP4_P  |            |           |          |

| CM3   | ADC1_CH7       | Yes             |           | CM3_H           |               | CMP6_P  |            |           |          |

| CM4   | ADC2_CH3       | Yes             |           | CM4_H           |               | CMP8_P  |            |           |          |

| SDD0  | ADC0_CH15      |                 |           |                 |               |         |            |           | SDD0_OUT |

| SDD1  | ADC1_CH15      |                 |           |                 |               |         |            |           | SDD1_OUT |

#### Table 5-2 • Relationships Between Signals in the Analog Front-End

Notes:

1. ABPSx\_IN: Input to active bipolar prescaler channel x.

2. CMx\_H/L: Current monitor channel x, high/low side.

3. TMx\_IO: Temperature monitor channel x.

4. CMPx\_P/N: Comparator channel x, positive/negative input.

5. LVTTLx\_IN: LVTTL I/O channel x.

6. SDDMx\_OUT: Output from sigma-delta DAC MUX channel x.

7. SDDx\_OUT: Direct output from sigma-delta DAC channel x.

| Pin  | ADC<br>Channel | DirIn<br>Option | Prescaler | Current<br>Mon. | Temp.<br>Mon. | Compar. | LVTTL | SDD MUX | SDD      |

|------|----------------|-----------------|-----------|-----------------|---------------|---------|-------|---------|----------|

| SDD2 | ADC2_CH15      |                 |           |                 |               |         |       |         | SDD2_OUT |

| TM0  | ADC0_CH4       | Yes             |           | CM0_L           | TM0_IO        | CMP0_N  |       |         |          |

| TM1  | ADC0_CH8       | Yes             |           | CM1_L           | TM1_IO        | CMP2_N  |       |         |          |

| TM2  | ADC1_CH4       | Yes             |           | CM2_L           | TM2_IO        | CMP4_N  |       |         |          |

| TM3  | ADC1_CH8       | Yes             |           | CM3_L           | TM3_IO        | CMP6_N  |       |         |          |

| TM4  | ADC2_CH4       | Yes             |           | CM4_L           | TM4_IO        | CMP8_N  |       |         |          |

#### Table 5-2 • Relationships Between Signals in the Analog Front-End

Notes:

1. ABPSx\_IN: Input to active bipolar prescaler channel x.

2. CMx\_H/L: Current monitor channel x, high/low side.

- 3. TMx\_IO: Temperature monitor channel x.

- 4. CMPx\_P/N: Comparator channel x, positive/negative input.

- 5. LVTTLx\_IN: LVTTL I/O channel x.

6. SDDMx\_OUT: Output from sigma-delta DAC MUX channel x.

7. SDDx\_OUT: Direct output from sigma-delta DAC channel x.

star i Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin | CS288                |                      |                              |  |  |  |  |  |

|-----|----------------------|----------------------|------------------------------|--|--|--|--|--|

| No. | A2F060 Function      | A2F200 Function      | A2F500 Function<br>GNDLPXTAL |  |  |  |  |  |

| K17 | GNDLPXTAL            | GNDLPXTAL            |                              |  |  |  |  |  |

| K19 | GNDMAINXTAL          | GNDMAINXTAL          | GNDMAINXTAL                  |  |  |  |  |  |

| K21 | MAINXIN              | MAINXIN              | MAINXIN                      |  |  |  |  |  |

| L1  | GNDRCOSC             | GNDRCOSC             | GNDRCOSC                     |  |  |  |  |  |

| L3  | VCCFPGAIOB5          | VCCFPGAIOB5          | VCCFPGAIOB5                  |  |  |  |  |  |

| L5  | EMC_DB[2]/IO37NPB5V0 | EMC_DB[2]/IO60NPB5V0 | EMC_DB[2]/IO77NPB5V0         |  |  |  |  |  |

| L6  | NC                   | GNDQ                 | GNDQ                         |  |  |  |  |  |

| L8  | VCC                  | VCC                  | VCC                          |  |  |  |  |  |

| L9  | GND                  | GND                  | GND                          |  |  |  |  |  |

| L10 | VCC                  | VCC                  | VCC                          |  |  |  |  |  |

| L12 | VCC                  | VCC                  | VCC                          |  |  |  |  |  |

| L13 | GND                  | GND                  | GND                          |  |  |  |  |  |

| L14 | VCC                  | VCC                  | VCC                          |  |  |  |  |  |

| L16 | VCCLPXTAL            | VCCLPXTAL            | VCCLPXTAL                    |  |  |  |  |  |

| L17 | VDDBAT               | VDDBAT               | VDDBAT                       |  |  |  |  |  |

| L19 | LPXIN                | LPXIN                | LPXIN                        |  |  |  |  |  |

| L21 | MAINXOUT             | MAINXOUT             | MAINXOUT                     |  |  |  |  |  |

| M1  | VCCRCOSC             | VCCRCOSC             | VCCRCOSC                     |  |  |  |  |  |

| M3  | MSS_RESET_N          | MSS_RESET_N          | MSS_RESET_N                  |  |  |  |  |  |

| M5  | GPIO_5/IO28RSB4V0    | GPIO_5/IO42RSB4V0    | GPIO_5/IO51RSB4V0            |  |  |  |  |  |

| M6  | GND                  | GND                  | GND                          |  |  |  |  |  |

| M8  | GND                  | GND                  | GND                          |  |  |  |  |  |

| M9  | VCC                  | VCC                  | VCC                          |  |  |  |  |  |

| M10 | GND                  | GND                  | GND                          |  |  |  |  |  |

| M11 | VCC                  | VCC                  | VCC                          |  |  |  |  |  |

| M12 | GND                  | GND                  | GND                          |  |  |  |  |  |

| M13 | VCC                  | VCC                  | VCC                          |  |  |  |  |  |

| M14 | GND                  | GND                  | GND                          |  |  |  |  |  |

| M16 | TMS                  | TMS                  | TMS                          |  |  |  |  |  |

| M17 | VJTAG                | VJTAG                | VJTAG                        |  |  |  |  |  |

| M19 | TDO                  | TDO                  | TDO                          |  |  |  |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

**CS288** Pin A2F060 Function A2F200 Function A2F500 Function No. U5 VCC33SDD0 VCC33SDD0 VCC33SDD0 U6 VCC15A VCC15A VCC15A U7 NC ABPS3 ABPS3 U8 NC ADC2 ADC2 U9 NC VCC33ADC0 VCC33ADC0 U10 GND15ADC0 GND15ADC1 GND15ADC1 U11 VCC33ADC0 VCC33ADC1 VCC33ADC1 U12 ADC10 ADC7 ADC7 U13 ABPS0 ABPS6 ABPS6 U14 **GNDTM0** GNDTM1 GNDTM1 SPI\_1\_CLK/GPIO\_26 U15 SPI\_1\_CLK/GPIO\_26 SPI\_1\_CLK/GPIO\_26 U16 SPI 0 CLK/GPIO 18 SPI 0 CLK/GPIO 18 SPI 0 CLK/GPIO 18 U17 SPI 0 SS/GPIO 19 SPI 0 SS/GPIO 19 SPI 0 SS/GPIO 19 U19 GND GND GND SPI 1 DO/GPIO 24 U21 SPI 1 DO/GPIO 24 SPI 1 DO/GPIO 24 V1 NC MAC CLK MAC CLK V3 GNDSDD0 GNDSDD0 GNDSDD0 V19 SPI 1 DI/GPIO 25 SPI 1 DI/GPIO 25 SPI 1 DI/GPIO 25 VCCMSSIOB2 V21 VCCMSSIOB2 VCCMSSIOB2 W1 PCAP PCAP PCAP W3 NCAP NCAP NCAP W4 ADC2 CM0 CM0 W5 ADC3 TM0 TM0 W6 ADC4 TM1 TM1 W7 NC ADC0 ADC0 W8 NC ADC3 ADC3 W9 NC GND33ADC0 GND33ADC0 W10 VCC15ADC0 VCC15ADC1 VCC15ADC1 W11 GND33ADC0 GND33ADC1 GND33ADC1 W12 ADC5 ADC8 ADC5 W13 CM0 CM3 CM3

Notes:

🔨 🤇 Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

FG256 Pin A2F060 Function A2F200 Function No. A2F500 Function K12 UART 0 RXD/GPIO 21 UART 0 RXD/GPIO 21 UART 0 RXD/GPIO 21 K13 GND GND GND K14 UART 1 TXD/GPIO 28 UART 1 TXD/GPIO 28 UART 1 TXD/GPIO 28 K15 UART 1 RXD/GPIO 29 UART 1 RXD/GPIO 29 UART\_1\_RXD/GPIO\_29 K16 UART\_0\_TXD/GPIO\_20 UART\_0\_TXD/GPIO\_20 UART\_0\_TXD/GPIO\_20 L1 GND GND GND L2 GPIO 2/IO31RSB4V0 MAC TXEN/IO52RSB4V0 MAC TXEN/IO61RSB4V0 L3 GPIO 3/IO30RSB4V0 MAC CRSDV/IO51RSB4V0 MAC CRSDV/IO60RSB4V0 L4 GPIO 4/IO29RSB4V0 MAC RXER/IO50RSB4V0 MAC RXER/IO59RSB4V0 L5 GPIO 9/IO24RSB4V0 MAC CLK MAC CLK GND GND 16 GND L7 VCC VCC VCC GND GND GND L8 L9 VCC VCC VCC L10 GND GND GND L11 VCCMSSIOB2 VCCMSSIOB2 VCCMSSIOB2 L12 SPI 1 DO/GPIO 24 SPI 1 DO/GPIO 24 SPI\_1\_DO/GPIO\_24 L13 SPI 1 SS/GPIO 27 SPI 1 SS/GPIO 27 SPI 1 SS/GPIO 27 L14 SPI 1 CLK/GPIO 26 SPI 1 CLK/GPIO 26 SPI 1 CLK/GPIO 26 L15 SPI\_1\_DI/GPIO\_25 SPI\_1\_DI/GPIO\_25 SPI\_1\_DI/GPIO\_25 L16 GND GND GND M1 GPIO 5/IO28RSB4V0 MAC TXD[0]/IO56RSB4V0 MAC TXD[0]/IO65RSB4V0 M2 GPIO 6/IO27RSB4V0 MAC TXD[1]/IO55RSB4V0 MAC TXD[1]/IO64RSB4V0 MAC RXD[0]/IO54RSB4V0 GPIO 7/IO26RSB4V0 MAC RXD[0]/IO63RSB4V0 M3 M4 GND GND GND NC ADC3 ADC3 M5 M6 NC GND15ADC0 GND15ADC0 GND33ADC1 M7 GND33ADC0 GND33ADC1 M8 GND33ADC0 GND33ADC1 GND33ADC1 ADC7 M9 ADC4 ADC4 M10 **GNDTM0** GNDTM1 GNDTM1

Notes:

🔨 🤇 Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

\*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

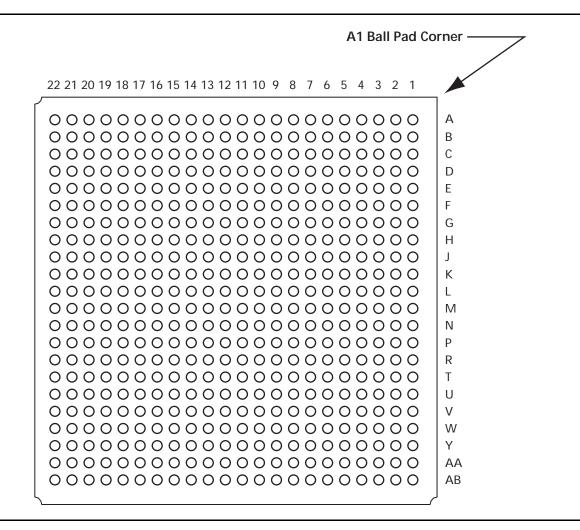

### FG484

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

🌜 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | FG484                     |                           |  |  |  |

|------------|---------------------------|---------------------------|--|--|--|

| Pin Number | A2F200 Function           | A2F500 Function           |  |  |  |

| A1         | GND                       | GND                       |  |  |  |

| A2         | NC                        | NC                        |  |  |  |

| A3         | NC                        | NC                        |  |  |  |

| A4         | GND                       | GND                       |  |  |  |

| A5         | EMC_CS0_N/GAB0/IO01NDB0V0 | EMC_CS0_N/GAB0/IO05NDB0V0 |  |  |  |

| A6         | EMC_CS1_N/GAB1/IO01PDB0V0 | EMC_CS1_N/GAB1/IO05PDB0V0 |  |  |  |

| A7         | GND                       | GND                       |  |  |  |

| A8         | EMC_AB[0]/IO04NDB0V0      | EMC_AB[0]/IO06NDB0V0      |  |  |  |

| A9         | EMC_AB[1]/IO04PDB0V0      | EMC_AB[1]/IO06PDB0V0      |  |  |  |

| A10        | GND                       | GND                       |  |  |  |

| A11        | NC                        | NC                        |  |  |  |

| A12        | EMC_AB[7]/IO07PDB0V0      | EMC_AB[7]/IO12PDB0V0      |  |  |  |

| A13        | GND                       | GND                       |  |  |  |

| A14        | EMC_AB[12]/IO10NDB0V0     | EMC_AB[12]/IO14NDB0V0     |  |  |  |

| A15        | EMC_AB[13]/IO10PDB0V0     | EMC_AB[13]/IO14PDB0V0     |  |  |  |

| A16        | GND                       | GND                       |  |  |  |

| A17        | NC                        | IO16NDB0V0                |  |  |  |

| A18        | NC                        | IO16PDB0V0                |  |  |  |

| A19        | GND                       | GND                       |  |  |  |

| A20        | NC                        | NC                        |  |  |  |

| A21        | NC                        | NC                        |  |  |  |

| A22        | GND                       | GND                       |  |  |  |

| AA1        | GPIO_4/IO43RSB4V0         | GPIO_4/IO52RSB4V0         |  |  |  |

| AA2        | GPIO_12/IO37RSB4V0        | GPIO_12/IO46RSB4V0        |  |  |  |

| AA3        | MAC_MDC/IO48RSB4V0        | MAC_MDC/IO57RSB4V0        |  |  |  |

| AA4        | MAC_RXER/IO50RSB4V0       | MAC_RXER/IO59RSB4V0       |  |  |  |

| AA5        | MAC_TXD[0]/IO56RSB4V0     | MAC_TXD[0]/IO65RSB4V0     |  |  |  |

| AA6        | ABPS0                     | ABPS0                     |  |  |  |

| AA7        | TM1                       | TM1                       |  |  |  |

| AA8        | ADC1                      | ADC1                      |  |  |  |

| AA9        | GND15ADC1                 | GND15ADC1                 |  |  |  |

| AA10       | GND33ADC1                 | GND33ADC1                 |  |  |  |

| AA11       | CM3                       | CM3                       |  |  |  |

| AA12       | GNDTM1                    | GNDTM1                    |  |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

2. \*: Indicates that the signal assigned to the pins as a CLKBUF/CLKBUF\_LVPECL/CLKBUF\_LVDS goes through a glitchless mux. In order for the glitchless mux to operate correctly, the signal must be a free-running clock signal. Refer to the 'Glitchless MUX' section in the SmartFusion Microcontroller Subsystem User's Guide for more details.

Datasheet Information

| Revision                      | Changes                                                                                                                                                                                                                                      | Page          |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 10<br>(January 2013) | The "SmartFusion cSoC Family Product Table" section has been updated to specify that External Memory Controller support for A2F060-TQ144 is not available (SAR 41555).                                                                       |               |

|                               | The following Note was added to the "Package I/Os: MSS + FPGA I/Os" table (SAR 41027): "There are no LVTTL capable direct inputs available on A2F060 devices."                                                                               |               |

|                               | The "Product Ordering Codes" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43218).                    |               |

|                               | Added a note to Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> (SAR 43428): The programming temperature range supported is $T_{ambient} = 0^{\circ}C$ to 85°C.                                                                  |               |

|                               | Statements about the state of the I/Os during programming were updated in the following sections: "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" and "User I/O Naming Conventions" (SAR 43380). |               |

|                               | In Table 2-4 • FPGA and Embedded Flash Programming, Storage and Operating Limits, the upper value of temperature ranges was corrected from "Min." to "Max." (SAR 41826).                                                                     |               |

|                               | Information for A2F200M3F-CS288 was added to Table 2-6 • Package Thermal Resistance. The die size column was removed (SARs 41828, 42168).<br>Also added details for A2F200M3F-PQG208I (SAR 35728).                                           | 2-7           |

|                               | Added the following note to Table 2-65 • LVDS and Table 2-68 • LVPECL: "The above mentioned timing parameters correspond to 24mA drive strength." (SAR 43457)                                                                                | 2-41,<br>2-43 |

|                               | The note in Table 2-86 • SmartFusion CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 34816).                                                            | 2-63          |

|                               | The SRAM collision data in Table 2-87 • RAM4K9 and Table 2-88 • RAM512X18 was updated (SAR 38583).                                                                                                                                           | 2-69,2-70     |

|                               | The maximum input bias current for comparators 1, 3, 5, 7, and 9, in Table 2-97 • Comparator Performance Specifications, was revised from 60 to 100 nA (SAR 36008).                                                                          | 2-84          |