Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Details                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Active                                                                      |

| Architecture            | MCU, FPGA                                                                   |

| Core Processor          | ARM® Cortex®-M3                                                             |

| Flash Size              | 512KB                                                                       |

| RAM Size                | 64KB                                                                        |

| Peripherals             | DMA, POR, WDT                                                               |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART                        |

| Speed                   | 80MHz                                                                       |

| Primary Attributes      | ProASIC®3 FPGA, 500K Gates, 11520 D-Flip-Flops                              |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                          |

| Package / Case          | 288-TFBGA, CSPBGA                                                           |

| Supplier Device Package | 288-CSP (11x11)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f500m3g-csg288i |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – SmartFusion Family Overview

## Introduction

The SmartFusion<sup>®</sup> family of cSoCs builds on the technology first introduced with the Fusion mixed signal FPGAs. SmartFusion cSoCs are made possible by integrating FPGA technology with programmable high-performance analog and hardened ARM Cortex-M3 microcontroller blocks on a flash semiconductor process. The SmartFusion cSoC takes its name from the fact that these three discrete technologies are integrated on a single chip, enabling the lowest cost of ownership and smallest footprint solution to you.

# **General Description**

## Microcontroller Subsystem (MSS)

The MSS is composed of a 100 MHz Cortex-M3 processor and integrated peripherals, which are interconnected via a multi-layer AHB bus matrix (ABM). This matrix allows the Cortex-M3 processor, FPGA fabric master, Ethernet media access controller (MAC), when available, and peripheral DMA (PDMA) controller to act as masters to the integrated peripherals, FPGA fabric, embedded nonvolatile memory (eNVM), embedded synchronous RAM (eSRAM), external memory controller (EMC), and analog compute engine (ACE) blocks.

SmartFusion cSoCs of different densities offer various sets of integrated peripherals. Available peripherals include SPI, I<sup>2</sup>C, and UART serial ports, embedded FlashROM (EFROM), 10/100 Ethernet MAC, timers, phase-locked loops (PLLs), oscillators, real-time counters (RTC), and peripheral DMA controller (PDMA).

## **Programmable Analog**

### Analog Front-End (AFE)

SmartFusion cSoCs offer an enhanced analog front-end compared to Fusion devices. The successive approximation register analog-to-digital converters (SAR ADC) are similar to those found on Fusion devices. SmartFusion cSoC also adds first order sigma-delta digital-to-analog converters (SDD DAC).

SmartFusion cSoCs can handle multiple analog signals simultaneously with its signal conditioning blocks (SCBs). SCBs are made of a combination of active bipolar prescalers (ABPS), comparators, current monitors and temperature monitors. ABPS modules allow larger bipolar voltages to be fed to the ADC. Current monitors take the voltage across an external sense resistor and convert it to a voltage suitable for the ADC input range. Similarly, the temperature monitor reads the current through an external PN-junction (diode or transistor) and converts it internally for the ADC. The SCB also includes comparators to monitor fast signal thresholds without using the ADC. The output of the comparators can be fed to the analog compute engine or the ADC.

### Analog Compute Engine (ACE)

The mixed signal blocks found in SmartFusion cSoCs are controlled and connected to the rest of the system via a dedicated processor called the analog compute engine (ACE). The role of the ACE is to offload control of the analog blocks from the Cortex-M3, thus offering faster throughput or better power consumption compared to a system where the main processor is in charge of monitoring the analog resources. The ACE is built to handle sampling, sequencing, and post-processing of the ADCs, DACs, and SCBs.

SmartFusion Family Overview

| om file Save to file | e                     |            | 🗖 Show BSR D            |

|----------------------|-----------------------|------------|-------------------------|

| Port Name            | Macro Cell            | Pin Number | 1/O State (Output Only) |

| BIST                 | ADLIB:INBUF           | T2         | 1                       |

| BYPASS_IO            | ADLIB:INBUF           | K1         | 1                       |

| CLK                  | ADLIB:INBUF           | B1         | 1                       |

| ENOUT                | ADLIB:INBUF           | J16        | 1                       |

| LED                  | ADLIB:OUTBUF          | M3         | 0                       |

| MONITOR[0]           | ADLIB:OUTBUF          | B5         | 0                       |

| MONITOR[1]           | ADLIB:OUTBUF          | C7         | Z                       |

| MONITOR[2]           | ADLIB:OUTBUF          | D9         | Z                       |

| MONITOR[3]           | ADLIB:OUTBUF          | D7         | Z                       |

| MONITOR[4]           | ADLIB:OUTBUF          | A11        | Z                       |

| OEa                  | ADLIB:INBUF           | E4         | Z                       |

| OEb                  | ADLIB:INBUF           | F1         | Z                       |

| OSC_EN               | ADLIB:INBUF           | К3         | Z                       |

| PAD[10]              | ADLIB:BIBUF_LVCMOS33U | M8         | Z                       |

| PAD[11]              | ADLIB:BIBUF_LVCMOS33D | R7         | Z                       |

| PAD[12]              | ADLIB:BIBUF_LVCMOS33U | D11        | Z                       |

| PAD[13]              | ADLIB:BIBUF_LVCMOS33D | C12        | Z                       |

| PAD[14]              | ADLIB:BIBUF_LVCMOS33U | R6         | Z                       |

### *Figure 1-1* • I/O States During Programming Window

- 6. Click OK to return to the FlashPoint Programming File Generator window.

- Note: I/O States During programming are saved to the ADB and resulting programming files after completing programming file generation.

# 2 – SmartFusion DC and Switching Characteristics

# **General Specifications**

### **Operating Conditions**

Stresses beyond the operating conditions listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-3 on page 2-3 is not implied.

| Symbol                        | Parameter                                                | Limits                                                                                                                                                          | Units |

|-------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| VCC                           | DC core supply voltage                                   | –0.3 to 1.65                                                                                                                                                    | V     |

| VJTAG                         | JTAG DC voltage                                          | –0.3 to 3.75                                                                                                                                                    | V     |

| VPP                           | Programming voltage                                      | –0.3 to 3.75                                                                                                                                                    | V     |

| VCCPLLx                       | Analog power supply (PLL)                                | –0.3 to 1.65                                                                                                                                                    | V     |

| VCCFPGAIOBx                   | DC FPGA I/O buffer supply voltage                        | –0.3 to 3.75                                                                                                                                                    | V     |

| VCCMSSIOBx                    | DC MSS I/O buffer supply voltage                         | –0.3 to 3.75                                                                                                                                                    | V     |

| VI                            | I/O input voltage                                        | –0.3 V to 3.6 V                                                                                                                                                 | V     |

|                               |                                                          | (when I/O hot insertion mode is enabled)<br>-0.3 V to (VCCxxxxIOBx + 1 V) or 3.6 V,<br>whichever voltage is lower (when I/O hot-<br>insertion mode is disabled) |       |

| VCC33A                        | Analog clean 3.3 V supply to the analog circuitry        | -0.3 to 3.75                                                                                                                                                    | V     |

| VCC33ADCx                     | Analog 3.3 V supply to ADC                               | -0.3 to 3.75                                                                                                                                                    | V     |

| VCC33AP                       | Analog clean 3.3 V supply to the charge pump             | -0.3 to 3.75                                                                                                                                                    | V     |

| VCC33SDDx                     | Analog 3.3 V supply to the sigma-delta DAC               | -0.3 to 3.75                                                                                                                                                    | V     |

| VAREFx                        | Voltage reference for ADC                                | 1.0 to 3.75                                                                                                                                                     | V     |

| VCCRCOSC                      | Analog supply to the integrated RC oscillator            | -0.3 to 3.75                                                                                                                                                    | V     |

| VDDBAT                        | External battery supply                                  | -0.3 to 3.75                                                                                                                                                    | V     |

| VCCMAINXTAL                   | Analog supply to the main crystal oscillator             | -0.3 to 3.75                                                                                                                                                    | V     |

| VCCLPXTAL                     | Analog supply to the low power 32 kHz crystal oscillator | –0.3 to 3.75                                                                                                                                                    | V     |

| VCCENVM                       | Embedded nonvolatile memory supply                       | -0.3 to 1.65                                                                                                                                                    | V     |

| VCCESRAM                      | Embedded SRAM supply                                     | –0.3 to 1.65                                                                                                                                                    | V     |

| VCC15A                        | Analog 1.5 V supply to the analog circuitry              | -0.3 to 1.65                                                                                                                                                    | V     |

| VCC15ADCx                     | Analog 1.5 V supply to the ADC                           | -0.3 to 1.65                                                                                                                                                    | V     |

| T <sub>STG</sub> <sup>1</sup> | Storage temperature                                      | –65 to +150                                                                                                                                                     | °C    |

| T <sub>J</sub> <sup>1</sup>   | Junction temperature                                     | 125                                                                                                                                                             | °C    |

#### Table 2-1 • Absolute Maximum Ratings

Notes:

1. For flash programming and retention maximum limits, refer to Table 2-4 on page 2-4. For recommended operating conditions, refer to Table 2-3 on page 2-3.

2. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-5 on page 2-4.

| Symbol                   | Paramete                                                | er <sup>1</sup>               | Commercial                  | Industrial     | Units |

|--------------------------|---------------------------------------------------------|-------------------------------|-----------------------------|----------------|-------|

| TJ                       | Junction temperature                                    |                               | 0 to +85                    | -40 to +100    | °C    |

| VCC <sup>2</sup>         | 1.5 V DC core supply voltage                            |                               | 1.425 to 1.575              | 1.425 to 1.575 | V     |

| VJTAG                    | JTAG DC voltage                                         |                               | 1.425 to 3.6 1.425 to 3.6   |                | V     |

| VPP                      | Programming voltage                                     | Programming mode <sup>3</sup> | 3.15 to 3.45                | 3.15 to 3.45   | V     |

|                          |                                                         | Operation <sup>4</sup>        | 0 to 3.6                    | 0 to 3.6       | V     |

| VCCPLLx                  | Analog power supply (PLL)                               | •                             | 1.425 to 1.575              | 1.425 to 1.575 | V     |

| VCCFPGAIOBx/             | 1.5 V DC supply voltage                                 |                               | 1.425 to 1.575              | 1.425 to 1.575 | V     |

| VCCMSSIOBx <sup>5</sup>  | 1.8 V DC supply voltage                                 |                               | 1.7 to 1.9                  | 1.7 to 1.9     | V     |

|                          | 2.5 V DC supply voltage                                 | 2.3 to 2.7                    | 2.3 to 2.7                  | V              |       |

|                          | 3.3 V DC supply voltage                                 | 3.0 to 3.6                    | 3.0 to 3.6                  | V              |       |

|                          | LVDS differential I/O                                   | 2.375 to 2.625                | 2.375 to 2.625              | V              |       |

|                          | LVPECL differential I/O                                 | 3.0 to 3.6                    | 3.0 to 3.6                  | V              |       |

| VCC33A <sup>6</sup>      | Analog clean 3.3 V supply to t                          | he analog circuitry           | 3.15 to 3.45                | 3.15 to 3.45   | V     |

| VCC33ADCx <sup>6</sup>   | Analog 3.3 V supply to ADC                              |                               | 3.15 to 3.45                | 3.15 to 3.45   | V     |

| VCC33AP <sup>6</sup>     | Analog clean 3.3 V supply to t                          | he charge pump                | 3.15 to 3.45                | 3.15 to 3.45   | V     |

| VCC33SDDx <sup>6</sup>   | Analog 3.3 V supply to sigma-                           | delta DAC                     | 3.15 to 3.45 3.15 to 3.45   |                | V     |

| VAREFx                   | Voltage reference for ADC                               |                               | 2.527 to 3.3                | 2.527 to 3.3   | V     |

| VCCRCOSC                 | Analog supply to the integrate                          | d RC oscillator               | 3.15 to 3.45                | 3.15 to 3.45   | V     |

| VDDBAT                   | External battery supply                                 |                               | 2.7 to 3.63                 | 2.7 to 3.63    | V     |

| VCCMAINXTAL <sup>6</sup> | Analog supply to the main cry                           | stal oscillator               | 3.15 to 3.45                | 3.15 to 3.45   | V     |

| VCCLPXTAL <sup>6</sup>   | Analog supply to the low power 32 KHz crysta oscillator |                               | 3.15 to 3.45                | 3.15 to 3.45   | V     |

| VCCENVM                  | Embedded nonvolatile memor                              | y supply                      | 1.425 to 1.575              | 1.425 to 1.575 | V     |

| VCCESRAM                 | Embedded SRAM supply                                    |                               | 1.425 to 1.575              | 1.425 to 1.575 | V     |

| VCC15A <sup>2</sup>      | Analog 1.5 V supply to the an                           | alog circuitry                | 1.425 to 1.575 1.425 to 1.5 |                | V     |

| VCC15ADCx <sup>2</sup>   | Analog 1.5 V supply to the AD                           | OC                            | 1.425 to 1.575              | 1.425 to 1.575 | V     |

### Table 2-3 • Recommended Operating Conditions<sup>5,6</sup>

Notes:

1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. The Programming temperature range supported is  $T_{ambient} = 0^{\circ}C$  to 85°C.

4. VPP can be left floating during operation (not programming mode).

5. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-19 on page 2-23. VCCxxxxIOBx should be at the same voltage within a given I/O bank.

6. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

SmartFusion DC and Switching Characteristics

### Theta-JA

Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is determined under standard conditions specified by JEDEC (JESD-51), but it has little relevance in actual performance of the product. It should be used with caution but is useful for comparing the thermal performance of one package to another.

A sample calculation showing the maximum power dissipation allowed for the A2F200-FG484 package under forced convection of 1.0 m/s and 75°C ambient temperature is as follows:

Maximum Power Allowed =

$$\frac{T_{J(MAX)} - T_{A(MAX)}}{\theta_{JA}}$$

EQ 4

where

$\theta_{JA}$  = 19.00°C/W (taken from Table 2-6 on page 2-7).

$T_A = 75.00^{\circ}C$

Maximum Power Allowed =  $\frac{100.00^{\circ}C - 75.00^{\circ}C}{19.00^{\circ}C/W} = 1.3 W$

EQ 5

The power consumption of a device can be calculated using the Microsemi SoC Products Group power calculator. The device's power consumption must be lower than the calculated maximum power dissipation by the package. If the power consumption is higher than the device's maximum allowable power dissipation, a heat sink can be attached on top of the case, or the airflow inside the system must be increased.

### Theta-JB

Junction-to-board thermal resistance ( $\theta_{JB}$ ) measures the ability of the package to dissipate heat from the surface of the chip to the PCB. As defined by the JEDEC (JESD-51) standard, the thermal resistance from junction to board uses an isothermal ring cold plate zone concept. The ring cold plate is simply a means to generate an isothermal boundary condition at the perimeter. The cold plate is mounted on a JEDEC standard board with a minimum distance of 5.0 mm away from the package edge.

### Theta-JC

Junction-to-case thermal resistance ( $\theta_{JC}$ ) measures the ability of a device to dissipate heat from the surface of the chip to the top or bottom surface of the package. It is applicable for packages used with external heat sinks. Constant temperature is applied to the surface in consideration and acts as a boundary condition. This only applies to situations where all or nearly all of the heat is dissipated through the surface in consideration.

### Calculation for Heat Sink

For example, in a design implemented in an A2F200-FG484 package with 2.5 m/s airflow, the power consumption value using the power calculator is 3.00 W. The user-dependent  $T_a$  and  $T_j$  are given as follows:

$T_J = 100.00^{\circ}C$  $T_{\Delta} = 70.00^{\circ}C$

From the datasheet:

$\theta_{JA} = 17.00^{\circ}C/W$  $\theta_{JC} = 8.28^{\circ}C/W$

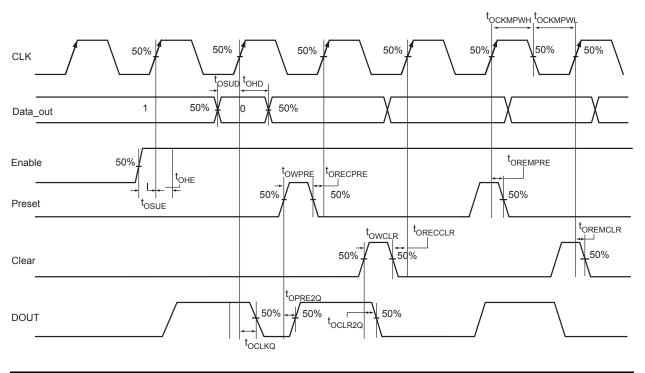

### **Output Register**

### Figure 2-17 • Output Register Timing Diagram

### **Timing Characteristics**

# Table 2-72 • Output Data Register Propagation DelaysWorst Commercial-Case Conditions: TJ = 85°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -1   | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 0.60 | 0.72 | ns    |

| tosud                | Data Setup Time for the Output Data Register                         | 0.32 | 0.38 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00 | ns    |

| t <sub>OSUE</sub>    | Enable Setup Time for the Output Data Register                       | 0.44 | 0.53 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.82 | 0.98 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.82 | 0.98 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.23 | 0.27 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.23 | 0.27 | ns    |

| towclr               | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.22 | 0.22 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.22 | 0.22 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.36 | 0.36 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.32 | 0.32 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## **Timing Characteristics**

### Table 2-89 • FIFO

| Parameter            | Description                                       | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.40 | 1.68 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.02 | 0.02 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.19 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.19 | 0.22 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.39 | 2.87 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.91 | 1.09 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.74 | 2.09 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.66 | 1.99 | ns    |

| t <sub>CKAF</sub>    | Clock HIGH to Almost Empty/Full Flag Valid        | 6.29 | 7.54 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.72 | 2.06 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.22 | 7.47 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (flow-through)    | 0.94 | 1.12 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.94 | 1.12 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.35 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.52 | 1.83 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.22 | 0.22 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.28 | 3.28 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 305  | 305  | MHz   |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

# Embedded Nonvolatile Memory Block (eNVM)

## **Electrical Characteristics**

Table 2-90 describes the eNVM maximum performance.

### *Table 2-90* • eNVM Block Timing, Worst Commercial Case Conditions: T<sub>J</sub> = 85°C, VCC = 1.425 V

|           |                                                                         | A2F060 |      | A2F060 A2I |      | A2F060 A2F200 |      | A2F500 |  |  |

|-----------|-------------------------------------------------------------------------|--------|------|------------|------|---------------|------|--------|--|--|

| Parameter | Description                                                             | -1     | Std. | -1         | Std. | -1            | Std. | Units  |  |  |

|           | Maximum frequency for clock for the control logic – 5 cycles (5:1:1:1*) | 50     | 50   | 50         | 50   | 50            | 50   | MHz    |  |  |

|           | Maximum frequency for clock for the control logic – 6 cycles (6:1:1:1*) | 100    | 80   | 100        | 80   | 100           | 80   | MHz    |  |  |

*Note:* \*6:1:1:1 indicates 6 cycles for the first access and 1 each for the next three accesses. 5:1:1:1 indicates 5 cycles for the first access and 1 each for the next three accesses.

Note: \*Moving from 5:1:1:1 mode to 6:1:1:1 mode results in throughput change that is dependent on the system functionality. When the Cortex-M3 code is executed from eNVM - with sequential firmware (sequential address reads), the throughput reduction can be around 10%.

# **Embedded FlashROM (eFROM)**

## **Electrical Characteristics**

Table 2-91 describes the eFROM maximum performance

| Parameter         | Description                     | -1    | Std.  | Units |

|-------------------|---------------------------------|-------|-------|-------|

| t <sub>CK2Q</sub> | Clock to out per configuration* | 28.68 | 32.98 | ns    |

| F <sub>max</sub>  | Maximum Clock frequency         | 15.00 | 15.00 | MHz   |

## **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-19 for more details.

### **Timing Characteristics**

### Table 2-92 • JTAG 1532

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter          | Description                 | -1   | Std. | Units |

|--------------------|-----------------------------|------|------|-------|

| t <sub>DISU</sub>  | Test Data Input Setup Time  | 0.67 | 0.77 | ns    |

| t <sub>DIHD</sub>  | Test Data Input Hold Time   | 1.33 | 1.53 | ns    |

| t <sub>TMSSU</sub> | Test Mode Select Setup Time | 0.67 | 0.77 | ns    |

| t <sub>TMDHD</sub> | Test Mode Select Hold Time  | 1.33 | 1.53 | ns    |

| t <sub>TCK2Q</sub> | Clock to Q (data out)       | 8.00 | 9.20 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

SmartFusion DC and Switching Characteristics

#### Table 2-98 • Analog Sigma-Delta DAC (continued)

| Specification                                                              | Test Conditions                                  | Min. | Тур. | Max. | Units |

|----------------------------------------------------------------------------|--------------------------------------------------|------|------|------|-------|

| Sigma-delta DAC power supply curren<br>requirements (not including VAREFx) | Input = 0, EN = 1<br>(operational mode)          |      |      |      |       |

|                                                                            | VCC33SDDx                                        |      | 30   | 35   | μA    |

|                                                                            | VCC15A                                           |      | 3    | 5    | μA    |

|                                                                            | Input = Half scale, EN = 1<br>(operational mode) |      |      |      |       |

|                                                                            | VCC33SDDx                                        |      | 160  | 165  | μA    |

|                                                                            | VCC15A                                           |      | 33   | 35   | μA    |

|                                                                            | Input = Full scale, EN = 1<br>(operational mode) |      |      |      |       |

|                                                                            | VCC33SDDx                                        |      | 280  | 285  | μA    |

|                                                                            | VCC15A                                           |      | 70   | 75   | μA    |

Note: \*FS is full-scale error, defined as the difference between the actual value that triggers the transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error. Refer to the Analog-to-Digital Converter chapter of the SmartFusion Programmable Analog User's Guide for more information.

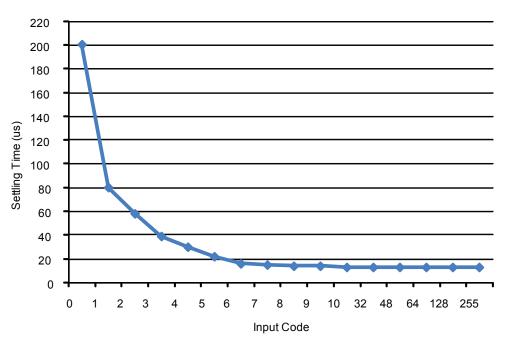

### Sigma Delta DAC Settling Time

Figure 2-44 • Sigma-Delta DAC Setting Time

# **5 – Pin Descriptions**

# **Supply Pins**

| Name        | Туре   | Description                                                                                                                                                                                                                                                                                                                                                |  |

|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND         | Ground | Digital ground to the FPGA fabric, microcontroller subsystem and GPIOs                                                                                                                                                                                                                                                                                     |  |

| GND15ADC0   | Ground | Quiet analog ground to the 1.5 V circuitry of the first analog-to-digital converter (ADC)                                                                                                                                                                                                                                                                  |  |

| GND15ADC1   | Ground | Quiet analog ground to the 1.5 V circuitry of the second ADC                                                                                                                                                                                                                                                                                               |  |

| GND15ADC2   | Ground | Quite analog ground to the 1.5 V circuitry of the third ADC                                                                                                                                                                                                                                                                                                |  |

| GND33ADC0   | Ground | Quiet analog ground to the 3.3 V circuitry of the first ADC                                                                                                                                                                                                                                                                                                |  |

| GND33ADC1   | Ground | Quiet analog ground to the 3.3 V circuitry of the second ADC                                                                                                                                                                                                                                                                                               |  |

| GND33ADC2   | Ground | Quiet analog ground to the 3.3 V circuitry of the third ADC                                                                                                                                                                                                                                                                                                |  |

| GNDA        | Ground | Quiet analog ground to the analog front-end                                                                                                                                                                                                                                                                                                                |  |

| GNDAQ       | Ground | Quiet analog ground to the analog I/O of SmartFusion cSoCs                                                                                                                                                                                                                                                                                                 |  |

| GNDENVM     | Ground | Digital ground to the embedded nonvolatile memory (eNVM)                                                                                                                                                                                                                                                                                                   |  |

| GNDLPXTAL   | Ground | Analog ground to the low power 32 KHz crystal oscillator circuitry                                                                                                                                                                                                                                                                                         |  |

| GNDMAINXTAL | Ground | Analog ground to the main crystal oscillator circuitry                                                                                                                                                                                                                                                                                                     |  |

| GNDQ        | Ground | Quiet digital ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ needs to always be connected on the board to GND. |  |

| GNDRCOSC    | Ground | Analog ground to the integrated RC oscillator circuit                                                                                                                                                                                                                                                                                                      |  |

| GNDSDD0     | Ground | Analog ground to the first sigma-delta DAC                                                                                                                                                                                                                                                                                                                 |  |

| GNDSDD1     | Ground | Common analog ground to the second and third sigma-delta DACs                                                                                                                                                                                                                                                                                              |  |

| GNDTM0      | Ground | Analog temperature monitor common ground for signal conditioning blocks SCB 0 and SCB 1 (see information for pins "TM0" and "TM1" in the "Analog Front-End (AFE)" section on page 5-14).                                                                                                                                                                   |  |

| GNDTM1      | Ground | Analog temperature monitor common ground for signal conditioning block SCB 2 and SBCB 3 (see information for pins "TM2" and "TM3" in the "Analog Front-End (AFE)" section on page 5-14).                                                                                                                                                                   |  |

| GNDTM2      | Ground | Analog temperature monitor common ground for signal conditioning block SCB4                                                                                                                                                                                                                                                                                |  |

| GNDVAREF    | Ground | Analog ground reference used by the ADC. This pad should be connected to a quiet analog ground.                                                                                                                                                                                                                                                            |  |

| VCC         | Supply | Digital supply to the FPGA fabric and MSS, nominally 1.5 V. VCC is also required<br>powering the JTAG state machine, in addition to VJTAG. Even when a SmartFusi<br>cSoC is in bypass mode in a JTAG chain of interconnected devices, both VCC a<br>VJTAG must remain powered to allow JTAG signals to pass through the SmartFusi<br>cSoC.                 |  |

Notes:

1. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. For more details on VCCPLLx capacitor recommendations, refer to the application note AC359, SmartFusion cSoC Board Design Guidelines, the "PLL Power Supply Decoupling Scheme" section.

Pin Descriptions

| Name        | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC15A      | Supply | Clean analog 1.5 V supply to the analog circuitry. Always power this pin.                                                                                                                                                                                                                                                                                                           |

| VCC15ADC0   | Supply | Analog 1.5 V supply to the first ADC. Always power this pin.                                                                                                                                                                                                                                                                                                                        |

| VCC15ADC1   | Supply | Analog 1.5 V supply to the second ADC. Always power this pin.                                                                                                                                                                                                                                                                                                                       |

| VCC15ADC2   | Supply | Analog 1.5 V supply to the third ADC. Always power this pin.                                                                                                                                                                                                                                                                                                                        |

| VCC33A      | Supply | Clean 3.3 V analog supply to the analog circuitry. VCC33A is also used to feed the 1.5 V voltage regulator for designs that do not provide an external supply to VCC. Refer to the Voltage Regulator (VR), Power Supply Monitor (PSM), and Power Modes section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> for more information.                               |

| VCC33ADC0   | Supply | Analog 3.3 V supply to the first ADC. If unused, Microsemi recommends connecting this pin to a 3.3 V supply. $^{\rm 1}$                                                                                                                                                                                                                                                             |

| VCC33ADC1   | Supply | Analog 3.3 V supply to the second ADC. If unused, Microsemi recommends connecting this pin to a 3.3 V supply. $^{\rm 1}$                                                                                                                                                                                                                                                            |

| VCC33ADC2   | Supply | Analog 3.3 V supply to the third ADC. If unused, Microsemi recommends connecting this pin to a 3.3 V supply. <sup>1</sup>                                                                                                                                                                                                                                                           |

| VCC33AP     | Supply | Analog clean 3.3 V supply to the charge pump. To avoid high current draw, VCC33AP should be powered up simultaneously with or after VCC33A. Can be pulled down if unused. <sup>1</sup>                                                                                                                                                                                              |

| VCC33N      | Supply | $-3.3$ V output from the voltage converter. A 2.2 $\mu$ F capacitor must be connected from this pin to GND. Analog charge pump capacitors are not needed if none of the analog SCB features are used and none of the SDDs are used. In that case it should be left unconnected.                                                                                                     |

| VCC33SDD0   | Supply | Analog 3.3 V supply to the first sigma-delta DAC                                                                                                                                                                                                                                                                                                                                    |

| VCC33SDD1   | Supply | Common analog 3.3 V supply to the second and third sigma-delta DACs                                                                                                                                                                                                                                                                                                                 |

| VCCENVM     | Supply | Digital 1.5 V power supply to the embedded nonvolatile memory blocks. To avoid high current draw, VCC should be powered up before or simultaneously with VCCENVM.                                                                                                                                                                                                                   |

| VCCESRAM    | Supply | Digital 1.5 V power supply to the embedded SRAM blocks. Available only on the 208PQFP package. It should be connected to VCC (in other packages, it is internally connected to VCC).                                                                                                                                                                                                |

| VCCFPGAIOB0 | Supply | Digital supply to the FPGA fabric I/O bank 0 (north FPGA I/O bank) for the output buffers and I/O logic.                                                                                                                                                                                                                                                                            |

|             |        | Each bank can have a separate VCCFPGAIO connection. All I/Os in a bank will run off the same VCCFPGAIO supply. VCCFPGAIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCFPGAIO pins tied to GND.                                                                                                                        |

| VCCFPGAIOB1 | Supply | Digital supply to the FPGA fabric I/O bank 1 (east FPGA I/O bank) for the output buffers<br>and I/O logic.<br>Each bank can have a separate VCCFPGAIO connection. All I/Os in a bank will run off<br>the same VCCFPGAIO supply. VCCFPGAIO can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V,<br>nominal voltage. Unused I/O banks should have their corresponding VCCFPGAIO pins<br>tied to GND. |

Notes:

1. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. For more details on VCCPLLx capacitor recommendations, refer to the application note AC359, SmartFusion cSoC Board Design Guidelines, the "PLL Power Supply Decoupling Scheme" section.

**CS288** Pin A2F060 Function A2F200 Function A2F500 Function No. VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 A1 A2 GNDQ GNDQ GNDQ A3 EMC CLK/IO00NDB0V0 EMC CLK/GAA0/IO00NDB0V0 EMC CLK/GAA0/IO02NDB0V0 EMC RW N/IO00PDB0V0 EMC RW N/GAA1/IO00PDB0V0 EMC RW N/GAA1/IO02PDB0V0 A4 A5 GND GND GND EMC CS1 N/GAB1/IO01PDB0V0 EMC CS1 N/GAB1/IO05PDB0V0 A6 EMC CS1 N/IO01PDB0V0 A7 EMC CS0 N/IO01NDB0V0 EMC CS0 N/GAB0/IO01NDB0V0 EMC CS0 N/GAB0/IO05NDB0V0 A8 EMC AB[0]/IO04NPB0V0 EMC AB[0]/IO04NPB0V0 EMC AB[0]/IO06NPB0V0 A9 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 EMC AB[4]/IO06NDB0V0 EMC AB[4]/IO06NDB0V0 EMC AB[4]/IO10NDB0V0 A10 A11 EMC AB[8]/IO08NPB0V0 EMC AB[8]/IO08NPB0V0 EMC AB[8]/IO13NPB0V0 A12 EMC AB[14]/IO11NPB0V0 EMC AB[14]/IO11NPB0V0 EMC AB[14]/IO15NPB0V0 A13 GND GND GND EMC AB[18]/IO13NDB0V0 EMC AB[18]/IO13NDB0V0 EMC AB[18]/IO18NDB0V0 A14 EMC AB[24]/IO16NDB0V0 A15 EMC AB[24]/IO16NDB0V0 EMC AB[24]/IO20NDB0V0 A16 EMC AB[25]/IO16PDB0V0 EMC AB[25]/IO16PDB0V0 EMC AB[25]/IO20PDB0V0 A17 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 A18 EMC AB[20]/IO14NDB0V0 EMC AB[20]/IO14NDB0V0 EMC AB[20]/IO21NDB0V0 A19 EMC AB[21]/IO14PDB0V0 EMC AB[21]/IO14PDB0V0 EMC AB[21]/IO21PDB0V0 A20 GNDQ GNDQ GNDQ GND GND GND A21 AA1 ADC1 ABPS1 ABPS1 AA2 **GNDAQ** GNDAQ GNDAQ AA3 GNDA GNDA GNDA AA4 VCC33N VCC33N VCC33N AA5 SDD0 SDD0 SDD0 AA6 ADC0 ABPS0 ABPS0 AA7 **GNDTM0** NC **GNDTM0** AA8 NC ABPS2 ABPS2 AA9 VAREF0 VAREF0 NC AA10 NC GND15ADC0 GND15ADC0

Notes:

🔨 🗇 Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin | CS288              |                       |                       |  |  |  |

|-----|--------------------|-----------------------|-----------------------|--|--|--|

| No. | A2F060 Function    | A2F200 Function       | A2F500 Function       |  |  |  |

| P19 | VCCMSSIOB2         | VCCMSSIOB2            | VCCMSSIOB2            |  |  |  |

| P21 | GND                | GND                   | GND                   |  |  |  |

| R1  | GPIO_2/IO31RSB4V0  | MAC_MDIO/IO49RSB4V0   | MAC_MDIO/IO58RSB4V0   |  |  |  |

| R3  | GPIO_1/IO32RSB4V0  | MAC_TXEN/IO52RSB4V0   | MAC_TXEN/IO61RSB4V0   |  |  |  |

| R5  | GPIO_3/IO30RSB4V0  | MAC_TXD[0]/IO56RSB4V0 | MAC_TXD[0]/IO65RSB4V0 |  |  |  |

| R6  | GPIO_10/IO35RSB4V0 | MAC_CRSDV/IO51RSB4V0  | MAC_CRSDV/IO60RSB4V0  |  |  |  |

| R9  | GNDA               | GNDA                  | GNDA                  |  |  |  |

| R13 | GNDA               | GNDA                  | GNDA                  |  |  |  |

| R16 | UART_1_RXD/GPIO_29 | UART_1_RXD/GPIO_29    | UART_1_RXD/GPIO_29    |  |  |  |

| R17 | UART_1_TXD/GPIO_28 | UART_1_TXD/GPIO_28    | UART_1_TXD/GPIO_28    |  |  |  |

| R19 | I2C_0_SDA/GPIO_22  | I2C_0_SDA/GPIO_22     | I2C_0_SDA/GPIO_22     |  |  |  |

| R21 | I2C_1_SDA/GPIO_30  | I2C_1_SDA/GPIO_30     | I2C_1_SDA/GPIO_30     |  |  |  |

| T1  | GND                | GND                   | GND                   |  |  |  |

| Т3  | NC                 | MAC_TXD[1]/IO55RSB4V0 | MAC_TXD[1]/IO64RSB4V0 |  |  |  |

| T5  | NC                 | MAC_RXD[1]/IO53RSB4V0 | MAC_RXD[1]/IO62RSB4V0 |  |  |  |

| Т6  | GPIO_11/IO34RSB4V0 | MAC_RXER/IO50RSB4V0   | MAC_RXER/IO59RSB4V0   |  |  |  |

| T7  | NC                 | CM1                   | CM1                   |  |  |  |

| Т8  | NC                 | ADC1                  | ADC1                  |  |  |  |

| Т9  | NC                 | GND33ADC0             | GND33ADC0             |  |  |  |

| T10 | NC                 | VCC15ADC0             | VCC15ADC0             |  |  |  |

| T11 | GND33ADC0          | GND33ADC1             | GND33ADC1             |  |  |  |

| T12 | VAREF0             | VAREF1                | VAREF1                |  |  |  |

| T13 | ADC7               | ADC4                  | ADC4                  |  |  |  |

| T14 | TM0                | TM3                   | TM3                   |  |  |  |

| T15 | SPI_1_SS/GPIO_27   | SPI_1_SS/GPIO_27      | SPI_1_SS/GPIO_27      |  |  |  |

| T16 | VCCMSSIOB2         | VCCMSSIOB2            | VCCMSSIOB2            |  |  |  |

| T17 | UART_0_RXD/GPIO_21 | UART_0_RXD/GPIO_21    | UART_0_RXD/GPIO_21    |  |  |  |

| T19 | UART_0_TXD/GPIO_20 | UART_0_TXD/GPIO_20    | UART_0_TXD/GPIO_20    |  |  |  |

| T21 | I2C_1_SCL/GPIO_31  | I2C_1_SCL/GPIO_31     | I2C_1_SCL/GPIO_31     |  |  |  |

| U1  | NC                 | MAC_RXD[0]/IO54RSB4V0 | MAC_RXD[0]/IO63RSB4V0 |  |  |  |

| U3  | VCCMSSIOB4         | VCCMSSIOB4            | VCCMSSIOB4            |  |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

**CS288** Pin A2F060 Function A2F200 Function A2F500 Function No. U5 VCC33SDD0 VCC33SDD0 VCC33SDD0 U6 VCC15A VCC15A VCC15A U7 NC ABPS3 ABPS3 U8 NC ADC2 ADC2 U9 NC VCC33ADC0 VCC33ADC0 U10 GND15ADC0 GND15ADC1 GND15ADC1 U11 VCC33ADC0 VCC33ADC1 VCC33ADC1 U12 ADC10 ADC7 ADC7 U13 ABPS0 ABPS6 ABPS6 U14 **GNDTM0** GNDTM1 GNDTM1 SPI\_1\_CLK/GPIO\_26 U15 SPI\_1\_CLK/GPIO\_26 SPI\_1\_CLK/GPIO\_26 U16 SPI 0 CLK/GPIO 18 SPI 0 CLK/GPIO 18 SPI 0 CLK/GPIO 18 U17 SPI 0 SS/GPIO 19 SPI 0 SS/GPIO 19 SPI 0 SS/GPIO 19 U19 GND GND GND SPI 1 DO/GPIO 24 U21 SPI 1 DO/GPIO 24 SPI 1 DO/GPIO 24 V1 NC MAC CLK MAC CLK V3 GNDSDD0 GNDSDD0 GNDSDD0 V19 SPI 1 DI/GPIO 25 SPI 1 DI/GPIO 25 SPI 1 DI/GPIO 25 VCCMSSIOB2 V21 VCCMSSIOB2 VCCMSSIOB2 W1 PCAP PCAP PCAP W3 NCAP NCAP NCAP W4 ADC2 CM0 CM0 W5 ADC3 TM0 TM0 W6 ADC4 TM1 TM1 W7 NC ADC0 ADC0 W8 NC ADC3 ADC3 W9 NC GND33ADC0 GND33ADC0 W10 VCC15ADC0 VCC15ADC1 VCC15ADC1 W11 GND33ADC0 GND33ADC1 GND33ADC1 W12 ADC5 ADC8 ADC5 W13 CM0 CM3 CM3

Notes:

🔨 🤇 Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

FG256 Pin A2F060 Function A2F200 Function A2F500 Function No. GNDQ GNDQ GNDQ B16 C1 EMC DB[14]/IO45NDB5V0 EMC DB[14]/GAB2/IO71NDB5V0 EMC DB[14]/GAB2/IO88NDB5V0 **VCCPLL0** VCCPLL VCCPLL0 C2 EMC BYTEN[0]/GAC0/IO02NDB0V0 EMC BYTEN[0]/GAC0/IO07NDB0V0 C3 EMC BYTEN[0]/IO02NDB0V0 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 C4 EMC CS0 N/GAB0/IO05NDB0V0 C5 EMC CS0 N/IO01NDB0V0 EMC CS0 N/GAB0/IO01NDB0V0 EMC CS1 N/IO01PDB0V0 EMC CS1 N/GAB1/IO01PDB0V0 EMC CS1 N/GAB1/IO05PDB0V0 C6 C7 GND GND GND EMC AB[8]/IO08NDB0V0 EMC AB[8]/IO08NDB0V0 EMC AB[8]/IO13NDB0V0 C8 EMC AB[11]/IO09PDB0V0 EMC AB[11]/IO09PDB0V0 EMC AB[11]/IO11PDB0V0 C9 VCCFPGAIOB0 VCCFPGAIOB0 VCCFPGAIOB0 C10 C11 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO12PDB0V0 EMC AB[17]/IO17PDB0V0 EMC AB[19]/IO13PDB0V0 C12 EMC AB[19]/IO13PDB0V0 EMC AB[19]/IO18PDB0V0 C13 GND GND GND C14 GCC0/IO18NPB0V0 GBA2/IO20PPB1V0 GBA2/IO27PPB1V0 C15 GCB0/IO19NDB0V0 GCA2/IO23PDB1V0 GCA2/IO28PDB1V0 \* C16 GCB1/IO19PDB0V0 IO23NDB1V0 IO28NDB1V0 D1 VCCFPGAIOB5 VCCFPGAIOB5 VCCFPGAIOB5 D2 VCOMPLA0 **VCOMPLA** VCOMPLA0 GND GND D3 GND D4 GNDQ GNDQ GNDQ D5 EMC CLK/IO00NDB0V0 EMC CLK/GAA0/IO00NDB0V0 EMC CLK/GAA0/IO02NDB0V0 D6 EMC RW N/IO00PDB0V0 EMC RW N/GAA1/IO00PDB0V0 EMC RW N/GAA1/IO02PDB0V0 EMC\_AB[6]/IO07NDB0V0 EMC AB[6]/IO07NDB0V0 EMC AB[6]/IO12NDB0V0 D7 D8 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO07PDB0V0 EMC AB[7]/IO12PDB0V0 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO09NDB0V0 EMC AB[10]/IO11NDB0V0 D9 D10 EMC AB[22]/IO15NDB0V0 EMC AB[22]/IO15NDB0V0 EMC AB[22]/IO19NDB0V0 EMC AB[23]/IO15PDB0V0 EMC AB[23]/IO15PDB0V0 EMC AB[23]/IO19PDB0V0 D11 D12 GNDQ GNDQ GNDQ GCC1/IO18PPB0V0 GBB2/IO20NPB1V0 GBB2/IO27NPB1V0 D13 D14 GCA0/IO20NDB0V0 GCB2/IO24PDB1V0 GCB2/IO33PDB1V0

Notes:

Microsemi

Pin Descriptions

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin    |                      | FG256                     |                           |

|--------|----------------------|---------------------------|---------------------------|

| No.    | A2F060 Function      | A2F200 Function           | A2F500 Function           |

| H13    | TDO                  | TDO                       | TDO                       |

| H14    | TDI                  | TDI                       | TDI                       |

| H15    | JTAGSEL              | JTAGSEL                   | JTAGSEL                   |

| H16    | GND                  | GND                       | GND                       |

| J1     | EMC_DB[4]/IO38NPB5V0 | EMC_DB[4]/GEA0/IO61NPB5V0 | EMC_DB[4]/GEA0/IO78NPB5V0 |

| J2     | EMC_DB[3]/IO37PDB5V0 | EMC_DB[3]/GEC2/IO60PDB5V0 | EMC_DB[3]/GEC2/IO77PDB5V0 |

| J3     | EMC_DB[2]/IO37NDB5V0 | EMC_DB[2]/IO60NDB5V0      | EMC_DB[2]/IO77NDB5V0      |

| J4     | GNDRCOSC             | GNDRCOSC                  | GNDRCOSC                  |

| J5     | NC                   | GNDQ                      | GNDQ                      |

| J6     | GND                  | GND                       | GND                       |

| J7     | VCC                  | VCC                       | VCC                       |

| J8     | GND                  | GND                       | GND                       |

| J9     | VCC                  | VCC                       | VCC                       |

| J10    | GND                  | GND                       | GND                       |

| J11    | VCCMSSIOB2           | VCCMSSIOB2                | VCCMSSIOB2                |

| J12    | I2C_0_SCL/GPIO_23    | I2C_0_SCL/GPIO_23         | I2C_0_SCL/GPIO_23         |

| J13    | I2C_0_SDA/GPIO_22    | I2C_0_SDA/GPIO_22         | I2C_0_SDA/GPIO_22         |

| J14    | I2C_1_SCL/GPIO_31    | I2C_1_SCL/GPIO_31         | I2C_1_SCL/GPIO_31         |

| J15    | VCCMSSIOB2           | VCCMSSIOB2                | VCCMSSIOB2                |

| J16    | I2C_1_SDA/GPIO_30    | I2C_1_SDA/GPIO_30         | I2C_1_SDA/GPIO_30         |

| K1     | GPIO_1/IO32RSB4V0    | MAC_MDIO/IO49RSB4V0       | MAC_MDIO/IO58RSB4V0       |

| K2     | GPIO_0/IO33RSB4V0    | MAC_MDC/IO48RSB4V0        | MAC_MDC/IO57RSB4V0        |

| K3     | VCCMSSIOB4           | VCCMSSIOB4                | VCCMSSIOB4                |

| K4     | MSS_RESET_N          | MSS_RESET_N               | MSS_RESET_N               |

| K5     | VCCRCOSC             | VCCRCOSC                  | VCCRCOSC                  |

| K6     | VCCMSSIOB4           | VCCMSSIOB4                | VCCMSSIOB4                |

| K7     | GND                  | GND                       | GND                       |

| K8     | VCC                  | VCC                       | VCC                       |

| K9     | GND                  | GND                       | GND                       |

| K10    | VCC                  | VCC                       | VCC                       |

| K11    | GND                  | GND                       | GND                       |

| Notes: |                      | •                         | •                         |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

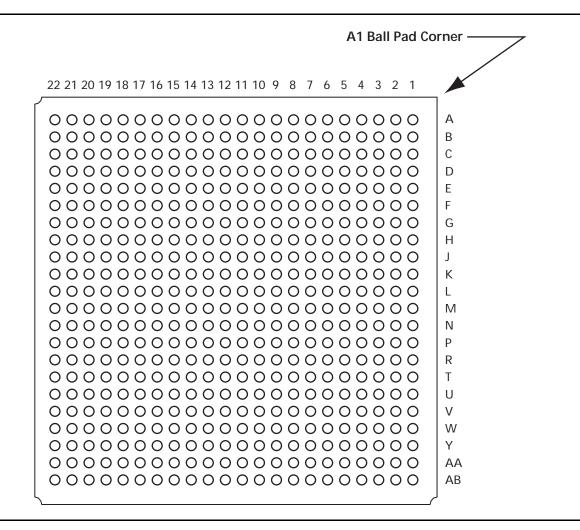

## FG484

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

|            | FG484                      |                            |  |

|------------|----------------------------|----------------------------|--|

| Pin Number | A2F200 Function            | A2F500 Function            |  |

| AA13       | NC                         | ADC10                      |  |

| AA14       | NC                         | ADC9                       |  |

| AA15       | NC                         | GND15ADC2                  |  |

| AA16       | MAINXIN                    | MAINXIN                    |  |

| AA17       | MAINXOUT                   | MAINXOUT                   |  |

| AA18       | LPXIN                      | LPXIN                      |  |

| AA19       | LPXOUT                     | LPXOUT                     |  |

| AA20       | NC                         | NC                         |  |

| AA21       | NC                         | NC                         |  |

| AA22       | SPI_1_CLK/GPIO_26          | SPI_1_CLK/GPIO_26          |  |

| AB1        | GND                        | GND                        |  |

| AB2        | GPIO_13/IO36RSB4V0         | GPIO_13/IO45RSB4V0         |  |

| AB3        | GPIO_14/IO35RSB4V0         | GPIO_14/IO44RSB4V0         |  |

| AB4        | GND                        | GND                        |  |

| AB5        | PCAP                       | PCAP                       |  |

| AB6        | NCAP                       | NCAP                       |  |

| AB7        | ABPS3                      | ABPS3                      |  |

| AB8        | ADC3                       | ADC3                       |  |

| AB9        | GND15ADC0                  | GND15ADC0                  |  |

| AB10       | VCC33ADC1                  | VCC33ADC1                  |  |

| AB11       | VAREF1                     | VAREF1                     |  |

| AB12       | TM2                        | TM2                        |  |

| AB13       | CM2                        | CM2                        |  |

| AB14       | ABPS4                      | ABPS4                      |  |

| AB15       | GNDAQ                      | GNDAQ                      |  |

| AB16       | GNDMAINXTAL                | GNDMAINXTAL                |  |

| AB17       | GNDLPXTAL                  | GNDLPXTAL                  |  |

| AB18       | VCCLPXTAL                  | VCCLPXTAL                  |  |

| AB19       | VDDBAT                     | VDDBAT                     |  |

| AB20       | PTBASE                     | PTBASE                     |  |

| AB21       | NC                         | NC                         |  |

| AB22       | GND                        | GND                        |  |

| B1         | EMC_DB[15]/GAA2/IO71PDB5V0 | EMC_DB[15]/GAA2/IO88PDB5V0 |  |

| B2         | GND                        | GND                        |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

## **Datasheet Categories**

### Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "SmartFusion cSoC Device Status" table on page III, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

### Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

### Production

This version contains information that is considered to be final.

### **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

## Microsemi SoC Products Group Safety Critical, Life Support, and High-Reliability Applications Policy

The SoC Products Group products described in this advance status document may not have completed the SoC Products Group's qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the SoC Products Group's Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available on the SoC Products Group website at:

http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=131372. Microsemi SoC Products Group also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local SoC Products Group sales office for additional reliability information.