Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Active                                                                     |

|-------------------------|----------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                  |

| Core Processor          | ARM® Cortex®-M3                                                            |

| Flash Size              | 512KB                                                                      |

| RAM Size                | 64KB                                                                       |

| Peripherals             | DMA, POR, WDT                                                              |

| Connectivity            | EBI/EMI, Ethernet, I²C, SPI, UART/USART                                    |

| Speed                   | 80MHz                                                                      |

| Primary Attributes      | ProASIC®3 FPGA, 500K Gates, 11520 D-Flip-Flops                             |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                            |

| Package / Case          | 484-BGA                                                                    |

| Supplier Device Package | 484-FPBGA (23x23)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/a2f500m3g-fgg484 |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Package I/Os: MSS + FPGA I/Os

| Device                  |                 | A2F060 <sup>1</sup> |                 |       | A2F   | <b>200</b> <sup>2</sup> |       | A2F500 <sup>2</sup> |       |       |       |  | A2F500 <sup>2</sup> |  |  |  |

|-------------------------|-----------------|---------------------|-----------------|-------|-------|-------------------------|-------|---------------------|-------|-------|-------|--|---------------------|--|--|--|

| Package                 | TQ144           | CS288               | FG256           | PQ208 | CS288 | FG256                   | FG484 | PQ208               | CS288 | FG256 | FG484 |  |                     |  |  |  |

| Direct Analog Inputs    | 11              | 11                  | 11              | 8     | 8     | 8                       | 8     | 8                   | 8     | 8     | 12    |  |                     |  |  |  |

| Shared Analog Inputs    | 4               | 4                   | 4               | 16    | 16    | 16                      | 16    | 16                  | 16    | 16    | 20    |  |                     |  |  |  |

| Total Analog Inputs     | 15              | 15                  | 15              | 24    | 24    | 24                      | 24    | 24                  | 24    | 24    | 32    |  |                     |  |  |  |

| Analog Outputs          | 1               | 1                   | 1               | 1     | 2     | 2                       | 2     | 1                   | 2     | 2     | 3     |  |                     |  |  |  |

| MSS I/Os <sup>3,4</sup> | 21 <sup>5</sup> | 28 <sup>5</sup>     | 26 <sup>5</sup> | 22    | 31    | 25                      | 41    | 22                  | 31    | 25    | 41    |  |                     |  |  |  |

| FPGA I/Os               | 33 <sup>6</sup> | 68                  | 66              | 66    | 78    | 66                      | 94    | 66 <sup>6</sup>     | 78    | 66    | 128   |  |                     |  |  |  |

| Total I/Os              | 70              | 112                 | 108             | 113   | 135   | 117                     | 161   | 113                 | 135   | 117   | 204   |  |                     |  |  |  |

#### Notes:

1. There are no LVTTL capable direct inputs available on A2F060 devices.

2. These pins are shared between direct analog inputs to the ADCs and voltage/current/temperature monitors.

3. 16 MSS I/Os are multiplexed and can be used as FPGA I/Os, if not needed for MSS. These I/Os support Schmitt triggers and support only LVTTL and LVCMOS (1.5 / 1.8 / 2.5, 3.3 V) standards.

4. 9 MSS I/Os are primarily for 10/100 Ethernet MAC and are also multiplexed and can be used as FPGA I/Os if Ethernet MAC is not used in a design. These I/Os support Schmitt triggers and support only LVTTL and LVCMOS (1.5 / 1.8 / 2.5, 3.3 V standards.

5. 10/100 Ethernet MAC is not available on A2F060.

6. EMC is not available on the A2F500 PQ208 and A2F060 TQ144 package.

#### Table 1 • SmartFusion cSoC Package Sizes Dimensions

| Package                         | TQ144   | PQ208   | CS288   | FG256   | FG484   |

|---------------------------------|---------|---------|---------|---------|---------|

| Length × Width (mm\mm)          | 20 × 20 | 28 × 28 | 11 × 11 | 17 × 17 | 23 × 23 |

| Nominal Area (mm <sup>2</sup> ) | 400     | 784     | 121     | 289     | 529     |

| Pitch (mm)                      | 0.5     | 0.5     | 0.5     | 1.0     | 1.0     |

| Height (mm)                     | 1.40    | 3.40    | 1.05    | 1.60    | 2.23    |

## SmartFusion cSoC Device Status

| Device | Status                                 |

|--------|----------------------------------------|

| A2F060 | Preliminary: CS288, FG256, TQ144       |

| A2F200 | Production: CS288, FG256, FG484, PQ208 |

| A2F500 | Production: CS288, FG256, FG484, PQ208 |

SmartFusion Family Overview

## ProASIC3 FPGA Fabric

The SmartFusion cSoC family, based on the proven, low power, firm-error immune ProASIC<sup>®</sup>3 flash FPGA architecture, benefits from the advantages only flash-based devices offer:

#### Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, high performance, and ease of use. Flashbased SmartFusion cSoCs are Instant On and do not need to be loaded from an external boot PROM at each power-up. On-board security mechanisms prevent access to the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system programming (ISP) to support future design iterations and critical field upgrades, with confidence that valuable IP cannot be compromised or copied. Secure ISP can be performed using the industry standard AES algorithm with MAC data authentication on the device.

#### Low Power

Flash-based SmartFusion cSoCs exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. With SmartFusion cSoCs, there is no power-on current and no high current transition, both of which are common with SRAM-based FPGAs.

SmartFusion cSoCs also have low dynamic power consumption and support very low power timekeeping mode, offering further power savings.

#### Security

As the nonvolatile, flash-based SmartFusion cSoC family requires no boot PROM, there is no vulnerable external bitstream. SmartFusion cSoCs incorporate FlashLock<sup>®</sup>, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only a device with nonvolatile flash programming can offer.

SmartFusion cSoCs utilize a 128-bit flash-based key lock and a separate AES key to provide security for programmed IP and configuration data. The FlashROM data in Fusion devices can also be encrypted prior to loading. Additionally, the flash memory blocks can be programmed during runtime using the AES-128 block cipher encryption standard (FIPS Publication 192).

SmartFusion cSoCs with AES-based security are designed to provide protection for remote field updates over public networks, such as the Internet, and help to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves. As an additional security measure, the FPGA configuration data of a programmed Fusion device cannot be read back, although secure design verification is possible. During design, the user controls and defines both internal and external access to the flash memory blocks.

Security, built into the FPGA fabric, is an inherent component of the SmartFusion cSoC family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. SmartFusion cSoCs, with FlashLock and AES security, are unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry standard security measures, making remote ISP feasible. A SmartFusion cSoC provides the highest security available for programmable logic designs.

#### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based SmartFusion cSoCs do not require system configuration components such as electrically erasable programmable read-only memories (EEPROMs) or microcontrollers to load device configuration data during power-up. This reduces bill-of-materials costs and PCB area, and increases system security and reliability.

#### Instant On

Flash-based SmartFusion cSoCs are Instant On. Instant On SmartFusion cSoCs greatly simplify total system design and reduce total system cost by eliminating the need for complex programmable logic devices (CPLDs). SmartFusion Instant On clocking (PLLs) replace off-chip clocking resources. In addition, glitches and brownouts in system power will not corrupt the SmartFusion flash configuration. Unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored.

SmartFusion Customizable System-on-Chip (cSoC)

$$P = \frac{T_J - T_A}{\theta_{JA}} = \frac{100^{\circ}C - 70^{\circ}C}{17.00 \text{ W}} = 1.76 \text{ W}$$

EQ 6

The 1.76 W power is less than the required 3.00 W. The design therefore requires a heat sink, or the airflow where the device is mounted should be increased. The design's total junction-to-air thermal resistance requirement can be estimated by EQ 7:

$$\theta_{JA(total)} = \frac{T_J - T_A}{P} = \frac{100^{\circ}C - 70^{\circ}C}{3.00 \text{ W}} = 10.00^{\circ}\text{C/W}$$

EQ 7

Determining the heat sink's thermal performance proceeds as follows:

$$\theta_{JA(TOTAL)} = \theta_{JC} + \theta_{CS} + \theta_{SA}$$

EQ 8

where

$$\theta_{JA} = 0.37^{\circ}C/W$$

Thermal resistance of the interface material between the case and the heat sink, usually provided by the thermal interface manufacturer

$\theta_{SA}$  = Thermal resistance of the heat sink in °C/W

$\theta_{\text{SA}}$

$$\theta_{SA} = \theta_{JA(TOTAL)} - \theta_{JC} - \theta_{CS}$$

$$EQ 9$$

$$= 13.33^{\circ}C/W - 8.28^{\circ}C/W - 0.37^{\circ}C/W = 5.01^{\circ}C/W$$

A heat sink with a thermal resistance of 5.01°C/W or better should be used. Thermal resistance of heat sinks is a function of airflow. The heat sink performance can be significantly improved with increased airflow.

Carefully estimating thermal resistance is important in the long-term reliability of an FPGA. Design engineers should always correlate the power consumption of the device with the maximum allowable power dissipation of the package selected for that device.

Note: The junction-to-air and junction-to-board thermal resistances are based on JEDEC standard (JESD-51) and assumptions made in building the model. It may not be realized in actual application and therefore should be used with a degree of caution. Junction-to-case thermal resistance assumes that all power is dissipated through the case.

#### **Temperature and Voltage Derating Factors**

Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays<br/>(normalized to T<sub>J</sub> = 85°C, worst-case VCC = 1.425 V)

| Array              | Junction Temperature (°C) |      |      |      |      |       |  |  |  |  |  |

|--------------------|---------------------------|------|------|------|------|-------|--|--|--|--|--|

| Voltage VCC<br>(V) | –40°C                     | 0°C  | 25°C | 70°C | 85°C | 100°C |  |  |  |  |  |

| 1.425              | 0.86                      | 0.91 | 0.93 | 0.98 | 1.00 | 1.02  |  |  |  |  |  |

| 1.500              | 0.81                      | 0.86 | 0.88 | 0.93 | 0.95 | 0.96  |  |  |  |  |  |

| 1.575              | 0.78                      | 0.83 | 0.85 | 0.90 | 0.91 | 0.93  |  |  |  |  |  |

## **Overview of I/O Performance**

## Summary of I/O DC Input and Output Levels – Default I/O Software Settings

#### Table 2-19 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial Conditions—Software Default Settings Applicable to FPGA I/O Banks

|                               |                  |                          | VIL  |                       | VIH                  |           | VOL                   | VOH                   | I <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> 1 |  |

|-------------------------------|------------------|--------------------------|------|-----------------------|----------------------|-----------|-----------------------|-----------------------|------------------------------|-------------------|--|

| I/O Standard                  | Drive<br>Strgth. |                          |      | Max.<br>V             | Min.<br>V            | Max.<br>V | Max.<br>V             | Min.<br>V             | mA                           | mA                |  |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA            | High                     | -0.3 | 0.8                   | 2                    | 3.6       | 0.4                   | 2.4                   | 12                           | 12                |  |

| 2.5 V LVCMOS                  | 12 mA            | High                     | -0.3 | 0.7                   | 1.7                  | 3.6       | 0.7                   | 1.7                   | 12                           | 12                |  |

| 1.8 V LVCMOS                  | 12 mA            | High                     | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                  | VCCxxxxIOBx<br>- 0.45 | 12                           | 12                |  |

| 1.5 V LVCMOS                  | 12 mA            | High                     | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25 *<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 12                           | 12                |  |

| 3.3 V PCI                     |                  | -                        |      |                       | Per PCI spec         | cificatio | ons                   | -                     | -                            | -                 |  |

| 3.3 V PCI-X                   |                  | Per PCI-X specifications |      |                       |                      |           |                       |                       |                              |                   |  |

Notes:

1. Currents are measured at 85°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

# Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial Conditions—Software Default Settings Applicable to MSS I/O Banks

|                               |                  |              | VIL  |                      | VIH                  |           | VOL                  | VOH                   | I <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> 1 |

|-------------------------------|------------------|--------------|------|----------------------|----------------------|-----------|----------------------|-----------------------|------------------------------|-------------------|

| I/O Standard                  | Drive<br>Strgth. | Slew<br>Rate |      | Max.<br>V            | Min.<br>V            | Max.<br>V | Max.<br>V            | Min.<br>V             | mA                           | mA                |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA             | High         | -0.3 | 0.8                  | 2                    | 3.6       | 0.4                  | 2.4                   | 8                            | 8                 |

| 2.5 V LVCMOS                  | 8 mA             | High         | -0.3 | 0.7                  | 1.7                  | 3.6       | 0.7                  | 1.7                   | 8                            | 8                 |

| 1.8 V LVCMOS                  | 4 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                 | VCCxxxxIOBx<br>- 0.45 | 4                            | 4                 |

| 1.5 V LVCMOS                  | 2 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25*<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 2                            | 2                 |

Notes:

1. Currents are measured at 85°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

SmartFusion DC and Switching Characteristics

## Single-Ended I/O Characteristics

#### 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer.

#### Table 2-35 • Minimum and Maximum DC Input and Output Levels Applicable to FPGA I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | VIL       |           | VIH       |           | VOL       | VOH       | I <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub>        | I <sub>OSH</sub>        | I <sub>IL</sub> | IIH |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------------|-----------------|-------------------------|-------------------------|-----------------|-----|

| Drive Strength                | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA              | mA              | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA²             | μA² |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2               | 2               | 27                      | 25                      | 15              | 15  |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4               | 4               | 27                      | 25                      | 15              | 15  |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6               | 6               | 54                      | 51                      | 15              | 15  |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8               | 8               | 54                      | 51                      | 15              | 15  |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12              | 12              | 109                     | 103                     | 15              | 15  |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16              | 16              | 127                     | 132                     | 15              | 15  |

| 24 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 24              | 24              | 181                     | 268                     | 10              | 10  |

Notes:

1. Currents are measured at 100°C junction temperature and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Software default selection highlighted in gray.

#### Table 2-36 • Minimum and Maximum DC Input and Output Levels Applicable to MSS I/O Banks

| 3.3 V LVTTL /<br>3.3 V LVCMOS | VIL       |           | VIL VIH VOL |           | VOH       | I <sub>OL</sub> | I <sub>OH</sub> | I <sub>OSL</sub> | I <sub>OSH</sub>        | I <sub>IL</sub>         | I <sub>IH</sub> |     |

|-------------------------------|-----------|-----------|-------------|-----------|-----------|-----------------|-----------------|------------------|-------------------------|-------------------------|-----------------|-----|

| Drive Strength                | Min.<br>V | Max.<br>V | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V       | mA              | mA               | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA²             | μA² |

| 8 mA                          | -0.3      | 0.8       | 2           | 3.6       | 0.4       | 2.4             | 8               | 8                | 54                      | 51                      | 15              | 15  |

Notes:

1. Currents are measured at 100°C junction temperature and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Software default selection highlighted in gray.

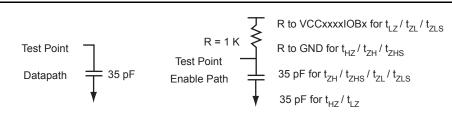

#### Figure 2-6 • AC Loading

#### Table 2-37 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------------------|------------------------|

| 0             | 3.3            | 1.4                  | -                           | 35                     |

Note: \*Measuring point =  $V_{trip}$ . See Table 2-22 on page 2-24 for a complete table of trip points.

## 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

#### **Timing Characteristics**

# Table 2-56 • 1.5 V LVCMOS High Slew Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.425 V Applies bla to EDCA VO Basks VC Applies to EMC VO Bins

Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 m               | Std.           | 0.60              | 7.79            | 0.04             | 1.34            | 0.39              | 6.43            | 7.79            | 3.19            | 2.59            | 8.49             | 9.85             | ns    |

|                   | –1             | 0.50              | 6.49            | 0.03             | 1.12            | 0.32              | 5.36            | 6.49            | 2.66            | 2.16            | 7.08             | 8.21             | ns    |

| 4 mA              | Std.           | 0.60              | 4.95            | 0.04             | 1.34            | 0.39              | 4.61            | 4.96            | 3.53            | 3.19            | 6.67             | 7.02             | ns    |

|                   | –1             | 0.50              | 4.13            | 0.03             | 1.12            | 0.32              | 3.85            | 4.13            | 2.94            | 2.66            | 5.56             | 5.85             | ns    |

| 6 mA              | Std.           | 0.60              | 4.36            | 0.04             | 1.34            | 0.39              | 4.34            | 4.36            | 3.60            | 3.34            | 6.40             | 6.42             | ns    |

|                   | –1             | 0.50              | 3.64            | 0.03             | 1.12            | 0.32              | 3.62            | 3.64            | 3.00            | 2.78            | 5.33             | 5.35             | ns    |

| 8 mA              | Std.           | 0.60              | 3.89            | 0.04             | 1.34            | 0.39              | 3.96            | 3.34            | 3.72            | 3.92            | 6.02             | 5.40             | ns    |

|                   | -1             | 0.50              | 3.24            | 0.03             | 1.12            | 0.32              | 3.30            | 2.79            | 3.10            | 3.27            | 5.02             | 4.50             | ns    |

| 12 mA             | Std.           | 0.60              | 3.89            | 0.04             | 1.34            | 0.39              | 3.96            | 3.34            | 3.72            | 3.92            | 6.02             | 5.40             | ns    |

|                   | -1             | 0.50              | 3.24            | 0.03             | 1.12            | 0.32              | 3.30            | 2.79            | 3.10            | 3.27            | 5.02             | 4.50             | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-57 • 1.5 V LVCMOS Low Slew

Worst Commercial-Case Conditions:  $T_J = 85^{\circ}C$ , Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 1.4 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.60              | 11.96           | 0.04             | 1.34            | 0.39              | 12.18           | 11.70           | 3.20            | 2.47            | 14.24            | 13.76            | ns    |

|                   | -1             | 0.50              | 9.96            | 0.03             | 1.12            | 0.32              | 10.15           | 9.75            | 2.67            | 2.06            | 11.86            | 11.46            | ns    |

| 4 mA              | Std.           | 0.60              | 9.51            | 0.04             | 1.34            | 0.39              | 9.68            | 8.76            | 3.54            | 3.07            | 11.74            | 10.82            | ns    |

|                   | -1             | 0.50              | 7.92            | 0.03             | 1.12            | 0.32              | 8.07            | 7.30            | 2.95            | 2.56            | 9.79             | 9.02             | ns    |

| 6 mA              | Std.           | 0.60              | 8.86            | 0.04             | 1.34            | 0.39              | 9.03            | 8.17            | 3.61            | 3.22            | 11.08            | 10.23            | ns    |

|                   | -1             | 0.50              | 7.39            | 0.03             | 1.12            | 0.32              | 7.52            | 6.81            | 3.01            | 2.68            | 9.24             | 8.52             | ns    |

| 8 mA              | Std.           | 0.60              | 8.44            | 0.04             | 1.34            | 0.39              | 8.60            | 8.18            | 3.73            | 3.78            | 10.66            | 10.24            | ns    |

|                   | -1             | 0.50              | 7.04            | 0.03             | 1.12            | 0.32              | 7.17            | 6.82            | 3.11            | 3.15            | 8.88             | 8.53             | ns    |

| 12 mA             | Std.           | 0.60              | 8.44            | 0.04             | 1.34            | 0.39              | 8.60            | 8.18            | 3.73            | 3.78            | 10.66            | 10.24            | ns    |

|                   | -1             | 0.50              | 7.04            | 0.03             | 1.12            | 0.32              | 7.17            | 6.82            | 3.11            | 3.15            | 8.88             | 8.53             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

#### Table 2-58 • 1.5 V LVCMOS High Slew

Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCxxxxIOBx = 3.0 V Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.22              | 3.24            | 0.09             | 1.28            | 1.86             | 0.22              | 3.30            | 3.20            | 2.24            | 2.21            | ns    |

|                   | -1             | 0.18              | 2.70            | 0.07             | 1.07            | 1.55             | 0.18              | 2.75            | 2.67            | 1.87            | 1.85            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

| DC Parameter                 | Description                 | Min.  | Тур.  | Max.  | Units |

|------------------------------|-----------------------------|-------|-------|-------|-------|

| VCCFPGAIOBx                  | Supply voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                          | Output low voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                          | Output high voltage         | 1.25  | 1.425 | 1.6   | V     |

| I <sub>OL</sub> <sup>1</sup> | Output lower current        | 0.65  | 0.91  | 1.16  | mA    |

| I <sub>OH</sub> <sup>1</sup> | Output high current         | 0.65  | 0.91  | 1.16  | mA    |

| VI                           | Input voltage               | 0     |       | 2.925 | V     |

| I <sub>IH</sub> <sup>2</sup> | Input high leakage current  |       |       | 15    | μΑ    |

| I <sub>IL</sub> <sup>2</sup> | Input low leakage current   |       |       | 15    | μA    |

| V <sub>ODIFF</sub>           | Differential output voltage | 250   | 350   | 450   | mV    |

| V <sub>OCM</sub>             | Output common mode voltage  | 1.125 | 1.25  | 1.375 | V     |

| V <sub>ICM</sub>             | Input common mode voltage   | 0.05  | 1.25  | 2.35  | V     |

| V <sub>IDIFF</sub>           | Input differential voltage  | 100   | 350   |       | mV    |

Notes:

1.  $I_{OL}/I_{OH}$  defined by  $V_{ODIFF}$  (resistor network).

2. Currents are measured at 85°C junction temperature.

#### Table 2-64 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) |

|---------------|----------------|----------------------|-----------------------------|

| 1.075         | 1.325          | Cross point          | -                           |

\* Measuring point =  $V_{trip.}$  See Table 2-22 on page 2-24 for a complete table of trip points.

#### **Timing Characteristics**

#### Table 2-65 • LVDS

#### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V, Worst-Case VCCFPGAIOBx = 2.3 V Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.60              | 1.83            | 0.04             | 1.87            | ns    |

| -1          | 0.50              | 1.53            | 0.03             | 1.55            | ns    |

Notes:

1. For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

2. The above mentioned timing parameters correspond to 24mA drive strength.

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>ОНD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| tosue                 | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| tOESUE                | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

#### Table 2-70 • Parameter Definition and Measuring Nodes

\* See Figure 2-15 on page 2-46 for more information.

#### **Timing Characteristics**

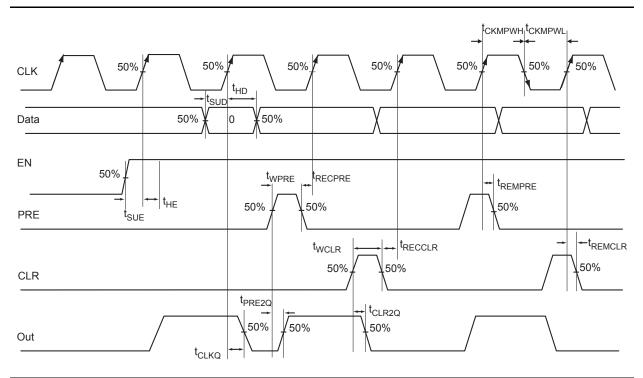

#### Table 2-79 • Register Delays

#### Worst Commercial-Case Conditions: T<sub>J</sub> = 85°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.56 | 0.67 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.44 | 0.52 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.46 | 0.55 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.41 | 0.49 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.41 | 0.49 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.23 | 0.27 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.23 | 0.27 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.22 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.22 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.32 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.36 | ns    |

*Note:* For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

SmartFusion DC and Switching Characteristics

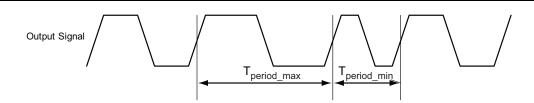

*Note:* Peak-to-peak jitter measurements are defined by  $T_{peak-to-peak} = T_{period_max} - T_{period_min}$ . *Figure 2-28* • Peak-to-Peak Jitter Definition

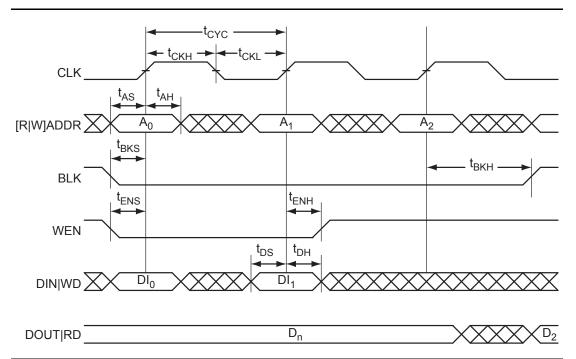

Figure 2-32 • RAM Write, Output Retained. Applicable to both RAM4K9 and RAM512x18.

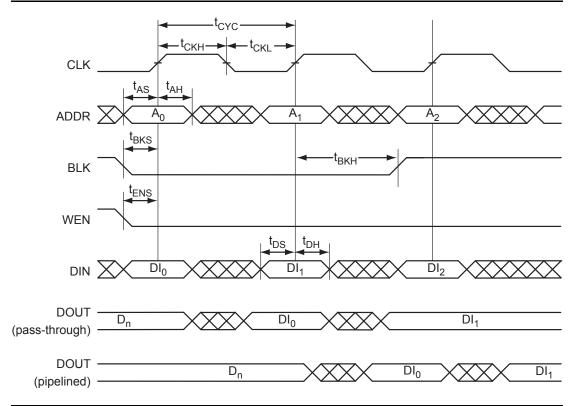

Figure 2-33 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 only.

## static Microsemi.

SmartFusion DC and Switching Characteristics

## Comparator

Unless otherwise specified, performance is specified at 25°C with nominal power supply voltages.

| Specification                                                   | Test Conditions   |                                               | Min. | Тур.  | Max. | Units |

|-----------------------------------------------------------------|-------------------|-----------------------------------------------|------|-------|------|-------|

| Input voltage range                                             | Minimum           |                                               |      | 0     |      | V     |

|                                                                 | Maximum           |                                               |      | 2.56  |      | V     |

| Input offset voltage                                            | HYS[1:0] = 00     |                                               |      | ±1    | ±3   | mV    |

|                                                                 | (no hysteresis)   | no hysteresis)                                |      |       |      |       |

| Input bias current                                              | Comparator 1,     | Comparator 1, 3, 5, 7, 9 (measured at 2.56 V) |      | 40    | 100  | nA    |

|                                                                 | Comparator 0,     | 2, 4, 6, 8 (measured at 2.56 V)               |      | 150   | 300  | nA    |

| Input resistance                                                |                   |                                               | 10   |       |      | MΩ    |

| Power supply rejection ratio                                    | DC (0 – 10 KHz    | <u>z</u> )                                    | 50   | 60    |      | dB    |

| Propagation delay                                               | 100 mV overdri    | ve                                            |      |       |      |       |

|                                                                 | HYS[1:0] = 00     |                                               |      |       |      |       |

|                                                                 | (no hysteresis)   |                                               |      | 15    | 18   | ns    |

|                                                                 | 100 mV overdrive  |                                               |      |       |      |       |

|                                                                 | HYS[1:0] = 10     |                                               |      |       |      |       |

|                                                                 | (with hysteresis) |                                               |      | 25    | 30   | ns    |

| Hysteresis                                                      | HYS[1:0] = 00     | Typical (25°C)                                | 0    | 0     | ±5   | mV    |

| (± refers to rising and falling threshold shifts, respectively) |                   | Across all corners (-40°C to +100°C)          | 0    |       | ±5   | mV    |

| theshold shifts, respectively)                                  | HYS[1:0] = 01     | Typical (25°C)                                | ±3   | ± 16  | ±30  | mV    |

|                                                                 |                   | Across all corners (-40°C to +100°C)          | 0    |       | ±36  | mV    |

|                                                                 | HYS[1:0] = 10     | Typical (25°C)                                | ±19  | ± 31  | ±48  | mV    |

|                                                                 |                   | Across all corners (-40°C to +100°C)          | ±12  |       | ±54  | mV    |

|                                                                 | HYS[1:0] = 11     | Typical (25°C)                                | ±80  | ± 105 | ±190 | mV    |

|                                                                 |                   | Across all corners (-40°C to +100°C)          | ±80  |       | ±194 | mV    |

| Comparator current                                              | VCC33A = 3.3      | V (operational mode); COMP_EN = 1             | 1    | •     |      | L     |

| requirements<br>(per comparator)                                | VCC33A            |                                               |      | 150   | 165  | μA    |

|                                                                 | VCC33AP           |                                               | 1    | 140   | 165  | μA    |

|                                                                 | VCC15A            |                                               |      | 1     | 3    | μA    |

SmartFusion DC and Switching Characteristics

#### Table 2-98 • Analog Sigma-Delta DAC (continued)

| Specification                                                            | Test Conditions                                  | Min. | Тур. | Max. | Units |

|--------------------------------------------------------------------------|--------------------------------------------------|------|------|------|-------|

| Sigma-delta DAC power supply current requirements (not including VAREFx) | Input = 0, EN = 1<br>(operational mode)          |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 30   | 35   | μA    |

|                                                                          | VCC15A                                           |      | 3    | 5    | μA    |

|                                                                          | Input = Half scale, EN = 1<br>(operational mode) |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 160  | 165  | μA    |

|                                                                          | VCC15A                                           |      | 33   | 35   | μA    |

|                                                                          | Input = Full scale, EN = 1<br>(operational mode) |      |      |      |       |

|                                                                          | VCC33SDDx                                        |      | 280  | 285  | μA    |

|                                                                          | VCC15A                                           |      | 70   | 75   | μA    |

Note: \*FS is full-scale error, defined as the difference between the actual value that triggers the transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error. Refer to the Analog-to-Digital Converter chapter of the SmartFusion Programmable Analog User's Guide for more information.

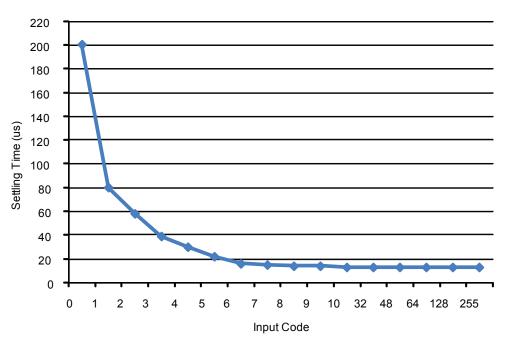

#### Sigma Delta DAC Settling Time

Figure 2-44 • Sigma-Delta DAC Setting Time

## **Serial Peripheral Interface (SPI) Characteristics**

This section describes the DC and switching of the SPI interface. Unless otherwise noted, all output characteristics given for a 35 pF load on the pins and all sequential timing characteristics are related to SPI\_x\_CLK. For timing parameter definitions, refer to Figure 2-47 on page 2-90.

| Symbol | Description and Condition                                      | A2F060 | A2F200 | A2F500 | Unit |

|--------|----------------------------------------------------------------|--------|--------|--------|------|

| sp1    | SPI_x_CLK minimum period                                       |        |        | LU     |      |

|        | SPI_x_CLK = PCLK/2                                             | 20     | NA     | 20     | ns   |

|        | SPI_x_CLK = PCLK/4                                             | 40     | 40     | 40     | ns   |

|        | SPI_x_CLK = PCLK/8                                             | 80     | 80     | 80     | ns   |

|        | SPI_x_CLK = PCLK/16                                            | 0.16   | 0.16   | 0.16   | μs   |

|        | SPI_x_CLK = PCLK/32                                            | 0.32   | 0.32   | 0.32   | μs   |

|        | SPI_x_CLK = PCLK/64                                            | 0.64   | 0.64   | 0.64   | μs   |

|        | SPI_x_CLK = PCLK/128                                           | 1.28   | 1.28   | 1.28   | μs   |

|        | SPI_x_CLK = PCLK/256                                           | 2.56   | 2.56   | 2.56   | μs   |

| sp2    | SPI_x_CLK minimum pulse width high                             |        |        |        |      |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | us   |

| sp3    | SPI_x_CLK minimum pulse width low                              |        |        |        |      |

|        | SPI_x_CLK = PCLK/2                                             | 10     | NA     | 10     | ns   |

|        | SPI_x_CLK = PCLK/4                                             | 20     | 20     | 20     | ns   |

|        | SPI_x_CLK = PCLK/8                                             | 40     | 40     | 40     | ns   |

|        | SPI_x_CLK = PCLK/16                                            | 0.08   | 0.08   | 0.08   | μs   |

|        | SPI_x_CLK = PCLK/32                                            | 0.16   | 0.16   | 0.16   | μs   |

|        | SPI_x_CLK = PCLK/64                                            | 0.32   | 0.32   | 0.32   | μs   |

|        | SPI_x_CLK = PCLK/128                                           | 0.64   | 0.64   | 0.64   | μs   |

|        | SPI_x_CLK = PCLK/256                                           | 1.28   | 1.28   | 1.28   | μs   |

| sp4    | SPI_x_CLK, SPI_x_DO, SPI_x_SS rise time (10%-90%) <sup>1</sup> | 4.7    | 4.7    | 4.7    | ns   |

| sp5    | SPI_x_CLK, SPI_x_DO, SPI_x_SS fall time (10%-90%) <sup>1</sup> | 3.4    | 3.4    | 3.4    | ns   |

#### Table 2-100 • SPI Characteristics

Commercial Case Conditions: T<sub>J</sub> = 85°C, VDD = 1.425 V, -1 Speed Grade

Notes:

These values are provided for a load of 35 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/index.php?option=com\_microsemi&ltemid=489&lang=en&view=salescontact.

2. For allowable pclk configurations, refer to the Serial Peripheral Interface Controller section in the SmartFusion Microcontroller Subsystem User's Guide.

## **5 – Pin Descriptions**

## **Supply Pins**

| Name        | Туре   | Description                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND         | Ground | Digital ground to the FPGA fabric, microcontroller subsystem and GPIOs                                                                                                                                                                                                                                                                                     |

| GND15ADC0   | Ground | Quiet analog ground to the 1.5 V circuitry of the first analog-to-digital converter (ADC)                                                                                                                                                                                                                                                                  |

| GND15ADC1   | Ground | Quiet analog ground to the 1.5 V circuitry of the second ADC                                                                                                                                                                                                                                                                                               |

| GND15ADC2   | Ground | Quite analog ground to the 1.5 V circuitry of the third ADC                                                                                                                                                                                                                                                                                                |

| GND33ADC0   | Ground | Quiet analog ground to the 3.3 V circuitry of the first ADC                                                                                                                                                                                                                                                                                                |

| GND33ADC1   | Ground | Quiet analog ground to the 3.3 V circuitry of the second ADC                                                                                                                                                                                                                                                                                               |

| GND33ADC2   | Ground | Quiet analog ground to the 3.3 V circuitry of the third ADC                                                                                                                                                                                                                                                                                                |

| GNDA        | Ground | Quiet analog ground to the analog front-end                                                                                                                                                                                                                                                                                                                |

| GNDAQ       | Ground | Quiet analog ground to the analog I/O of SmartFusion cSoCs                                                                                                                                                                                                                                                                                                 |

| GNDENVM     | Ground | Digital ground to the embedded nonvolatile memory (eNVM)                                                                                                                                                                                                                                                                                                   |

| GNDLPXTAL   | Ground | Analog ground to the low power 32 KHz crystal oscillator circuitry                                                                                                                                                                                                                                                                                         |

| GNDMAINXTAL | Ground | Analog ground to the main crystal oscillator circuitry                                                                                                                                                                                                                                                                                                     |

| GNDQ        | Ground | Quiet digital ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ needs to always be connected on the board to GND. |

| GNDRCOSC    | Ground | Analog ground to the integrated RC oscillator circuit                                                                                                                                                                                                                                                                                                      |

| GNDSDD0     | Ground | Analog ground to the first sigma-delta DAC                                                                                                                                                                                                                                                                                                                 |

| GNDSDD1     | Ground | Common analog ground to the second and third sigma-delta DACs                                                                                                                                                                                                                                                                                              |

| GNDTM0      | Ground | Analog temperature monitor common ground for signal conditioning blocks SCB 0 and SCB 1 (see information for pins "TM0" and "TM1" in the "Analog Front-End (AFE)" section on page 5-14).                                                                                                                                                                   |

| GNDTM1      | Ground | Analog temperature monitor common ground for signal conditioning block SCB 2 and SBCB 3 (see information for pins "TM2" and "TM3" in the "Analog Front-End (AFE)" section on page 5-14).                                                                                                                                                                   |

| GNDTM2      | Ground | Analog temperature monitor common ground for signal conditioning block SCB4                                                                                                                                                                                                                                                                                |

| GNDVAREF    | Ground | Analog ground reference used by the ADC. This pad should be connected to a quiet analog ground.                                                                                                                                                                                                                                                            |

| VCC         | Supply | Digital supply to the FPGA fabric and MSS, nominally 1.5 V. VCC is also required for powering the JTAG state machine, in addition to VJTAG. Even when a SmartFusion cSoC is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the SmartFusion cSoC.                   |

Notes:

1. The following 3.3 V supplies should be connected together while following proper noise filtering practices: VCC33A, VCC33ADCx, VCC33ADCx, VCC33SDDx, VCCMAINXTAL, and VCCLPXTAL.

2. The following 1.5 V supplies should be connected together while following proper noise filtering practices: VCC, VCC15A, and VCC15ADCx.

3. For more details on VCCPLLx capacitor recommendations, refer to the application note AC359, SmartFusion cSoC Board Design Guidelines, the "PLL Power Supply Decoupling Scheme" section.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin | FG256                   |                              |                              |  |  |

|-----|-------------------------|------------------------------|------------------------------|--|--|

| No. | A2F060 Function         | A2F200 Function              | A2F500 Function              |  |  |

| A1  | GND                     | GND                          | GND                          |  |  |

| A2  | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| A3  | EMC_AB[0]/IO04NDB0V0    | EMC_AB[0]/IO04NDB0V0         | EMC_AB[0]/IO06NDB0V0         |  |  |

| A4  | EMC_AB[1]/IO04PDB0V0    | EMC_AB[1]/IO04PDB0V0         | EMC_AB[1]/IO06PDB0V0         |  |  |

| A5  | GND                     | GND                          | GND                          |  |  |

| A6  | EMC_AB[3]/IO05PDB0V0    | EMC_AB[3]/IO05PDB0V0         | EMC_AB[3]/IO09PDB0V0         |  |  |

| A7  | EMC_AB[5]/IO06PDB0V0    | EMC_AB[5]/IO06PDB0V0         | EMC_AB[5]/IO10PDB0V0         |  |  |

| A8  | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| A9  | GND                     | GND                          | GND                          |  |  |

| A10 | EMC_AB[14]/IO11NDB0V0   | EMC_AB[14]/IO11NDB0V0        | EMC_AB[14]/IO15NDB0V0        |  |  |

| A11 | EMC_AB[15]/IO11PDB0V0   | EMC_AB[15]/IO11PDB0V0        | EMC_AB[15]/IO15PDB0V0        |  |  |

| A12 | GND                     | GND                          | GND                          |  |  |

| A13 | EMC_AB[20]/IO14NDB0V0   | EMC_AB[20]/IO14NDB0V0        | EMC_AB[20]/IO21NDB0V0        |  |  |

| A14 | EMC_AB[24]/IO16NDB0V0   | EMC_AB[24]/IO16NDB0V0        | EMC_AB[24]/IO20NDB0V0        |  |  |

| A15 | VCCFPGAIOB0             | VCCFPGAIOB0                  | VCCFPGAIOB0                  |  |  |

| A16 | GND                     | GND                          | GND                          |  |  |

| B1  | EMC_DB[15]/IO45PDB5V0   | EMC_DB[15]/GAA2/IO71PDB5V0   | EMC_DB[15]/GAA2/IO88PDB5V0   |  |  |

| B2  | GND                     | GND                          | GND                          |  |  |

| B3  | EMC_BYTEN[1]/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO02PDB0V0 | EMC_BYTEN[1]/GAC1/IO07PDB0V0 |  |  |

| B4  | EMC_OEN0_N/IO03NDB0V0   | EMC_OEN0_N/IO03NDB0V0        | EMC_OEN0_N/IO08NDB0V0        |  |  |

| B5  | EMC_OEN1_N/IO03PDB0V0   | EMC_OEN1_N/IO03PDB0V0        | EMC_OEN1_N/IO08PDB0V0        |  |  |

| B6  | EMC_AB[2]/IO05NDB0V0    | EMC_AB[2]/IO05NDB0V0         | EMC_AB[2]/IO09NDB0V0         |  |  |

| B7  | EMC_AB[4]/IO06NDB0V0    | EMC_AB[4]/IO06NDB0V0         | EMC_AB[4]/IO10NDB0V0         |  |  |

| B8  | EMC_AB[9]/IO08PDB0V0    | EMC_AB[9]/IO08PDB0V0         | EMC_AB[9]/IO13PDB0V0         |  |  |

| B9  | EMC_AB[12]/IO10NDB0V0   | EMC_AB[12]/IO10NDB0V0        | EMC_AB[12]/IO14NDB0V0        |  |  |

| B10 | EMC_AB[13]/IO10PDB0V0   | EMC_AB[13]/IO10PDB0V0        | EMC_AB[13]/IO14PDB0V0        |  |  |

| B11 | EMC_AB[16]/IO12NDB0V0   | EMC_AB[16]/IO12NDB0V0        | EMC_AB[16]/IO17NDB0V0        |  |  |

| B12 | EMC_AB[18]/IO13NDB0V0   | EMC_AB[18]/IO13NDB0V0        | EMC_AB[18]/IO18NDB0V0        |  |  |

| B13 | EMC_AB[21]/IO14PDB0V0   | EMC_AB[21]/IO14PDB0V0        | EMC_AB[21]/IO21PDB0V0        |  |  |

| B14 | EMC_AB[25]/IO16PDB0V0   | EMC_AB[25]/IO16PDB0V0        | EMC_AB[25]/IO20PDB0V0        |  |  |

| B15 | GND                     | GND                          | GND                          |  |  |

#### Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

SmartFusion Customizable System-on-Chip (cSoC)

| Pin<br>No. | FG256                |                           |                           |  |  |

|------------|----------------------|---------------------------|---------------------------|--|--|

|            | A2F060 Function      | A2F200 Function           | A2F500 Function           |  |  |

| H13        | TDO                  | TDO                       | TDO                       |  |  |

| H14        | TDI                  | TDI                       | TDI                       |  |  |

| H15        | JTAGSEL              | JTAGSEL                   | JTAGSEL                   |  |  |

| H16        | GND                  | GND                       | GND                       |  |  |

| J1         | EMC_DB[4]/IO38NPB5V0 | EMC_DB[4]/GEA0/IO61NPB5V0 | EMC_DB[4]/GEA0/IO78NPB5V0 |  |  |

| J2         | EMC_DB[3]/IO37PDB5V0 | EMC_DB[3]/GEC2/IO60PDB5V0 | EMC_DB[3]/GEC2/IO77PDB5V0 |  |  |

| J3         | EMC_DB[2]/IO37NDB5V0 | EMC_DB[2]/IO60NDB5V0      | EMC_DB[2]/IO77NDB5V0      |  |  |

| J4         | GNDRCOSC             | GNDRCOSC                  | GNDRCOSC                  |  |  |

| J5         | NC                   | GNDQ                      | GNDQ                      |  |  |

| J6         | GND                  | GND                       | GND                       |  |  |

| J7         | VCC                  | VCC                       | VCC                       |  |  |

| J8         | GND                  | GND                       | GND                       |  |  |

| J9         | VCC                  | VCC                       | VCC                       |  |  |

| J10        | GND                  | GND                       | GND                       |  |  |

| J11        | VCCMSSIOB2           | VCCMSSIOB2                | VCCMSSIOB2                |  |  |

| J12        | I2C_0_SCL/GPIO_23    | I2C_0_SCL/GPIO_23         | I2C_0_SCL/GPIO_23         |  |  |

| J13        | I2C_0_SDA/GPIO_22    | I2C_0_SDA/GPIO_22         | I2C_0_SDA/GPIO_22         |  |  |

| J14        | I2C_1_SCL/GPIO_31    | I2C_1_SCL/GPIO_31         | I2C_1_SCL/GPIO_31         |  |  |

| J15        | VCCMSSIOB2           | VCCMSSIOB2                | VCCMSSIOB2                |  |  |

| J16        | I2C_1_SDA/GPIO_30    | I2C_1_SDA/GPIO_30         | I2C_1_SDA/GPIO_30         |  |  |

| K1         | GPIO_1/IO32RSB4V0    | MAC_MDIO/IO49RSB4V0       | MAC_MDIO/IO58RSB4V0       |  |  |

| K2         | GPIO_0/IO33RSB4V0    | MAC_MDC/IO48RSB4V0        | MAC_MDC/IO57RSB4V0        |  |  |

| K3         | VCCMSSIOB4           | VCCMSSIOB4                | VCCMSSIOB4                |  |  |

| K4         | MSS_RESET_N          | MSS_RESET_N               | MSS_RESET_N               |  |  |

| K5         | VCCRCOSC             | VCCRCOSC                  | VCCRCOSC                  |  |  |

| K6         | VCCMSSIOB4           | VCCMSSIOB4                | VCCMSSIOB4                |  |  |

| K7         | GND                  | GND                       | GND                       |  |  |

| K8         | VCC                  | VCC                       | VCC                       |  |  |

| K9         | GND                  | GND                       | GND                       |  |  |

| K10        | VCC                  | VCC                       | VCC                       |  |  |

| K11        | GND                  | GND                       | GND                       |  |  |

| Notes:     |                      | •                         | •                         |  |  |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

🕓 Microsemi.

SmartFusion Customizable System-on-Chip (cSoC)

|            | FG              | 484             |

|------------|-----------------|-----------------|

| Pin Number | A2F200 Function | A2F500 Function |

| L9         | VCC             | VCC             |

| L10        | GND             | GND             |

| L11        | VCC             | VCC             |

| L12        | GND             | GND             |

| L13        | VCC             | VCC             |

| L14        | GND             | GND             |

| L15        | VCC             | VCC             |

| L16        | GND             | GND             |

| L17        | GNDQ            | GNDQ            |

| L18        | GDA2/IO33NDB1V0 | GDA2/IO42NDB1V0 |

| L19        | VCCFPGAIOB1     | VCCFPGAIOB1     |

| L20        | GDB1/IO30PDB1V0 | GDB1/IO39PDB1V0 |

| L21        | GDB0/IO30NDB1V0 | GDB0/IO39NDB1V0 |

| L22        | GDC2/IO32PDB1V0 | GDC2/IO41PDB1V0 |

| M1         | NC              | IO71PDB5V0      |

| M2         | NC              | IO71NDB5V0      |

| M3         | VCCFPGAIOB5     | VCCFPGAIOB5     |

| M4         | NC              | IO72NPB5V0      |

| M5         | GNDQ            | GNDQ            |

| M6         | NC              | IO68PDB5V0      |

| M7         | GND             | GND             |

| M8         | VCC             | VCC             |

| M9         | GND             | GND             |

| M10        | VCC             | VCC             |

| M11        | GND             | GND             |

| M12        | VCC             | VCC             |

| M13        | GND             | GND             |

| M14        | VCC             | VCC             |

| M15        | GND             | GND             |

| M16        | VCCFPGAIOB1     | VCCFPGAIOB1     |

| M17        | NC              | NC              |

| M18        | GDB2/IO33PDB1V0 | GDB2/IO42PDB1V0 |

| M19        | VJTAG           | VJTAG           |

| M20        | GND             | GND             |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

|            | FG              | 484             |

|------------|-----------------|-----------------|

| Pin Number | A2F200 Function | A2F500 Function |

| M21        | VPP             | VPP             |

| M22        | IO32NDB1V0      | IO41NDB1V0      |

| N1         | GND             | GND             |

| N2         | NC              | IO70PDB5V0      |

| N3         | NC              | IO70NDB5V0      |

| N4         | VCCRCOSC        | VCCRCOSC        |

| N5         | VCCFPGAIOB5     | VCCFPGAIOB5     |

| N6         | NC              | IO68NDB5V0      |

| N7         | VCCFPGAIOB5     | VCCFPGAIOB5     |

| N8         | GND             | GND             |

| N9         | VCC             | VCC             |

| N10        | GND             | GND             |

| N11        | VCC             | VCC             |

| N12        | GND             | GND             |

| N13        | VCC             | VCC             |

| N14        | GND             | GND             |

| N15        | VCC             | VCC             |

| N16        | NC              | GND             |

| N17        | NC              | NC              |

| N18        | VCCFPGAIOB1     | VCCFPGAIOB1     |

| N19        | VCCENVM         | VCCENVM         |

| N20        | GNDENVM         | GNDENVM         |

| N21        | NC              | NC              |

| N22        | GND             | GND             |

| P1         | NC              | IO69NDB5V0      |

| P2         | NC              | IO69PDB5V0      |

| P3         | GNDRCOSC        | GNDRCOSC        |

| P4         | GND             | GND             |

| P5         | NC              | NC              |

| P6         | NC              | NC              |

| P7         | GND             | GND             |

| P8         | VCC             | VCC             |

| P9         | GND             | GND             |

| P10        | VCC             | VCC             |

Notes:

1. Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

Datasheet Information

| Revision | Changes                                                                                                                                                                                                   | Page                  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|          | The A2F060 device was added to product information tables.                                                                                                                                                | N/A                   |

|          | The "Product Ordering Codes" table was updated to removed Std. speed and add speed grade 1. Pre-production was removed from the application ordering code category.                                       | VI                    |

|          | The "SmartFusion cSoC Block Diagram" was revised.                                                                                                                                                         | IV                    |

|          | The "Datasheet Categories" section was updated, referencing the "SmartFusion cSoC Block Diagram" table, which is new.                                                                                     | 1-4, IV               |

|          | The "VCCI" parameter was renamed to "VCCxxxxIOBx."<br>"Advanced I/Os" were renamed to "FPGA I/Os."                                                                                                        | N/A                   |

|          | Generic pin names that represent multiple pins were standardized with a lower case x as a placeholder. For example, VAREFx designates VAREF0, VAREF1, and VAREF2. Modes were renamed as follows:          |                       |

|          | Operating mode was renamed to SoC mode.                                                                                                                                                                   |                       |

|          | 32KHz Active mode was renamed to Standby mode.                                                                                                                                                            |                       |

|          | Battery mode was renamed to Time Keeping mode.                                                                                                                                                            |                       |

|          | Table entries have been filled with values as data has become available.                                                                                                                                  |                       |

|          | Table 2-1 • Absolute Maximum Ratings, Table 2-2 • Analog Maximum Ratings, and Table 2-3 • Recommended Operating Conditions <sup>5,6</sup> were revised extensively.                                       | 2-1<br>through<br>2-3 |

|          | Device names were updated in Table 2-6 • Package Thermal Resistance.                                                                                                                                      | 2-7                   |

|          | Table 2-8 • Power Supplies Configuration was revised extensively.                                                                                                                                         | 2-10                  |

|          | Table 2-11 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings was revised extensively.                                                                                         | 2-11                  |

|          | Removed "Example of Power Calculation."                                                                                                                                                                   | N/A                   |

|          | Table 2-14 • Different Components Contributing to Dynamic Power Consumption in SmartFusion cSoCs was revised extensively.                                                                                 | 2-12                  |

|          | Table 2-15 • Different Components Contributing to the Static Power Consumption in SmartFusion cSoCs was revised extensively.                                                                              | 2-13                  |

|          | The "Power Calculation Methodology" section was revised.                                                                                                                                                  | 2-14                  |

|          | Table 2-83 • Electrical Characteristics of the RC Oscillator was revised extensively.                                                                                                                     | 2-61                  |