Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 2MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 5                                                                      |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                            |

| Data Converters            | A/D 4x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 8-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchlc908qt2cpe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features of the CPU08 include the following:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

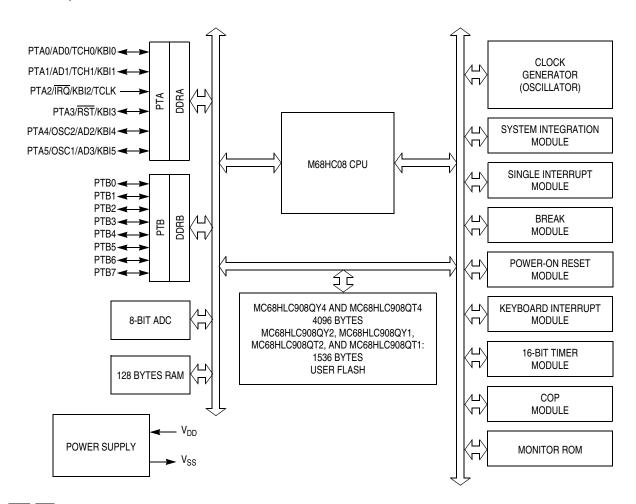

# 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HLC908QY4.

# 1.4 Pin Assignments

The MC68HLC908QT4, MC68HLC908QT2, and MC68HLC908QT1 are available in 8-pin packages and the MC68HLC908QY4, MC68HLC908QY2, and MC68HLC908QY1 in 16-pin packages. Figure 1-2 shows the pin assignment for these packages.

# **General Description**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

18

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices – MC68HLC908QT1, MC68HLC908QT2, and MC68HLC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HLC908QY1 and MC68HC9L08QT1

Figure 1-1. Block Diagram

MC68HLC908QY/QT Family Data Sheet, Rev. 3

Auto Wakeup Module (AWU)

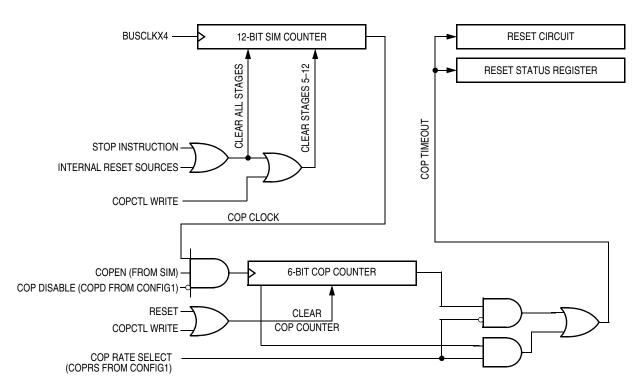

# **Chapter 6 Computer Operating Properly (COP)**

# 6.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the configuration 1 (CONFIG1) register.

# **6.2 Functional Description**

Figure 6-1. COP Block Diagram

# **Central Processor Unit (CPU)**

Table 7-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | Effect on CCR |   |          | Address<br>Mode | Opcode   | Operand                                             | es                                               |                                                 |                                      |

|------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|---|----------|-----------------|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | ) Description                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ٧  | Н             | ı | N        | z               | С        | Add                                                 | obc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                           | Clear                            | $\begin{array}{c} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                          | 0  | _             | _ | 0        | 1               | _        | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff                                        | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP  | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | _             | _ | <b>‡</b> | ‡               | ‡        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                                                                                                                 | 0  | -             | _ | <b>‡</b> | 1               | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1  | -             | - | ‡        | 1               | 1        | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ţ  | _             | _ | <b>‡</b> | 1               | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff          | 23443245                             |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U  | -             | _ | 1        | 1               | 1        | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ Opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A)-1 \text{ or } M \leftarrow (M)-1 \text{ or } X \leftarrow (X)-1 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+4+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+4+\mathit{rel}? \text{ (result)} \neq 0 \end{array}$ | _  | _             | _ | _        | _               | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 533546                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{l} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                     | î  | _             | - | 1        | 1               | -        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                            | Divide                           | $\begin{array}{c} A \leftarrow (\text{H:A})/(\text{X}) \\ \text{H} \leftarrow \text{Remainder} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -  | -             | - | -        | ‡               | ‡        | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0  | _             | _ | ‡        | 1               | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Į. | _             | _ | Î        | 1               | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

# Table 7-1. Instruction Set Summary (Sheet 6 of 6)

| Source                                                       | Operation                             | Description                                                                                                                                                                                                                                                                                                                                                                  |   |   |   | ec<br>CC |   |   | Address<br>Mode                       | Opcode                             | Operand        | rand        |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|----------|---|---|---------------------------------------|------------------------------------|----------------|-------------|--|--|--|--|

| Form                                                         | Form Beschption                       |                                                                                                                                                                                                                                                                                                                                                                              | ٧ | Н | I | N        | Z | С | Add                                   | Opc                                | Ope            | Cycles      |  |  |  |  |

| SWI                                                          | Software Interrupt                    | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  l \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ | - | - | 1 | -        | _ | _ | INH                                   | 83                                 |                | 9           |  |  |  |  |

| TAP                                                          | Transfer A to CCR                     | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                    |   | 1 | 1 | 1        | 1 | 1 | INH                                   | 84                                 |                | 2           |  |  |  |  |

| TAX                                                          | Transfer A to X                       | $X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                                           | - | - | - | -        | - | - | INH                                   | 97                                 |                | 1           |  |  |  |  |

| TPA                                                          | Transfer CCR to A                     | $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                         | - | - | - | -        | - | - | INH                                   | 85                                 |                | 1           |  |  |  |  |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP | Test for Negative or Zero             | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                       |   | _ | ı | 1        | ‡ | ı | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 3 1 1 3 2 4 |  |  |  |  |

| TSX                                                          | Transfer SP to H:X                    | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                               | - | - | _ | -        | - | - | INH                                   | 95                                 |                | 2           |  |  |  |  |

| TXA                                                          | Transfer X to A                       | $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                                           | - | - | _ | _        | - | - | INH                                   | 9F                                 |                | 1           |  |  |  |  |

| TXS                                                          | Transfer H:X to SP                    | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                             | - | - | _ | -        | _ | _ | INH                                   | 94                                 |                | 2           |  |  |  |  |

| WAIT                                                         | Enable Interrupts; Wait for Interrupt | I bit ← 0; Inhibit CPU clocking until interrupted                                                                                                                                                                                                                                                                                                                            | - | - | 0 | -        | - | - | INH                                   | 8F                                 |                | 1           |  |  |  |  |

| Α     | Accumulator                                                         | n               | Any bit                                     |

|-------|---------------------------------------------------------------------|-----------------|---------------------------------------------|

| С     | Carry/borrow bit                                                    | opr             | Operand (one or two bytes)                  |

| CCR   | Condition code register                                             | PC              | Program counter                             |

| dd    | Direct address of operand                                           | PCH             | Program counter high byte                   |

| dd rr | Direct address of operand and relative offset of branch instruction |                 | Program counter low byte                    |

| DD    | Direct to direct addressing mode                                    | REL             | Relative addressing mode                    |

| DIR   | Direct addressing mode                                              | rel             | Relative program counter offset byte        |

| DIX+  | Direct to indexed with post increment addressing mode               | rr              | Relative program counter offset byte        |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | SP1             | Stack pointer, 8-bit offset addressing mode |

| EXT   | Extended addressing mode                                            | SP2             | Stack pointer 16-bit offset addressing mode |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | SP              | Stack pointer                               |

| Н     | Half-carry bit                                                      | U               | Undefined                                   |

| Н     | Index register high byte                                            | V               | Overflow bit                                |

| hh II | High and low bytes of operand address in extended addressing        | Χ               | Index register low byte                     |

|       | Interrupt mask                                                      | Z               | Zero bit                                    |

| ii    | Immediate operand byte                                              | &               | Logical AND                                 |

| IMD   | Immediate source to direct destination addressing mode              |                 | Logical OR                                  |

| IMM   | Immediate addressing mode                                           | $\oplus$        | Logical EXCLUSIVE OR                        |

| INH   | Inherent addressing mode                                            | ()              | Contents of                                 |

| IX    | Indexed, no offset addressing mode                                  | <del>-</del> () | Negation (two's complement)                 |

| IX+   | Indexed, no offset, post increment addressing mode                  | #`              | Immediate value                             |

| IX+D  | Indexed with post increment to direct addressing mode               | **              | Sign extend                                 |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$    | Loaded with                                 |

| IX1+  | Indexed, 8-bit offset, post increment addressing mode               | ?               | If                                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | :               | Concatenated with                           |

| M     | Memory location                                                     | <b>‡</b>        | Set or cleared                              |

| N     | Negative bit                                                        | _               | Not affected                                |

# 7.8 Opcode Map

See Table 7-2.

Polling and forced reset operation modes can be combined to take full advantage of LVD and LVR trip voltages selection. LVD (LVDLVR = 1) in polling mode (LVIRSTD = 1) can be used as a low voltage warning in a slowly and continuously falling  $V_{DD}$  application (for example, battery applications). Once LVD has been identified, the part can be set to LVR (LVDLVR = 0) and reset enabled (LVIRSTD = 0). So, as  $V_{DD}$  continues to fall the part will reset when LVR trip voltage is reached. Unlike other bits in CONFIG registers, LVIRSTD and LVDLVR bits are allowed to be written multiple times after reset.

#### NOTE

The microcontroller is guaranteed to operate at a minimum supply voltage. The trip point ( $V_{TRIPF}$  [LVD] or  $V_{TRIPF}$  [LVR]) may be lower than this. See 16.5 DC Electrical Characteristics for the actual trip point voltages.

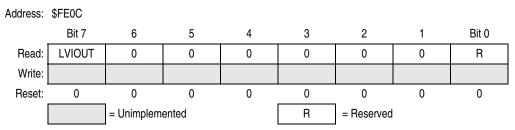

# 10.4 LVI Status Register

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level while LVI resets have been disabled.

Figure 10-2. LVI Status Register (LVISR)

# LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPR}$ . The difference in these threshold levels results in a hysteresis that prevents oscillation into and out of reset (see Table 10-1). Reset clears the LVIOUT bit.

| V <sub>DD</sub>                                           | LVIOUT         |

|-----------------------------------------------------------|----------------|

| V <sub>DD</sub> > V <sub>TRIPR</sub>                      | 0              |

| V <sub>DD</sub> < V <sub>TRIPF</sub>                      | 1              |

| V <sub>TRIPF</sub> < V <sub>DD</sub> < V <sub>TRIPR</sub> | Previous value |

Table 10-1, LVIOUT Bit Indication

# 10.5 LVI Interrupts

The LVI module does not generate interrupt requests.

Input/Output Ports (PORTS)

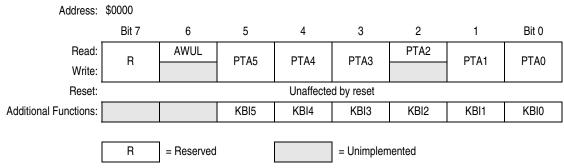

# 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the six port A pins.

Figure 12-1. Port A Data Register (PTA)

# PTA[5:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

# AWUL — Auto Wakeup Latch Data Bit

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally (see Chapter 4 Auto Wakeup Module (AWU)). There is no PTA6 port nor any of the associated bits such as PTA6 data register, pullup enable or direction.

#### KBI[5:0] — Port A Keyboard Interrupts

The keyboard interrupt enable bits, KBIE5–KBIE0, in the keyboard interrupt control enable register (KBIER) enable the port A pins as external interrupt pins (see Chapter 9 Keyboard Interrupt Module (KBI)).

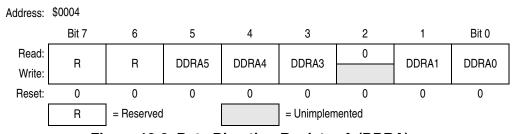

# 12.2.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

Figure 12-2. Data Direction Register A (DDRA)

# DDRA[5:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[5:0], configuring all port A pins as inputs.

- 1 = Corresponding port A pin configured as output

- 0 = Corresponding port A pin configured as input

## **NOTE**

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

#### Input/Output Ports (PORTS)

# PTAPUE[5:0] — Port A Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port A pins.

- 1 = Corresponding port A pin configured to have internal pull if its DDRA bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port A pin regardless of the state of its DDRA bit

Table 12-1 summarizes the operation of the port A pins.

Table 12-1. Port A Pin Functions

| PTAPUE | DDRA | PTA              | I/O Pin                               | Accesses to DDRA | Access    | ses to PTA               |

|--------|------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit  | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0    | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRA5-DDRA0      | Pin       | PTA5-PTA0 <sup>(3)</sup> |

| 0      | 0    | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRA5-DDRA0      | Pin       | PTA5-PTA0 <sup>(3)</sup> |

| Х      | 1    | Х                | Output                                | DDRA5-DDRA0      | PTA5-PTA0 | PTA5-PTA0 <sup>(5)</sup> |

- 1. X = don't care

- 2. I/O pin pulled to  $V_{DD}$  by internal pullup.

- 3. Writing affects data register, but does not affect input.

- 4. Hi-Z = high impedance

- 5. Output does not apply to PTA2

# 12.3 Port B

Port B is an 8-bit general purpose I/O port. Port B is only available on the MC68HLC908QY1, MC68HLC908QY2, and MC68HLC908QY4.

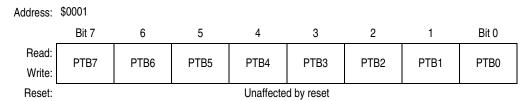

# 12.3.1 Port B Data Register

The port B data register (PTB) contains a data latch for each of the eight port B pins.

Figure 12-5. Port B Data Register (PTB)

#### PTB[7:0] — Port B Data Bits

These read/write bits are software programmable. Data direction of each port B pin is under the control of the corresponding bit in data direction register B. Reset has no effect on port B data.

#### **System Integration Module (SIM)**

The LDA opcode is prefetched by both the INT1 and INT2 return-from-interrupt (RTI) instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

#### NOTE

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

# 13.6.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

#### NOTE

A software interrupt pushes PC onto the stack. A software interrupt does **not** push PC – 1, as a hardware interrupt does.

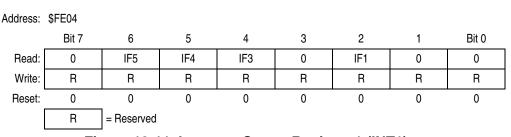

# 13.6.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. Table 13-3 summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

**Table 13-3. Interrupt Sources**

| Priority | Source                            | Flag | Mask <sup>(1)</sup> | INT<br>Register<br>Flag | Vector<br>Address |

|----------|-----------------------------------|------|---------------------|-------------------------|-------------------|

| Highest  | Reset                             | _    | _                   | _                       | \$FFFE-\$FFFF     |

| <b>A</b> | SWI instruction                   | _    | _                   | _                       | \$FFFC-\$FFFD     |

|          | ĪRQ pin                           | IRQF | IMASK               | IF1                     | \$FFFA-\$FFFB     |

|          | Timer channel 0 interrupt         | CH0F | CH0IE               | IF3                     | \$FFF6-\$FFF7     |

|          | Timer channel 1 interrupt         | CH1F | CH1IE               | IF4                     | \$FFF4-\$FFF5     |

|          | Timer overflow interrupt          | TOF  | TOIE                | IF5                     | \$FFF2-\$FFF3     |

| <b>\</b> | Keyboard interrupt                | KEYF | IMASKK              | IF14                    | \$FFE0-\$FFE1     |

| Lowest   | ADC conversion complete interrupt | COCO | AIEN                | IF15                    | \$FFDE-\$FFDF     |

The I bit in the condition code register is a global mask for all interrupt sources except the SWI instruction.

# 13.6.2.1 Interrupt Status Register 1

Figure 13-11. Interrupt Status Register 1 (INT1)

MC68HLC908QY/QT Family Data Sheet, Rev. 3

## **Timer Interface Module (TIM)**

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as a 0. Reset clears the TRST bit.

- 1 = Prescaler and TIM counter cleared

- 0 = No effect

## NOTE

Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

# PS[2:0] — Prescaler Select Bits

These read/write bits select either the PTA2/TCLK pin or one of the seven prescaler outputs as the input to the TIM counter as Table 14-2 shows. Reset clears the PS[2:0] bits.

PS<sub>2</sub> PS<sub>1</sub> PS<sub>0</sub> **TIM Clock Source** 0 0 0 Internal bus clock ÷ 1 0 0 1 Internal bus clock ÷ 2 0 0 Internal bus clock ÷ 4 0 1 1 Internal bus clock ÷ 8 0 0 1 Internal bus clock ÷ 16 1 0 1 Internal bus clock ÷ 32 1 1 0 Internal bus clock ÷ 64 1 1 PTA2/TCLK

**Table 14-2. Prescaler Selection**

# 14.9.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

# NOTE

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

When the internal address bus matches the value written in the break address registers or when software writes a 1 to the BRKA bit in the break status and control register, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode)

The break interrupt timing is:

- When a break address is placed at the address of the instruction opcode, the instruction is not executed until after completion of the break interrupt routine.

- When a break address is placed at an address of an instruction operand, the instruction is executed before the break interrupt.

- When software writes a 1 to the BRKA bit, the break interrupt occurs just before the next instruction is executed.

By updating a break address and clearing the BRKA bit in a break interrupt routine, a break interrupt can be generated continuously.

#### **CAUTION**

A break address should be placed at the address of the instruction opcode. When software does not change the break address and clears the BRKA bit in the first break interrupt routine, the next break interrupt will not be generated after exiting the interrupt routine even when the internal address bus matches the value written in the break address registers.

# 15.2.1.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register and the **Break Interrupts** subsection for each module.

# 15.2.1.2 TIM During Break Interrupts

A break interrupt stops the timer counter.

# 15.2.1.3 COP During Break Interrupts

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

# 15.2.2 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

- Break status register (BSR)

- Break flag control register (BFCR)

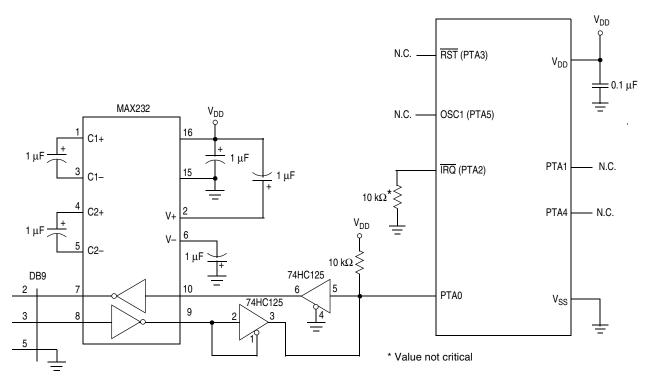

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 4800 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (1.0 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- IRQ = V<sub>SS</sub> (internal oscillator is selected, no external clock required)

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

#### **Development Support**

# 15.3.2 Security

A security feature discourages unauthorized reading of FLASH locations while in monitor mode. The host can bypass the security feature at monitor mode entry by sending eight security bytes that match the bytes at locations \$FFF6\_\$FFFD. Locations \$FFF6\_\$FFFD contain user-defined data.

#### NOTE

Do not leave locations \$FFF6-\$FFFD blank. For security reasons, program locations \$FFF6-\$FFFD even if they are not used for vectors.

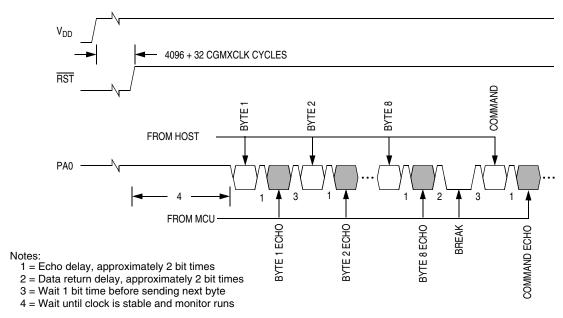

During monitor mode entry, the MCU waits after the power-on reset for the host to send the eight security bytes on pin PTA0. If the received bytes match those at locations \$FFF6—\$FFFD, the host bypasses the security feature and can read all FLASH locations and execute code from FLASH. Security remains bypassed until a power-on reset occurs. If the reset was not a power-on reset, security remains bypassed and security code entry is not required. See Figure 15-18.

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6-\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

## **NOTE**

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$80 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

Figure 15-18. Monitor Mode Entry Timing

MC68HLC908QY/QT Family Data Sheet, Rev. 3

# **Electrical Specifications**

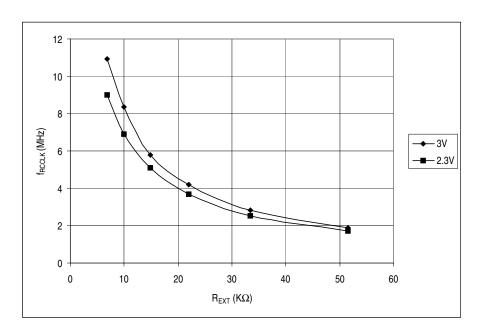

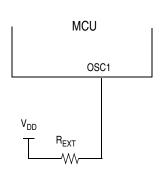

# 16.8 Oscillator Characteristics

| Characteristic                                         | Symbol               | Min                  | Тур                | Max | Unit |

|--------------------------------------------------------|----------------------|----------------------|--------------------|-----|------|

| Internal oscillator frequency <sup>(1)</sup>           | f <sub>INTCLK</sub>  | _                    | 4.0                | _   | MHz  |

| Crystal frequency, XTALCLK <sup>(1)</sup>              | f <sub>OSCXCLK</sub> | 30                   | 32.768             | 100 | kHz  |

| External RC oscillator frequency, RCCLK <sup>(1)</sup> | f <sub>RCCLK</sub>   | f <sub>RCCLK</sub> 2 |                    | 8   | MHz  |

| External clock reference frequency <sup>(1), (2)</sup> | foscxclk             | dc                   | _                  | 8   | MHz  |

| Crystal load capacitance <sup>(3)</sup>                | C <sub>L</sub>       | _                    | 12.5               | _   | pF   |

| Crystal fixed capacitance <sup>(3)</sup>               | C <sub>1</sub>       | _                    | 2 x C <sub>L</sub> | _   | _    |

| Crystal tuning capacitance <sup>(3)</sup>              | C <sub>2</sub>       | _                    | 2 x C <sub>L</sub> | _   | _    |

| Feedback bias resistor                                 | R <sub>B</sub>       | 1                    | 10                 | 22  | ΜΩ   |

| Series resistor                                        | R <sub>S</sub>       | 100                  | 330                | 470 | kΩ   |

| RC oscillator external resistor                        | R <sub>EXT</sub>     | (                    | _                  |     |      |

- 1. Bus frequency,  $f_{OP}$ , is oscillator frequency divided by 4. 2. No more than 10% duty cycle deviation from 50%.

- 3. Consult crystal vendor data sheet.

Figure 16-4. Typical RC Oscillator Frequency versus R<sub>EXT</sub> (25°C)

# 16.9 Supply Current Characteristics

| Characteristic                                                                                                                                                 | Voltage    | Bus Freq.<br>(MHz) | Symbol             | Тур                                  | Max                 | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|--------------------|--------------------------------------|---------------------|------|

| Run mode V <sub>DD</sub> supply current <sup>(1)</sup>                                                                                                         | 3.0<br>2.2 | 1<br>1             | RI <sub>DD</sub>   | 1.5<br>1.0                           | 2.5<br>1.5          | mA   |

| WAIT mode V <sub>DD</sub> supply current <sup>(2)</sup>                                                                                                        | 3.0<br>2.2 | 1<br>1             | WI <sub>DD</sub>   | 1.2<br>1.0                           | 2.0<br>1.0          | mA   |

| Stop mode V <sub>DD</sub> supply current <sup>(3)</sup> 25°C 0 to 70°C -40 to 85°C 25°C with auto wake-up enabled Incremental current with LVI enabled at 25°C | 3.0        |                    | SI.                | 0.006<br>0.08<br>0.12<br>5.70<br>110 |                     | μΑ   |

| 25°C 0 to 70°C -40 to 85°C 25°C with auto wake-up enabled Incremental current with LVI enabled at 25°C                                                         | 2.2        |                    | - SI <sub>DD</sub> | 0.005<br>0.08<br>0.12<br>1.30<br>100 | <br><br>1.0<br><br> | μΑ   |

- 1. Run (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules except ADC enabled.

- 2. Wait (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules except ADC enabled.

- 3. Stop I<sub>DD</sub> measured with all ports driven 0.2 V or less from rail. No dc loads. On the 8-pin versions, port B is configured as inputs with pullups enabled.

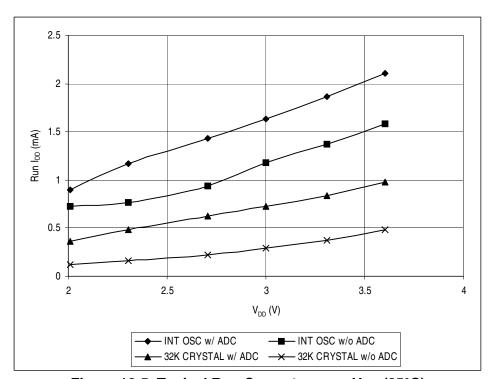

Figure 16-5. Typical Run Current versus  $V_{DD}$  (25°C) ( $f_{Bus}$  = 1 MHz for Internal Oscillator,  $f_{Bus}$  = 8 kHz for Crystal Oscillator)

MC68HLC908QY/QT Family Data Sheet, Rev. 3

# **Electrical Specifications**

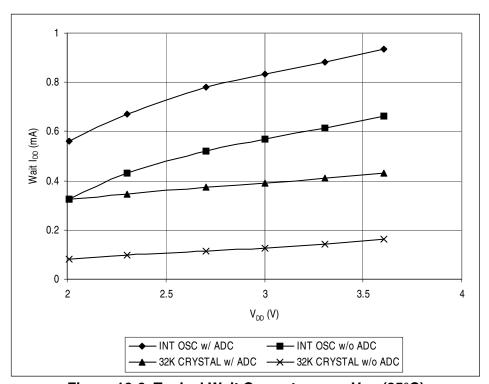

Figure 16-6. Typical Wait Current versus  $V_{DD}$  (25°C)  $f_{Bus}$  = 1 MHz for Internal Oscillator,  $f_{Bus}$  = 8 kHz for Crystal Oscillator)

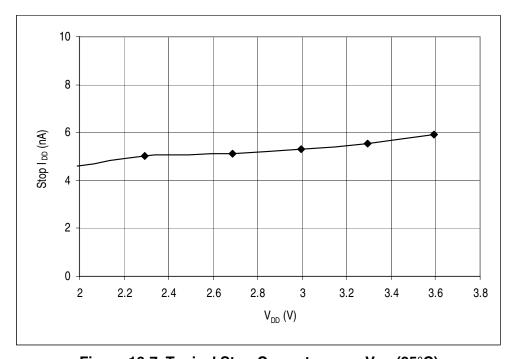

Figure 16-7. Typical Stop Current versus V<sub>DD</sub> (25°C)

# **Electrical Specifications**

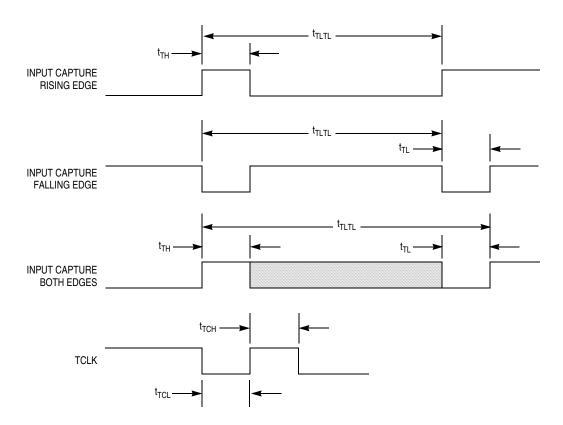

# **16.11 Timer Interface Module Characteristics**

| Characteristic                  | Symbol                              | Min                  | Max | Unit             |

|---------------------------------|-------------------------------------|----------------------|-----|------------------|

| Timer input capture pulse width | t <sub>TH</sub> , t <sub>TL</sub>   | 2                    | _   | t <sub>cyc</sub> |

| Timer input capture period      | t <sub>TLTL</sub>                   | Note <sup>(1)</sup>  | _   | t <sub>cyc</sub> |

| Timer input clock pulse width   | t <sub>TCL</sub> , t <sub>TCH</sub> | t <sub>cyc</sub> + 5 | _   | ns               |

<sup>1.</sup> The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-8. Timer Input Timing

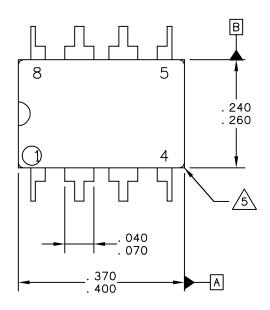

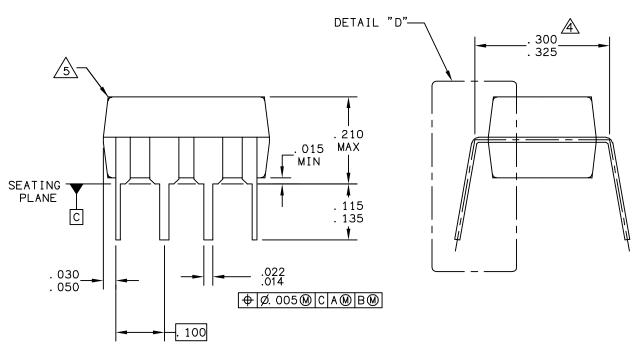

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                            |           | CASE NUMBER  | 19 MAY 2005      |             |

|                                                      |           | STANDARD: NO | N-JEDEC          |             |

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

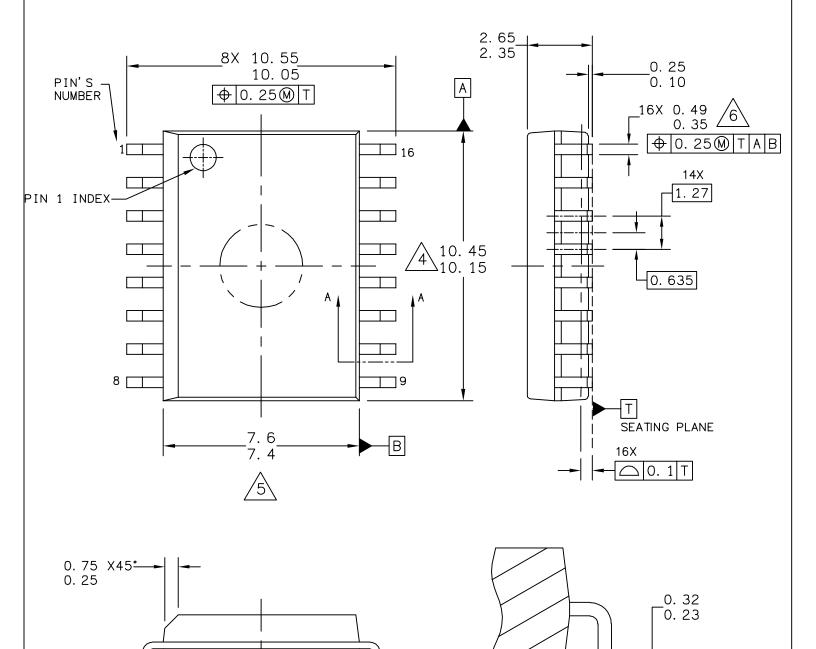

# MECHANICAL OUTLINES DICTIONARY

DO NOT SCALE THIS DRAWING

DOCUMENT NO: 98ASB42567B

PAGE: 751G

REV: E

16LD SOIC W/B, 1.27 PITCH CASE-OUTLINE

CASE NUMBER: 751G-05

STANDARD: JEDEC MS-013AA

SECTION A-A

PACKAGE CODE: 2003 | SHEET: 1 OF 3

0°