Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 2MHz                                                                   |

| Connectivity               | -                                                                      |

| Peripherals                | LVD, POR, PWM                                                          |

| Number of I/O              | 5                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 128 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                            |

| Data Converters            | A/D 4x8b                                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 8-SO                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mchlc908qt4dwe |

**List of Chapters**

| <b>T</b> - | <b>L</b> | ۱. | _4 |    |     |     |

|------------|----------|----|----|----|-----|-----|

| ıa         | D        | ıe | OΙ | Co | nte | nis |

| 9.7<br>9.7.1<br>9.7.2 | Input/Output Registers                                     | 83 |

|-----------------------|------------------------------------------------------------|----|

|                       | Chapter 10<br>Low-Voltage Inhibit (LVI)                    |    |

| 10.1                  | Introduction                                               | 25 |

| 10.2                  | Features                                                   |    |

| 10.3                  | Functional Description                                     |    |

| 10.3.1                | Polled LVI Operation                                       |    |

| 10.3.2                | Forced Reset Operation                                     |    |

| 10.3.3                | Voltage Hysteresis Protection                              |    |

| 10.3.4                | LVI Trip Selection                                         |    |

| 10.4                  | LVI Status Register                                        |    |

| 10.5                  | LVI Interrupts                                             |    |

| 10.6                  | Low-Power Modes                                            |    |

| 10.6.1<br>10.6.2      | Wait Mode                                                  |    |

| 10.0.2                | Stop Wode                                                  | 00 |

|                       | Chapter 11                                                 |    |

|                       | Oscillator Module (OSC)                                    |    |

| 11.1                  | Introduction                                               |    |

| 11.2                  | Features                                                   |    |

| 11.3                  | Functional Description                                     |    |

| 11.3.1                | Internal Oscillator                                        |    |

| 11.3.1.<br>11.3.1.    | J                                                          |    |

| 11.3.1.               | External Oscillator                                        |    |

| 11.3.3                | XTAL Oscillator                                            |    |

| 11.3.4                | RC Oscillator                                              |    |

| 11.4                  | Oscillator Module Signals                                  | 93 |

| 11.4.1                | Crystal Amplifier Input Pin (OSC1)                         | 93 |

| 11.4.2                | Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4)          | 93 |

| 11.4.3                | Oscillator Enable Signal (SIMOSCEN)                        |    |

| 11.4.4<br>11.4.5      | XTAL Oscillator Clock (XTALCLK)RC Oscillator Clock (RCCLK) |    |

| 11.4.6                | Internal Oscillator Clock (INTCLK)                         |    |

| 11.4.7                | Oscillator Out 2 (BUSCLKX4)                                |    |

| 11.4.8                | Oscillator Out (BUSCLKX2)                                  |    |

| 11.5                  | Low Power Modes                                            | 94 |

| 11.5.1                | Wait Mode                                                  | -  |

| 11.5.2                | Stop Mode                                                  |    |

| 11.6                  | Oscillator During Break Mode                               |    |

| 11.7                  | CONFIG2 Options                                            |    |

| 11.8                  | Input/Output (I/O) Registers                               |    |

| 11.8.1                | Oscillator Status Register (OSCIDIM)                       |    |

| 11.8.2                | Oscillator Trim Register (OSCTRIM)                         | 90 |

MC68HLC908QY/QT Family Data Sheet, Rev. 3

|  |  |  | nts |

|--|--|--|-----|

|  |  |  |     |

|  |  |  |     |

| 13.8               | SIM Registers                                  | 116 |

|--------------------|------------------------------------------------|-----|

| 13.8.1             | SIM Reset Status Register                      | 117 |

| 13.8.2             | Break Flag Control Register                    | 118 |

|                    | Chapter 14                                     |     |

|                    | Timer Interface Module (TIM)                   |     |

| 14.1               | Introduction                                   | 119 |

| 14.2               | Features                                       | 119 |

| 14.3               | Pin Name Conventions                           | 119 |

| 14.4               | Functional Description                         | 121 |

| 14.4.1             | TIM Counter Prescaler                          |     |

| 14.4.2             | Input Capture                                  | 122 |

| 14.4.3             | Output Compare                                 | 122 |

| 14.4.3.            | 1 Unbuffered Output Compare                    | 122 |

| 14.4.3.            | 2 Buffered Output Compare                      | 122 |

| 14.4.4             | Pulse Width Modulation (PWM)                   | 123 |

| 14.4.4.            | 1 Unbuffered PWM Signal Generation             | 124 |

| 14.4.4.            |                                                | 124 |

| 14.4.4.            | 3 PWM Initialization                           | 125 |

| 14.5               | Interrupts                                     | 125 |

| 14.6               | Wait Mode                                      | 126 |

| 14.7               | TIM During Break Interrupts                    |     |

| 14.8               | Input/Output Signals                           |     |

| 14.8.1             | TIM Clock Pin (PTA2/TCLK)                      |     |

| 14.8.2             | TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1) |     |

| 14.9               | Input/Output Registers                         |     |

| 14.9.1             | TIM Status and Control Register                |     |

| 14.9.2             | TIM Counter Registers                          |     |

| 14.9.3             | TIM Counter Modulo Registers                   |     |

| 14.9.4             | TIM Channel Status and Control Registers       |     |

| 14.9.5             | TIM Channel Registers                          |     |

|                    |                                                |     |

|                    | Chapter 15                                     |     |

| 45 4               | Development Support                            | 105 |

| 15.1               | Introduction                                   |     |

| 15.2               | Break Module (BRK)                             |     |

| 15.2.1<br>15.2.1.  | Functional Description                         |     |

| 15.2.1.<br>15.2.1. | 3                                              |     |

| 15.2.1.<br>15.2.1. | J i                                            |     |

| 15.2.1.<br>15.2.2  | 3 COP During Break Interrupts                  |     |

| 15.2.2.            | <b>y</b>                                       |     |

| 15.2.2.            | · · · · · · · · · · · · · · · · · · ·          |     |

| 15.2.2.            |                                                |     |

| 15.2.2.            | ·                                              |     |

| 15.2.2.            | · · · · · · · · · · · · · · · · · · ·          |     |

| 15.2.3             | Low-Power Modes                                |     |

|                    |                                                |     |

MC68HLC908QY/QT Family Data Sheet, Rev. 3

# Chapter 2 Memory

## 2.1 Introduction

The central processor unit (CPU08) can address 64 Kbytes of memory space. The memory map, shown in Figure 2-1, includes:

- 4096 bytes of user FLASH for MC68HLC908QT4 and MC68HLC908QY4

- 1536 bytes of user FLASH for MC68HLC908QT2, MC68HLC908QT1, MC68HLC908QY2, and MC68HLC908QY1

- 128 bytes of random access memory (RAM)

- 48 bytes of user-defined vectors, located in FLASH

- 416 bytes of monitor read-only memory (ROM)

- 1536 bytes of FLASH program and erase routines, located in ROM

# 2.2 Unimplemented Memory Locations

Accessing an unimplemented location can have unpredictable effects on MCU operation. In Figure 2-1 and in register figures in this document, unimplemented locations are shaded.

# 2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on MCU operation. In Figure 2-1 and in register figures in this document, reserved locations are marked with the word Reserved or with the letter R.

## Memory

| Addr.                 | Register Name                                              |                 | Bit 7     | 6                         | 5      | 4           | 3              | 2        | 1      | Bit 0      |

|-----------------------|------------------------------------------------------------|-----------------|-----------|---------------------------|--------|-------------|----------------|----------|--------|------------|

| \$0029                | TIM Channel 1<br>Register High (TCH1H)                     | Read:<br>Write: | Bit 15    | Bit 14                    | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8      |

|                       | See page 133.                                              | Reset:          |           | Indeterminate after reset |        |             |                |          |        |            |

| \$002A                | TIM Channel 1<br>Register Low (TCH1L)                      | Read:<br>Write: | Bit 7     | Bit 6                     | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0      |

|                       | See page 133.                                              | Reset:          |           |                           |        | Indetermina | te after reset |          | l      |            |

| \$002B<br>↓<br>\$0035 | Unimplemented                                              |                 |           |                           |        |             |                |          |        |            |

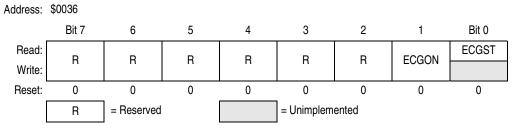

| \$0036                | Oscillator Status Register<br>(OSCSTAT)                    | Read:<br>Write: | R         | R                         | R      | R           | R              | R        | ECGON  | ECGST      |

|                       | See page 95.                                               | Reset:          | 0         | 0                         | 0      | 0           | 0              | 0        | 0      | 0          |

| \$0037                | Unimplemented                                              | Read:           |           |                           |        |             |                |          |        |            |

| \$0038                | Oscillator Trim Register<br>(OSCTRIM)<br>See page 96.      | Read:<br>Write: | TRIM7     | TRIM6                     | TRIM5  | TRIM4       | TRIM3          | TRIM2    | TRIM1  | TRIMO<br>0 |

| \$0039<br>↓<br>\$003B | Unimplemented                                              |                 |           |                           |        |             |                |          |        |            |

| \$003C                | ADC Status and Control<br>Register (ADSCR)<br>See page 43. | Read:<br>Write: | COCO<br>R | AIEN                      | ADCO   | CH4         | СНЗ            | CH2      | CH1    | СНО        |

|                       |                                                            | Reset:          | 0         | 0                         | 0      | 1           | 1              | 1        | 1      | 1          |

| \$003D                | Unimplemented                                              |                 |           |                           |        |             |                |          |        |            |

| \$003E                | ADC Data Register<br>(ADR)<br>See page 44.                 | Read:<br>Write: | Bit 7     | Bit 6                     | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0      |

|                       | See page 44.                                               | Reset:          |           | T                         | ı      |             | te after reset |          | ı      |            |

| \$003F                | ADC Input Clock Register (ADICLK)                          | Read:<br>Write: | ADIV2     | ADIV1                     | ADIV0  | 0           | 0              | 0        | 0      | 0          |

|                       | See page 45.                                               | Reset:          | 0         | 0                         | 0      | 0           | 0              | 0        | 0      | 0          |

|                       |                                                            |                 |           | = Unimplem                | nented | R           | = Reserved     | U = Unaf | fected |            |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 6)

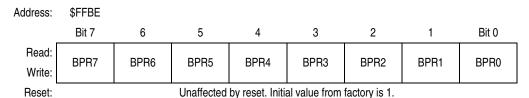

## 2.6.6 FLASH Block Protect Register

The FLASH block protect register is implemented as a byte within the FLASH memory, and therefore can only be written during a programming sequence of the FLASH memory. The value in this register determines the starting address of the protected range within the FLASH memory.

Write to this register is by a programming sequence to the FLASH memory.

Figure 2-5. FLASH Block Protect Register (FLBPR)

## BPR[7:0] — FLASH Protection Register Bits [7:0]

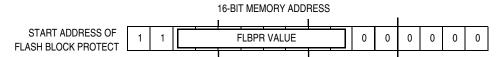

These eight bits in FLBPR represent bits [13:6] of a 16-bit memory address. Bits [15:14] are 1s and bits [5:0] are 0s.

The resultant 16-bit address is used for specifying the start address of the FLASH memory for block protection. The FLASH is protected from this start address to the end of FLASH memory, at \$FFFF. With this mechanism, the protect start address can be XX00, XX40, XX80, or XXC0 within the FLASH memory. See Figure 2-6 and Table 2-2.

Figure 2-6. FLASH Block Protect Start Address

Table 2-2. Examples of Protect Start Address

| BPR[7:0]                  | Start of Address of Protect Range                                                  |  |  |  |  |  |

|---------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| \$00-\$B8                 | The entire FLASH memory is protected.                                              |  |  |  |  |  |

| \$B9 ( <b>1011 1001</b> ) | \$EE40 (11 <b>10 1110 01</b> 00 0000)                                              |  |  |  |  |  |

| \$BA ( <b>1011 1010</b> ) | \$EE80 (11 <b>10 1110 10</b> 00 0000)                                              |  |  |  |  |  |

| \$BB ( <b>1011 1011</b> ) | \$EEC0 (11 <b>10 1110 11</b> 00 0000)                                              |  |  |  |  |  |

| \$BC ( <b>1011 1100</b> ) | \$EF00 (11 <b>10 1111 00</b> 00 0000)                                              |  |  |  |  |  |

|                           | and so on                                                                          |  |  |  |  |  |

| \$DE (1101 1110)          | \$F780 (11 <b>11 0111 10</b> 00 0000)                                              |  |  |  |  |  |

| \$DF (1101 1111)          | \$F7C0 (11 <b>11 0111 11</b> 00 0000)                                              |  |  |  |  |  |

| \$FE (1111 1110)          | \$FF80 (11 <b>11 1111 10</b> 00 0000)<br>FLBPR, OSCTRIM, and vectors are protected |  |  |  |  |  |

| \$FF                      | The entire FLASH memory is not protected.                                          |  |  |  |  |  |

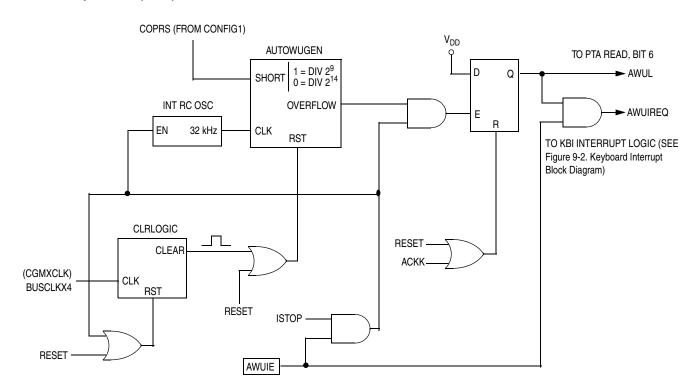

#### **Auto Wakeup Module (AWU)**

Figure 4-1. Auto Wakeup Interrupt Request Generation Logic

The overflow count can be selected from two options defined by the COPRS bit in CONFIG1. This bit was "borrowed" from the computer operating properly (COP) using the fact that the COP feature is idle (no MCU clock available) in stop mode. The typical values of the periodic wakeup request are (at room temperature):

- COPRS = 0: 875 ms @ 3.0 V, 1.1 s @ 2.3 V

- COPRS = 1: 22 ms @ 3.0 V, 27 ms @ 2.3 V

The auto wakeup RC oscillator is highly dependent on operating voltage and temperature. This feature is not recommended for use as a time-keeping function.

The wakeup request is latched to allow the interrupt source identification. The latched value, AWUL, can be read directly from the bit 6 position of PTA data register. This is a read-only bit which is occupying an empty bit position on PTA. No PTA associated registers, such as PTA6 data, PTA6 direction, and PTA6 pullup exist for this bit. The latch can be cleared by writing to the ACKK bit in the KBSCR register. Reset also clears the latch. AWUIE bit in KBI interrupt enable register (see Figure 4-1) has no effect on AWUL reading.

The AWU oscillator and counters are inactive in normal operating mode and become active only upon entering stop mode.

Auto Wakeup Module (AWU)

**Configuration Register (CONFIG)**

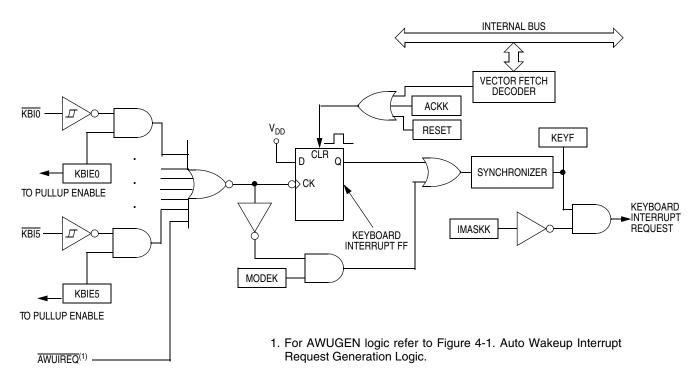

Figure 9-2. Keyboard Interrupt Block Diagram

If the MODEK bit is set, the keyboard interrupt inputs are both falling edge and low-level sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register (KBSCR). The ACKK bit is useful in applications that poll the keyboard interrupt inputs and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt inputs. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the central processor unit (CPU) loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt inputs to logic 1 As long as any enabled keyboard interrupt pin is at logic 0, the keyboard interrupt remains set. The auto wakeup interrupt input, AWUIREQ, will be cleared only by writing to ACKK bit in KBSCR or reset.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to logic 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt input stays at logic 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

#### Low-Voltage Inhibit (LVI)

The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit (LVIPWRD) enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit (LVIRSTD) enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,  $V_{TRIPF}$  or  $V_{DTRIPF}$ . Setting the LVI enable in stop mode bit (LVISTOP) enables the LVI to operate in stop mode. Setting the LVD or LVR trip point bit (LVDLVR) selects the LVD trip point voltage. The actual trip thresholds are specified in 16.5 DC Electrical Characteristics. Either trip level can be used as a detect or reset.

#### **NOTE**

After a power-on reset, the LVI's default mode of operation is LVR trip voltage. If a higher trip voltage is desired, the user must set the LVDLVR bit to raise the trip point to the LVD voltage.

If the user requires the higher trip voltage and sets the LVDLVR bit after power-on reset while the VDD supply is not above the  $V_{TRIPR}$  for LVD mode, the microcontroller unit (MCU) will immediately go into reset. The next time the LVI releases the reset, the supply will be above the  $V_{TRIPR}$  for LVD mode.

Once an LVI reset occurs, the MCU remains in reset until  $V_{DD}$  rises above a voltage,  $V_{TRIPR}$ , which causes the MCU to exit reset. See Chapter 13 System Integration Module (SIM) for the reset recovery sequence.

The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR) and can be used for polling LVI operation when the LVI reset is disabled.

## 10.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, the LVIPWRD bit must be cleared to enable the LVI module, and the LVIRSTD bit must be set to disable LVI resets.

### 10.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, the LVIPWRD and LVIRSTD bits must be cleared to enable the LVI module and to enable LVI resets.

### 10.3.3 Voltage Hysteresis Protection

Once the LVI has triggered (by having  $V_{DD}$  fall below  $V_{TRIPF}$ ), the LVI will maintain a reset condition until  $V_{DD}$  rises above the rising trip point voltage,  $V_{TRIPR}$ . This prevents a condition in which the MCU is continually entering and exiting reset if  $V_{DD}$  is approximately equal to  $V_{TRIPF}$ .  $V_{TRIPR}$  is greater than  $V_{TRIPF}$  by the hysteresis voltage,  $V_{HYS}$ .

## 10.3.4 LVI Trip Selection

The LVDLVR bit in the configuration register selects whether the LVI is configured for LVD (low voltage detect) or LVR (low voltage reset) protection. The LVD trip voltage can be used as a low voltage warning. The LVR trip voltage will commonly be configured as a reset condition since it is very close to the minimum operating voltage of the device. The LVDLVR bit can be written to anytime so that battery applications can make use of the LVI as both a warning indicator and to generate a system reset.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

Polling and forced reset operation modes can be combined to take full advantage of LVD and LVR trip voltages selection. LVD (LVDLVR = 1) in polling mode (LVIRSTD = 1) can be used as a low voltage warning in a slowly and continuously falling  $V_{DD}$  application (for example, battery applications). Once LVD has been identified, the part can be set to LVR (LVDLVR = 0) and reset enabled (LVIRSTD = 0). So, as  $V_{DD}$  continues to fall the part will reset when LVR trip voltage is reached. Unlike other bits in CONFIG registers, LVIRSTD and LVDLVR bits are allowed to be written multiple times after reset.

#### NOTE

The microcontroller is guaranteed to operate at a minimum supply voltage. The trip point ( $V_{TRIPF}$  [LVD] or  $V_{TRIPF}$  [LVR]) may be lower than this. See 16.5 DC Electrical Characteristics for the actual trip point voltages.

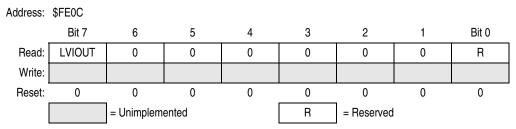

# 10.4 LVI Status Register

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level while LVI resets have been disabled.

Figure 10-2. LVI Status Register (LVISR)

### LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPR}$ . The difference in these threshold levels results in a hysteresis that prevents oscillation into and out of reset (see Table 10-1). Reset clears the LVIOUT bit.

| V <sub>DD</sub>                                           | LVIOUT         |

|-----------------------------------------------------------|----------------|

| V <sub>DD</sub> > V <sub>TRIPR</sub>                      | 0              |

| V <sub>DD</sub> < V <sub>TRIPF</sub>                      | 1              |

| V <sub>TRIPF</sub> < V <sub>DD</sub> < V <sub>TRIPR</sub> | Previous value |

Table 10-1. LVIOUT Bit Indication

# 10.5 LVI Interrupts

The LVI module does not generate interrupt requests.

# 11.6 Oscillator During Break Mode

The oscillator continues to drive BUSCLKX2 and BUSCLKX4 when the device enters the break state.

# 11.7 CONFIG2 Options

Two CONFIG2 register options affect the operation of the oscillator module: OSCOPT1 and OSCOPT0. All CONFIG2 register bits will have a default configuration. Refer to Chapter 5 Configuration Register (CONFIG) for more information on how the CONFIG2 register is used.

Table 11-2 shows how the OSCOPT bits are used to select the oscillator clock source.

| OSCOPT1 | OSCOPT0 | Oscillator Modes    |

|---------|---------|---------------------|

| 0       | 0       | Internal Oscillator |

| 0       | 1       | External Oscillator |

| 1       | 0       | External RC         |

| 1       | 1       | External Crystal    |

Table 11-2. Oscillator Modes

# 11.8 Input/Output (I/O) Registers

The oscillator module contains these two registers:

- 1. Oscillator status register (OSCSTAT)

- Oscillator trim register (OSCTRIM)

## 11.8.1 Oscillator Status Register

The oscillator status register (OSCSTAT) contains the bits for switching from internal to external clock sources.

Figure 11-4. Oscillator Status Register (OSCSTAT)

### ECGON — External Clock Generator On Bit

This read/write bit enables external clock generator, so that the switching process can be initiated. This bit is forced low during reset. This bit is ignored in monitor mode with the internal oscillator bypassed.

- 1 = External clock generator enabled

- 0 = External clock generator disabled

#### ECGST — External Clock Status Bit

This read-only bit indicates whether or not an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

MC68HLC908QY/QT Family Data Sheet, Rev. 3

#### **System Integration Module (SIM)**

The LDA opcode is prefetched by both the INT1 and INT2 return-from-interrupt (RTI) instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

#### NOTE

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

### 13.6.1.2 SWI Instruction

The SWI instruction is a non-maskable instruction that causes an interrupt regardless of the state of the interrupt mask (I bit) in the condition code register.

#### NOTE

A software interrupt pushes PC onto the stack. A software interrupt does **not** push PC – 1, as a hardware interrupt does.

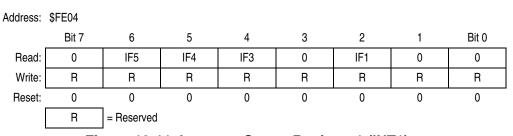

## 13.6.2 Interrupt Status Registers

The flags in the interrupt status registers identify maskable interrupt sources. Table 13-3 summarizes the interrupt sources and the interrupt status register flags that they set. The interrupt status registers can be useful for debugging.

**Table 13-3. Interrupt Sources**

| Priority | Source                            | Flag | Mask <sup>(1)</sup> | INT<br>Register<br>Flag | Vector<br>Address |

|----------|-----------------------------------|------|---------------------|-------------------------|-------------------|

| Highest  | Reset                             | _    | _                   | _                       | \$FFFE-\$FFFF     |

| <b>A</b> | SWI instruction                   | _    | _                   | _                       | \$FFFC-\$FFFD     |

|          | ĪRQ pin                           | IRQF | IMASK               | IF1                     | \$FFFA-\$FFFB     |

|          | Timer channel 0 interrupt         | CH0F | CH0IE               | IF3                     | \$FFF6-\$FFF7     |

|          | Timer channel 1 interrupt         | CH1F | CH1IE               | IF4                     | \$FFF4-\$FFF5     |

|          | Timer overflow interrupt          | TOF  | TOIE                | IF5                     | \$FFF2-\$FFF3     |

| <b>\</b> | Keyboard interrupt                | KEYF | IMASKK              | IF14                    | \$FFE0-\$FFE1     |

| Lowest   | ADC conversion complete interrupt | COCO | AIEN                | IF15                    | \$FFDE-\$FFDF     |

The I bit in the condition code register is a global mask for all interrupt sources except the SWI instruction.

### 13.6.2.1 Interrupt Status Register 1

Figure 13-11. Interrupt Status Register 1 (INT1)

MC68HLC908QY/QT Family Data Sheet, Rev. 3

#### **System Integration Module (SIM)**

state by forcing it to the SWI vector location. Refer to the break interrupt subsection of each module to see how each module is affected by the break state.

## 13.6.5 Status Flag Protection in Break Mode

The SIM controls whether status flags contained in other modules can be cleared during break mode. The user can select whether flags are protected from being cleared by properly initializing the break clear flag enable bit (BCFE) in the break flag control register (BFCR).

Protecting flags in break mode ensures that set flags will not be cleared while in break mode. This protection allows registers to be freely read and written during break mode without losing status flag information.

Setting the BCFE bit enables the clearing mechanisms. Once cleared in break mode, a flag remains cleared even when break mode is exited. Status flags with a two-step clearing mechanism — for example, a read of one register followed by the read or write of another — are protected, even when the first step is accomplished prior to entering break mode. Upon leaving break mode, execution of the second step will clear the flag as normal.

## 13.7 Low-Power Modes

Executing the WAIT or STOP instruction puts the MCU in a low power-consumption mode for standby situations. The SIM holds the CPU in a non-clocked state. The operation of each of these modes is described below. Both STOP and WAIT clear the interrupt mask (I) in the condition code register, allowing interrupts to occur.

#### 13.7.1 Wait Mode

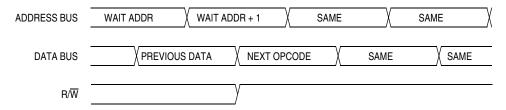

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

#### Figure 13-14. Wait Mode Entry Timing

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset (or break in emulation mode). A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the break status register (BSR). If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

**System Integration Module (SIM)**

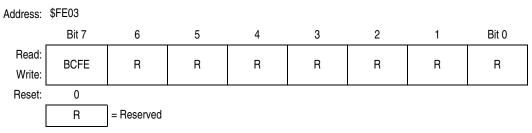

## 13.8.2 Break Flag Control Register

The break control register (BFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 13-20. Break Flag Control Register (BFCR)

## **BCFE** — Break Clear Flag Enable Bit

This read/write bit enables software to clear status bits by accessing status registers while the MCU is in a break state. To clear status bits during the break state, the BCFE bit must be set.

- 1 = Status bits clearable during break

- 0 = Status bits not clearable during break

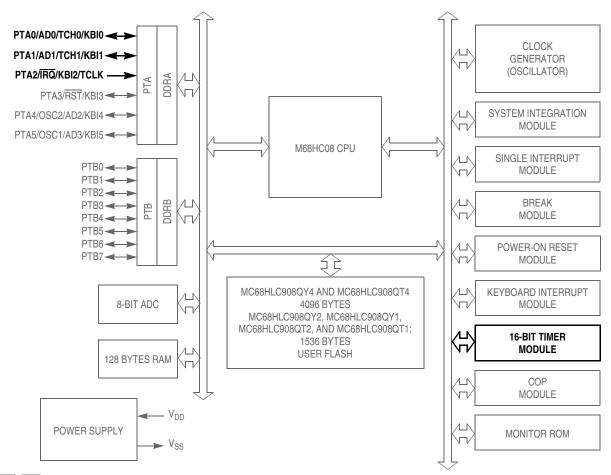

### **Timer Interface Module (TIM)**

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

$\label{eq:pta} \mbox{{\tt PTA[0:5]: Pins have programmable keyboard interrupt and pull up}} \\$

PTB[0:7]: Not available on 8-pin devices – MC68HLC908QT1, MC68HLC908QT2, and MC68HLC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HLC908QY1 and MC68HC9L08QT1

Figure 14-1. Block Diagram Highlighting TIM Block and Pins

MC68HLC908QY/QT Family Data Sheet, Rev. 3

**Timer Interface Module (TIM)**

## 14.6 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

# 14.7 TIM During Break Interrupts

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

# 14.8 Input/Output Signals

Port A shares three of its pins with the TIM. Two TIM channel I/O pins are PTA0/TCH0 and PTA1/TCH1 and an alternate clock source is PTA2/TCLK.

# 14.8.1 TIM Clock Pin (PTA2/TCLK)

PTA2/TCLK is an external clock input that can be the clock source for the TIM counter instead of the prescaled internal bus clock. Select the PTA2/TCLK input by writing 1s to the three prescaler select bits, PS[2–0]. (See 14.9.1 TIM Status and Control Register.) When the PTA2/TCLK pin is the TIM clock input, it is an input regardless of port pin initialization.

# 14.8.2 TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. PTA0/TCH0 can be configured as a buffered output compare or buffered PWM pin.

# 14.9 Input/Output Registers

The following I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

MC68HLC908QY/QT Family Data Sheet, Rev. 3

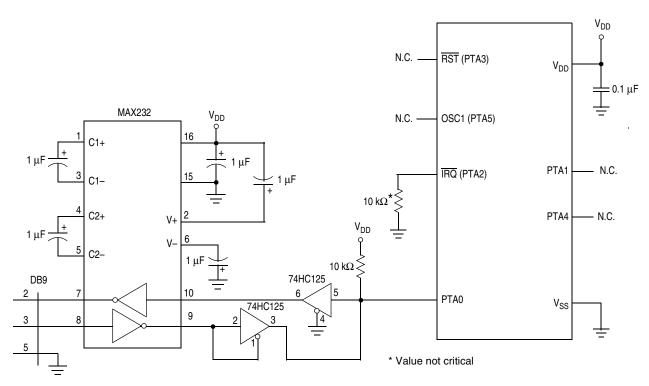

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 4800 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (1.0 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- IRQ = V<sub>SS</sub> (internal oscillator is selected, no external clock required)

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

# **Chapter 16 Electrical Specifications**

## 16.1 Introduction

This section contains electrical and timing specifications.

# **16.2 Absolute Maximum Ratings**

Maximum ratings are the extreme limits to which the microcontroller unit (MCU) can be exposed without permanently damaging it.

#### NOTE

This device is not guaranteed to operate properly at the maximum ratings. Refer to 16.5 DC Electrical Characteristics for guaranteed operating conditions.

| Characteristic <sup>(1)</sup>                                        | Symbol                               | Value                          | Unit |

|----------------------------------------------------------------------|--------------------------------------|--------------------------------|------|

| Supply voltage                                                       | V <sub>DD</sub>                      | -0.3 to +6.0                   | V    |

| Input voltage                                                        | V <sub>IN</sub>                      | $V_{SS}$ =0.3 to $V_{DD}$ +0.3 | V    |

| Mode entry voltage, IRQ pin                                          | V <sub>TST</sub>                     | V <sub>SS</sub> -0.3 to +9.1   | V    |

| Maximum current per pin excluding PTA0–PTA5, $V_{DD}$ , and $V_{SS}$ | I                                    | ±15                            | mA   |

| Maximum current for pins PTA0-PTA5                                   | I <sub>PTA0</sub> —I <sub>PTA5</sub> | ±25                            | mA   |

| Storage temperature                                                  | T <sub>STG</sub>                     | -55 to +150                    | °C   |

| Maximum current out of V <sub>SS</sub>                               | I <sub>MVSS</sub>                    | 100                            | mA   |

| Maximum current into V <sub>DD</sub>                                 | I <sub>MVDD</sub>                    | 100                            | mA   |

Voltages references to V<sub>SS</sub>.

#### NOTE

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum-rated voltages to this high-impedance circuit. For proper operation, it is recommended that  $V_{IN}$  and  $V_{OUT}$  be constrained to the range  $V_{SS} \leq (V_{IN} \text{ or } V_{OUT}) \leq V_{DD}$ . Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (for example, either  $V_{SS}$  or  $V_{DD}$ .)