Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | HC08                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 2MHz                                                                 |

| Connectivity               | -                                                                    |

| Peripherals                | LVD, POR, PWM                                                        |

| Number of I/O              | 5                                                                    |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 128 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                          |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                        |

| Supplier Device Package    | 8-SO                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcl908gt1dwe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Memory

| Addr.                 | Register Name                             |                 | Bit 7               | 6                   | 5     | 4           | 3          | 2     | 1     | Bit 0 |

|-----------------------|-------------------------------------------|-----------------|---------------------|---------------------|-------|-------------|------------|-------|-------|-------|

|                       | Break Status and Control                  | Read:           | BRKE                | BRKA                | 0     | 0           | 0          | 0     | 0     | 0     |

| \$FE0B                | Register (BRKSCR)                         | Write:          | DUVE                | DRNA                |       |             |            |       |       |       |

|                       | See page 138.                             | Reset:          | 0                   | 0                   | 0     | 0           | 0          | 0     | 0     | 0     |

|                       |                                           | Read:           | LVIOUT              | 0                   | 0     | 0           | 0          | 0     | 0     | R     |

| \$FE0C                | LVI Status Register (LVISR) See page 87.  | Write:          |                     |                     |       |             |            |       |       |       |

|                       | . •                                       | Reset:          | 0                   | 0                   | 0     | 0           | 0          | 0     | 0     | 0     |

| \$FE0D<br>↓<br>\$FE0F | Reserved for FLASH Test                   |                 | R                   | R                   | R     | R           | R          | R     | R     | R     |

|                       |                                           | ţ               |                     |                     |       |             |            |       |       |       |

| \$FFBE                | FLASH Block Protect<br>Register (FLBPR)   | Read:<br>Write: | BPR7                | BPR6                | BPR5  | BPR4        | BPR3       | BPR2  | BPR1  | BPR0  |

|                       | See page 37.                              | Reset:          | Unaffected by reset |                     |       |             |            |       |       |       |

| \$FFBF                | Reserved                                  |                 | R                   | R                   | R     | R           | R          | R     | R     | R     |

|                       |                                           | ·               |                     |                     | •     |             |            |       |       |       |

| \$FFC0                | Internal Oscillator Trim Value (Optional) | Read:<br>Write: | TRIM7               | TRIM6               | TRIM5 | TRIM4       | TRIM3      | TRIM2 | TRIM1 | TRIM0 |

|                       | (-1)                                      | Reset:          |                     | Unaffected by reset |       |             |            |       |       |       |

| \$FFC1                | Reserved                                  |                 | R                   | R                   | R     | R           | R          | R     | R     | R     |

|                       |                                           | Read:           |                     |                     | LO    | W BYTE OF F | DESET VECT | OP.   |       |       |

| \$FFFF                | COP Control Register (COPCTL)             | Write:          |                     |                     |       |             |            |       |       |       |

| ψιιιι                 | See page 59.                              | Reset:          |                     |                     |       |             |            |       |       |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 6 of 6)

= Reserved

U = Unaffected

= Unimplemented

MC68HLC908QY/QT Family Data Sheet, Rev. 3

#### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module.

- 1 = LVI module power disabled

- 0 = LVI module power enabled

#### LVDLVR — Low Voltage Detect or Low Voltage Reset Mode Bit

LVDLVR selects the trip voltage of the LVI module. LVD trip voltage can be used as a low voltage warning, while LVR will commonly be used as a reset condition. Unlike other CONFIG bits, LVDLVR can be written multiple times after reset.

- 1 = LVI trip voltage level set to LVD trip voltage

- 0 = LVI trip voltage level set to LVR trip voltage

#### NOTE

The LVDLVR bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 BUSCLKX4 cycles instead of a 4096 BUSCLKX4 cycle delay.

- 1 = Stop mode recovery after 32 BUSCLKX4 cycles

- 0 = Stop mode recovery after 4096 BUSCLKX4 cycles

#### NOTE

Exiting stop mode by an LVI reset will result in the long stop recovery.

The system stabilization time for power-on reset and long stop recovery (both 4096 BUSCLKX4 cycles) gives a delay longer than the LVI enable time for these startup scenarios. There is no period where the MCU is not protected from a low-power condition. However, when using the short stop recovery configuration option, the 32 BUSCLKX4 delay must be greater than the LVI's turn on time to avoid a period in startup where the LVI is not protecting the MCU.

#### STOP — STOP Instruction Enable Bit

STOP enables the STOP instruction.

- 1 = STOP instruction enabled

- 0 = STOP instruction treated as illegal opcode

#### **COPD** — **COP** Disable Bit

COPD disables the COP module.

- 1 = COP module disabled

- 0 = COP module enabled

**Central Processor Unit (CPU)**

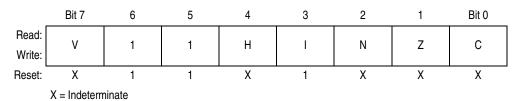

#### 7.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 7-6. Condition Code Register (CCR)

#### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

#### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

- 1 = Carry between bits 3 and 4

- 0 = No carry between bits 3 and 4

#### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

#### **NOTE**

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

#### Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

#### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

- 1 = Carry out of bit 7

- 0 = No carry out of bit 7

# 7.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

#### 7.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 7.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

#### 7.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 7.6 CPU During Break Interrupts

If a break module is present on the MCU, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD or with \$FEFC:\$FEFD in monitor mode

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

# Table 7-1. Instruction Set Summary (Sheet 6 of 6)

| Source                                                       | Operation                             | Description                                                                                                                                                                                                                                                                                                                                                                  |   |   |   | ec<br>CC |   |   | Address<br>Mode                       | Opcode                             |                | Cycles      |

|--------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|----------|---|---|---------------------------------------|------------------------------------|----------------|-------------|

| Form                                                         | Орегиноп                              | Description Description                                                                                                                                                                                                                                                                                                                                                      |   |   |   | N        | Z | С | Add                                   | Opc                                | odo<br>Obe     |             |

| SWI                                                          | Software Interrupt                    | $\begin{array}{c} PC \leftarrow (PC) + 1;  Push  (PCL) \\ SP \leftarrow (SP) - 1;  Push  (PCH) \\ SP \leftarrow (SP) - 1;  Push  (X) \\ SP \leftarrow (SP) - 1;  Push  (A) \\ SP \leftarrow (SP) - 1;  Push  (CCR) \\ SP \leftarrow (SP) - 1;  l \leftarrow 1 \\ PCH \leftarrow Interrupt  Vector  High  Byte \\ PCL \leftarrow Interrupt  Vector  Low  Byte \\ \end{array}$ | - | - | 1 | -        | _ | _ | INH                                   | 83                                 |                | 9           |

| TAP                                                          | Transfer A to CCR                     | CCR ← (A)                                                                                                                                                                                                                                                                                                                                                                    | 1 | 1 | 1 | 1        | 1 | 1 | INH                                   | 84                                 |                | 2           |

| TAX                                                          | Transfer A to X                       | $X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                                           | - | - | - | -        | - | - | INH                                   | 97                                 |                | 1           |

| TPA                                                          | Transfer CCR to A                     | $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                         | - | - | - | -        | - | - | INH                                   | 85                                 |                | 1           |

| TST opr<br>TSTA<br>TSTX<br>TST opr,X<br>TST ,X<br>TST opr,SP | Test for Negative or Zero             | (A) – \$00 or (X) – \$00 or (M) – \$00                                                                                                                                                                                                                                                                                                                                       | 0 | _ | ı | 1        | ‡ | ı | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1 | 3D<br>4D<br>5D<br>6D<br>7D<br>9E6D | dd<br>ff<br>ff | 3 1 1 3 2 4 |

| TSX                                                          | Transfer SP to H:X                    | H:X ← (SP) + 1                                                                                                                                                                                                                                                                                                                                                               | - | - | _ | -        | - | - | INH                                   | 95                                 |                | 2           |

| TXA                                                          | Transfer X to A                       | $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                                           | - | - | _ | _        | - | - | INH                                   | 9F                                 |                | 1           |

| TXS                                                          | Transfer H:X to SP                    | (SP) ← (H:X) – 1                                                                                                                                                                                                                                                                                                                                                             | - | - | _ | -        | _ | _ | INH                                   | 94                                 |                | 2           |

| WAIT                                                         | Enable Interrupts; Wait for Interrupt | I bit ← 0; Inhibit CPU clocking until interrupted                                                                                                                                                                                                                                                                                                                            | - | - | 0 | -        | - | - | INH                                   | 8F                                 |                | 1           |

| Α     | Accumulator                                                         | n               | Any bit                                     |

|-------|---------------------------------------------------------------------|-----------------|---------------------------------------------|

| С     | Carry/borrow bit                                                    | opr             | Operand (one or two bytes)                  |

| CCR   | Condition code register                                             | PC              | Program counter                             |

| dd    | Direct address of operand                                           | PCH             | Program counter high byte                   |

| dd rr | Direct address of operand and relative offset of branch instruction |                 | Program counter low byte                    |

| DD    | Direct to direct addressing mode                                    | REL             | Relative addressing mode                    |

| DIR   | Direct addressing mode                                              | rel             | Relative program counter offset byte        |

| DIX+  | Direct to indexed with post increment addressing mode               | rr              | Relative program counter offset byte        |

| ee ff | High and low bytes of offset in indexed, 16-bit offset addressing   | SP1             | Stack pointer, 8-bit offset addressing mode |

| EXT   | Extended addressing mode                                            | SP2             | Stack pointer 16-bit offset addressing mode |

| ff    | Offset byte in indexed, 8-bit offset addressing                     | SP              | Stack pointer                               |

| Н     | Half-carry bit                                                      | U               | Undefined                                   |

| Н     | Index register high byte                                            | V               | Overflow bit                                |

| hh II | High and low bytes of operand address in extended addressing        | Χ               | Index register low byte                     |

|       | Interrupt mask                                                      | Z               | Zero bit                                    |

| ii    | Immediate operand byte                                              | &               | Logical AND                                 |

| IMD   | Immediate source to direct destination addressing mode              |                 | Logical OR                                  |

| IMM   | Immediate addressing mode                                           | $\oplus$        | Logical EXCLUSIVE OR                        |

| INH   | Inherent addressing mode                                            | ()              | Contents of                                 |

| IX    | Indexed, no offset addressing mode                                  | <del>-</del> () | Negation (two's complement)                 |

| IX+   | Indexed, no offset, post increment addressing mode                  | #`              | Immediate value                             |

| IX+D  | Indexed with post increment to direct addressing mode               | **              | Sign extend                                 |

| IX1   | Indexed, 8-bit offset addressing mode                               | $\leftarrow$    | Loaded with                                 |

| IX1+  | Indexed, 8-bit offset, post increment addressing mode               | ?               | If                                          |

| IX2   | Indexed, 16-bit offset addressing mode                              | :               | Concatenated with                           |

| M     | Memory location                                                     | <b>‡</b>        | Set or cleared                              |

| N     | Negative bit                                                        | _               | Not affected                                |

# 7.8 Opcode Map

See Table 7-2.

# Chapter 9 Keyboard Interrupt Module (KBI)

#### 9.1 Introduction

The keyboard interrupt module (KBI) provides six independently maskable external interrupts, which are accessible via the PTA0–PTA5 pins.

#### 9.2 Features

Features of the keyboard interrupt module include:

- Six keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Software configurable pullup device if input pin is configured as input port bit

- Programmable edge-only or edge and level interrupt sensitivity

- Exit from low-power modes

## 9.3 Functional Description

The keyboard interrupt module controls the enabling/disabling of interrupt functions on the six port A pins. These six pins can be enabled/disabled independently of each other.

## 9.3.1 Keyboard Operation

Writing to the KBIE0–KBIE5 bits in the keyboard interrupt enable register (KBIER) independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin in port A also enables its internal pullup device irrespective of PTAPUEx bits in the port A input pullup enable register (see 12.2.3 Port A Input Pullup Enable Register). A logic 0 applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard interrupt inputs goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard interrupt input does

not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt

request on one input because another input is still low, software can disable the latter input while

it is low.

- If the keyboard interrupt is falling edge and low-level sensitive, an interrupt request is present as long as any keyboard interrupt input is low.

**Oscillator Module (OSC)**

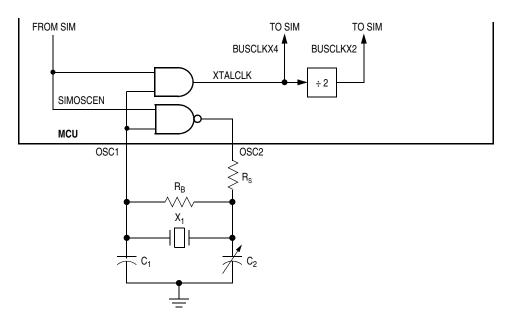

#### 11.3.3 XTAL Oscillator

The XTAL oscillator circuit is designed for use with an external low-frequency crystal or ceramic resonator to provide an accurate clock source. In this configuration, the OSC2 pin is dedicated to the external crystal circuit. The OSC2EN bit in the port A pullup enable register has no effect when this clock mode is selected.

In its typical configuration, the XTAL oscillator is connected in a Pierce oscillator configuration, as shown in Figure 11-2. This figure shows only the logical representation of the internal components and may not represent actual circuitry. The oscillator configuration uses five components:

- Crystal, X<sub>1</sub>

- Fixed capacitor, C<sub>1</sub>

- Tuning capacitor, C<sub>2</sub> (can also be a fixed capacitor)

- Feedback resistor, R<sub>B</sub>

- Series resistor, R<sub>s</sub>

Figure 11-2. XTAL Oscillator External Connections

#### 11.3.4 RC Oscillator

The RC oscillator circuit is designed for use with an external resistor ( $R_{EXT}$ ) to provide a clock source with a tolerance within 25% of the expected frequency. See Figure 11-3.

The capacitor (C) for the RC oscillator is internal to the MCU. The R<sub>EXT</sub> value must have a tolerance of 1% or less to minimize its effect on the frequency.

In this configuration, the OSC2 pin can be left in the reset state as PTA4. Or, the OSC2EN bit in the port A pullup enable register can be set to enable the OSC2 output function on the pin. Enabling the OSC2 output slightly increases the external RC oscillator frequency, f<sub>RCCLK</sub>.

**Oscillator Module (OSC)**

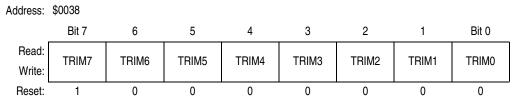

# 11.8.2 Oscillator Trim Register (OSCTRIM)

Figure 11-5. Oscillator Trim Register (OSCTRIM)

#### TRIM7-TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the size of the internal capacitor used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by approximately 0.2% of the untrimmed period (the period for TRIM = \$80). The trimmed frequency is guaranteed not to vary by more than  $\pm 5\%$  over the full specified range of temperature and voltage. The reset value is \$80, which sets the frequency to 4.0 MHz (1.0 MHz bus speed)  $\pm 25\%$ .

Input/Output Ports (PORTS)

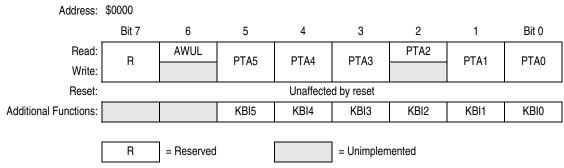

#### 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the six port A pins.

Figure 12-1. Port A Data Register (PTA)

#### PTA[5:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

#### AWUL — Auto Wakeup Latch Data Bit

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally (see Chapter 4 Auto Wakeup Module (AWU)). There is no PTA6 port nor any of the associated bits such as PTA6 data register, pullup enable or direction.

#### KBI[5:0] — Port A Keyboard Interrupts

The keyboard interrupt enable bits, KBIE5–KBIE0, in the keyboard interrupt control enable register (KBIER) enable the port A pins as external interrupt pins (see Chapter 9 Keyboard Interrupt Module (KBI)).

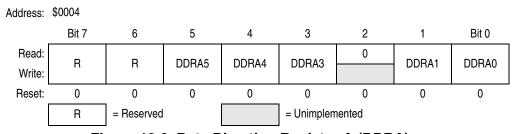

#### 12.2.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

Figure 12-2. Data Direction Register A (DDRA)

### DDRA[5:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[5:0], configuring all port A pins as inputs.

- 1 = Corresponding port A pin configured as output

- 0 = Corresponding port A pin configured as input

#### **NOTE**

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

#### 14.4.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use the following initialization procedure:

- 1. In the TIM status and control register (TSC):

- a. Stop the TIM counter by setting the TIM stop bit, TSTOP.

- b. Reset the TIM counter and prescaler by setting the TIM reset bit, TRST.

- 2. In the TIM counter modulo registers (TMODH:TMODL), write the value for the required PWM period.

- 3. In the TIM channel x registers (TCHxH:TCHxL), write the value for the required pulse width.

- 4. In TIM channel x status and control register (TSCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB:MSxA. See Table 14-3.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (polarity 1 to clear output on compare) or 1:1 (polarity 0 to set output on compare) to the edge/level select bits, ELSxB:ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 14-3.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIM status control register (TSC), clear the TIM stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIM channel 0 registers (TCH0H:TCH0L) initially control the buffered PWM output. TIM status control register 0 (TSCR0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIM overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 14.9.4 TIM Channel Status and Control Registers.

# 14.5 Interrupts

The following TIM sources can generate interrupt requests:

- TIM overflow flag (TOF) The TOF bit is set when the TIM counter reaches the modulo value programmed in the TIM counter modulo registers. The TIM overflow interrupt enable bit, TOIE, enables TIM overflow CPU interrupt requests. TOF and TOIE are in the TIM status and control register.

- TIM channel flags (CH1F:CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIM CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE. Channel x TIM CPU interrupt requests are enabled when CHxIE = 1. CHxF and CHxIE are in the TIM channel x status and control register.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

**Timer Interface Module (TIM)**

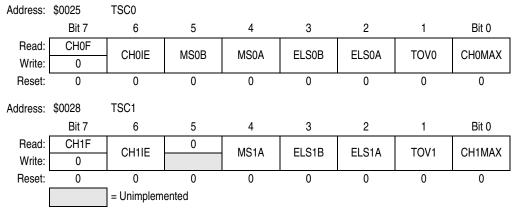

#### 14.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- · Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Figure 14-7. TIM Channel Status and Control Registers (TSC0:TSC1)

#### CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

Clear CHxF by reading the TIM channel x status and control register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing a 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

#### CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

#### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIM channel 0 status and control register.

Setting MS0B disables the channel 1 status and control register and reverts TCH1 to general-purpose I/O.

Reset clears the MSxB bit.

- 1 = Buffered output compare/PWM operation enabled

- 0 = Buffered output compare/PWM operation disabled

#### MSxA — Mode Select Bit A

When ELSxB:A  $\neq$  00, this read/write bit selects either input capture operation or unbuffered output compare/PWM operation.

See Table 14-3.

- 1 = Unbuffered output compare/PWM operation

- 0 = Input capture operation

When ELSxB:A = 00, this read/write bit selects the initial output level of the TCHx pin (see Table 14-3). Reset clears the MSxA bit.

- 1 = Initial output level low

- 0 = Initial output level high

#### NOTE

Before changing a channel function by writing to the MSxB or MSxA bit, set the TSTOP and TRST bits in the TIM status and control register (TSC).

| MSxB | MSxA | ELSxB | ELSxA | Mode            | Configuration                                     |

|------|------|-------|-------|-----------------|---------------------------------------------------|

| Х    | 0    | 0     | 0     | Output procet   | Pin under port control; initial output level high |

| Х    | 1    | 0     | 0     | Output preset   | Pin under port control; initial output level low  |

| 0    | 0    | 0     | 1     |                 | Capture on rising edge only                       |

| 0    | 0    | 1     | 0     | Input capture   | Capture on falling edge only                      |

| 0    | 0    | 1     | 1     |                 | Capture on rising or falling edge                 |

| 0    | 1    | 0     | 0     |                 | Software compare only                             |

| 0    | 1    | 0     | 1     | Output compare  | Toggle output on compare                          |

| 0    | 1    | 1     | 0     | or PWM          | Clear output on compare                           |

| 0    | 1    | 1     | 1     |                 | Set output on compare                             |

| 1    | Х    | 0     | 1     | Buffered output | Toggle output on compare                          |

| 1    | Х    | 1     | 0     | compare or      | Clear output on compare                           |

| 1    | Х    | 1     | 1     | buffered PWM    | Set output on compare                             |

Table 14-3. Mode, Edge, and Level Selection

#### ELSxB and ELSxA — Edge/Level Select Bits

When channel x is an input capture channel, these read/write bits control the active edge-sensing logic on channel x.

When channel x is an output compare channel, ELSxB and ELSxA control the channel x output behavior when an output compare occurs.

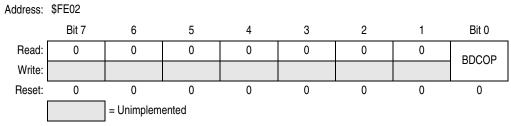

#### 15.2.2.3 Break Auxiliary Register

The break auxiliary register (BRKAR) contains a bit that enables software to disable the COP while the MCU is in a state of break interrupt with monitor mode.

Figure 15-6. Break Auxiliary Register (BRKAR)

#### BDCOP — Break Disable COP Bit

This read/write bit disables the COP during a break interrupt. Reset clears the BDCOP bit.

- 1 = COP disabled during break interrupt

- 0 = COP enabled during break interrupt.

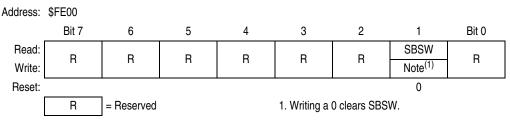

#### 15.2.2.4 Break Status Register

The break status register (BSR) contains a flag to indicate that a break caused an exit from wait mode. This register is only used in emulation mode.

Figure 15-7. Break Status Register (BSR)

#### SBSW — SIM Break Stop/Wait

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

- 1 = Wait mode was exited by break interrupt

- 0 = Wait mode was not exited by break interrupt

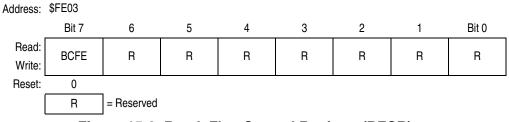

#### 15.2.2.5 Break Flag Control Register

The break control register (BFCR) contains a bit that enables software to clear status bits while the MCU is in a break state.

Figure 15-8. Break Flag Control Register (BFCR)

MC68HLC908QY/QT Family Data Sheet, Rev. 3

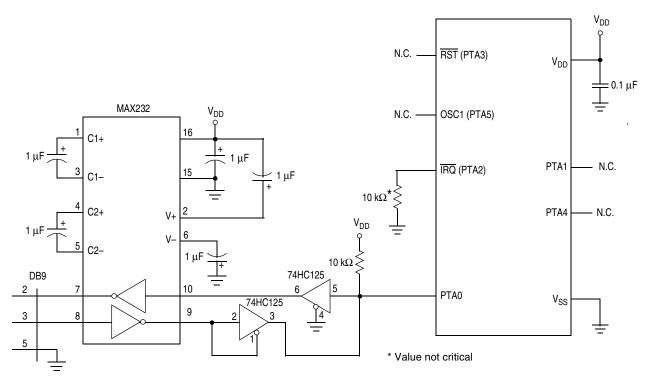

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 4800 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (1.0 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- IRQ = V<sub>SS</sub> (internal oscillator is selected, no external clock required)

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

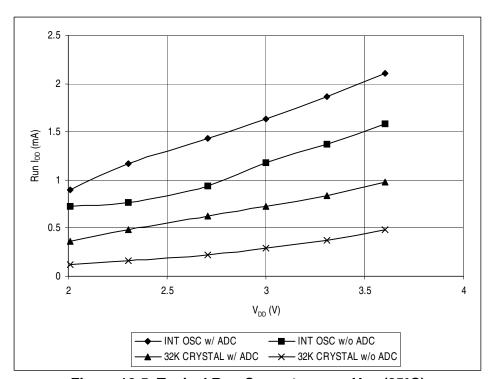

# 16.9 Supply Current Characteristics

| Characteristic                                                                                                                                                 | Voltage    | Bus Freq.<br>(MHz) | Symbol             | Тур                                  | Max                 | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|--------------------|--------------------------------------|---------------------|------|

| Run mode V <sub>DD</sub> supply current <sup>(1)</sup>                                                                                                         | 3.0<br>2.2 | 1<br>1             | RI <sub>DD</sub>   | 1.5<br>1.0                           | 2.5<br>1.5          | mA   |

| WAIT mode V <sub>DD</sub> supply current <sup>(2)</sup>                                                                                                        | 3.0<br>2.2 | 1<br>1             | WI <sub>DD</sub>   | 1.2<br>1.0                           | 2.0<br>1.0          | mA   |

| Stop mode V <sub>DD</sub> supply current <sup>(3)</sup> 25°C 0 to 70°C -40 to 85°C 25°C with auto wake-up enabled Incremental current with LVI enabled at 25°C | 3.0        |                    | SI.                | 0.006<br>0.08<br>0.12<br>5.70<br>110 |                     | μΑ   |

| 25°C 0 to 70°C -40 to 85°C 25°C with auto wake-up enabled Incremental current with LVI enabled at 25°C                                                         | 2.2        |                    | - SI <sub>DD</sub> | 0.005<br>0.08<br>0.12<br>1.30<br>100 | <br><br>1.0<br><br> | μΑ   |

- 1. Run (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules except ADC enabled.

- 2. Wait (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules except ADC enabled.

- 3. Stop I<sub>DD</sub> measured with all ports driven 0.2 V or less from rail. No dc loads. On the 8-pin versions, port B is configured as inputs with pullups enabled.

Figure 16-5. Typical Run Current versus  $V_{DD}$  (25°C) ( $f_{Bus}$  = 1 MHz for Internal Oscillator,  $f_{Bus}$  = 8 kHz for Crystal Oscillator)

MC68HLC908QY/QT Family Data Sheet, Rev. 3

**Electrical Specifications**

#### NOTES:

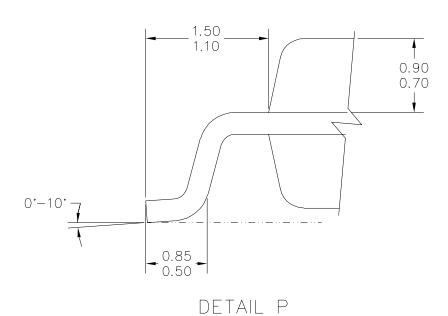

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M 1994.

- 2. ALL DIMENSIONS ARE IN INCHES.

- 3. 626-03 TO 626-06 OBSOLETE. NEW STANDARD 626-07.

- A DIMENSION TO CENTER OF LEAD WHEN FORMED PARALLEL.

- A PACKAGE CONTOUR OPTIONAL (ROUND OR SQUARE CONERS).

#### STYLE 1:

PIN 1. AC IN 5. GROUND 2. DC + IN 6. OUTPUT 3. DC - IN 7. AUXILIARY

4. AC IN 8. VCC

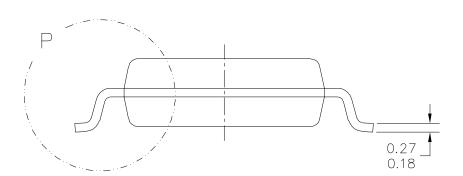

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ASB42420B   | REV: N      |

| 8 LD PDIP                                            |           | CASE NUMBER  | R: 626–06        | 19 MAY 2005 |

|                                                      |           | STANDARD: NO | NIFDFC           |             |

FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED 'CONTROLLED COPY' IN RED.

| MECHANICAL | DUTLINES |

|------------|----------|

| חורדותו    | JARY     |

| $D\Box$ | $N\Box T$ | SCALE | THIS | DRAWING |

|---------|-----------|-------|------|---------|

|         |           |       |      |         |

| DOCUMENT | N□: | 98ASH70107A |

|----------|-----|-------------|

| PAGE:    |     | 968         |

| REV:     |     | А           |

| TITLE:     | CASE NUMBER: 968-02              |

|------------|----------------------------------|

| 8 LEAD MFP | STANDARD: EIAJ                   |

|            | PACKAGE CODE: 6003 SHEET: 2 OF 4 |

Semiconductor

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.

ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED

DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY, PRINTED

VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED

COPY" IN RED.

# MECHANICAL OUTLINES DICTIONARY

DOCUMENT NO: 98ASH70107A

PAGE: 968

REV: A

DO NOT SCALE THIS DRAWING

#### NOTES:

- 1. DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEDD 0.15mm PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION.

DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46mm.

TITLE:

8 LEAD MFP

STANDARD: E1AJ

PACKAGE CODE: 6003 SHEET: 3 OF 4

# MECHANICAL OUTLINES DICTIONARY

DOCUMENT NO: 98ASB42567B

PAGE: 751G

DO NOT SCALE THIS DRAWING

REV: E

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE INTER—LEAD FLASH OR PROTRUSIONS. INTER—LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

TITLE:

16LD SOIC W/B, 1.27 PITCH, CASE OUTLINE

CASE NUMBER: 751G-05

STANDARD: JEDEC MS-013AA

PACKAGE CODE: 2003 | SHEET: 2 OF 3