Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 2MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 13                                                                    |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                           |

| Data Converters            | A/D 4x8b                                                              |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 16-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcl908qy2cdwe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Revision History**

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History**

| Date             | Revision<br>Level                                                                                | Description                                                                                                                                                                                                        | Page<br>Number(s) |

|------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| August,<br>2003  | N/A                                                                                              | Initial release                                                                                                                                                                                                    | N/A               |

|                  |                                                                                                  | Figure 2-2. Control, Status, and Data Registers Deleted unimplemented areas from \$FFB0-\$FFBD and \$FFC2-\$FFCF as they are actually available. Also corrected \$FFBF designation from unimplemented to reserved. | 26                |

|                  |                                                                                                  | Figure 6-1. COP Block Diagram — Reworked for clarity                                                                                                                                                               | 57                |

| October,         |                                                                                                  | 6.3.2 STOP Instruction — Added subsection for STOP instruction                                                                                                                                                     | 58                |

| 2003             | 1.0                                                                                              | 13.4.2 Active Resets from Internal Sources — Reworked notes for clarity.                                                                                                                                           | 115               |

|                  |                                                                                                  | 15.3 Monitor Module (MON) — Clarified seventh bullet.                                                                                                                                                              | 154               |

|                  |                                                                                                  | 16.5 DC Electrical Characteristics — Corrected notes 4 and 5.                                                                                                                                                      | 169               |

|                  |                                                                                                  | 16.6 Control Timing — Updated values for $\overline{\text{RST}}$ input pulse width low and $\overline{\text{IRQ}}$ interrupt pulse width low                                                                       | 170               |

| January,<br>2004 | FLASH Block Protect Register at address location \$FFBE and the Oscillator Trim Value at \$FFC0. | Figure 2-2. Control, Status, and Data Registers — Corrected reset state for the FLASH Block Protect Register at address location \$FFBE and the Internal Oscillator Trim Value at \$FFC0.                          | 30                |

| 2004             |                                                                                                  | Figure 2-5. FLASH Block Protect Register (FLBPR) — Restated reset state for clarity.                                                                                                                               | 37                |

|                  |                                                                                                  | Reformatted to meet current documentation standards                                                                                                                                                                | Throughout        |

| July,            | 3.0                                                                                              | Chapter 7 Central Processor Unit (CPU) — In 7.7 Instruction Set Summary: Reworked definitions for STOP instruction Added WAIT instruction                                                                          | 70<br>71          |

| 2005             | 0.0                                                                                              | 13.8.1 SIM Reset Status Register — Clarified SRSR flag setting.                                                                                                                                                    | 117               |

|                  |                                                                                                  | 14.9.1 TIM Status and Control Register — Added information to TSTOP note.                                                                                                                                          | 127               |

|                  |                                                                                                  | 17.3 Package Dimensions — Updated package information.                                                                                                                                                             | 163               |

**List of Chapters**

| 15.3             | Monitor Module (MON)                                                                                            | 140 |

|------------------|-----------------------------------------------------------------------------------------------------------------|-----|

| 15.3.1           | Functional Description                                                                                          | 140 |

| 15.3.1           | .1 Normal Monitor Mode                                                                                          | 144 |

| 15.3.1           |                                                                                                                 |     |

| 15.3.1           |                                                                                                                 |     |

| 15.3.1           |                                                                                                                 |     |

| 15.3.1           |                                                                                                                 |     |

| 15.3.1           |                                                                                                                 |     |

| 15.3.1<br>15.3.2 |                                                                                                                 |     |

| 15.3.2           | Security                                                                                                        | 150 |

|                  | Chapter 16                                                                                                      |     |

|                  | Electrical Specifications                                                                                       |     |

| 16.1             | Introduction                                                                                                    | 151 |

| 16.2             | Absolute Maximum Ratings                                                                                        | 151 |

| 16.3             | Functional Operating Range                                                                                      | 152 |

| 16.4             | Thermal Characteristics                                                                                         |     |

| 16.5             | DC Electrical Characteristics                                                                                   | 153 |

| 16.6             | Control Timing                                                                                                  | 154 |

| 16.7             | Typical 3.0-V Output Drive Characteristics                                                                      | 155 |

| 16.8             | Oscillator Characteristics                                                                                      |     |

| 16.9             | Supply Current Characteristics                                                                                  |     |

| 16.10            | Analog-to-Digital (ADC) Converter Characteristics                                                               |     |

| 16.10.           |                                                                                                                 |     |

| 16.10.           | i variable de la companya de la comp |     |

| 16.11            | Timer Interface Module Characteristics                                                                          | 160 |

| 16.12            | Memory Characteristics                                                                                          | 161 |

|                  |                                                                                                                 |     |

|                  | Chapter 17                                                                                                      |     |

|                  | Ordering Information and Mechanical Specifications                                                              |     |

| 17.1             | Introduction                                                                                                    |     |

| 17.2             | MC Order Numbers                                                                                                | 163 |

| 17.3             | Package Dimensions                                                                                              | 163 |

#### Memory

| Addr.                 | Register Name                                              |                           | Bit 7           | 6      | 5      | 4           | 3              | 2        | 1      | Bit 0 |

|-----------------------|------------------------------------------------------------|---------------------------|-----------------|--------|--------|-------------|----------------|----------|--------|-------|

| \$0029                | TIM Channel 1<br>Register High (TCH1H)                     | Read:<br>Write:           | Bit 15          | Bit 14 | Bit 13 | Bit 12      | Bit 11         | Bit 10   | Bit 9  | Bit 8 |

|                       | See page 133.                                              | Reset:                    |                 |        |        | Indetermina | te after reset |          |        |       |

| \$002A                | TIM Channel 1<br>Register Low (TCH1L)                      | Read:<br>Write:           | Bit 7           | Bit 6  | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0 |

|                       | See page 133.                                              | Reset:                    |                 |        | l      | Indetermina | te after reset |          | I.     |       |

| \$002B<br>↓<br>\$0035 | Unimplemented                                              |                           |                 |        |        |             |                |          |        |       |

| \$0036                | Oscillator Status Register<br>(OSCSTAT)                    | Read:<br>Write:           | R               | R      | R      | R           | R              | R        | ECGON  | ECGST |

|                       | See page 95.                                               | Reset:                    | 0               | 0      | 0      | 0           | 0              | 0        | 0      | 0     |

| \$0037                | Unimplemented                                              | Read:                     |                 |        |        |             |                |          |        |       |

| \$0038                | Oscillator Trim Register<br>(OSCTRIM)<br>See page 96.      | Read:<br>Write:           | TRIM7           | TRIM6  | TRIM5  | TRIM4       | TRIM3          | TRIM2    | TRIM1  | TRIM0 |

| \$0039<br>↓<br>\$003B | Unimplemented                                              |                           |                 |        |        |             |                |          |        |       |

| \$003C                | ADC Status and Control<br>Register (ADSCR)<br>See page 43. | Read:<br>Write:           | COCO<br>R       | - AIEN | ADCO   | CH4         | СНЗ            | CH2      | CH1    | CH0   |

|                       |                                                            | Reset:                    | 0               | 0      | 0      | 1           | 1              | 1        | 1      | 1     |

| \$003D                | Unimplemented                                              |                           |                 |        |        |             |                |          |        |       |

| \$003E                | ADC Data Register<br>(ADR)<br>See page 44.                 | Read:<br>Write:<br>Reset: | Bit 7           | Bit 6  | Bit 5  | Bit 4       | Bit 3          | Bit 2    | Bit 1  | Bit 0 |

|                       | See page 44.                                               |                           |                 | 1      | 1      | Indetermina | te after reset |          | T      |       |

| \$003F                | ADC Input Clock Register<br>(ADICLK)                       | Read:<br>Write:           | ADIV2           | ADIV1  | ADIV0  | 0           | 0              | 0        | 0      | 0     |

|                       | See page 45.                                               | Reset:                    | 0               | 0      | 0      | 0           | 0              | 0        | 0      | 0     |

|                       |                                                            |                           | = Unimplemented |        |        | R           | = Reserved     | U = Unaf | fected |       |

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 6)

#### Memory

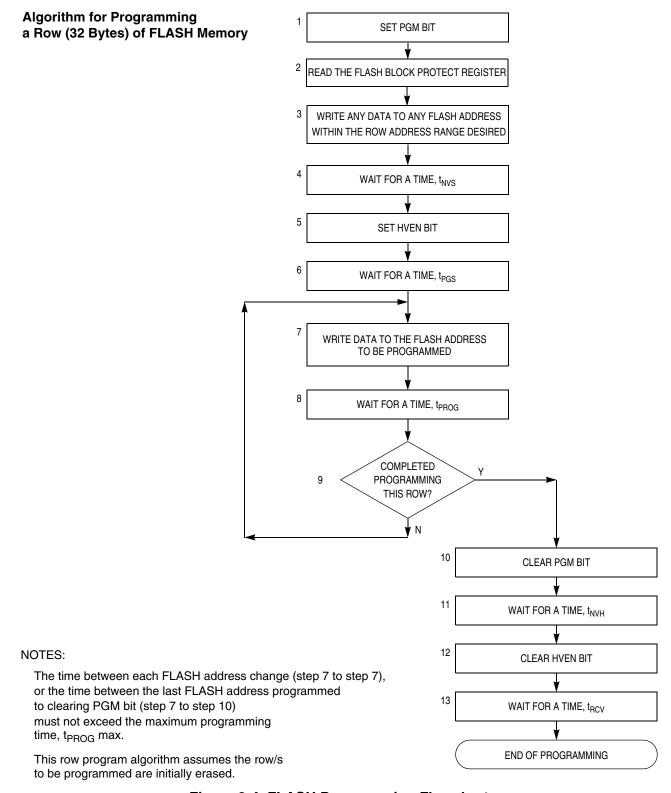

Figure 2-4. FLASH Programming Flowchart

# **Chapter 5 Configuration Register (CONFIG)**

#### 5.1 Introduction

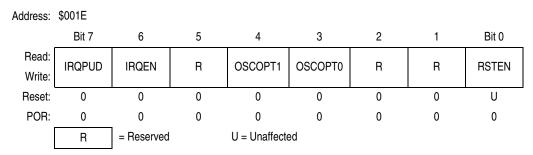

This section describes the configuration registers (CONFIG1 and CONFIG2). The configuration registers enable or disable the following options:

- Stop mode recovery time (32 × BUSCLKX4 cycles or 4096 × BUSCLKX4 cycles)

- STOP instruction

- Computer operating properly module (COP)

- COP reset period (COPRS): 8176 × BUSCLKX4 or 262,128 × BUSCLKX4

- Low-voltage inhibit (LVI) enable and trip voltage selection

- OSC option selection

- ĪRQ pin

- RST pin

- Auto wakeup timeout period

## 5.2 Functional Description

The configuration registers are used in the initialization of various options. The configuration registers can be written once after each reset. Exceptions are bits LVDLVR and LVIRSTD which may be written at any time. Most of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU) it is recommended that this register be written immediately after reset. The configuration registers are located at \$001E and \$001F, and may be read at anytime.

Figure 5-1. Configuration Register 2 (CONFIG2)

**Computer Operating Properly (COP)**

#### Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

#### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

- 1 = Carry out of bit 7

- 0 = No carry out of bit 7

## 7.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

#### 7.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 7.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

#### 7.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 7.6 CPU During Break Interrupts

If a break module is present on the MCU, the CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD or with \$FEFC:\$FEFD in monitor mode

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

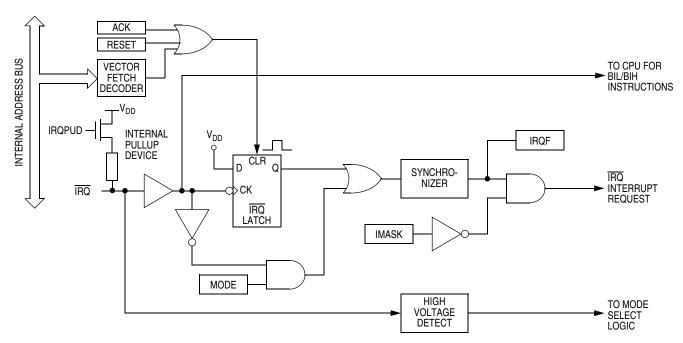

Figure 8-2. IRQ Module Block Diagram

#### 8.3.1 MODE = 1

If the MODE bit is set, the  $\overline{IRQ}$  pin is both falling edge sensitive and low level sensitive. With MODE set, both of the following actions must occur to clear the  $\overline{IRQ}$  interrupt request:

- Return of the IRQ pin to a high level. As long as the IRQ pin is low, the IRQ request remains active.

- IRQ vector fetch or software clear. An IRQ vector fetch generates an interrupt acknowledge signal to clear the IRQ latch. Software generates the interrupt acknowledge signal by writing a 1 to ACK in INTSCR. The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to ACK prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to ACK latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the IRQ vector address.

The IRQ vector fetch or software clear and the return of the  $\overline{\text{IRQ}}$  pin to a high level may occur in any order. The interrupt request remains pending as long as the  $\overline{\text{IRQ}}$  pin is low. A reset will clear the IRQ latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

Use the BIH or BIL instruction to read the logic level on the IRQ pin.

#### 8.3.2 MODE = 0

If the MODE bit is clear, the  $\overline{IRQ}$  pin is falling edge sensitive only. With MODE clear, an IRQ vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in INTSCR can be read to check for pending interrupts. The IRQF bit is not affected by IMASK, which makes it useful in applications where polling is preferred.

#### NOTE

When using the level-sensitive interrupt trigger, avoid false IRQ interrupts by masking interrupt requests in the interrupt routine.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

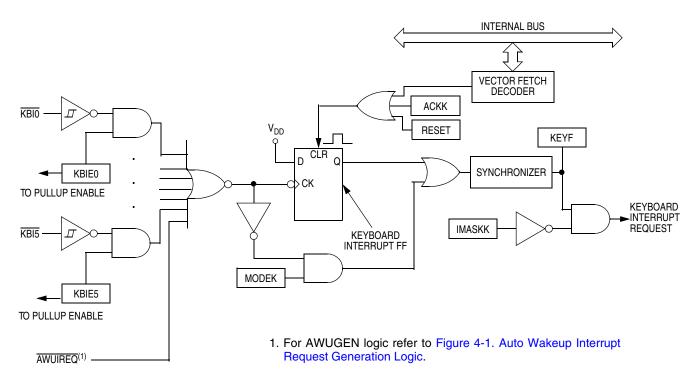

Figure 9-2. Keyboard Interrupt Block Diagram

If the MODEK bit is set, the keyboard interrupt inputs are both falling edge and low-level sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a 1 to the ACKK bit in the keyboard status and control register (KBSCR). The ACKK bit is useful in applications that poll the keyboard interrupt inputs and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt inputs. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the central processor unit (CPU) loads the program counter with the vector address at locations \$FFE0 and \$FFE1.

- Return of all enabled keyboard interrupt inputs to logic 1 As long as any enabled keyboard interrupt pin is at logic 0, the keyboard interrupt remains set. The auto wakeup interrupt input, AWUIREQ, will be cleared only by writing to ACKK bit in KBSCR or reset.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to logic 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge sensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt input stays at logic 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

Input/Output Ports (PORTS)

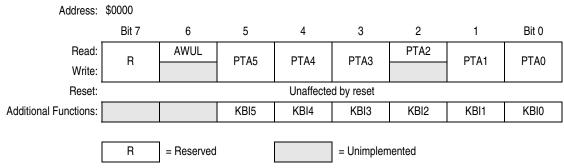

#### 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the six port A pins.

Figure 12-1. Port A Data Register (PTA)

#### PTA[5:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

#### AWUL — Auto Wakeup Latch Data Bit

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally (see Chapter 4 Auto Wakeup Module (AWU)). There is no PTA6 port nor any of the associated bits such as PTA6 data register, pullup enable or direction.

#### KBI[5:0] — Port A Keyboard Interrupts

The keyboard interrupt enable bits, KBIE5–KBIE0, in the keyboard interrupt control enable register (KBIER) enable the port A pins as external interrupt pins (see Chapter 9 Keyboard Interrupt Module (KBI)).

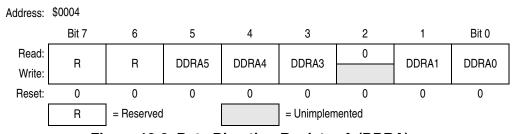

#### 12.2.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

Figure 12-2. Data Direction Register A (DDRA)

#### DDRA[5:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[5:0], configuring all port A pins as inputs.

- 1 = Corresponding port A pin configured as output

- 0 = Corresponding port A pin configured as input

#### **NOTE**

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

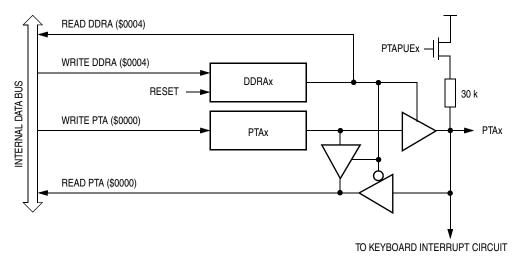

Figure 12-3 shows the port A I/O logic.

Figure 12-3. Port A I/O Circuit

#### NOTE

Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

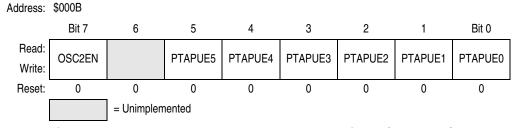

#### 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each if the six port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

Figure 12-4. Port A Input Pullup Enable Register (PTAPUE)

#### OSC2EN — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

- 1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

- 0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

MC68HLC908QY/QT Family Data Sheet, Rev. 3

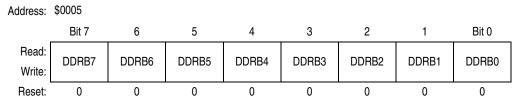

#### 12.3.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a 0 disables the output buffer.

Figure 12-6. Data Direction Register B (DDRB)

#### DDRB[7:0] — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB[7:0], configuring all port B pins as inputs.

- 1 = Corresponding port B pin configured as output

- 0 = Corresponding port B pin configured as input

#### NOTE

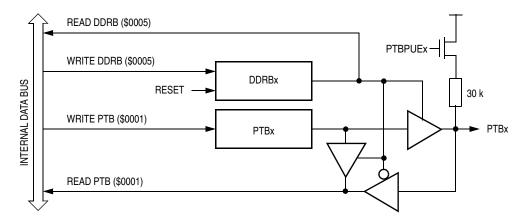

Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1. Figure 12-7 shows the port B I/O logic.

Figure 12-7. Port B I/O Circuit

When DDRBx is a 1, reading address \$0001 reads the PTBx data latch. When DDRBx is a 0, reading address \$0001 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-2 summarizes the operation of the port B pins.

Table 12-2. Port B Pin Functions

| DDRB | PTB              | I/O Pin                    | Accesses to DDRB | A   | ccesses to PTB           |

|------|------------------|----------------------------|------------------|-----|--------------------------|

| Bit  | t Bit Mode       |                            | Mode Read/Write  |     | Write                    |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRB7-DDRB0      | Pin | PTB7-PTB0 <sup>(3)</sup> |

| 1    | Х                | Output                     | DDRB7-DDRB0      | Pin | PTB7-PTB0                |

- 1. X = don't care

- 2. Hi-Z = high impedance

- 3. Writing affects data register, but does not affect the input.

#### MC68HLC908QY/QT Family Data Sheet, Rev. 3

#### IF1 and IF3-IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 0, 1, 3, and 7 — Always read 0

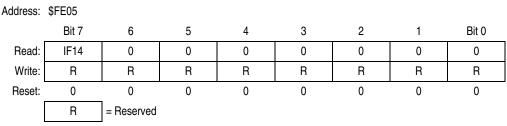

#### 13.6.2.2 Interrupt Status Register 2

Figure 13-12. Interrupt Status Register 2 (INT2)

#### IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 0-6 — Always read 0

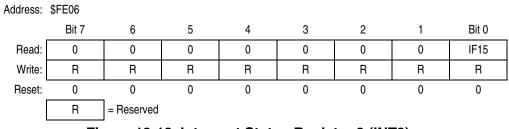

#### 13.6.2.3 Interrupt Status Register 3

Figure 13-13. Interrupt Status Register 3 (INT3)

#### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 1-7 — Always read 0

#### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

#### 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break

MC68HLC908QY/QT Family Data Sheet, Rev. 3

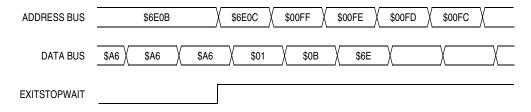

Figure 13-15 and Figure 13-16 show the timing for wait recovery.

NOTE: EXITSTOPWAIT =  $\overline{RST}$  pin OR CPU interrupt

Figure 13-15. Wait Recovery from Interrupt

1. RST is only available if the RSTEN bit in the CONFIG1 register is set.

Figure 13-16. Wait Recovery from Internal Reset

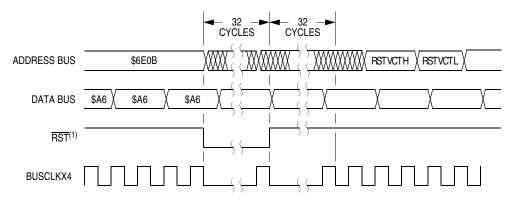

#### **13.7.2 Stop Mode**

In stop mode, the SIM counter is reset and the system clocks are disabled. An interrupt request from a module can cause an exit from stop mode. Stacking for interrupts begins after the selected stop recovery time has elapsed. Reset or break also causes an exit from stop mode.

The SIM disables the oscillator signals (BUSCLKX2 and BUSCLKX4) in stop mode, stopping the CPU and peripherals. Stop recovery time is selectable using the SSREC bit in the configuration register 1 (CONFIG1). If SSREC is set, stop recovery is reduced from the normal delay of 4096 BUSCLKX4 cycles down to 32. This is ideal for the internal oscillator, RC oscillator, and external oscillator options which do not require long start-up times from stop mode.

#### NOTE

External crystal applications should use the full stop recovery time by clearing the SSREC bit.

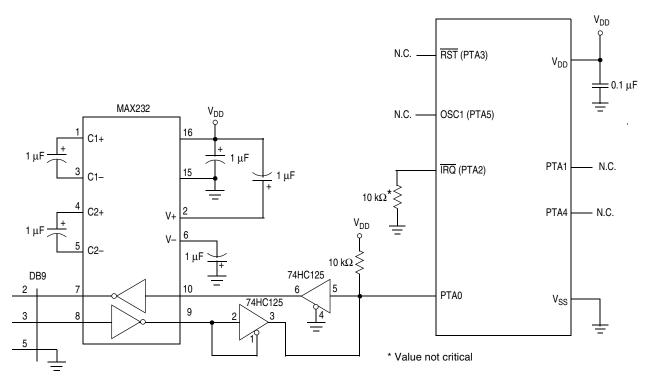

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 4800 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (1.0 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{TST}$

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- $\overline{IRQ} = V_{DD}$  (this can be implemented through the internal  $\overline{IRQ}$  pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- IRQ = V<sub>SS</sub> (internal oscillator is selected, no external clock required)

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

#### **Electrical Specifications**

# 16.3 Functional Operating Range

| Characteristic                                                                                            | Symbol          | Value                    | Unit | Temp<br>Code |

|-----------------------------------------------------------------------------------------------------------|-----------------|--------------------------|------|--------------|

| Operating temperature range (T <sub>L</sub> to T <sub>H</sub> )                                           | T <sub>A</sub>  | -40 to 85<br>0 to 70     | °C   | 0            |

| Operating voltage range <sup>(1)</sup> (V <sub>DDMIN</sub> to V <sub>DDMAX</sub> )  -40 to 85°C 0 to 70°C | V <sub>DD</sub> | 2.4 to 3.6<br>2.2 to 3.6 | V    | C<br>_       |

<sup>1.</sup>  $V_{DD}$  must be above  $V_{TRIPR}$  upon power on.

### 16.4 Thermal Characteristics

| Characteristic                                                                          | Symbol           | Value                                                                  | Unit |

|-----------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------|------|

| Thermal resistance 8-pin PDIP 8-pin SOIC 8-pin DFN 16-pin PDIP 16-pin SOIC 16-pin TSSOP | $\theta_{ m JA}$ | 105<br>142<br>173<br>76<br>90<br>133                                   | °C/W |

| I/O pin power dissipation                                                               | P <sub>I/O</sub> | User determined                                                        | W    |

| Power dissipation <sup>(1)</sup>                                                        | P <sub>D</sub>   | $P_D = (I_{DD} \times V_{DD})$<br>+ $P_{I/O} = K/(T_J + 273^{\circ}C)$ | W    |

| Constant <sup>(2)</sup>                                                                 | К                | $P_{D} x (T_{A} + 273^{\circ}C) + P_{D}^{2} x \theta_{JA}$             | W/°C |

| Average junction temperature                                                            | TJ               | $T_A + (P_D \times \theta_{JA})$                                       | °C   |

| Maximum junction temperature                                                            | T <sub>JM</sub>  | 150                                                                    | °C   |

<sup>1.</sup> Power dissipation is a function of temperature.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

<sup>2.</sup> K constant unique to the device. K can be determined for a known  $T_A$  and measured  $P_D$ . With this value of K,  $P_D$  and  $T_J$  can be determined for any value of  $T_A$ .

**Electrical Specifications**

# MECHANICAL OUTLINES DICTIONARY

DOCUMENT NO: 98ASB42431B

PAGE:

648

Τ

DO NOT SCALE THIS DRAWING

REV:

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: INCH.

$\overline{ {\it \Delta} }$  dimension to center of leads when formed parallel.

A. DIMENSIONS DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

- 6. 648-01 THRU -08 OBSOLETE, NEW STANDARD 648-09.

|     | MILLIMETERS |       | MILLIMETERS INCHES |       |     | MILLIM | IETERS | INC | HES |

|-----|-------------|-------|--------------------|-------|-----|--------|--------|-----|-----|

| DIM | MIN         | MAX   | MIN                | MAX   | DIM | MIN    | MAX    | MIN | MAX |

| А   | 18.80       | 19.55 | 0.740              | 0.770 |     |        |        |     |     |

| В   | 6.35        | 6.85  | 0.250              | 0.270 |     |        |        |     |     |

| С   | 3.69        | 4.44  | 0.145              | 0.175 |     |        |        |     |     |

| D   | 0.39        | 0.53  | 0.015              | 0.021 |     |        |        |     |     |

| F   | 1.02        | 1.77  | 0.040              | 0.070 |     |        |        |     |     |

| G   | 2.54 BSC    |       | 0.100              | BSC   |     |        |        |     |     |

| Н   | 1.27        | BSC   | 0.050              | BSC   |     |        |        |     |     |

| J   | 0.21        | 0.38  | 0.008              | 0.015 |     |        |        |     |     |

| K   | 2.80        | 3.30  | 0.110              | 0.130 |     |        |        |     |     |

| L   | 7.50        | 7.74  | 0.295              | 0.305 |     |        |        |     |     |

| М   | 0.          | 10°   | 0.                 | 10°   |     |        |        |     |     |

| S   | 0.51        | 1.01  | 0.020              | 0.040 |     |        |        |     |     |

TITLE:

16 LD PDIP

CASE NUMBER: 648-08

STANDARD: NON-JEDEC

PACKAGE CODE: 0006 | SHEET: 2 OF 4

# MECHANICAL OUTLINES DICTIONARY

DOCUMENT NO: 98ASB42567B

PAGE: 751G

DO NOT SCALE THIS DRAWING

REV: E

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A AND B TO BE DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSION OR GATE BURRS SHALL NOT EXCEED 0.15 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE INTER—LEAD FLASH OR PROTRUSIONS. INTER—LEAD FLASH AND PROTRUSIONS SHALL NOT EXCEED 0.25 MM PER SIDE. THIS DIMENSION IS DETERMINED AT THE PLANE WHERE THE BOTTOM OF THE LEADS EXIT THE PLASTIC BODY.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.62 mm.

TITLE:

16LD SOIC W/B, 1.27 PITCH, CASE OUTLINE

CASE NUMBER: 751G-05

STANDARD: JEDEC MS-013AA

PACKAGE CODE: 2003 | SHEET: 2 OF 3