# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | HC08                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 2MHz                                                                 |

| Connectivity               |                                                                      |

| Peripherals                | LVD, POR, PWM                                                        |

| Number of I/O              | 13                                                                   |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                |                                                                      |

| RAM Size                   | 128 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                          |

| Data Converters            | A/D 4x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | 16-SOIC                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcl908qy2dwe |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Features of the CPU08 include the following:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

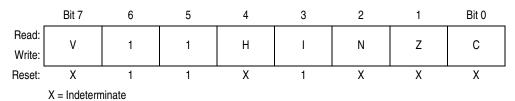

# 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HLC908QY4.

# **1.4 Pin Assignments**

The MC68HLC908QT4, MC68HLC908QT2, and MC68HLC908QT1 are available in 8-pin packages and the MC68HLC908QY4, MC68HLC908QY2, and MC68HLC908QY1 in 16-pin packages. Figure 1-2 shows the pin assignment for these packages.

Memory

# 2.6 FLASH Memory (FLASH)

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

The FLASH memory consists of an array of 4096 or 1536 bytes with an additional 48 bytes for user vectors. The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section. The address ranges for the user memory and vectors are:

- \$EE00 \$FDFF; user memory, 4096 bytes: MC68HLC908QY4 and MC68HLC908QT4

- \$F800 \$FDFF; user memory, 1536 bytes: MC68HLC908QY2, MC68HLC908QT2, MC68HLC908QY1 and MC68HLC908QT1

- \$FFD0 \$FFFF; user interrupt vectors, 48 bytes.

### NOTE

An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

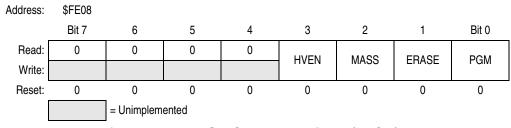

# 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

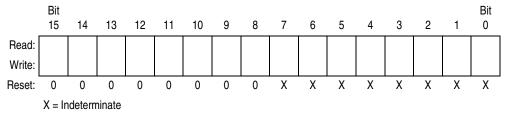

Figure 2-3. FLASH Control Register (FLCR)

### HVEN — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

1 = High voltage enabled to array and charge pump on

0 = High voltage disabled to array and charge pump off

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

#### Computer Operating Properly (COP)

The COP counter is a free-running 6-bit counter preceded by the 12-bit system integration module (SIM) counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 BUSCLKX4 cycles; depending on the state of the COP rate select bit, COPRS, in configuration register 1. With a 262,128 BUSCLKX4 cycle overflow option, the internal 4.0-MHz oscillator gives a COP timeout period of 65.53 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

A COP reset pulls the  $\overline{\text{RST}}$  pin low (if the RSTEN bit is set in the CONFIG1 register) for  $32 \times \text{BUSCLKX4}$  cycles and sets the COP bit in the reset status register (RSR). See 13.8.1 SIM Reset Status Register.

### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

# 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

# 6.3.1 BUSCLKX4

BUSCLKX4 is the oscillator output signal. BUSCLKX4 frequency is equal to the internal oscillator frequency, crystal frequency, or the RC-oscillator frequency.

# 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

# 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see 6.4 COP Control Register) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector.

# 6.3.4 Power-On Reset

The power-on reset (POR) circuit in the SIM clears the SIM counter  $4096 \times BUSCLKX4$  cycles after power up.

# 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

# 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

Computer Operating Properly (COP)

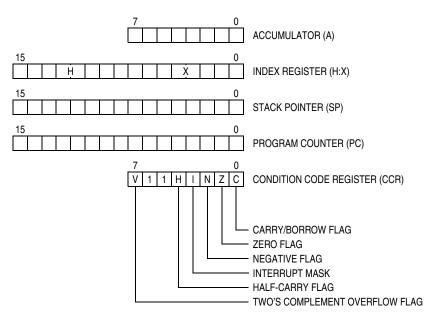

#### **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

# 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 7-2. Accumulator (A)

# 7.3.2 Index Register

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

**Central Processor Unit (CPU)**

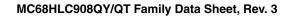

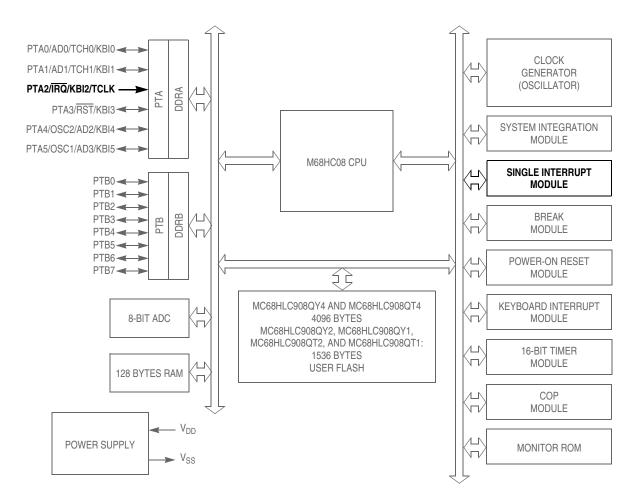

# 7.3.5 Condition Code Register

The 8-bit condition code register contains the interrupt mask and five flags that indicate the results of the instruction just executed. Bits 6 and 5 are set permanently to 1. The following paragraphs describe the functions of the condition code register.

Figure 7-6. Condition Code Register (CCR)

# V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

# H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

1 = Carry between bits 3 and 4

0 = No carry between bits 3 and 4

# I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

# NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first. A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

### N — Negative Flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

1 = Negative result

0 = Non-negative result

\_\_\_\_\_

| Source                                                                                         | Operation                           | Description                                                                                                                                                                                                | Effect<br>on CCF |    |   |    | fect v<br>CCR |   |                                                     | Address<br>Mode<br>Opcode                        | Operand                    | es                    |

|------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----|---|----|---------------|---|-----------------------------------------------------|--------------------------------------------------|----------------------------|-----------------------|

| Form                                                                                           |                                     |                                                                                                                                                                                                            |                  |    | I | Ν  | z             | С | Add                                                 | Opc                                              | Ope                        | Cycles                |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X                                         | Jump                                | $PC \gets Jump \; Address$                                                                                                                                                                                 | -                | _  | _ | -  | _             | - | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC<br>CC<br>DC<br>EC<br>FC                       | dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>3<br>2 |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X                                         | Jump to Subroutine                  | $\begin{array}{l} PC \leftarrow (PC) + n  (n = 1, 2,  \mathrm{or}  3) \\ Push  (PCL);  SP \leftarrow (SP) - 1 \\ Push  (PCH);  SP \leftarrow (SP) - 1 \\ PC \leftarrow Unconditional  Address \end{array}$ | _                | _  | _ | _  | -             | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD<br>CD<br>DD<br>ED<br>FD                       | dd<br>hh ll<br>ee ff<br>ff | 4<br>5<br>6<br>5<br>4 |

| LDA #opr<br>LDA opr<br>LDA opr<br>LDA opr,X<br>LDA opr,X<br>LDA ,X<br>LDA opr,SP<br>LDA opr,SP | Load A from M                       | A ← (M)                                                                                                                                                                                                    | 0                | -  | _ | ţ  | ţ             | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A6<br>B6<br>C6<br>D6<br>E6<br>F6<br>9EE6<br>9ED6 |                            | 2 3 4 4 3 2 4 5       |

| LDHX #opr<br>LDHX opr                                                                          | Load H:X from M                     | $H:X \leftarrow (M:M+1)$                                                                                                                                                                                   | 0                | -  | - | \$ | ţ             | - | IMM<br>DIR                                          | 45<br>55                                         | ii jj<br>dd                | 3<br>4                |

| LDX #opr<br>LDX opr<br>LDX opr<br>LDX opr,X<br>LDX opr,X<br>LDX ,X<br>LDX opr,SP<br>LDX opr,SP | Load X from M                       | $X \gets (M)$                                                                                                                                                                                              | 0                | -  | _ | ţ  | ţ             | - | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AE<br>BE<br>CE<br>EE<br>FE<br>9EEE<br>9EDE       |                            | 23443245              |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X<br>LSL ,Opr,SP                                  | Logical Shift Left<br>(Same as ASL) | C ← ← 0<br>b7 b0                                                                                                                                                                                           | ţ                | _  | _ | ţ  | ţ             | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff             | 4<br>1<br>4<br>3<br>5 |

| LSR opr<br>LSRA<br>LSRX<br>LSR opr,X<br>LSR ,X<br>LSR opr,SP                                   | Logical Shift Right                 | 0 → C<br>b7 b0                                                                                                                                                                                             | ţ                | _  | _ | 0  | ţ             | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 34<br>44<br>54<br>64<br>74<br>9E64               | dd<br>ff<br>ff             | 4 1<br>1 4 3 5        |

| MOV opr,opr<br>MOV opr,X+<br>MOV #opr,opr<br>MOV X+,opr                                        | Move                                | $\begin{array}{l} (M)_{Destination} \leftarrow (M)_{Source} \\ H:X \leftarrow (H:X) + 1 \; (IX+D, DIX+) \end{array}$                                                                                       | 0                | _  | _ | ţ  | t             | - | DD<br>DIX+<br>IMD<br>IX+D                           | 4E<br>5E<br>6E<br>7E                             | dd dd<br>dd<br>ii dd<br>dd | 5<br>4<br>4<br>4      |

| MUL                                                                                            | Unsigned multiply                   | $X:A \leftarrow (X) \times (A)$                                                                                                                                                                            | -                | 0  | - | -  | -             | 0 | INH                                                 | 42                                               |                            | 5                     |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG ,X<br>NEG opr,SP                                   | Negate (Two's Complement)           | $\begin{array}{l} M \leftarrow -(M) = \$00 - (M) \\ A \leftarrow -(A) = \$00 - (A) \\ X \leftarrow -(X) = \$00 - (X) \\ M \leftarrow -(M) = \$00 - (M) \\ M \leftarrow -(M) = \$00 - (M) \end{array}$      | ţ                | _  | _ | ţ  | ţ             | ţ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60               | dd<br>ff<br>ff             | 4<br>1<br>4<br>3<br>5 |

| NOP                                                                                            | No Operation                        | None                                                                                                                                                                                                       | -                | -  | - | -  | -             | - | INH                                                 | 9D                                               |                            | 1                     |

| NSA                                                                                            | Nibble Swap A                       | A ← (A[3:0]:A[7:4])                                                                                                                                                                                        | -                | [- | - | -  | -             | - | INH                                                 | 62                                               |                            | 3                     |

| ORA #opr<br>ORA opr<br>ORA opr<br>ORA opr,X<br>ORA opr,X<br>ORA opr,SP<br>ORA opr,SP           | Inclusive OR A and M                | A ← (A) I (M)                                                                                                                                                                                              | 0                | _  | _ | ţ  | ţ             | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EEA<br>9EDA |                            | 2 3 4 4 3 2 4 5       |

| PSHA                                                                                           | Push A onto Stack                   | Push (A); SP $\leftarrow$ (SP) – 1                                                                                                                                                                         | -                | -  | - | -  | -             | - | INH                                                 | 87                                               |                            | 2                     |

| PSHH                                                                                           | Push H onto Stack                   | Push (H); SP $\leftarrow$ (SP) – 1                                                                                                                                                                         | <u> -</u>        | [_ | - | -  | _             | - | INH                                                 | 8B                                               |                            | 2                     |

| PSHX                                                                                           | Push X onto Stack                   | Push (X); SP $\leftarrow$ (SP) – 1                                                                                                                                                                         | -                | -  | - | -  | -             | - | INH                                                 | 89                                               |                            | 2                     |

| Table 7-1. Instruction Set Summar | ry (Sheet 4 of 6) |

|-----------------------------------|-------------------|

|-----------------------------------|-------------------|

MC68HLC908QY/QT Family Data Sheet, Rev. 3

#### **External Interrupt (IRQ)**

RST, IRQ: Pins have internal (about 30K Ohms) pull up PTA[0:5]: High current sink and source capability PTA[0:5]: Pins have programmable keyboard interrupt and pull up PTB[0:7]: Not available on 8-pin devices – MC68HLC908QT1, MC68HLC908QT2, and MC68HLC908QT4 (see note in 12.1 Introduction)

ADC: Not available on the MC68HLC908QY1 and MC68HC9L08QT1

### Figure 8-1. Block Diagram Highlighting IRQ Block and Pins

When set, the IMASK bit in INTSCR masks the IRQ interrupt request. A latched interrupt request is not presented to the interrupt priority logic unless IMASK is clear.

NOTE

The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including the IRQ interrupt request.

A falling edge on the IRQ pin can latch an interrupt request into the IRQ latch. An IRQ vector fetch, software clear, or reset clears the IRQ latch.

# 8.7.1 IRQ Input Pins (IRQ)

The IRQ pin provides a maskable external interrupt source. The IRQ pin contains an internal pullup device.

# 8.8 Registers

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. See Chapter 5 Configuration Register (CONFIG).

The INTSCR has the following functions:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks the IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

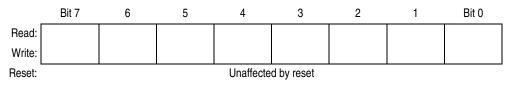

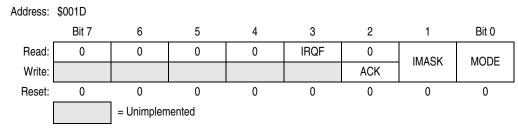

Figure 8-3. IRQ Status and Control Register (INTSCR)

#### **IRQF** — **IRQ** Flag

This read-only status bit is set when the IRQ interrupt is pending.

$1 = \overline{IRQ}$  interrupt pending

$0 = \overline{IRQ}$  interrupt not pending

#### ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads as 0.

#### IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables the IRQ interrupt request.

- 1 = IRQ interrupt request disabled

- 0 = IRQ interrupt request enabled

#### MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin.

- $1 = \overline{IRQ}$  interrupt request on falling edges and low levels

- $0 = \overline{IRQ}$  interrupt request on falling edges only

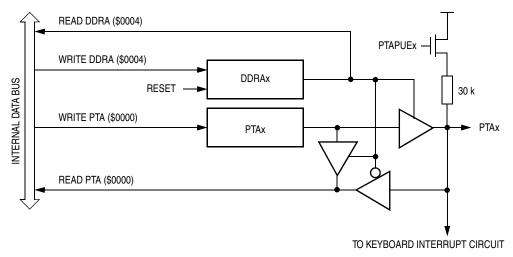

Figure 12-3 shows the port A I/O logic.

### Figure 12-3. Port A I/O Circuit

NOTE

Figure 12-3 does not apply to PTA2

When DDRAx is a 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

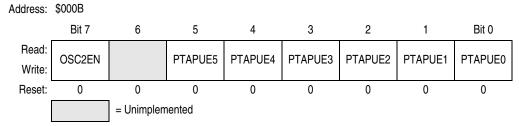

### 12.2.3 Port A Input Pullup Enable Register

The port A input pullup enable register (PTAPUE) contains a software configurable pullup device for each if the six port A pins. Each bit is individually configurable and requires the corresponding data direction register, DDRAx, to be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRAx bit is configured as output.

#### OSC2EN — Enable PTA4 on OSC2 Pin

This read/write bit configures the OSC2 pin function when internal oscillator or RC oscillator option is selected. This bit has no effect for the XTAL or external oscillator options.

1 = OSC2 pin outputs the internal or RC oscillator clock (BUSCLKX4)

0 = OSC2 pin configured for PTA4 I/O, having all the interrupt and pullup functions

Input/Output Ports (PORTS)

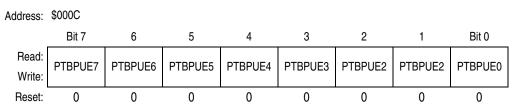

# 12.3.3 Port B Input Pullup Enable Register

The port B input pullup enable register (PTBPUE) contains a software configurable pullup device for each of the eight port B pins. Each bit is individually configurable and requires the corresponding data direction register, DDRBx, be configured as input. Each pullup device is automatically and dynamically disabled when its corresponding DDRBx bit is configured as output.

Figure 12-8. Port B Input Pullup Enable Register (PTBPUE)

# PTBPUE[7:0] — Port B Input Pullup Enable Bits

These read/write bits are software programmable to enable pullup devices on port B pins

- 1 = Corresponding port B pin configured to have internal pull if its DDRB bit is set to 0

- 0 = Pullup device is disconnected on the corresponding port B pin regardless of the state of its DDRB bit.

Table 12-3 summarizes the operation of the port B pins.

| Table | 12-3. | Port B | Pin | Functions |

|-------|-------|--------|-----|-----------|

|-------|-------|--------|-----|-----------|

| PTBPUE | PTBPUE DDRB PTB |                  | I/O Pin                               | Accesses to DDRB | Access    | es to PTB                |

|--------|-----------------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| Bit    | Bit             | Bit              | Mode                                  | Read/Write       | Read      | Write                    |

| 1      | 0               | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(2)</sup> | DDRB7-DDRB0      | Pin       | PTB7–PTB0 <sup>(3)</sup> |

| 0      | 0               | Х                | Input, Hi-Z <sup>(4)</sup>            | DDRB7-DDRB0      | Pin       | PTB7–PTB0 <sup>(3)</sup> |

| Х      | 1               | Х                | Output                                | DDRB7-DDRB0      | PTB7–PTB0 | PTB7–PTB0                |

1. X = don't care

2. I/O pin pulled to  $V_{DD}$  by internal pullup.

3. Writing affects data register, but does not affect input.

4. Hi-Z = high impedance

### IF1 and IF3–IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 0, 1, 3, and 7 — Always read 0

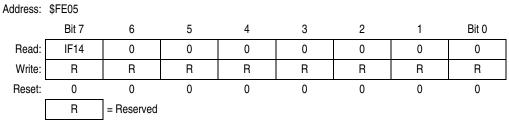

#### 13.6.2.2 Interrupt Status Register 2

#### Figure 13-12. Interrupt Status Register 2 (INT2)

#### IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 0–6 — Always read 0

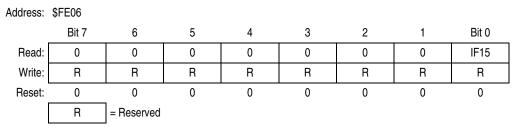

#### 13.6.2.3 Interrupt Status Register 3

#### Figure 13-13. Interrupt Status Register 3 (INT3)

#### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

#### Bit 1–7 — Always read 0

#### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

### 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break

#### MC68HLC908QY/QT Family Data Sheet, Rev. 3

Timer Interface Module (TIM)

# 14.6 Wait Mode

The WAIT instruction puts the MCU in low power-consumption standby mode.

The TIM remains active after the execution of a WAIT instruction. In wait mode the TIM registers are not accessible by the CPU. Any enabled CPU interrupt request from the TIM can bring the MCU out of wait mode.

If TIM functions are not required during wait mode, reduce power consumption by stopping the TIM before executing the WAIT instruction.

# 14.7 TIM During Break Interrupts

A break interrupt stops the TIM counter.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 13.8.2 Break Flag Control Register.

To allow software to clear status bits during a break interrupt, write a 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to the BCFE bit. With BCFE at 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at 0. After the break, doing the second step clears the status bit.

# 14.8 Input/Output Signals

Port A shares three of its pins with the TIM. Two TIM channel I/O pins are PTA0/TCH0 and PTA1/TCH1 and an alternate clock source is PTA2/TCLK.

# 14.8.1 TIM Clock Pin (PTA2/TCLK)

PTA2/TCLK is an external clock input that can be the clock source for the TIM counter instead of the prescaled internal bus clock. Select the PTA2/TCLK input by writing 1s to the three prescaler select bits, PS[2–0]. (See 14.9.1 TIM Status and Control Register.) When the PTA2/TCLK pin is the TIM clock input, it is an input regardless of port pin initialization.

# 14.8.2 TIM Channel I/O Pins (PTA0/TCH0 and PTA1/TCH1)

Each channel I/O pin is programmable independently as an input capture pin or an output compare pin. PTA0/TCH0 can be configured as a buffered output compare or buffered PWM pin.

# 14.9 Input/Output Registers

The following I/O registers control and monitor operation of the TIM:

- TIM status and control register (TSC)

- TIM counter registers (TCNTH:TCNTL)

- TIM counter modulo registers (TMODH:TMODL)

- TIM channel status and control registers (TSC0 and TSC1)

- TIM channel registers (TCH0H:TCH0L and TCH1H:TCH1L)

Timer Interface Module (TIM)

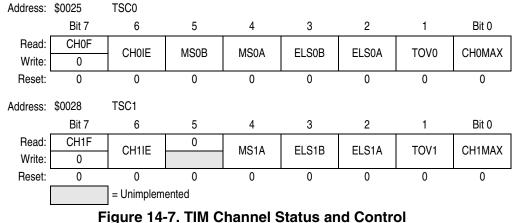

# 14.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- · Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Registers (TSC0:TSC1)

# CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

Clear CHxF by reading the TIM channel x status and control register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing a 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

# CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIM channel 0 status and control register.

# Chapter 15 Development Support

# **15.1 Introduction**

This section describes the break module, the monitor read-only memory (MON), and the monitor mode entry methods.

# 15.2 Break Module (BRK)

The break module can generate a break interrupt that stops normal program flow at a defined address to enter a background program.

Features include:

- Accessible input/output (I/O) registers during the break Interrupt

- Central processor unit (CPU) generated break interrupts

- Software-generated break interrupts

- Computer operating properly (COP) disabling during break interrupts

# 15.2.1 Functional Description

When the internal address bus matches the value written in the break address registers, the break module issues a breakpoint signal (BKPT) to the system integration module (SIM). The SIM then causes the CPU to load the instruction register with a software interrupt instruction (SWI). The program counter vectors to \$FFFC and \$FFFD (\$FEFC and \$FEFD in monitor mode).

The following events can cause a break interrupt to occur:

- A CPU generated address (the address in the program counter) matches the contents of the break address registers.

- Software writes a 1 to the BRKA bit in the break status and control register.

When a CPU generated address matches the contents of the break address registers, the break interrupt is generated. A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the microcontroller unit (MCU) to normal operation.

Figure 15-2 shows the structure of the break module.

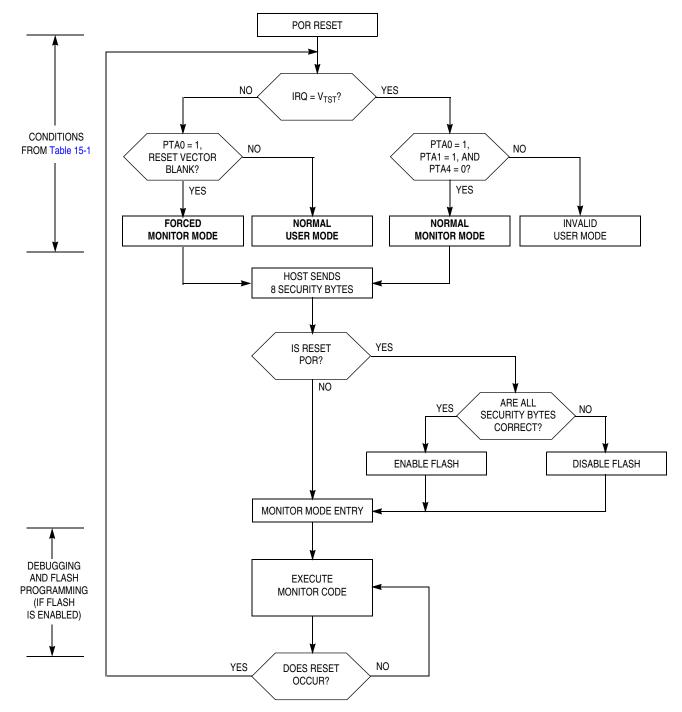

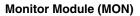

#### Monitor Module (MON)

Figure 15-9. Simplified Monitor Mode Entry Flowchart

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 4800 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (1.0 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires V<sub>TST</sub> on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- IRQ = V<sub>TST</sub>

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- IRQ = V<sub>DD</sub> (this can be implemented through the internal IRQ pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- $\overline{IRQ} = V_{SS}$  (internal oscillator is selected, no external clock required)

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

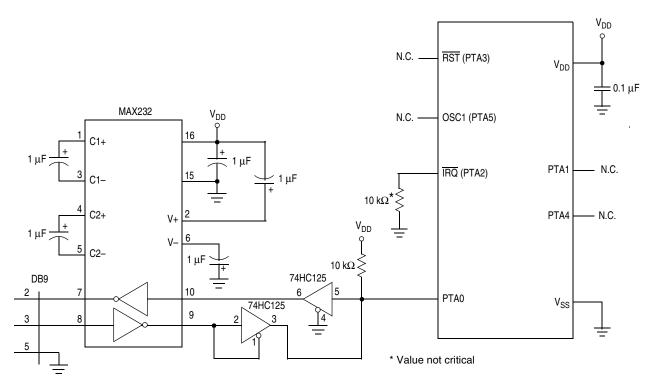

# Chapter 17 Ordering Information and Mechanical Specifications

# 17.1 Introduction

This section contains ordering numbers for MC68HLC908QY1, MC68HLC908QY2, MC68HLC908QY4, MC68HLC908QT1, MC68HLC908QT2, and MC69HLC908QT4. Refer to Figure 17-1 for an example of the device numbering system.

In addition, this section gives the package dimensions for:

- 8-pin plastic dual in-line package (PDIP)

- 8-pin small outline integrated circuit (SOIC) package

- 8-pin dual flat no lead (DFN) package

- 16-pin PDIP

- 16-pin SOIC

- 16-pin thin shrink small outline package (TSSOP)

# 17.2 MC Order Numbers

Table 17-1. MC Order Numbers

| MC Order Number | ADC | FLASH Memory | Package     |

|-----------------|-----|--------------|-------------|

| MCL908QY1       | —   | 1536 bytes   | 16-pins     |

| MCL908QY2       | Yes | 1536 bytes   | PDIP, SOIC, |

| MCL908QY4       | Yes | 4096 bytes   | and TSSOP   |

| MCL908QT1       | _   | 1536 bytes   | 8-pins      |

| MCL908QT2       | Yes | 1536 bytes   | PDIP, SOIC, |

| MCL908QT4       | Yes | 4096 bytes   | and DFN     |

Temperature and package designators:

Blank =  $0^{\circ}$ C to  $70^{\circ}$ C

C =  $-40^{\circ}$ C to  $85^{\circ}$ C

P = Plastic dual in-line package (PDIP)

DW = Small outline integrated circuit package (SOIC)

DT = Thin shrink small outline package (TSSOP)

FQ = Dual flat no lead (DFN)

Figure 17-1. Device Numbering System

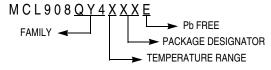

# 17.3 Package Dimensions

Refer to the following pages for detailed package dimensions.

MC68HLC908QY/QT Family Data Sheet, Rev. 3

DETAIL "D"

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTL | .INE PRINT VERSION N | IOT TO SCALE |

|---------------------------------------------------------|-----------------|----------------------|--------------|

| TITLE:                                                  | DOCUM           | ENT NO: 98ASB42420B  | REV: N       |

| 8 LD PDIP                                               | CASE            | NUMBER: 626-06       | 19 MAY 2005  |

|                                                         | STAND           | ARD: NON-JEDEC       |              |

|                                                                                                                                                                                                   | MECHANICAL OUTLINES       | DOCUMENT | NO: 98ASB42431B |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|-----------------|

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                                                                                              | DICTIONARY                | PAGE:    | 648             |

| ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROW THE DOCUMENT CONTROL REPOSITORY. PRINTED<br>VERSIONS ARE UNCONTROLLED EXCEPT WHEN STAWPED "CONTROLLED<br>COPY" IN RED. | DO NOT SCALE THIS DRAWING | REV:     | Т               |

# NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION TO CENTER OF LEADS WHEN FORMED PARALLEL.

- A DIMENSIONS DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

- 6. 648-01 THRU -08 OBSOLETE, NEW STANDARD 648-09.

|                                | MILLIN | IETERS | INC   | HES   |      | MILLIMETERS |          |       | NCHES  |

|--------------------------------|--------|--------|-------|-------|------|-------------|----------|-------|--------|

| DIM                            | MIN    | MAX    | MIN   | MAX   | DIM  | MIN         | MAX      | MIN   | MAX    |

| А                              | 18.80  | 19.55  | 0.740 | 0.770 |      |             |          |       |        |

| В                              | 6.35   | 6.85   | 0.250 | 0,270 |      |             |          |       |        |

| С                              | 3.69   | 4.44   | 0.145 | 0.175 |      |             |          |       |        |

| D                              | 0.39   | 0.53   | 0.015 | 0.021 |      |             |          |       |        |

| F                              | 1.02   | 1.77   | 0.040 | 0.070 |      |             |          |       |        |

| G                              | 2.54   | BSC    | 0.100 | BSC   |      |             |          |       |        |

| Н                              | 1.27   | BSC    | 0.050 | ) BSC |      |             |          |       |        |

| J                              | 0.21   | 0.38   | 0.008 | 0.015 |      |             |          |       |        |

| K                              | 2.80   | 3.30   | 0.110 | 0.130 |      |             |          |       |        |

| L                              | 7.50   | 7.74   | 0.295 | 0.305 |      |             |          |       |        |

| М                              | 0.     | 10°    | 0.    | 10°   |      |             |          |       |        |

| S                              | 0.51   | 1.01   | 0.020 | 0.040 |      |             |          |       |        |

| TITLE:                         |        |        |       |       |      | NUMBER: (   | 648-08   |       |        |

| 16 LD PDIP STANDARD: NON-JEDEC |        |        |       |       |      | -JEDEC      |          |       |        |

|                                |        |        |       |       | PACK | AGE CODE:   | : 0006 S | HEET: | 2 OF 4 |