### NXP USA Inc. - MCL908QY4CDTE Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 2MHz                                                                  |

| Connectivity               | -                                                                     |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 13                                                                    |

| Program Memory Size        | 4KB (4K × 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 128 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                           |

| Data Converters            | A/D 4x8b                                                              |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

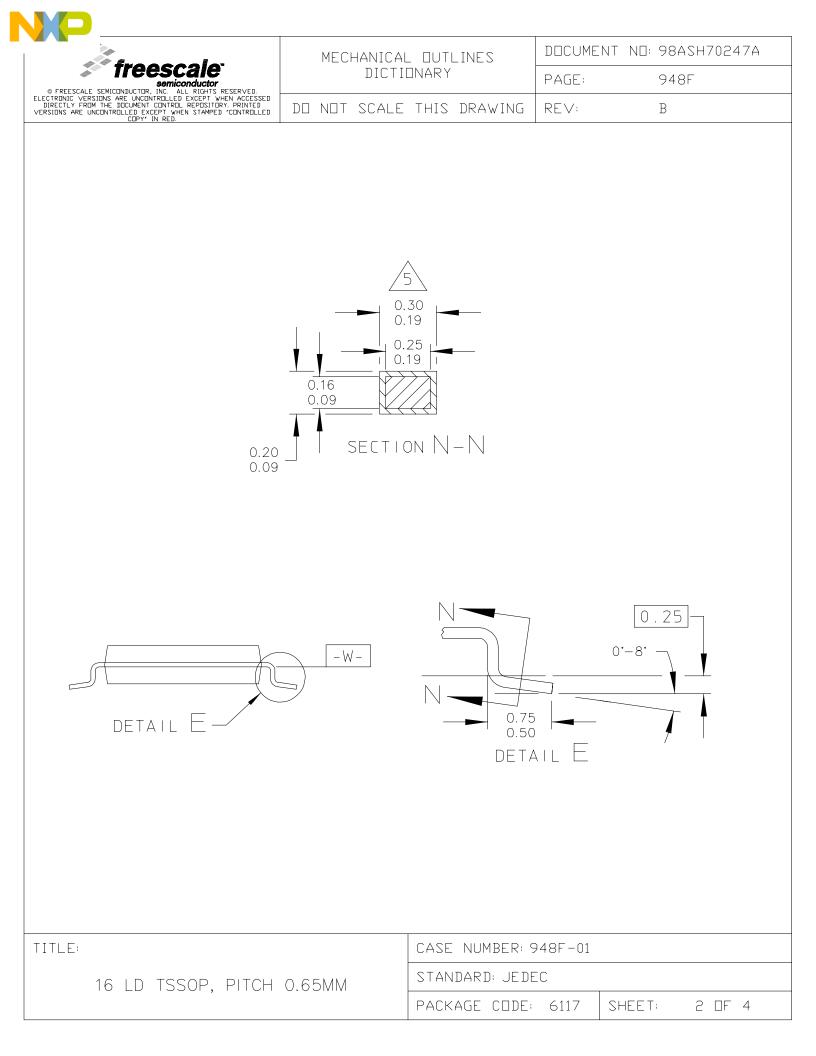

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 16-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcl908qy4cdte |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 7 and 8 until all desired bytes within the row are programmed.

- 10. Clear the PGM bit $^{(1)}$ .

- 11. Wait for time,  $t_{NVH}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{RCV}$  (typical 1 µs), the memory can be accessed in read mode again.

### NOTE

The COP register at location \$FFFF should not be written between steps 5-12, when the HVEN bit is set. Since this register is located at a valid FLASH address, unpredictable behavior may occur if this location is written while HVEN is set.

This program sequence is repeated throughout the memory until all data is programmed.

### NOTE

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. While these operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum, see 16.12 Memory Characteristics.

### 2.6.5 FLASH Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either ERASE or PROGRAM operations.

### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit.

When the FLBPR is programmed with all 0s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1s), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory. The address ranges are shown in 2.6.6 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. Mass erase is disabled whenever any block is protected (FLBPR does not equal FF). The FLBPR itself can be erased or programmed only with an external voltage,  $V_{TST}$ , present on the IRQ pin. This voltage also allows entry from reset into the monitor mode.

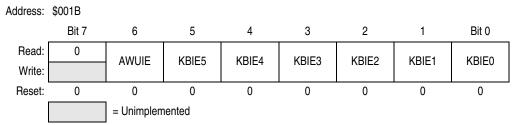

# 4.6.3 Keyboard Interrupt Enable Register

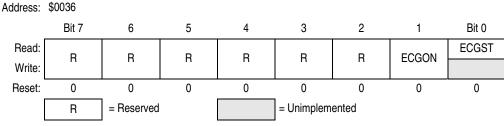

The keyboard interrupt enable register (KBIER) enables or disables the auto wakeup to operate as a keyboard/auto wakeup interrupt input.

### Figure 4-4. Keyboard Interrupt Enable Register (KBIER)

### AWUIE — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

1 = Auto wakeup enabled as interrupt input

0 = Auto wakeup not enabled as interrupt input

### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. To see a description of these bits, see 9.7.2 Keyboard Interrupt Enable Register.

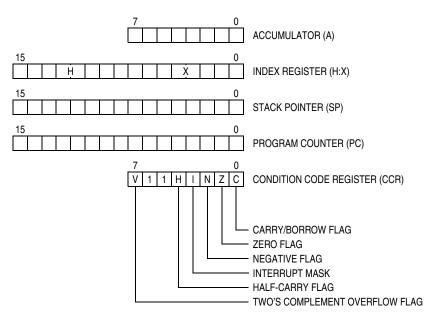

#### **Central Processor Unit (CPU)**

Figure 7-1. CPU Registers

# 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

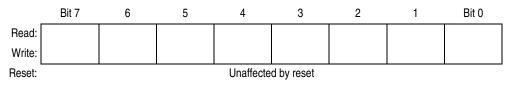

Figure 7-2. Accumulator (A)

## 7.3.2 Index Register

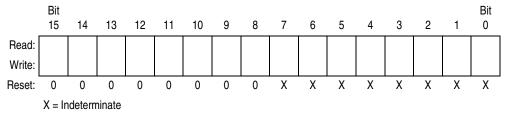

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

### Z — Zero Flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

### C — Carry/Borrow Flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions — such as bit test and branch, shift, and rotate — also clear or set the carry/borrow flag.

1 = Carry out of bit 7

0 = No carry out of bit 7

# 7.4 Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (document order number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about the architecture of the CPU.

# 7.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 7.5.1 Wait Mode

The WAIT instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling interrupts. After exit from wait mode by interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

# 7.5.2 Stop Mode

The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

# 7.6 CPU During Break Interrupts

If a break module is present on the MCU, the CPU starts a break interrupt by:

- · Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD or with \$FEFC:\$FEFD in monitor mode

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

### Low-Voltage Inhibit (LVI)

The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit (LVIPWRD) enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit (LVIRSTD) enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,  $V_{TRIPF}$  or  $V_{DTRIPF}$ . Setting the LVI enable in stop mode bit (LVISTOP) enables the LVI to operate in stop mode. Setting the LVD or LVR trip point bit (LVDLVR) selects the LVD trip point voltage. The actual trip thresholds are specified in 16.5 DC Electrical Characteristics. Either trip level can be used as a detect or reset.

### NOTE

After a power-on reset, the LVI's default mode of operation is LVR trip voltage. If a higher trip voltage is desired, the user must set the LVDLVR bit to raise the trip point to the LVD voltage.

If the user requires the higher trip voltage and sets the LVDLVR bit after power-on reset while the VDD supply is not above the  $V_{TRIPR}$  for LVD mode, the microcontroller unit (MCU) will immediately go into reset. The next time the LVI releases the reset, the supply will be above the  $V_{TRIPR}$  for LVD mode.

Once an LVI reset occurs, the MCU remains in reset until  $V_{DD}$  rises above a voltage,  $V_{TRIPR}$ , which causes the MCU to exit reset. See Chapter 13 System Integration Module (SIM) for the reset recovery sequence.

The output of the comparator controls the state of the LVIOUT flag in the LVI status register (LVISR) and can be used for polling LVI operation when the LVI reset is disabled.

# 10.3.1 Polled LVI Operation

In applications that can operate at  $V_{DD}$  levels below the  $V_{TRIPF}$  level, software can monitor  $V_{DD}$  by polling the LVIOUT bit. In the configuration register, the LVIPWRD bit must be cleared to enable the LVI module, and the LVIRSTD bit must be set to disable LVI resets.

## 10.3.2 Forced Reset Operation

In applications that require  $V_{DD}$  to remain above the  $V_{TRIPF}$  level, enabling LVI resets allows the LVI module to reset the MCU when  $V_{DD}$  falls below the  $V_{TRIPF}$  level. In the configuration register, the LVIPWRD and LVIRSTD bits must be cleared to enable the LVI module and to enable LVI resets.

## 10.3.3 Voltage Hysteresis Protection

Once the LVI has triggered (by having  $V_{DD}$  fall below  $V_{TRIPF}$ ), the LVI will maintain a reset condition until  $V_{DD}$  rises above the rising trip point voltage,  $V_{TRIPR}$ . This prevents a condition in which the MCU is continually entering and exiting reset if  $V_{DD}$  is approximately equal to  $V_{TRIPF}$ .  $V_{TRIPR}$  is greater than  $V_{TRIPF}$  by the hysteresis voltage,  $V_{HYS}$ .

## 10.3.4 LVI Trip Selection

The LVDLVR bit in the configuration register selects whether the LVI is configured for LVD (low voltage detect) or LVR (low voltage reset) protection. The LVD trip voltage can be used as a low voltage warning. The LVR trip voltage will commonly be configured as a reset condition since it is very close to the minimum operating voltage of the device. The LVDLVR bit can be written to anytime so that battery applications can make use of the LVI as both a warning indicator and to generate a system reset.

# 11.6 Oscillator During Break Mode

The oscillator continues to drive BUSCLKX2 and BUSCLKX4 when the device enters the break state.

# 11.7 CONFIG2 Options

Two CONFIG2 register options affect the operation of the oscillator module: OSCOPT1 and OSCOPT0. All CONFIG2 register bits will have a default configuration. Refer to Chapter 5 Configuration Register (CONFIG) for more information on how the CONFIG2 register is used.

Table 11-2 shows how the OSCOPT bits are used to select the oscillator clock source.

| OSCOPT1 | OSCOPT0 | Oscillator Modes    |

|---------|---------|---------------------|

| 0       | 0       | Internal Oscillator |

| 0       | 1       | External Oscillator |

| 1       | 0       | External RC         |

| 1       | 1       | External Crystal    |

Table 11-2. Oscillator Modes

# 11.8 Input/Output (I/O) Registers

The oscillator module contains these two registers:

- 1. Oscillator status register (OSCSTAT)

- 2. Oscillator trim register (OSCTRIM)

## 11.8.1 Oscillator Status Register

The oscillator status register (OSCSTAT) contains the bits for switching from internal to external clock sources.

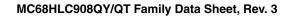

Figure 11-4. Oscillator Status Register (OSCSTAT)

### ECGON — External Clock Generator On Bit

This read/write bit enables external clock generator, so that the switching process can be initiated. This bit is forced low during reset. This bit is ignored in monitor mode with the internal oscillator bypassed.

1 = External clock generator enabled

0 = External clock generator disabled

### ECGST — External Clock Status Bit

This read-only bit indicates whether or not an external clock source is engaged to drive the system clock.

1 = An external clock source engaged

0 = An external clock source disengaged

# Chapter 12 Input/Output Ports (PORTS)

# 12.1 Introduction

The MC68HLC908QT1, MC68HLC908QT2, and MC68HLC908QT4 have five bidirectional input-output (I/O) pins and one input only pin. The MC68HLC908QY1, MC68HLC908QY2, and MC68HLC908QY4 have thirteen bidirectional pins and one input only pin. All I/O pins are programmable as inputs or outputs.

### NOTE

Connect any unused I/O pins to an appropriate logic level, either  $V_{DD}$  or  $V_{SS}$ . Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

8-pin devices have non-bonded pins. These pins should be configured either as outputs driving low or high, or as inputs with internal pullups enabled. Configuring these non-bonded pins in this manner will prevent any excess current consumption caused by floating inputs.

# 12.2 Port A

Port A is a 6-bit special function port that shares all six of its pins with the keyboard interrupt (KBI) module (see Chapter 9 Keyboard Interrupt Module (KBI)). Each port A pin also has a software configurable pullup device if the corresponding port pin is configured as an input port.

### NOTE

## PTA2 is input only.

When the IRQ function is enabled in the configuration register 2 (CONFIG2), bit 2 of the port A data register (PTA) will always read a 0. In this case, the BIH and BIL instructions can be used to read the logic level on the PTA2 pin. When the IRQ function is disabled, these instructions will behave as if the PTA2 pin is a logic 1. However, reading bit 2 of PTA will read the actual logic level on the pin.

Input/Output Ports (PORTS)

# 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the six port A pins.

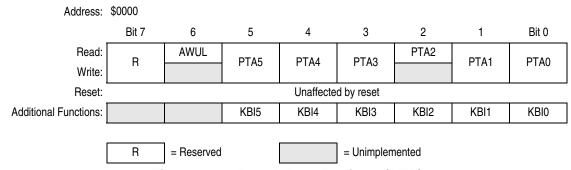

Figure 12-1. Port A Data Register (PTA)

### PTA[5:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

### AWUL — Auto Wakeup Latch Data Bit

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally (see Chapter 4 Auto Wakeup Module (AWU)). There is no PTA6 port nor any of the associated bits such as PTA6 data register, pullup enable or direction.

### KBI[5:0] — Port A Keyboard Interrupts

The keyboard interrupt enable bits, KBIE5–KBIE0, in the keyboard interrupt control enable register (KBIER) enable the port A pins as external interrupt pins (see Chapter 9 Keyboard Interrupt Module (KBI)).

# 12.2.2 Data Direction Register A

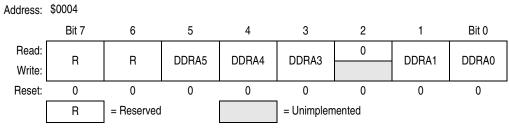

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

Figure 12-2. Data Direction Register A (DDRA)

### DDRA[5:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[5:0], configuring all port A pins as inputs.

1 = Corresponding port A pin configured as output

0 = Corresponding port A pin configured as input

## NOTE

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

### IF1 and IF3–IF5 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 0, 1, 3, and 7 — Always read 0

### 13.6.2.2 Interrupt Status Register 2

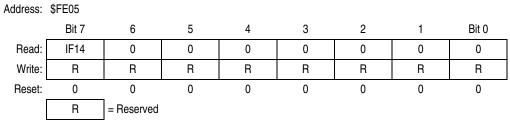

#### Figure 13-12. Interrupt Status Register 2 (INT2)

#### IF14 — Interrupt Flags

This flag indicates the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 0–6 — Always read 0

### 13.6.2.3 Interrupt Status Register 3

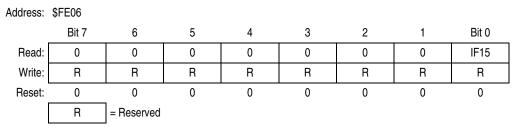

### Figure 13-13. Interrupt Status Register 3 (INT3)

### IF15 — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown in Table 13-3.

- 1 = Interrupt request present

- 0 = No interrupt request present

### Bit 1–7 — Always read 0

### 13.6.3 Reset

All reset sources always have equal and highest priority and cannot be arbitrated.

### 13.6.4 Break Interrupts

The break module can stop normal program flow at a software programmable break point by asserting its break interrupt output. (See Chapter 15 Development Support.) The SIM puts the CPU into the break

Timer Interface Module (TIM)

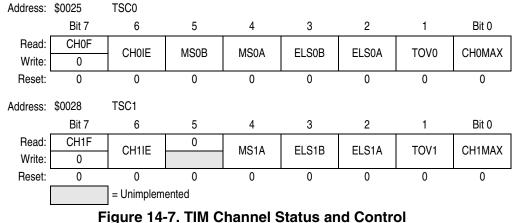

# 14.9.4 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers does the following:

- · Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Registers (TSC0:TSC1)

## CHxF — Channel x Flag Bit

When channel x is an input capture channel, this read/write bit is set when an active edge occurs on the channel x pin. When channel x is an output compare channel, CHxF is set when the value in the TIM counter registers matches the value in the TIM channel x registers.

Clear CHxF by reading the TIM channel x status and control register with CHxF set and then writing a 0 to CHxF. If another interrupt request occurs before the clearing sequence is complete, then writing a 0 to CHxF has no effect. Therefore, an interrupt request cannot be lost due to inadvertent clearing of CHxF.

Reset clears the CHxF bit. Writing a 1 to CHxF has no effect.

- 1 = Input capture or output compare on channel x

- 0 = No input capture or output compare on channel x

## CHxIE — Channel x Interrupt Enable Bit

This read/write bit enables TIM CPU interrupt service requests on channel x. Reset clears the CHxIE bit.

- 1 = Channel x CPU interrupt requests enabled

- 0 = Channel x CPU interrupt requests disabled

### MSxB — Mode Select Bit B

This read/write bit selects buffered output compare/PWM operation. MSxB exists only in the TIM channel 0 status and control register.

#### Monitor Module (MON)

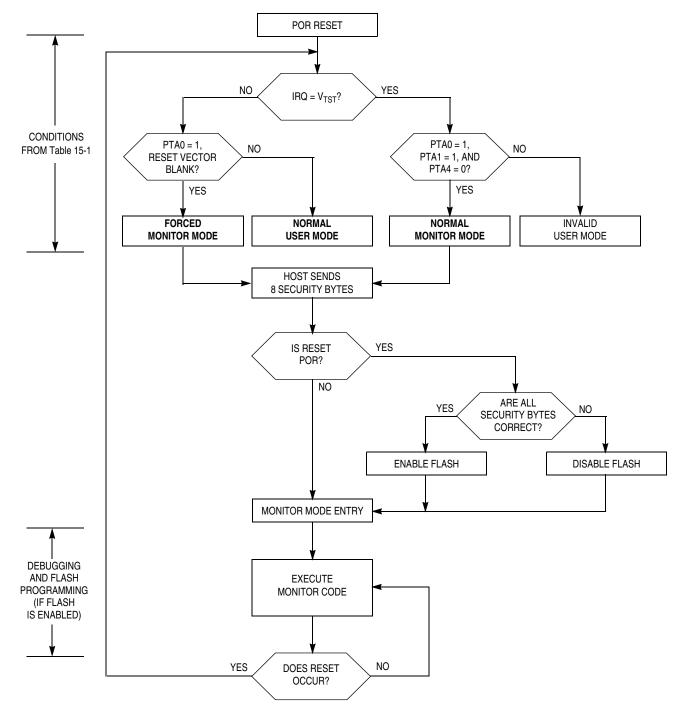

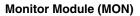

Figure 15-9. Simplified Monitor Mode Entry Flowchart

Figure 15-12. Monitor Mode Circuit (Internal Clock, No High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 4800 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (1.0 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires V<sub>TST</sub> on  $\overline{IRQ}$ . The  $\overline{IRQ}$  pin must remain low during this monitor session in order to maintain communication.

Table 15-1 shows the pin conditions for entering monitor mode. As specified in the table, monitor mode may be entered after a power-on reset (POR) and will allow communication at 9600 baud provided one of the following sets of conditions is met:

- If \$FFFE and \$FFFF do not contain \$FF (programmed state):

- The external clock is 9.8304 MHz

- IRQ = V<sub>TST</sub>

- If \$FFFE and \$FFFF contain \$FF (erased state):

- The external clock is 9.8304 MHz

- IRQ = V<sub>DD</sub> (this can be implemented through the internal IRQ pullup)

- If \$FFFE and \$FFFF contain \$FF (erased state):

- $\overline{IRQ} = V_{SS}$  (internal oscillator is selected, no external clock required)

The rising edge of the internal RST signal latches the monitor mode. Once monitor mode is latched, the values on PTA1 and PTA4 pins can be changed.

# **16.5 DC Electrical Characteristics**

| Characteristic <sup>(1)</sup>                                                                                                                        | Symbol                              | Min                                          | Typ <sup>(2)</sup> | Max                   | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------|--------------------|-----------------------|------|

| Output high voltage (for $V_{DD} > 2.7 V$ )<br>$I_{Load} = -4 mA$<br>$I_{Load} = -10 mA, PTA0, PTA1, PTA3-PTA5 only$                                 | V <sub>OH</sub>                     | V <sub>DD</sub> -0.8<br>V <sub>DD</sub> -0.8 | _                  |                       | v    |

| Output high voltage (for $V_{DDMIN} < V_{DD} < V_{DDMAX}$ )<br>$I_{Load} = -2 \text{ mA}$<br>$I_{Load} = -5 \text{ mA}$ , PTA0, PTA1, PTA3–PTA5 only | V <sub>OH</sub>                     | V <sub>DD</sub> -0.8<br>V <sub>DD</sub> -0.8 |                    |                       | v    |

| Output low voltage (for $V_{DD} > 2.7 \text{ V}$ )<br>$I_{Load} = 4 \text{ mA}$<br>$I_{Load} = 10 \text{ mA}$ , PTA0, PTA1, PTA3–PTA5 only           | V <sub>OL</sub>                     |                                              | _                  | 0.8<br>0.8            | v    |

| Output low voltage (for $V_{DDMIN} < V_{DD} < V_{DDMAX}$ )<br>$I_{Load} = 2 \text{ mA}$<br>$I_{Load} = 5 \text{ mA}$ , PTA0, PTA1, PTA3–PTA5 only    | V <sub>OL</sub>                     | _                                            | _                  | 0.8<br>0.8            | v    |

| Maximum combined I <sub>OH</sub> (all I/O pins)                                                                                                      | I <sub>OHT</sub>                    | —                                            | —                  | 50                    | mA   |

| Maximum combined I <sub>OL</sub> (all I/O pins)                                                                                                      | I <sub>OLT</sub>                    | —                                            | —                  | 50                    | mA   |

| Input high voltage<br>PTA0–PTA5, PTB0–PTB7                                                                                                           | V <sub>IH</sub>                     | 0.7 x V <sub>DD</sub>                        | _                  | V <sub>DD</sub>       | V    |

| Input low voltage<br>PTA0–PTA5, PTB0–PTB7                                                                                                            | V <sub>IL</sub>                     | V <sub>SS</sub>                              | _                  | 0.3 x V <sub>DD</sub> | V    |

| Input hysteresis                                                                                                                                     | V <sub>HYS</sub>                    | 0.06 x V <sub>DD</sub>                       | —                  | —                     | V    |

| DC injection current, all ports                                                                                                                      | I <sub>INJ</sub>                    | -2                                           | —                  | +2                    | mA   |

| Total dc current injection (sum of all I/O)                                                                                                          | I <sub>INJTOT</sub>                 | -25                                          | —                  | +25                   | mA   |

| Digital I/O ports Hi-Z leakage current<br>Typical at 25°C                                                                                            | IIL                                 | -1<br>                                       | <br>±0.1           | +1                    | μΑ   |

| Digital input only ports leakage current (PA2/IRQ/KBI2)                                                                                              | I <sub>IN</sub>                     | -1                                           | —                  | +1                    | μA   |

| Capacitance<br>Ports (as input)<br>Ports (as output)                                                                                                 | C <sub>IN</sub><br>C <sub>OUT</sub> |                                              | _                  | 12<br>8               | pF   |

| POR rearm voltage <sup>(3)</sup>                                                                                                                     | V <sub>POR</sub>                    | 0                                            | —                  | 100                   | mV   |

| POR rise time ramp rate <sup>(4)</sup>                                                                                                               | R <sub>POR</sub>                    | 0.035                                        | —                  | —                     | V/ms |

| Monitor mode entry voltage                                                                                                                           | V <sub>TST</sub>                    | V <sub>DD</sub> + 2.5                        | —                  | 9.1                   | V    |

| Pullup resistors <sup>(5)</sup><br>PTA0–PTA5, PTB0–PTB7                                                                                              | R <sub>PU</sub>                     | 16                                           | 26                 | 36                    | kΩ   |

- Continued on next page

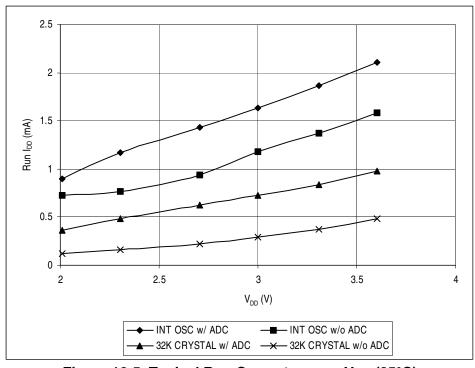

# **16.9 Supply Current Characteristics**

| Characteristic                                                                                                                                                                | Voltage    | Bus Freq.<br>(MHz) | Symbol           | Тур                                  | Max         | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|------------------|--------------------------------------|-------------|------|

| Run mode V <sub>DD</sub> supply current <sup>(1)</sup>                                                                                                                        | 3.0<br>2.2 | 1<br>1             | RI <sub>DD</sub> | 1.5<br>1.0                           | 2.5<br>1.5  | mA   |

| WAIT mode V <sub>DD</sub> supply current <sup>(2)</sup>                                                                                                                       | 3.0<br>2.2 | 1<br>1             | WI <sub>DD</sub> | 1.2<br>1.0                           | 2.0<br>1.0  | mA   |

| Stop mode V <sub>DD</sub> supply current <sup>(3)</sup><br>25°C<br>0 to 70°C<br>-40 to 85°C<br>25°C with auto wake-up enabled<br>Incremental current with LVI enabled at 25°C | 3.0        |                    | SI <sub>DD</sub> | 0.006<br>0.08<br>0.12<br>5.70<br>110 | <br>2.0<br> | μΑ   |

| 25°C<br>0 to 70°C<br>–40 to 85°C<br>25°C with auto wake-up enabled<br>Incremental current with LVI enabled at 25°C                                                            | 2.2        |                    | O'DD             | 0.005<br>0.08<br>0.12<br>1.30<br>100 | <br>1.0<br> | μΑ   |

1. Run (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules except ADC enabled.

Wait (operating) I<sub>DD</sub> measured using external square wave clock source. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules except ADC enabled.

3. Stop I<sub>DD</sub> measured with all ports driven 0.2 V or less from rail. No dc loads. On the 8-pin versions, port B is configured as inputs with pullups enabled.

Figure 16-5. Typical Run Current versus  $V_{DD}$  (25°C) (f<sub>Bus</sub> = 1 MHz for Internal Oscillator, f<sub>Bus</sub> = 8 kHz for Crystal Oscillator)

Electrical Specifications

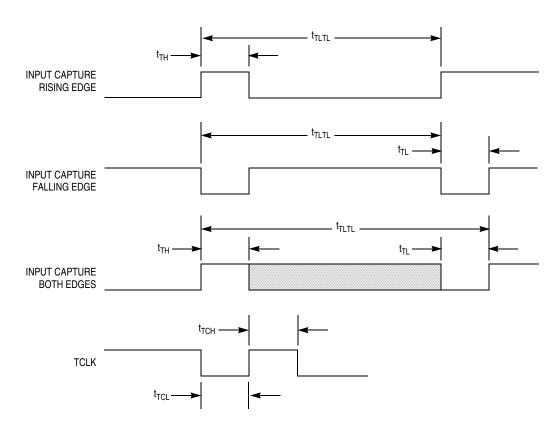

# **16.11 Timer Interface Module Characteristics**

| Characteristic                  | Symbol                              | Min                  | Max | Unit             |

|---------------------------------|-------------------------------------|----------------------|-----|------------------|

| Timer input capture pulse width | t <sub>TH,</sub> t <sub>TL</sub>    | 2                    |     | t <sub>cyc</sub> |

| Timer input capture period      | t <sub>TLTL</sub>                   | Note <sup>(1)</sup>  |     | t <sub>cyc</sub> |

| Timer input clock pulse width   | t <sub>TCL</sub> , t <sub>TCH</sub> | t <sub>cyc</sub> + 5 | —   | ns               |

1. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1  $t_{cyc}$ .

Figure 16-8. Timer Input Timing

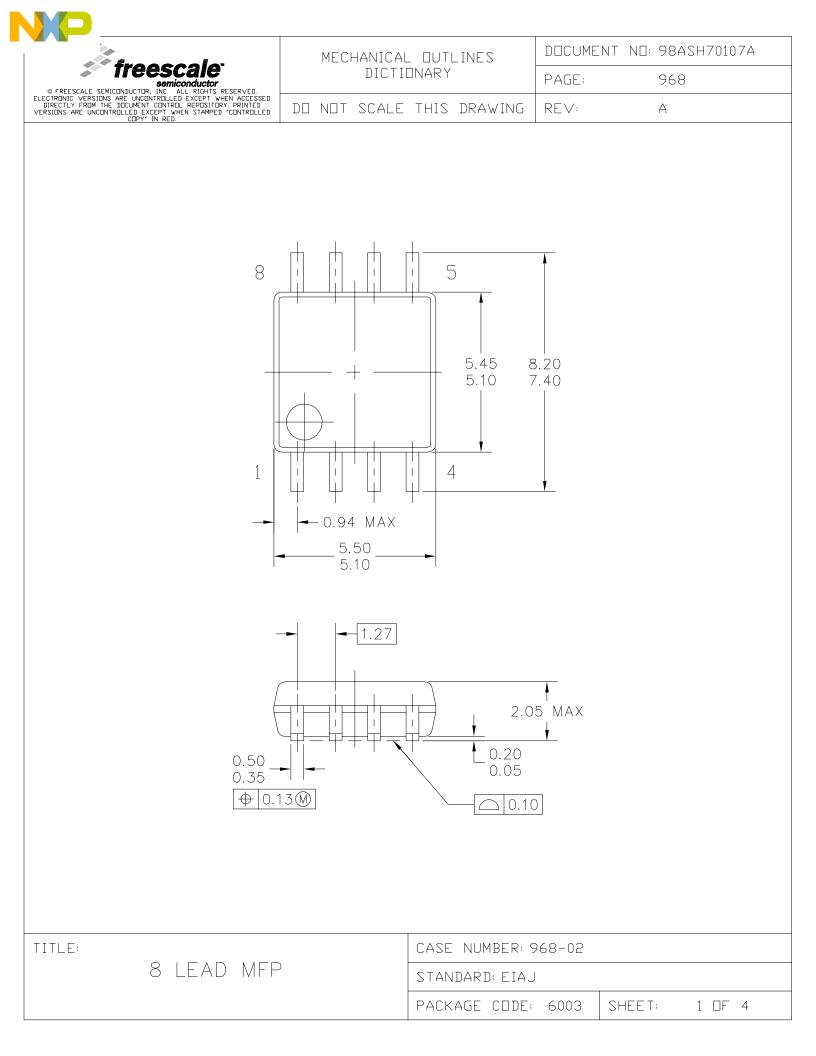

|                  |                                                                                                                                                  | MECHANICAL OUTLINES |       |       | INES    | DOCUMENT NO: 98ASH70107A |     |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|-------|---------|--------------------------|-----|--|

| © FREESCALE SEM  | Treescale<br>somiconductor<br>NICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                                             |                     | DICTI | ONARY |         | PAGE:                    | 968 |  |

| DIRECTLY FROM TH | NS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>HE DOCUMENT CONTROL REPOSITORY. PRINTED<br>NTROLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NOT              | SCALE | THIS  | DRAWING | REV:                     | А   |  |

NOTES:

1. DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEDD 0.15mm PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

5. THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION SHALL BE 0.08mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46mm.

|  | CASE NUMBER: 968-02 |               |  |  |  |

|--|---------------------|---------------|--|--|--|

|  | STANDARD: EIAJ      |               |  |  |  |

|  | PACKAGE CODE: 6003  | SHEET: 3 OF 4 |  |  |  |

|                     |                                                                                                                                        | ME    | CHANICA | L OUTI | INES    | DOCUMENT | NO: 98ARL10557D |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|---------|--------|---------|----------|-----------------|

|                     | TEESCALE<br>semiconductor<br>NDUCTOR, INC. ALL RIGHTS RESERVED.                                                                        |       | DICTI   | ONARY  |         | PAGE:    | 1452            |

| DIRECTLY FROM THE D | ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>OCUMENT CONTROL REPOSITORY. PRINTED<br>DLLED EXCEPT WHEN STAMPED "CONTROLLED<br>COPY" IN RED. | DO NO | T SCALE | THIS   | DRAWING | REV:     | А               |

NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HP-VFDFP-N.

4. COPLANARITY APPLIES TO LEADS AND DIE ATTACH PAD.

| TITLE:THERMALLY ENHANCED DUAL                  | CASE NUMBER: 1452-01             |

|------------------------------------------------|----------------------------------|

| FLAT NO LEAD PACKAGE (DFN)                     | STANDARD: NON-JEDEC              |

| 8 TERMINAL, 0. 8 PITCH $(4 \times 4 \times 1)$ | PACKAGE CODE: 6165 SHEET: 4 OF 5 |