Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                        |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                      |

| Core Size                  | 16/32-Bit                                                                  |

| Speed                      | 60MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART    |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 112                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 144-LQFP                                                                   |

| Supplier Device Package    | 144-LQFP (20x20)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc2292fbd144-01-5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1.

Ordering information ...continued

| Type number      | Package |                                                                                        |          |  |  |  |

|------------------|---------|----------------------------------------------------------------------------------------|----------|--|--|--|

|                  | Name    | Description                                                                            | Version  |  |  |  |

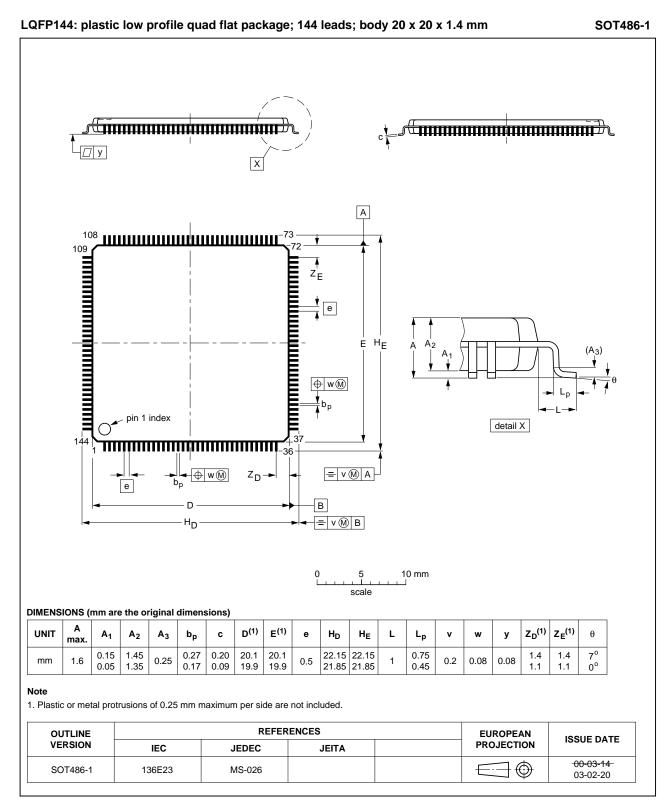

| LPC2294HBD144    | LQFP144 | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm    | SOT486-1 |  |  |  |

| LPC2294HBD144/00 | LQFP144 | plastic low profile quad flat package;<br>144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |  |  |

| LPC2294HBD144/01 | LQFP144 | plastic low profile quad flat package;<br>144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |  |  |

## 3.1 Ordering options

## Table 2. Ordering options

| Type number      | Flash<br>memory | RAM   | CAN        | Fast GPIO/<br>SSP/<br>Enhanced<br>UART, ADC,<br>Timer | Temperature range |

|------------------|-----------------|-------|------------|-------------------------------------------------------|-------------------|

| LPC2292FBD144/01 | 256 kB          | 16 kB | 2 channels | yes                                                   | –40 °C to +85 °C  |

| LPC2292FET144/00 | 256 kB          | 16 kB | 2 channels | no                                                    | –40 °C to +85 °C  |

| LPC2292FET144/01 | 256 kB          | 16 kB | 2 channels | yes                                                   | –40 °C to +85 °C  |

| LPC2292FET144/G  | 256 kB          | 16 kB | 2 channels | no                                                    | –40 °C to +85 °C  |

| LPC2294HBD144    | 256 kB          | 16 kB | 4 channels | no                                                    | –40 °C to +125 °C |

| LPC2294HBD144/00 | 256 kB          | 16 kB | 4 channels | no                                                    | –40 °C to +125 °C |

| LPC2294HBD144/01 | 256 kB          | 16 kB | 4 channels | yes                                                   | –40 °C to +125 °C |

#### 16/32-bit ARM microcontrollers with external memory interface

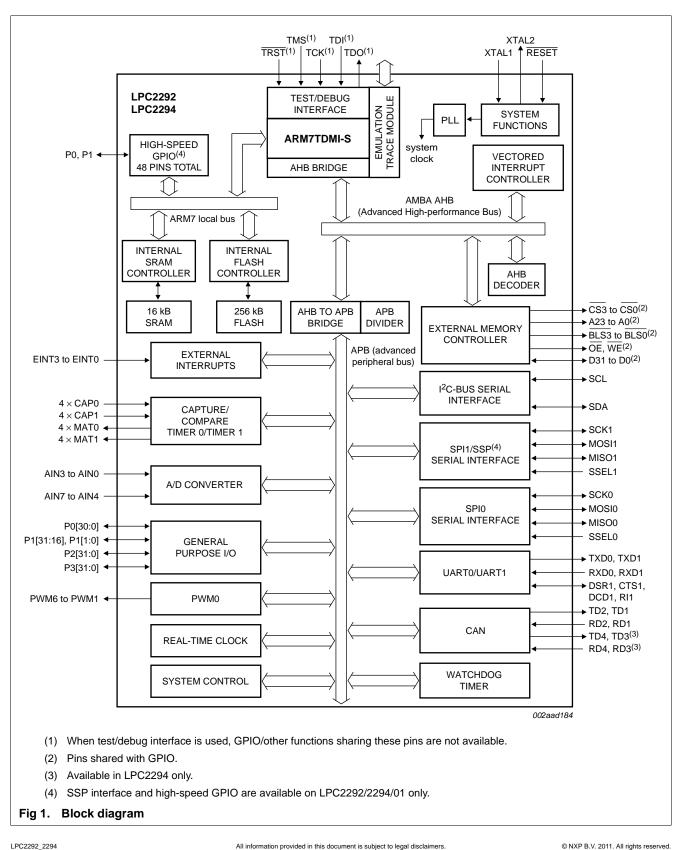

#### 4. Block diagram

Product data sheet

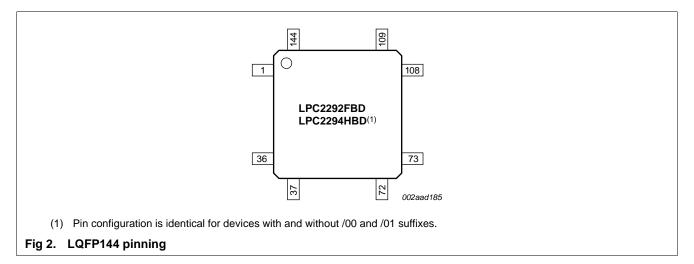

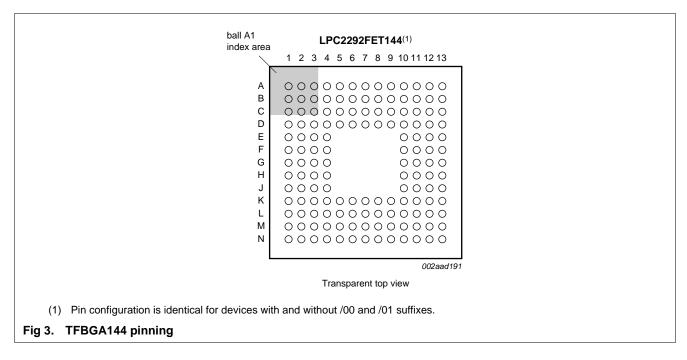

## 5. Pinning information

## 5.1 Pinning

## 5.2 Pin description

| Table 4. Pin o              | description              |                                      |      |                                                                                                                                                                                                          |

|-----------------------------|--------------------------|--------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                      | Pin (LQFP)               | Pin<br>(TFBGA) <u><sup>[1]</sup></u> | Туре | Description                                                                                                                                                                                              |

| P0[0] to P0[31]             |                          |                                      | I/O  | <b>Port 0:</b> Port 0 is a 32-bit bidirectional I/O port with individual direction controls for each bit. The operation of port 0 pins depends upon the pin function selected via the Pin Connect Block. |

|                             |                          |                                      |      | Pins 26 and 31 of port 0 are not available.                                                                                                                                                              |

| P0[0]/TXD0/                 | 42 <u>[2]</u>            | L4 <u>[2]</u>                        | 0    | <b>TXD0</b> — Transmitter output for UART0.                                                                                                                                                              |

| PWM1                        |                          |                                      | 0    | <b>PWM1</b> — Pulse Width Modulator output 1.                                                                                                                                                            |

| P0[1]/RXD0/                 | 49 <u><sup>[4]</sup></u> | K6 <u><sup>[4]</sup></u>             | 1    | <b>RXD0</b> — Receiver input for UART0.                                                                                                                                                                  |

| PWM3/EINT0                  |                          |                                      | 0    | PWM3 — Pulse Width Modulator output 3.                                                                                                                                                                   |

|                             |                          |                                      | Ι    | EINT0 — External interrupt 0 input                                                                                                                                                                       |

| P0[2]/SCL/<br>CAP0[0]       | 50 <u>[5]</u>            | L6[5]                                | I/O  | <b>SCL</b> — I <sup>2</sup> C-bus clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                           |

|                             |                          |                                      | I    | CAP0[0] — Capture input for Timer 0, channel 0.                                                                                                                                                          |

| P0[3]/SDA/<br>MAT0[0]/EINT1 | 58 <u>[5]</u>            | M8 <u>[5]</u>                        | I/O  | <b>SDA</b> — I <sup>2</sup> C-bus data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                            |

|                             |                          |                                      | 0    | MAT0[0] — Match output for Timer 0, channel 0.                                                                                                                                                           |

|                             |                          |                                      | I    | EINT1 — External interrupt 1 input.                                                                                                                                                                      |

| P0[4]/SCK0/<br>CAP0[1]      | 59 <u>[2]</u>            | L8 <u>[2]</u>                        | I/O  | <b>SCK0</b> — Serial clock for SPI0. SPI clock output from master or input to slave.                                                                                                                     |

|                             |                          |                                      | I    | CAP0[1] — Capture input for Timer 0, channel 1.                                                                                                                                                          |

| P0[5]/MISO0/<br>MAT0[1]     | 61 <u>[2]</u>            | N9 <u>[2]</u>                        | I/O  | <b>MISO0</b> — Master In Slave OUT for SPI0. Data input to SPI master or data output from SPI slave.                                                                                                     |

|                             |                          |                                      | 0    | MAT0[1] — Match output for Timer 0, channel 1.                                                                                                                                                           |

| P0[6]/MOSI0/<br>CAP0[2]     | 68 <u>[2]</u>            | N11 <sup>[2]</sup>                   | I/O  | <b>MOSI0</b> — Master Out Slave In for SPI0. Data output from SPI master or data input to SPI slave.                                                                                                     |

|                             |                          |                                      | I    | CAP0[2] — Capture input for Timer 0, channel 2.                                                                                                                                                          |

| P0[7]/SSEL0/<br>PWM2/EINT2  | 69 <u>[4]</u>            | M11[4]                               | Ι    | <b>SSEL0</b> — Slave Select for SPI0. Selects the SPI interface as a slave.                                                                                                                              |

|                             |                          |                                      | 0    | <b>PWM2</b> — Pulse Width Modulator output 2.                                                                                                                                                            |

|                             |                          |                                      | I    | EINT2 — External interrupt 2 input.                                                                                                                                                                      |

| P0[8]/TXD1/                 | 75 <u>[2]</u>            | L12 <sup>[2]</sup>                   | 0    | <b>TXD1</b> — Transmitter output for UART1.                                                                                                                                                              |

| PWM4                        |                          |                                      | 0    | <b>PWM4</b> — Pulse Width Modulator output 4.                                                                                                                                                            |

| P0[9]/RXD1/                 | 76 <u><sup>[4]</sup></u> | L13 <sup>[4]</sup>                   | I    | <b>RXD1</b> — Receiver input for UART1.                                                                                                                                                                  |

| PWM6/EINT3                  |                          |                                      | 0    | <b>PWM6</b> — Pulse Width Modulator output 6.                                                                                                                                                            |

|                             |                          |                                      | Ι    | EINT3 — External interrupt 3 input.                                                                                                                                                                      |

| P0[10]/RTS1/                | 78 <u>[2]</u>            | K11 <sup>[2]</sup>                   | 0    | RTS1 — Request to Send output for UART1.                                                                                                                                                                 |

| CAP1[0]                     |                          |                                      | I    | CAP1[0] — Capture input for Timer 1, channel 0.                                                                                                                                                          |

| P0[11]/CTS1/                | 83 <u>[2]</u>            | J12 <sup>[2]</sup>                   | I    | <b>CTS1</b> — Clear to Send input for UART1.                                                                                                                                                             |

| CAP1[1]                     |                          |                                      | I    | CAP1[1] — Capture input for Timer 1, channel 1.                                                                                                                                                          |

LPC2292\_2294

## 16/32-bit ARM microcontrollers with external memory interface

|                      |                           | Pin<br>(TFBGA) <u><sup>[1]</sup></u> | Туре | Description                                                                                                              |

|----------------------|---------------------------|--------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------|

| P0[12]/DSR1/         | 84 <u>[2]</u>             | J13[2]                               | I    | <b>DSR1</b> — Data Set Ready input for UART1.                                                                            |

| MAT1[0]/RD4          |                           |                                      | 0    | MAT1[0] — Match output for Timer 1, channel 0.                                                                           |

|                      |                           |                                      | I    | RD4 — CAN4 receiver input (LPC2294 only).                                                                                |

| P0[13]/DTR1/         | 85 <u>[2]</u>             | H10 <sup>[2]</sup>                   | 0    | <b>DTR1</b> — Data Terminal Ready output for UART1.                                                                      |

| MAT1[1]/TD4          |                           |                                      | 0    | MAT1[1] — Match output for Timer 1, channel 1.                                                                           |

|                      |                           |                                      | 0    | TD4 — CAN4 transmitter output (LPC2294 only).                                                                            |

| P0[14]/DCD1/         | 92 <sup>[4]</sup>         | G10 <sup>[4]</sup>                   | Ι    | DCD1 — Data Carrier Detect input for UART1.                                                                              |

| EINT1                |                           |                                      | Ι    | EINT1 — External interrupt 1 input.                                                                                      |

|                      |                           |                                      |      | <b>Note:</b> LOW on this pin while RESET is LOW forces on-chip bootloader to take over control of the part after reset.  |

| P0[15]/RI1/          | 99 <u>[4]</u>             | E11[4]                               | I    | RI1 — Ring Indicator input for UART1.                                                                                    |

| EINT2                |                           |                                      | Ι    | EINT2 — External interrupt 2 input.                                                                                      |

| P0[16]/EINT0/        | 100 <u><sup>[4]</sup></u> | E10 <sup>[4]</sup>                   | I    | EINT0 — External interrupt 0 input.                                                                                      |

| MAT0[2]/             |                           |                                      | 0    | MAT0[2] — Match output for Timer 0, channel 2.                                                                           |

| CAP0[2]              |                           |                                      | Ι    | CAP0[2] — Capture input for Timer 0, channel 2.                                                                          |

| P0[17]/CAP1[2]/      | 101 <u>[2]</u>            | D13 <sup>[2]</sup>                   | I    | CAP1[2] — Capture input for Timer 1, channel 2.                                                                          |

| SCK1/MAT1[2]         |                           |                                      | I/O  | SCK1 — Serial Clock for SPI1/SSP <sup>[3]</sup> . SPI clock output from master or input to slave.                        |

|                      |                           |                                      | 0    | MAT1[2] — Match output for Timer 1, channel 2.                                                                           |

| P0[18]/CAP1[3]/      | 121 <u>[2]</u>            | D8[2]                                | I    | CAP1[3] — Capture input for Timer 1, channel 3.                                                                          |

| MISO1/MAT1[3]        |                           |                                      | I/O  | <b>MISO1</b> — Master In Slave Out for SPI1/SSP <sup>[3]</sup> . Data input to SPI master or data output from SPI slave. |

|                      |                           |                                      | 0    | MAT1[3] — Match output for Timer 1, channel 3.                                                                           |

| P0[19]/MAT1[2]/      | 122 <sup>[2]</sup>        | C8 <sup>[2]</sup>                    | 0    | MAT1[2] — Match output for Timer 1, channel 2.                                                                           |

| MOSI1/CAP1[2]        |                           |                                      | I/O  | <b>MOSI1</b> — Master Out Slave In for SPI1/SSP <sup>[3]</sup> . Data output from SPI master or data input to SPI slave. |

|                      |                           |                                      | Ι    | CAP1[2] — Capture input for Timer 1, channel 2.                                                                          |

| P0[20]/MAT1[3]/      | 123 <u><sup>[4]</sup></u> | B8[4]                                | 0    | MAT1[3] — Match output for Timer 1, channel 3.                                                                           |

| SSEL1/EINT3          |                           |                                      | I    | <b>SSEL1</b> — Slave Select for SPI1/SSP <sup>I3</sup> . Selects the SPI interface as a slave.                           |

|                      |                           |                                      | Ι    | EINT3 — External interrupt 3 input.                                                                                      |

| P0[21]/PWM5/         | 4 <u>[2]</u>              | C1 <sup>[2]</sup>                    | 0    | <b>PWM5</b> — Pulse Width Modulator output 5.                                                                            |

| RD3/CAP1[3]          |                           |                                      | I    | RD3 — CAN3 receiver input (LPC2294 only).                                                                                |

|                      |                           |                                      | Ι    | CAP1[3] — Capture input for Timer 1, channel 3.                                                                          |

| P0[22]/TD3/          | 5 <u>[2]</u>              | D4 <u><sup>[2]</sup></u>             | 0    | TD3 — CAN3 transmitter output (LPC2294 only).                                                                            |

| CAP0[0]/<br>//AT0[0] |                           |                                      | I    | <b>CAP0[0]</b> — Capture input for Timer 0, channel 0.                                                                   |

|                      |                           |                                      | 0    | <b>MAT0[0]</b> — Match output for Timer 0, channel 0.                                                                    |

| P0[23]/RD2           | 6 <u>[2]</u>              | D3 <u>[2]</u>                        | I    | RD2 — CAN2 receiver input.                                                                                               |

| P0[24]/TD2           | 8 <u>[2]</u>              | D1 <u>[2]</u>                        | 0    | <b>TD2</b> — CAN2 transmitter output.                                                                                    |

| P0[25]/RD1           | 21 <sup>[2]</sup>         | H1[2]                                | I    | RD1 — CAN1 receiver input.                                                                                               |

LPC2292\_2294

## 16/32-bit ARM microcontrollers with external memory interface

| Symbol          | Pin (LQFP)               | Pin<br>(TFBGA) <u><sup>[1]</sup></u> | Туре | Description                                                                                                                                                                                                                                                                                                                                    |

|-----------------|--------------------------|--------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2[24]/D24      | 11[7]                    | E2[7]                                | I/O  | <b>D24</b> — External memory data line 24.                                                                                                                                                                                                                                                                                                     |

| P2[25]/D25      | 12 <u>[7]</u>            | E1[7]                                | I/O  | D25 — External memory data line 25.                                                                                                                                                                                                                                                                                                            |

| P2[26]/D26/     | 13 <u>[7]</u>            | F4 <u>[7]</u>                        | I/O  | <b>D26</b> — External memory data line 26.                                                                                                                                                                                                                                                                                                     |

| BOOTO           | -                        |                                      | 1    | <b>BOOT0</b> — While RESET is low, together with BOOT1 controls booting and internal operation. Internal pull-up ensures high state if pin is left unconnected.                                                                                                                                                                                |

| P2[27]/D27/     | 16 <u>[7]</u>            | F1[7]                                | I/O  | <b>D27</b> — External memory data line 27.                                                                                                                                                                                                                                                                                                     |

| BOOT1           |                          |                                      | Ι    | <b>BOOT1</b> — While $\overline{\text{RESET}}$ is low, together with BOOT0<br>controls booting and internal operation. Internal pull-up<br>ensures high state if pin is left unconnected.<br>BOOT1:0 = 00 selects 8-bit memory on $\overline{\text{CS0}}$ for boot.<br>BOOT1:0 = 01 selects 16-bit memory on $\overline{\text{CS0}}$ for boot. |

|                 |                          |                                      |      | BOOT1:0 = 10 selects 32-bit memory on $\overline{CS0}$ for boot.                                                                                                                                                                                                                                                                               |

|                 |                          |                                      |      | BOOT1:0 = 11 selects internal flash memory.                                                                                                                                                                                                                                                                                                    |

| P2[28]/D28      | 17 <u>[7]</u>            | G2[7]                                | I/O  | <b>D28</b> — External memory data line 28.                                                                                                                                                                                                                                                                                                     |

| P2[29]/D29      | 18 <u>[7]</u>            | G1[7]                                | I/O  | <b>D29</b> — External memory data line 29.                                                                                                                                                                                                                                                                                                     |

| P2[30]/D30/     | 19 <u><sup>[6]</sup></u> | G3 <u>[6]</u>                        | I/O  | <b>D30</b> — External memory data line 30.                                                                                                                                                                                                                                                                                                     |

| AIN4            |                          |                                      | Ι    | <b>AIN4</b> — ADC, input 4. This analog input is always connected to its pin.                                                                                                                                                                                                                                                                  |

| P2[31]/D31/     | 20 <u>[6]</u>            | G4 <u><sup>[6]</sup></u>             | I/O  | D31 — External memory data line 31.                                                                                                                                                                                                                                                                                                            |

| AIN5            |                          |                                      | I    | <b>AIN5</b> — ADC, input 5. This analog input is always connected to its pin.                                                                                                                                                                                                                                                                  |

| P3[0] to P3[31] |                          |                                      | I/O  | <b>Port 3</b> — Port 3 is a 32-bit bidirectional I/O port with individual direction controls for each bit. The operation of port 3 pins depends upon the pin function selected via the Pin Connect Block.                                                                                                                                      |

| P3[0]/A0        | 89 <u>[7]</u>            | G12 <sup>[7]</sup>                   | 0    | A0 — External memory address line 0.                                                                                                                                                                                                                                                                                                           |

| P3[1]/A1        | 88 <u>[7]</u>            | H13 <sup>[7]</sup>                   | 0    | A1 — External memory address line 1.                                                                                                                                                                                                                                                                                                           |

| P3[2]/A2        | 87 <u>[7]</u>            | H12 <sup>[7]</sup>                   | 0    | A2 — External memory address line 2.                                                                                                                                                                                                                                                                                                           |

| P3[3]/A3        | 81 <u>[7]</u>            | J10 <sup>[7]</sup>                   | 0    | A3 — External memory address line 3.                                                                                                                                                                                                                                                                                                           |

| P3[4]/A4        | 80 <u>[7]</u>            | K13 <u>[7]</u>                       | 0    | A4 — External memory address line 4.                                                                                                                                                                                                                                                                                                           |

| P3[5]/A5        | 74 <u>[7]</u>            | M13[7]                               | 0    | A5 — External memory address line 5.                                                                                                                                                                                                                                                                                                           |

| P3[6]/A6        | 73 <u>[7]</u>            | N13 <sup>[7]</sup>                   | 0    | A6 — External memory address line 6.                                                                                                                                                                                                                                                                                                           |

| P3[7]/A7        | 72 <u>[7]</u>            | M12 <sup>[7]</sup>                   | 0    | A7 — External memory address line 7.                                                                                                                                                                                                                                                                                                           |

| P3[8]/A8        | 71 <u>[7]</u>            | N12[7]                               | 0    | A8 — External memory address line 8.                                                                                                                                                                                                                                                                                                           |

| P3[9]/A9        | 66 <u>[7]</u>            | M10 <sup>[7]</sup>                   | 0    | A9 — External memory address line 9.                                                                                                                                                                                                                                                                                                           |

| P3[10]/A10      | 65 <u>[7]</u>            | N10 <sup>[7]</sup>                   | 0    | A10 — External memory address line 10.                                                                                                                                                                                                                                                                                                         |

| P3[11]/A11      | 64 <u>[7]</u>            | K9 <u>[7]</u>                        | 0    | A11 — External memory address line 11.                                                                                                                                                                                                                                                                                                         |

| P3[12]/A12      | 63 <u>[7]</u>            | L9 <u>[7]</u>                        | 0    | A12 — External memory address line 12.                                                                                                                                                                                                                                                                                                         |

| P3[13]/A13      | 62 <u>[7]</u>            | M9 <u>[7]</u>                        | 0    | A13 — External memory address line 13.                                                                                                                                                                                                                                                                                                         |

| P3[14]/A14      | 56 <u>[7]</u>            | K7[7]                                | 0    | A14 — External memory address line 14.                                                                                                                                                                                                                                                                                                         |

| P3[15]/A15      | 55 <u>[7]</u>            | L7[ <u>7]</u>                        | 0    | A15 — External memory address line 15.                                                                                                                                                                                                                                                                                                         |

| P3[16]/A16      | 53 <u>[7]</u>            | M7 <u>[7]</u>                        | 0    | A16 — External memory address line 16.                                                                                                                                                                                                                                                                                                         |

Product data sheet

| Table 5. Interr | rupt sourcescontinued                                                           |               |

|-----------------|---------------------------------------------------------------------------------|---------------|

| Block           | Flag(s)                                                                         | VIC channel # |

| UART1           | RX Line Status (RLS)                                                            | 7             |

|                 | Transmit Holding Register empty (THRE)                                          |               |

|                 | RX Data Available (RDA)                                                         |               |

|                 | Character Time-out Indicator (CTI)                                              |               |

|                 | Modem Status Interrupt (MSI)                                                    |               |

|                 | Auto-baud time-out (ABTO) <sup>[1]</sup> End of auto-baud (ABEO) <sup>[1]</sup> |               |

| PWM0            | Match 0 to 6 (MR0, MR1, MR2, MR3, MR4, MR5, MR6)                                | 8             |

| I2C             | SI (state change)                                                               | 9             |

| SPI0            | SPIF, MODF                                                                      | 10            |

| SPI1 and SSP[1] | SPIF, MODF and TXRIS, RXRIS, RTRIS, RORRIS                                      | 11            |

| PLL             | PLL Lock (PLOCK)                                                                | 12            |

| RTC             | RTCCIF (Counter Increment), RTCALF (Alarm)                                      | 13            |

| System Control  | External Interrupt 0 (EINT0)                                                    | 14            |

|                 | External Interrupt 1 (EINT1)                                                    | 15            |

|                 | External Interrupt 2 (EINT2)                                                    | 16            |

|                 | External Interrupt 3 (EINT3)                                                    | 17            |

| ADC             | ADC                                                                             | 18            |

| CAN             | 1 ORed CAN Acceptance Filter                                                    | 19            |

|                 | CAN1/2 Tx                                                                       | 20, 21        |

|                 | CAN2/3 Tx (LPC2294 only)                                                        | 22, 23        |

|                 | reserved                                                                        | 24, 25        |

|                 | CAN1/2 Rx                                                                       | 26, 27        |

|                 | CAN3/4 Rx (LPC2294 only)                                                        | 28,29         |

[1] SSP interface and UART0/1 auto-baud control are available on LPC2292/2294/01 only.

## 6.6 Pin connect block

The pin connect block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on chip peripherals. Peripherals should be connected to the appropriate pins prior to being activated, and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

## 6.7 External memory controller

The external Static Memory Controller is a module which provides an interface between the system bus and external (off-chip) memory devices. It provides support for up to four independently configurable memory banks (16 MB each with byte lane enable control) simultaneously. Each memory bank is capable of supporting SRAM, ROM, flash EPROM, burst ROM memory, or some external I/O devices.

Each memory bank may be 8-bit, 16-bit, or 32-bit wide.

### 6.15.2 Features available in LPC2292/2294/01 only

The LPC2292/2294/01 can count external events on one of the capture inputs if the external pulse lasts at least one half of the period of the PCLK. In this configuration, unused capture lines can be selected as regular timer capture inputs, or used as external interrupts.

- Timer can count cycles of either the peripheral clock (PCLK) or an externally supplied clock.

- When counting cycles of an externally supplied clock, only one of the timer's capture inputs can be selected as the timer's clock. The rate of such a clock is limited to PCLK / 4. Duration of HIGH/LOW levels on the selected CAP input cannot be shorter than 1 / (2PCLK).

## 6.16 Watchdog timer

The purpose of the watchdog is to reset the microcontroller within a reasonable amount of time if it enters an erroneous state. When enabled, the watchdog will generate a system reset if the user program fails to 'feed' (or reload) the watchdog within a predetermined amount of time.

## 6.16.1 Features

- Internally resets chip if not periodically reloaded.

- Debug mode.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 32-bit timer with internal prescaler.

- Selectable time period from (T<sub>cy(PCLK)</sub> × 256 × 4) to (T<sub>cy(PCLK)</sub> × 2<sup>32</sup> × 4) in multiples of T<sub>cy(PCLK)</sub> × 4.

## 6.17 Real-time clock

The Real-Time Clock (RTC) is designed to provide a set of counters to measure time when normal or idle operating mode is selected. The RTC has been designed to use little power, making it suitable for battery powered systems where the CPU is not running continuously (Idle mode).

### 6.17.1 Features

- Measures the passage of time to maintain a calendar and clock.

- Ultra-low power design to support battery powered systems.

- Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year.

- Programmable Reference Clock Divider allows adjustment of the RTC to match various crystal frequencies.

## 6.18 Pulse width modulator

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC2292/2294. The Timer is designed to count cycles of the peripheral clock (PCLK) and optionally generate interrupts or perform other actions when specified timer values occur, based on seven match registers. The PWM function is also based on match register events.

The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (MR0) controls the PWM cycle rate, by resetting the count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an MR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the MR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

### 6.18.1 Features

- Seven match registers allow up to six single edge controlled or three double edge controlled PWM outputs, or a mix of both types.

- The match registers also allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Supports single edge controlled and/or double edge controlled PWM outputs. Single edge controlled PWM outputs all go HIGH at the beginning of each cycle unless the output is a constant LOW. Double edge controlled PWM outputs can have either edge occur at any position within a cycle. This allows for both positive going and negative going pulses.

- Pulse period and width can be any number of timer counts. This allows complete flexibility in the trade-off between resolution and repetition rate. All PWM outputs will occur at the same repetition rate.

- Double edge controlled PWM outputs can be programmed to be either positive going or negative going pulses.

- Match register updates are synchronized with pulse outputs to prevent generation of erroneous pulses. Software must 'release' new match values before they can become effective.

- May be used as a standard timer if the PWM mode is not enabled.

- A 32-bit Timer/Counter with a programmable 32-bit prescaler.

## 6.19 System control

### 6.19.1 Crystal oscillator

The oscillator supports crystals in the range of 1 MHz to 25 MHz. The oscillator output frequency is called  $f_{osc}$  and the ARM processor clock frequency is referred to as CCLK for purposes of rate equations, etc.  $f_{osc}$  and CCLK are the same value unless the PLL is running and connected. Refer to <u>Section 6.19.2 "PLL"</u> for additional information.

## 6.19.2 PLL

The PLL accepts an input clock frequency in the range of 10 MHz to 25 MHz. The input frequency is multiplied up into the range of 10 MHz to 60 MHz with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32 (in practice, the multiplier value cannot be higher than 6 on this family of microcontrollers due to the upper frequency limit of the CPU). The CCO operates in the range of 156 MHz to 320 MHz, so there is an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The output divider may be set to divide by 2, 4, 8, or 16 to produce the output clock. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset and may be enabled by software. The program must configure and activate the PLL, wait for the PLL to Lock, then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

### 6.19.3 Reset and wake-up timer

Reset has two sources on the LPC2292/2294: the RESET pin and watchdog reset. The RESET pin is a Schmitt trigger input pin with an additional glitch filter. Assertion of chip reset by any source starts the Wake-up Timer (see Wake-up Timer description below), causing the internal chip reset to remain asserted until the external reset is de-asserted, the oscillator is running, a fixed number of clocks have passed, and the on-chip flash controller has completed its initialization.

When the internal reset is removed, the processor begins executing at address 0, which is the reset vector. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

The Wake-up Timer ensures that the oscillator and other analog functions required for chip operation are fully functional before the processor is allowed to execute instructions. This is important at power-on, all types of reset, and whenever any of the aforementioned functions are turned off for any reason. Since the oscillator and other functions are turned off during Power-down mode, any wake-up of the processor from Power-down mode makes use of the Wake-up Timer.

## 8. Static characteristics

## Table 7. Static characteristics

$T_{amb} = -40$  °C to +125 °C, unless otherwise specified.

| Symbol                | Parameter                                  | Conditions                                                                                |                      | Min                 | Typ <u>[1]</u> | Max                  | Unit |

|-----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------|----------------------|---------------------|----------------|----------------------|------|

| V <sub>DD(1V8)</sub>  | supply voltage (1.8 V)                     |                                                                                           | [2]                  | 1.65                | 1.8            | 1.95                 | V    |

| V <sub>DD(3V3)</sub>  | supply voltage (3.3 V)                     |                                                                                           | [3]                  | 3.0                 | 3.3            | 3.6                  | V    |

| V <sub>DDA(3V3)</sub> | analog supply voltage<br>(3.3 V)           |                                                                                           |                      | 2.5                 | 3.3            | 3.6                  | V    |

| Standard              | port pins, RESET, RTCK                     |                                                                                           |                      |                     |                |                      |      |

| IIL                   | LOW-level input current                    | V <sub>I</sub> = 0 V; no pull-up                                                          |                      | -                   | -              | 3                    | μA   |

| I <sub>IH</sub>       | HIGH-level input current                   | $V_{I} = V_{DD(3V3)}$ ; no pull-down                                                      |                      | -                   | -              | 3                    | μA   |

| I <sub>OZ</sub>       | OFF-state output current                   | $V_O = 0 V$ , $V_O = V_{DD(3V3)}$ ;<br>no pull-up/down                                    |                      | -                   | -              | 3                    | μΑ   |

| I <sub>latch</sub>    | I/O latch-up current                       | –(0.5V <sub>DD(3V3)</sub> ) < V₁ <<br>(1.5V <sub>DD(3V3)</sub> ); T <sub>j</sub> < 125 °C |                      | 100                 | -              | -                    | mA   |

| VI                    | input voltage                              |                                                                                           | <u>[4][5]</u><br>[6] | 0                   | -              | 5.5                  | V    |

| Vo                    | output voltage                             | output active                                                                             |                      | 0                   | -              | V <sub>DD(3V3)</sub> | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                   |                                                                                           |                      | 2.0                 | -              | -                    | V    |

| V <sub>IL</sub>       | LOW-level input voltage                    |                                                                                           |                      | -                   | -              | 0.8                  | V    |

| V <sub>hys</sub>      | hysteresis voltage                         |                                                                                           |                      | 0.4                 | -              | -                    | V    |

| V <sub>OH</sub>       | HIGH-level output voltage                  | I <sub>OH</sub> = -4 mA                                                                   | [7]                  | $V_{DD(3V3)} - 0.4$ | -              | -                    | V    |

| V <sub>OL</sub>       | LOW-level output voltage                   | I <sub>OL</sub> = 4 mA                                                                    | [7]                  | -                   | -              | 0.4                  | V    |

| I <sub>OH</sub>       | HIGH-level output current                  | $V_{OH} = V_{DD(3V3)} - 0.4 V$                                                            | [7]                  | -4                  | -              | -                    | mA   |

| I <sub>OL</sub>       | LOW-level output current                   | V <sub>OL</sub> = 0.4 V                                                                   | [7]                  | 4                   | -              | -                    | mA   |

| I <sub>OHS</sub>      | HIGH-level short-circuit<br>output current | V <sub>OH</sub> = 0 V                                                                     | [8]                  | -                   | -              | -45                  | mA   |

| I <sub>OLS</sub>      | LOW-level short-circuit<br>output current  | $V_{OL} = V_{DD(3V3)}$                                                                    | [8]                  | -                   | -              | 50                   | mA   |

| I <sub>pd</sub>       | pull-down current                          | V <sub>I</sub> = 5 V                                                                      | [9]                  | 10                  | 50             | 150                  | μA   |

| I <sub>pu</sub>       | pull-up current                            | V <sub>I</sub> = 0 V                                                                      | [10]                 | –15                 | -50            | -85                  | μA   |

|                       |                                            | $V_{DD(3V3)} < V_{I} < 5 V$                                                               | [9]                  | 0                   | 0              | 0                    | μA   |

|                       |                                            |                                                                                           |                      |                     |                |                      |      |

## LPC2292/2294

# LPC2292/2294

# LPC2292/2294

# LPC2292/2294

| Core voltage 1.8 V; $T_{amb} = 25 \text{ °C}$ ; all measurements in $\mu A$ ; PCLK = <sup>CCLK</sup> / <sub>4</sub> ; all peripherals enabled. |               |               |               |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|--|--|

| Peripheral                                                                                                                                     | CCLK = 12 MHz | CCLK = 48 MHz | CCLK = 60 MHz |  |  |

| PWM0                                                                                                                                           | 103           | 341           | 407           |  |  |

| l <sup>2</sup> C-bus                                                                                                                           | 9             | 37            | 53            |  |  |

| SPI0/1                                                                                                                                         | 6             | 27            | 29            |  |  |

| RTC                                                                                                                                            | 16            | 55            | 78            |  |  |

| PCEMC                                                                                                                                          | 306           | 994           | 1205          |  |  |

| ADC                                                                                                                                            | 33            | 128           | 167           |  |  |

| CAN1/2                                                                                                                                         | 229           | 771           | 914           |  |  |

**Table 9.** Typical LPC2292/01 peripheral power consumption in active mode ... continued Core voltage 1.8 V:  $T_{exc} = 25 \, \%$ : all measurements in uA: PCLK = CCLK/c: all peripherals enabled

Table 10.

Typical LPC2294/01 peripheral power consumption in active mode

Core voltage 1.8 V;  $T_{amb} = 25 \, ^{\circ}$ C; all measurements in  $\mu$ A; PCLK = <sup>CCLK</sup>/<sub>4</sub>; all peripherals enabled.

| -                    |               |               |               |

|----------------------|---------------|---------------|---------------|

| Peripheral           | CCLK = 12 MHz | CCLK = 48 MHz | CCLK = 60 MHz |

| Timer0               | 43            | 141           | 184           |

| Timer1               | 46            | 150           | 180           |

| UART0                | 98            | 320           | 398           |

| UART1                | 103           | 351           | 421           |

| PWM0                 | 103           | 341           | 407           |

| l <sup>2</sup> C-bus | 9             | 37            | 53            |

| SPI0/1               | 6             | 27            | 29            |

| RTC                  | 16            | 55            | 78            |

| PCEMC                | 306           | 994           | 1205          |

| ADC                  | 33            | 128           | 167           |

| CAN1/2/3/4           | 230           | 769           | 912           |

|                      |               |               |               |

## 9. Dynamic characteristics

### Table 11. Dynamic characteristics

$T_{amb} = -40 \text{ °C to } +125 \text{ °C}; V_{DD(1V8)}, V_{DD(3V3)} \text{ over specified ranges.}$ [1]

| Symbol               | Parameter            | Conditions                                                                             | Min                                                     | Тур | Max  | Unit |

|----------------------|----------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------|-----|------|------|

| External cloc        | :k                   |                                                                                        |                                                         |     |      |      |

| f <sub>osc</sub> os  | oscillator frequency | supplied by an external oscillator (signal generator)                                  | 1                                                       | -   | 25   | MHz  |

|                      |                      | external clock frequency<br>supplied by an external<br>crystal oscillator              | 1                                                       | -   | 25   | MHz  |

|                      |                      | external clock frequency if<br>on-chip PLL is used                                     | 10                                                      | -   | 25   | MHz  |

|                      |                      | external clock frequency if<br>on-chip bootloader is used<br>for initial code download | 10                                                      | -   | 25   | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     |                                                                                        | 20                                                      | -   | 1000 | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      |                                                                                        | $\rm T_{cy(clk)} \times 0.4$                            | -   | -    | ns   |

| t <sub>CLCX</sub>    | clock LOW time       |                                                                                        | $\frac{T_{cy(clk)} \times 0.4}{T_{cy(clk)} \times 0.4}$ | -   | -    | ns   |

LPC2292\_2294

#### 16/32-bit ARM microcontrollers with external memory interface

### Table 12. External memory interface dynamic characteristics

| Symbol                | Parameter                                        | Conditions | Min                                                         | Тур | Мах                                       | Unit |

|-----------------------|--------------------------------------------------|------------|-------------------------------------------------------------|-----|-------------------------------------------|------|

| Common                | to read and write cycles                         |            |                                                             |     |                                           |      |

| t <sub>CHAV</sub>     | XCLK HIGH to address valid time                  |            | -                                                           | -   | 10                                        | ns   |

| t <sub>CHCSL</sub>    | XCLK HIGH to CS LOW time                         |            | -                                                           | -   | 10                                        | ns   |

| tснсян                | XCLK HIGH to CS HIGH time                        |            | -                                                           | -   | 10                                        | ns   |

| t <sub>CHANV</sub>    | XCLK HIGH to address<br>invalid time             |            | -                                                           | -   | 10                                        | ns   |

| Read cyc              | le parameters                                    |            |                                                             |     |                                           |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time                     | <u>[</u>   | <u>l</u> –5                                                 | -   | +10                                       | ns   |

| t <sub>OELAV</sub>    | OE LOW to address valid time                     | <u>[</u>   | 1 –5                                                        | -   | +10                                       | ns   |

| t <sub>CSLOEL</sub>   | CS LOW to OE LOW time                            |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>am</sub>       | memory access time                               | [2][3      | <sup>8</sup> ] (T <sub>cy(CCLK)</sub> × (2 + WST1)) + (−20) | -   | -                                         | ns   |

| t <sub>am(ibr)</sub>  | memory access time (initial burst-ROM)           | [2][:      | <sup>3]</sup> (T <sub>cy(CCLK)</sub> × (2 + WST1)) + (−20)  | -   | -                                         | ns   |

| t <sub>am(sbr)</sub>  | memory access time<br>(subsequent burst-ROM)     | [2][4      | H_T <sub>cy(CCLK)</sub> + (-20)                             | -   | -                                         | ns   |

| t <sub>h(D)</sub>     | data input hold time                             | [{         | 5] 0                                                        | -   | -                                         | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE HIGH time                          |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>OEHANV</sub>   | OE HIGH to address invalid time                  |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>CHOEL</sub>    | XCLK HIGH to OE LOW time                         |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>СНОЕН</sub>    | XCLK HIGH to OE HIGH time                        |            | -5                                                          | -   | +5                                        | ns   |

| Write cyc             | le parameters                                    |            |                                                             |     |                                           |      |

| t <sub>AVCSL</sub>    | address valid to $\overline{\text{CS}}$ LOW time | <u>1</u>   | Ц Т <sub>су(ССLК)</sub> – 10                                | -   | -                                         | ns   |

| t <sub>CSLDV</sub>    | CS LOW to data valid time                        |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>CSLWEL</sub>   | CS LOW to WE LOW time                            |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time                           |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>WELDV</sub>    | WE LOW to data valid time                        |            | -5                                                          | -   | +5                                        | ns   |

| t <sub>CSLDV</sub>    | $\overline{\text{CS}}$ LOW to data valid time    |            | -5                                                          | -   | +5                                        | ns   |

| twelweh               | WE LOW to WE HIGH time                           | <u>[</u> ; | 2] T <sub>cy(CCLK)</sub> × (1 + WST2) – 5                   | -   | $T_{cy(CCLK)} \times (1 + WST2) + 5$      | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time                         | [2         | 킨 T <sub>cy(CCLK)</sub> × (1 + WST2) – 5                    | -   | T <sub>су(ССLK)</sub> ×<br>(1 + WST2) + 5 | ns   |

| t <sub>WEHANV</sub>   | WE HIGH to address invalid time                  | [2         | 21 T <sub>cy(CCLK)</sub> – 5                                | -   | $T_{cy(CCLK)}$ + 5                        | ns   |

| t <sub>WEHDNV</sub>   | WE HIGH to data invalid time                     | [2         | <sup>2]</sup> (2 × T <sub>cy(CCLK)</sub> ) – 5              | -   | $(2 \times T_{cy(CCLK)}) + 5$             | ns   |

| t <sub>BLSHANV</sub>  | BLS HIGH to address invalid time                 | <u>[</u> 2 | 인 T <sub>cy(CCLK)</sub> – 5                                 | -   | T <sub>cy(CCLK)</sub> + 5                 | ns   |

LPC2292\_2294

#### 16/32-bit ARM microcontrollers with external memory interface

## 10. Package outline

### Fig 25. Package outline SOT486-1 (LQFP144)

Product data sheet

LPC2292 2294

#### 16/32-bit ARM microcontrollers with external memory interface

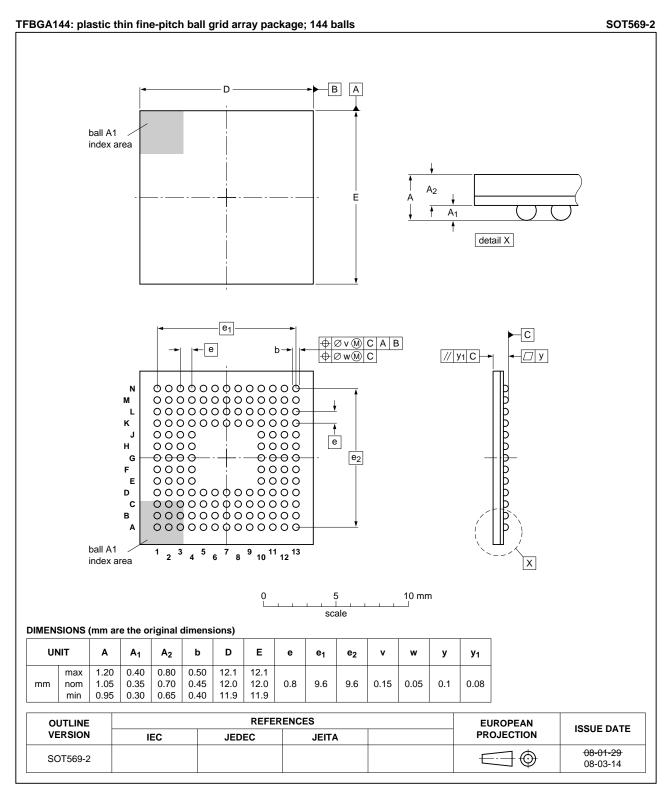

#### Fig 26. Package outline SOT569-2 (TFBGA144)

LPC2292\_2294

49 of 54

#### 16/32-bit ARM microcontrollers with external memory interface

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's

## 14. Contact information

own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

## 13.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

#### For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com