#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 18MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 26                                                                      |

| Program Memory Size        | 8KB (8K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

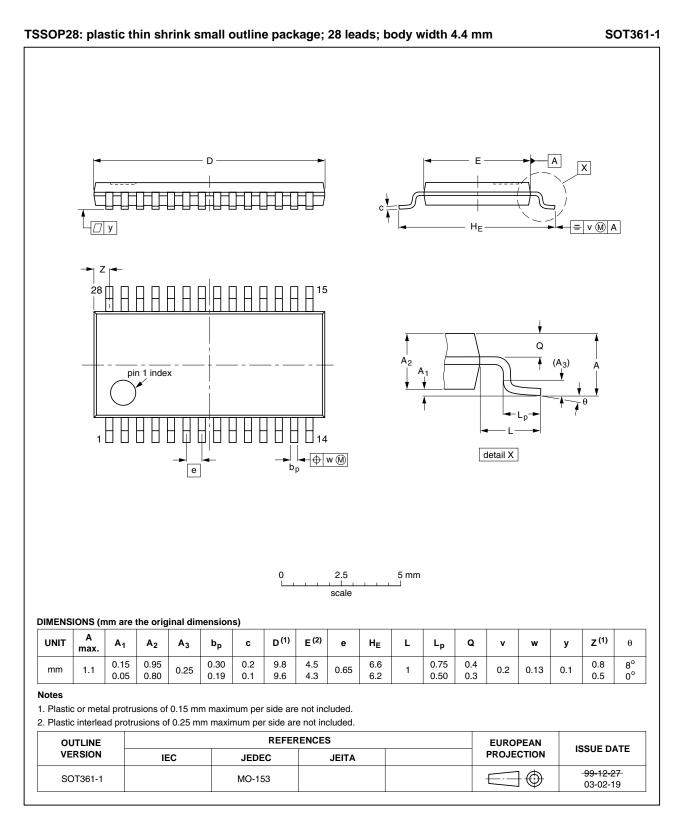

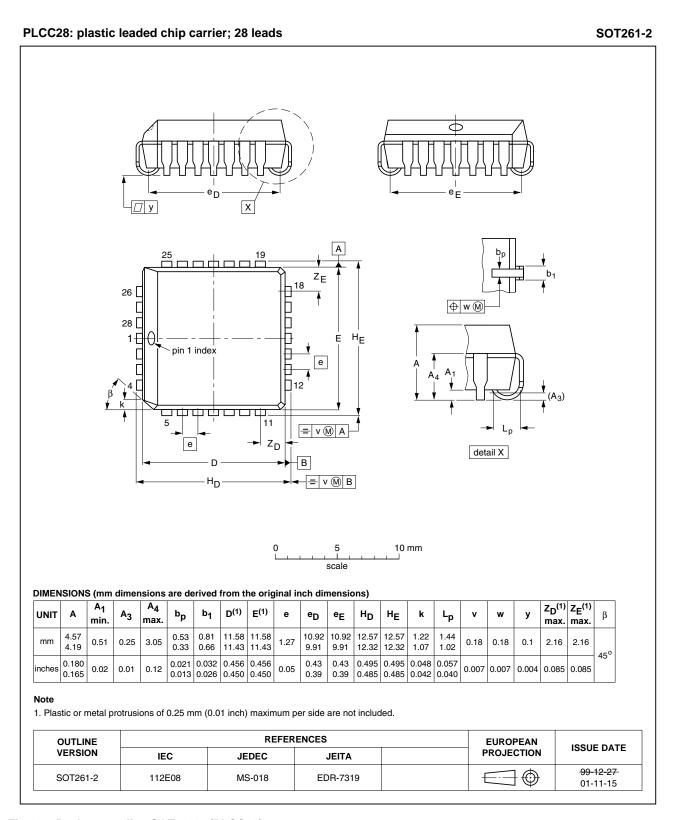

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-LCC (J-Lead)                                                         |

| Supplier Device Package    | 28-PLCC (11.48x11.48)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89lpc982fa-529 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Additional features

- A high performance 80C51 CPU provides instruction cycle times of 111 ns to 222 ns for all instructions except multiply and divide when executing at 18 MHz. This is six times the performance of the standard 80C51 running at the same clock frequency. A lower clock frequency for the same performance results in power savings and reduced EMI.

- Serial flash In-Circuit Programming (ICP) allows simple production coding with commercial EPROM programmers. Flash security bits prevent reading of sensitive application programs.

- Serial flash In-System Programming (ISP) allows coding while the device is mounted in the end application.

- In-Application Programming (IAP) of the flash code memory. This allows changing the code in a running application.

- Clock switching on the fly among internal RC oscillator, watchdog oscillator, external clock source provides optimal support of minimal power active mode with fast switching to maximum performance.

- Idle and two different power-down reduced power modes. Improved wake-up from Power-down mode (a LOW interrupt input starts execution). Typical power-down current is 1 µA (total power-down with voltage comparators disabled).

- Integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Idle mode, Power-down mode and Total power-down mode. In addition, the power consumption can be further reduced in Normal or Idle mode through configuring regulators modes according to the applications.

- Active-LOW reset. On-chip power-on reset allows operation without external reset components. A software reset function is also available.

- Configurable on-chip oscillator with frequency range options selected by user programmed flash configuration bits. Oscillator options support frequencies from 20 kHz to the maximum operating frequency of 18 MHz.

- Oscillator fail detect. The watchdog timer has a separate fully on-chip oscillator allowing it to perform an oscillator fail detect function.

- Programmable port output configuration options: quasi-bidirectional, open drain, push-pull, input-only.

- High current sourcing/sinking (20 mA) on eight I/O pins (P0.3 to P0.7, P1.4, P1.6, P1.7). All other port pins have high sinking capability (20 mA). A maximum limit is specified for the entire chip.

- Port 'input pattern match' detect. Port 0 may generate an interrupt when the value of the pins match or do not match a programmable pattern.

- Controlled slew rate port outputs to reduce EMI. Outputs have approximately 10 ns minimum ramp times.

- Only power and ground connections are required to operate the P89LPC980/982/983/985 when internal reset option is selected.

- Four interrupt priority levels.

- Eight keypad interrupt inputs, plus two additional external interrupt inputs.

- Schmitt trigger port inputs.

- Second data pointer.

- Emulation support.

# 6.2 Pin description

| Symbol          | Pin                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | PLCC28,<br>TSSOP28 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P0.0 to P0.7    |                    | I/O  | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. During reset Port 0 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <u>Section</u> 7.16.1 "Port configurations" and <u>Table 13 "Static characteristics"</u> for details. |

|                 |                    |      | The Keypad Interrupt feature operates with Port 0 pins.                                                                                                                                                                                                                                                                                                                                                                                           |

|                 |                    |      | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 |                    |      | Port 0 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                |

| P0.0/CMP2/KBI0/ | 3                  | I/O  | <b>P0.0</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AD05/SPICLK     |                    | 0    | CMP2 — Comparator 2 output                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | Ι    | <b>KBI0</b> — Keyboard input 0.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |                    | I    | AD05 — ADC0 channel 5 analog input. (P89LPC985)                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |                    | I/O  | <b>SPICLK</b> — SPI clock. When configured as master, this pin is output; when configured as slave, this pin is input. (pin remap)                                                                                                                                                                                                                                                                                                                |

| P0.1/CIN2B/     | 26                 | I/O  | <b>P0.1</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| KBI1/AD00       |                    | I    | <b>CIN2B</b> — Comparator 2 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                    | I    | KBI1 — Keyboard input 1.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |                    | I    | AD00 — ADC0 channel 0 analog input. (P89LPC983/985)                                                                                                                                                                                                                                                                                                                                                                                               |

| P0.2/CIN2A/     | 25                 | I/O  | <b>P0.2</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| KBI2/AD01       |                    | I    | <b>CIN2A</b> — Comparator 2 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                    | I    | KBI2 — Keyboard input 2.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |                    | I    | AD01 — ADC0 channel 1 analog input. (P89LPC983/985)                                                                                                                                                                                                                                                                                                                                                                                               |

| P0.3/CIN1B/     | 24                 | I/O  | P0.3 — Port 0 bit 3. High current source.                                                                                                                                                                                                                                                                                                                                                                                                         |

| KBI3/AD02/T2    |                    | I    | <b>CIN1B</b> — Comparator 1 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                    | I    | KBI3 — Keyboard input 3.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |                    | I    | AD02 — ADC0 channel 2 analog input. (P89LPC983/985)                                                                                                                                                                                                                                                                                                                                                                                               |

|                 |                    | I/O  | T2 — Timer/counter 2 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                                     |

| P0.4/CIN1A/     | 23                 | I/O  | P0.4 — Port 0 bit 4. High current source.                                                                                                                                                                                                                                                                                                                                                                                                         |

| KBI4/AD03       |                    | I    | CIN1A — Comparator 1 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 |                    | I    | KBI4 — Keyboard input 4.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |                    | I    | AD03 — ADC0 channel 3 analog input. (P89LPC983/985)                                                                                                                                                                                                                                                                                                                                                                                               |

| P0.5/CMPREF/    | 22                 | I/O  | P0.5 — Port 0 bit 5. High current source.                                                                                                                                                                                                                                                                                                                                                                                                         |

| KBI5/T3         |                    | I    | <b>CMPREF</b> — Comparator reference (negative) input.                                                                                                                                                                                                                                                                                                                                                                                            |

|                 |                    | I    | KBI5 — Keyboard input 5.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                 |                    | I/O  | <b>T3</b> — Timer/counter 3 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol          | Pin                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | PLCC28,<br>TSSOP28 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P1.7/AD04/T3EX/ | 4                  | I/O  | P1.7 — Port 1 bit 7. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MOSI            |                    | Ι    | AD04 — ADC0 channel 4 analog input. (P89LPC985)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |                    | Ι    | T3EX — Timer/counter 3 external capture input.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |                    | I/O  | <b>MOSI</b> — SPI master out slave in. When configured as master, this pin is output; when configured as slave, this pin is input. (pin remap)                                                                                                                                                                                                                                                                                                                     |

| P2.0 to P2.7    |                    | I/O  | <b>Port 2:</b> Port 2 is an 8-bit I/O port with a user-configurable output type. During rese<br>Port 2 latches are configured in the input only mode with the internal pull-up<br>disabled. The operation of Port 2 pins as inputs and outputs depends upon the por<br>configuration selected. Each port pin is configured independently. Refer to <u>Section</u><br><u>7.16.1 "Port configurations"</u> and <u>Table 13 "Static characteristics"</u> for details. |

|                 |                    |      | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |                    |      | Port 2 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                 |

| P2.0/AD07/TXD   | 1                  | I/O  | <b>P2.0</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    |      | AD07 — ADC0 channel 7 analog input. (P89LPC985)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |                    | 0    | <b>TXD</b> — Transmitter output for serial port. (pin remap)                                                                                                                                                                                                                                                                                                                                                                                                       |

| P2.1/AD06/RXD   | 2                  | I/O  | <b>P2.1</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | 1    | AD06 — ADC0 channel 6 analog input. (P89LPC985)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |                    | I    | <b>RXD</b> — Receiver input for serial port. (pin remap)                                                                                                                                                                                                                                                                                                                                                                                                           |

| P2.2/MOSI       | 13                 | I/O  | <b>P2.2</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | I/O  | <b>MOSI</b> — SPI master out slave in. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                                                 |

| P2.3/MISO       | 14                 | I/O  | <b>P2.3</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | I/O  | <b>MISO</b> — SPI master in slave out. When configured as master, this pin is input, when configured as slave, this pin is output.                                                                                                                                                                                                                                                                                                                                 |

| P2.4/SS         | 15                 | I/O  | <b>P2.4</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | I    | SS — SPI Slave select.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P2.5/SPICLK     | 16                 | I/O  | <b>P2.5</b> — Port 2 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | I/O  | <b>SPICLK</b> — SPI clock. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                                                             |

| P2.6/SCL        | 27                 | I/O  | <b>P2.6</b> — Port 2 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | I/O  | SCL — I <sup>2</sup> C-bus serial clock input/output. (pin remap)                                                                                                                                                                                                                                                                                                                                                                                                  |

| P2.7/SDA        | 28                 | I/O  | <b>P2.7</b> — Port 2 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |                    | I/O  | SDA — I <sup>2</sup> C-bus serial data input/output. (pin remap)                                                                                                                                                                                                                                                                                                                                                                                                   |

| P3.0 to P3.1    |                    | I/O  | <b>Port 3:</b> Port 3 is a 2-bit I/O port with a user-configurable output type. During rese<br>Port 3 latches are configured in the input only mode with the internal pull-up<br>disabled. The operation of Port 3 pins as inputs and outputs depends upon the po<br>configuration selected. Each port pin is configured independently. Refer to <u>Sectio</u><br><u>7.16.1 "Port configurations"</u> and <u>Table 13 "Static characteristics"</u> for details.    |

|                 |                    |      | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 3.

Pin description ...continued

Port 3 also provides various special functions as described below:

# Table 4. Special function registers - P89LPC980/982 ...continued \* indicates SFRs that are bit addressable.

| Product | P89LPC980_ |

|---------|------------|

| t data  | 982_983    |

| sheet   | 985        |

| Re  |  |

|-----|--|

| ev. |  |

| 4   |  |

|     |  |

| 1   |  |

| G   |  |

| 5   |  |

| 5   |  |

| e   |  |

| N   |  |

| 2   |  |

| ō   |  |

| Name   | Description                                     | SFR     | Bit functions and addresses |       |         |         |         |         |          |          | Reset value   |           |

|--------|-------------------------------------------------|---------|-----------------------------|-------|---------|---------|---------|---------|----------|----------|---------------|-----------|

|        |                                                 | addr.   | MSB                         |       |         |         |         |         |          | LSB      | Hex           | Binary    |

| P3M1   | Port 3 output<br>mode 1                         | B1H     | -                           | -     | -       | -       | -       | -       | (P3M1.1) | (P3M1.0) | 03 <u>[2]</u> | xxxx xx11 |

| P3M2   | Port 3 output<br>mode 2                         | B2H     | -                           | -     | -       | -       | -       | -       | (P3M2.1) | (P3M2.0) | 00 <u>[2]</u> | xxxx xx00 |

| PCON   | Power control register                          | 87H     | SMOD1                       | SMOD0 | -       | BOI     | GF1     | GF0     | PMOD1    | PMOD0    | 00            | 0000 0000 |

| PCONA  | Power control<br>register A                     | B5H     | RTCPD                       | -     | VCPD    | -       | I2PD    | SPPD    | SPD      | -        | 00 <u>[2]</u> | 0000 0000 |

| PINCON | Pin remap control register                      | CFH     | -                           | -     | -       | -       | -       | UART    | SPI      | I2C      | 00 <u>[2]</u> | 0000 0000 |

| PMUCON | Power<br>Management<br>Unit control<br>register | FAH     | LPMOD                       | -     | -       | -       | -       | -       | -        | HCOK     |               | 0xxx xxx1 |

|        | Bit a                                           | address | D7                          | D6    | D5      | D4      | D3      | D2      | D1       | D0       |               |           |

| PSW*   | Program status<br>word                          | D0H     | CY                          | AC    | F0      | RS1     | RS0     | OV      | F1       | Р        | 00            | 0000 0000 |

| PT0AD  | Port 0 digital<br>input disable                 | F6H     | -                           | -     | PT0AD.5 | PT0AD.4 | PT0AD.3 | PT0AD.2 | PT0AD.1  | -        | 00            | xx00 000x |

| PWMD2H | PWM Free Cycle<br>Register 2 High<br>Byte       | AEH     |                             |       |         |         |         |         |          |          | 00            | 0000 0000 |

| PWMD2L | PWM Free Cycle<br>Register 2 Low<br>Byte        | AFH     |                             |       |         |         |         |         |          |          | 00            | 0000 0000 |

| PWMD3H | PWM Free Cycle<br>Register 3 High<br>Byte       | E9H     |                             |       |         |         |         |         |          |          | 00            | 0000 0000 |

| PWMD3L | PWM Free Cycle<br>Register 3 Low<br>Byte        | EAH     |                             |       |         |         |         |         |          |          | 00            | 0000 0000 |

| PWMD4H | PWM Free Cycle<br>Register 4 High<br>Byte       | AAH     |                             |       |         |         |         |         |          |          | 00            | 0000 0000 |

**NXP Semiconductors**

8-bit microcontroller with accelerated two-clock 80C51 core P89LPC980/982/983/985

© NXP B.V. 2010. All rights reserved. 18 of 85

# Table 4. Special function registers - P89LPC980/982 ...continued \* indicates SFRs that are bit addressable. P89LPC9

| Name   | Description                  | SFR     | Bit function | ns and addr | esses |      |        |       |       |         | Reset value |           |

|--------|------------------------------|---------|--------------|-------------|-------|------|--------|-------|-------|---------|-------------|-----------|

|        |                              | addr.   | MSB          |             |       |      |        |       |       | LSB     | Hex         | Binary    |

| SPCTL  | SPI control register         | E2H     | SSIG         | SPEN        | DORD  | MSTR | CPOL   | CPHA  | SPR1  | SPR0    | 04          | 0000 0100 |

| SPSTAT | SPI status<br>register       | E1H     | SPIF         | WCOL        | -     | -    | -      | -     | -     | -       | 00          | 00xx xxxx |

| SPDAT  | SPI data register            | E3H     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| TAMOD  | Timer 0 and 1 auxiliary mode | 8FH     | -            | -           | -     | T1M2 | -      | -     | -     | T0M2    | 00          | xxx0 xxx0 |

|        | Bit a                        | address | 8F           | 8E          | 8D    | 8C   | 8B     | 8A    | 89    | 88      |             |           |

| TCON*  | Timer 0 and 1 control        | 88H     | TF1          | TR1         | TF0   | TR0  | IE1    | IT1   | IE0   | IT0     | 00          | 0000 0000 |

| TH0    | Timer 0 high                 | 8CH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| TH1    | Timer 1 high                 | 8DH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| TL0    | Timer 0 low                  | 8AH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| TL1    | Timer 1 low                  | 8BH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| TMOD   | Timer 0 and 1 mode           | 89H     | T1GATE       | T1C/T       | T1M1  | T1M0 | TOGATE | T0C/T | T0M1  | T0M0    | 00          | 0000 0000 |

| T2CON  | Timer/Counter 2<br>Control   | FFH     | PSEL2        | ENT2        | TIEN2 | PWM2 | EXEN2  | TR2   | C/NT2 | CP/NRL2 | 00          | 0000 0000 |

| TH2    | Timer/Counter 2<br>High Byte | FEH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| TL2    | Timer/Counter 2<br>Low Byte  | FDH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| T3CON  | Timer/Counter 3<br>Control   | EFH     | PSEL3        | ENT3        | TIEN3 | PWM3 | EXEN3  | TR3   | C/NT3 | CP/NRL3 | 00          | 0000 0000 |

| TH3    | Timer/Counter 3<br>High Byte | EEH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| TL3    | Timer/Counter 3<br>Low Byte  | EDH     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

| T4CON  | Timer/Counter 2<br>Control   | CDH     | PSEL4        | ENT4        | TIEN4 | PWM4 | EXEN4  | TR4   | C/NT4 | CP/NRL4 | 00          | 0000 0000 |

| TH4    | Timer/Counter 4<br>High Byte | ССН     |              |             |       |      |        |       |       |         | 00          | 0000 0000 |

**NXP Semiconductors**

8-bit microcontroller with accelerated two-clock 80C51 core P89LPC980/982/983/985

20 of 85

Product data sheet

Rev. 4 — 15 June 2010

# Table 6.Special function registers - P89LPC983/985\* indicates SFRs that are bit addressable. P89LPC98

| Name     | Description                           | SFR     | Bit function | Bit functions and addresses |       |        |       |        |        |        |               | value     |

|----------|---------------------------------------|---------|--------------|-----------------------------|-------|--------|-------|--------|--------|--------|---------------|-----------|

|          |                                       | addr.   | MSB          |                             |       |        |       |        |        | LSB    | Hex           | Binary    |

|          | Bit                                   | address | E7           | E6                          | E5    | E4     | E3    | E2     | E1     | E0     |               |           |

| ACC*     | Accumulator                           | E0H     |              |                             |       |        |       |        |        |        | 00            | 0000 0000 |

| AD0CON   | A/D control<br>register 0             | 97H     | ENBI0        | ENADCI0                     | TMM10 | EDGE0  | ADCI0 | ENADC0 | ADCS01 | ADCS00 | 00            | 0000 0000 |

| AD0INS   | A/D input select                      | A3H     | AIN07        | AIN06                       | AIN05 | AIN04  | AIN03 | AIN02  | AIN01  | AIN00  | 00            | 0000 0000 |

| AD0MODA  | A/D mode<br>register A                | C0H     | BNDI0        | BURST0                      | SCC0  | SCAN0  | -     | -      | -      | -      | 00            | 0000 0000 |

| AD0MODB  | A/D mode<br>register B                | A1H     | CLK2         | CLK1                        | CLK0  | INBND0 | -     | -      | BSA0   | FCIIS  | 00            | 000x 0000 |

| AUXR1    | Auxiliary<br>function register        | A2H     | CLKLP        | EBRR                        | ENT1  | ENT0   | SRST  | 0      | -      | DPS    | 00            | 0000 00x0 |

|          | Bit                                   | address | F7           | F6                          | F5    | F4     | F3    | F2     | F1     | F0     |               |           |

| B*       | B register                            | F0H     |              |                             |       |        |       |        |        |        | 00            | 0000 0000 |

| BRGR0[1] | Baud rate<br>generator 0 rate<br>low  | BEH     |              |                             |       |        |       |        |        |        | 00            | 0000 0000 |

| BRGR1[1] | Baud rate<br>generator 0 rate<br>high | BFH     |              |                             |       |        |       |        |        |        | 00            | 0000 0000 |

| BRGCON   | Baud rate<br>generator 0<br>control   | BDH     | -            | -                           | -     | -      | -     | -      | SBRGS  | BRGEN  | 00 <u>[1]</u> | xxxx xx00 |

| CMP1     | Comparator 1 control register         | ACH     | -            | -                           | CE1   | CP1    | CN1   | OE1    | CO1    | CMF1   | 00 <u>[2]</u> | xx00 0000 |

| CMP2     | Comparator 2 control register         | ADH     | -            | -                           | CE2   | CP2    | CN2   | OE2    | CO2    | CMF2   | 00 <u>[2]</u> | xx00 0000 |

| DIVM     | CPU clock<br>divide-by-M<br>control   | 95H     |              |                             |       |        |       |        |        |        | 00            | 0000 0000 |

| DPTR     | Data pointer<br>(2 bytes)             |         |              |                             |       |        |       |        |        |        |               |           |

| DPH      | Data pointer<br>high                  | 83H     |              |                             |       |        |       |        |        |        | 00            | 0000 0000 |

**NXP Semiconductors**

8-bit microcontroller with accelerated two-clock 80C51 core P89LPC980/982/983/985

ights reserved. 23 of 85

Product data sheet

Rev. 4 — 15 June 2010

# Table 6.Special function registers - P89LPC983/985 ...continued\* indicates SFRs that are bit addressable. P89LPC9

| I      | Name   | Description                                     | SFR     | Bit functio | ns and add | resses   |          |          |          |          |          | Reset v       | value     |

|--------|--------|-------------------------------------------------|---------|-------------|------------|----------|----------|----------|----------|----------|----------|---------------|-----------|

| T<br>* |        |                                                 | addr.   | MSB         |            |          |          |          |          |          | LSB      | Hex           | Binary    |

| 1      | P1M2   | Port 1 output<br>mode 2                         | 92H     | (P1M2.7)    | (P1M2.6)   | -        | (P1M2.4) | (P1M2.3) | (P1M2.2) | (P1M2.1) | (P1M2.0) | 00 <u>[2]</u> | 00x0 xx0  |

| I      | P2M1   | Port 2 output<br>mode 1                         | A4H     | (P2M1.7)    | (P2M1.6)   | (P2M1.5) | (P2M1.4) | (P2M1.3) | (P2M1.2) | (P2M1.1) | (P2M1.0) | FF <u>[2]</u> | 1111 1111 |

| I      | P2M2   | Port 2 output<br>mode 2                         | A5H     | (P2M2.7)    | (P2M2.6)   | (P2M2.5) | (P2M2.4) | (P2M2.3) | (P2M2.2) | (P2M2.1) | (P2M2.0) | 00 <u>[2]</u> | 0000 000  |

| I      | P3M1   | Port 3 output<br>mode 1                         | B1H     | -           | -          | -        | -        | -        | -        | (P3M1.1) | (P3M1.0) | 03 <u>[2]</u> | xxxx xx11 |

| I      | P3M2   | Port 3 output<br>mode 2                         | B2H     | -           | -          | -        | -        | -        | -        | (P3M2.1) | (P3M2.0) | 00 <u>[2]</u> | xxxx xx00 |

| I      | PCON   | Power control<br>register                       | 87H     | SMOD1       | SMOD0      | -        | BOI      | GF1      | GF0      | PMOD1    | PMOD0    | 00            | 0000 000  |

| I      | PCONA  | Power control<br>register A                     | B5H     | RTCPD       | -          | VCPD     | ADPD     | I2PD     | SPPD     | SPD      | -        | 00[2]         | 0000 000  |

| I      | PINCON | Pin remap<br>control register                   | CFH     | -           | -          | -        | -        | -        | UART     | SPI      | I2C      | 00 <u>[2]</u> | 0000 000  |

| i      | PMUCON | Power<br>Management<br>Unit control<br>register | FAH     | LPMOD       | -          | -        | -        | -        | -        | -        | HCOK     |               | 0xxx xxx  |

| _      |        | Bit                                             | address | D7          | D6         | D5       | D4       | D3       | D2       | D1       | D0       |               |           |

| I      | PSW*   | Program status<br>word                          | D0H     | CY          | AC         | F0       | RS1      | RS0      | OV       | F1       | Ρ        | 00            | 0000 000  |

| I      | PT0AD  | Port 0 digital<br>input disable                 | F6H     | -           | -          | PT0AD.5  | PT0AD.4  | PT0AD.3  | PT0AD.2  | PT0AD.1  | -        | 00            | xx00 000  |

| I      | PWMD2H | PWM Free<br>Cycle Register 2<br>High Byte       | AEH     |             |            |          |          |          |          |          |          | 00            | 0000 000  |

|        | PWMD2L | PWM Free<br>Cycle Register 2<br>Low Byte        | AFH     |             |            |          |          |          |          |          |          | 00            | 0000 000  |

| I      | PWMD3H | PWM Free<br>Cycle Register 3<br>High Byte       | E9H     |             |            |          |          |          |          |          |          | 00            | 0000 000  |

# **NXP Semiconductors**

8-bit microcontroller with accelerated two-clock 80C51 core P89LPC980/982/983/985

rights reserved. 26 of 85

#### **Table 6.** Special function registers - P89LPC983/985 ... continued

\* indicates SFRs that are bit addressable.

| Name   | Description                                               | SFR   | Bit functio | ns and add | resses |        |        |        |        |         | Reset  | value     |

|--------|-----------------------------------------------------------|-------|-------------|------------|--------|--------|--------|--------|--------|---------|--------|-----------|

|        |                                                           | addr. | MSB LSB     |            |        |        |        |        |        | Hex     | Binary |           |

| TH3    | Timer/Counter 3<br>High Byte                              | EEH   |             |            |        |        |        |        |        |         | 00     | 0000 0000 |

| TL3    | Timer/Counter 3<br>Low Byte                               | EDH   |             |            |        |        |        |        |        |         | 00     | 0000 0000 |

| T4CON  | Timer/Counter 2<br>Control                                | CDH   | PSEL4       | ENT4       | TIEN4  | PWM4   | EXEN4  | TR4    | C/NT4  | CP/NRL4 | 00     | 0000 0000 |

| TH4    | Timer/Counter 4<br>High Byte                              | CCH   |             |            |        |        |        |        |        |         | 00     | 0000 0000 |

| TL4    | Timer/Counter 4<br>Low Byte                               | CBH   |             |            |        |        |        |        |        |         | 00     | 0000 0000 |

| TINTF  | Timer/Counters<br>2/3/4 Overflow<br>and External<br>Flags | CEH   | -           | -          | TF4    | EXF4   | TF3    | EXF3   | TF2    | EXF2    | 00     | 0000 0000 |

| TRIM   | Internal<br>oscillator trim<br>register                   | 96H   | RCCLK       | ENCLK      | TRIM.5 | TRIM.4 | TRIM.3 | TRIM.2 | TRIM.1 | TRIM.0  | [4][5] |           |

| WDCON  | Watchdog<br>control register                              | A7H   | PRE2        | PRE1       | PRE0   | -      | -      | WDRUN  | WDTOF  | WDCLK   | [4][6] |           |

| WDL    | Watchdog load                                             | C1H   |             |            |        |        |        |        |        |         | FF     | 1111 1111 |

| WFEED1 | Watchdog<br>feed 1                                        | C2H   |             |            |        |        |        |        |        |         |        |           |

| WFEED2 | Watchdog<br>feed 2                                        | СЗН   |             |            |        |        |        |        |        |         |        |           |

NXP Semiconductors

8-bit microcontroller with accelerated two-clock 80C51 core

P89LPC980/982/983/985

[1] BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is logic 0. If any are written while BRGEN = 1, the result is unpredictable.

[2] All ports are in input only (high-impedance) state after power-up.

[3] The RSTSRC register reflects the cause of the P89LPC980/982/983/985 reset except BOIF bit. Upon a power-up reset, all reset source flags are cleared except POF and BOF; the power-on reset value is x011 0000.

[4] The only reset sources that affect these SFRs are power-on reset and watchdog reset.

[5] On power-on reset and watchdog reset, the TRIM SFR is initialized with a factory preprogrammed value. Other resets will not cause initialization of the TRIM register.

[6] After reset, the value is 1110 01x1, i.e., PRE2 to PRE0 are all logic 1, WDRUN = 1 and WDCLK = 1. WDTOF bit is logic 1 after watchdog reset and is logic 0 after power-on reset. Other resets will not affect WDTOF.

# PR9LPC980\_982\_983\_985 Product data sheet

Rev. 4 — 15 June 2010

NXP E

2010.

. A

29 of 85

# 7.5 Clock output

The P89LPC980/982/983/985 supports a user-selectable clock output function on the P3.0/XTAL2/CLKOUT pin when crystal oscillator is not being used. This condition occurs if another clock source has been selected (on-chip RC oscillator, watchdog oscillator, external clock input on XTAL1) and if the RTC and WDT are not using the crystal oscillator as their clock source. This allows external devices to synchronize to the P89LPC980/982/983/985. This output is enabled by the ENCLK bit in the TRIM register.

The frequency of this clock output is  $\frac{1}{2}$  that of the CCLK. If the clock output is not needed in Idle mode, it may be turned off prior to entering Idle, saving additional power.

# 7.6 On-chip RC oscillator option

The P89LPC980/982/983/985 has a 6-bit TRIM register that can be used to tune the frequency of the RC oscillator. During reset, the TRIM value is initialized to a factory preprogrammed value to adjust the oscillator frequency to 7.373 MHz  $\pm$  1 % at room temperature. End-user applications can write to the TRIM register to adjust the on-chip RC oscillator to other frequencies. When the clock doubler option is enabled (UCFG2.7 = 1), the output frequency is 14.746 MHz. If CCLK is 8 MHz or slower, the CLKLP SFR bit (AUXR1.7) can be set to logic 1 to reduce power consumption. On reset, CLKLP is logic 0 allowing highest performance access. This bit can then be set in software if CCLK is running at 8 MHz or slower. When clock doubler option is enabled, BOE0 to BOE2 bits (UCFG1[3:5]) are required to hold the device in reset at power-up until V<sub>DD</sub> has reached its specified level.

# 7.7 Watchdog oscillator option

The watchdog has a separate oscillator which provides two options: 400 kHz and 25 kHz. It is calibrated to  $\pm 10$  % at 400 kHz. The oscillator can be used to save power when a high clock frequency is not needed.

# 7.8 External clock input option

In this configuration, the processor clock is derived from an external source driving the P3.1/XTAL1 pin. The rate may be from 0 Hz up to 18 MHz. The P3.0/XTAL2/CLKOUT pin may be used as a standard port pin or a clock output. When using an oscillator frequency above 12 MHz, BOE0 to BOE2 bits (UCFG1[3:5]) are required to hold the device in reset at power-up until  $V_{DD}$  has reached its specified level.

# 7.9 Clock source switching on the fly

P89LPC980/982/983/985 can implement clock switching on any sources of watchdog oscillator, 7 MHz/14 MHz internal RC oscillator, crystal oscillator and external clock input during code is running. CLKOK bit in CLKCON register is used to indicate the clock switch status. CLKOK is cleared when starting clock source switch and set when completed. Notice that when CLKOK is '0', writing to CLKCON register is not allowed.

## 8-bit microcontroller with accelerated two-clock 80C51 core

| Peripherals | Function | Primary pin out | Alternative pin out |

|-------------|----------|-----------------|---------------------|

| SPI         | SPICLK   | P2.5            | P0.0                |

|             | MOSI     | P2.2            | P1.7                |

|             | MISO     | P2.3            | P1.6                |

|             | SS       | P2.4            | P1.4                |

| 12C         | SDA      | P1.3            | P2.7                |

|             | SCL      | P1.2            | P2.6                |

| JART        | TXD      | P1.0            | P2.0                |

|             | RXD      | P1.1            | P2.1                |

Please refer to P89LPC980/982/983/985 User manual for detail configurations.

# 7.17 Power management

The P89LPC980/982/983/985 support a variety of power management features.

Power-on detect and brownout detect are designed to prevent incorrect operation during initial power-up and power loss or reduction during operation.

The P89LPC980/982/983/985 support three different power reduction modes: Idle mode, Power-down mode, and total Power-down mode. In addition, individual on-chip peripherals can be disabled to eliminate unnecessary dynamic power use in any peripherals that are not required for the application.

Integrated PMU automatically adjusts internal regulators to minimize power consumption during Idle mode, Power-down mode and total Power-down mode. In addition, the power consumption can be further reduced in Normal or Idle mode through configuring regulators mode according to the applications.

# 7.17.1 Brownout detection

The brownout detect function determines if the power supply voltage drops below a certain level. Enhanced brownout detection has 3 independent functions: BOD reset, BOD interrupt and BOD flash.

These three functions are disabled in Power-down mode and Total Power-down mode. In Normal or Idle mode, BOD reset and BOD flash are always on and can not be disabled in software. BOD interrupt may be enabled or disabled in software.

BOD reset and BOD interrupt, each has 6 levels. BOE0 to BOE2 (UCFG1[3:5]) are used as trip point configuration bits of BOD reset. BOICFG0 to BOICFG2 in register BODCFG are used as trip point configuration bits of BOD interrupt.

BOD reset voltage should be lower than BOD interrupt trip point. BOD flash is used for flash programming/erase protection and has only 1 trip point at 2.4 V. Please refer to *P89LPC980/982/983/985 User manual* for detail configurations.

If brownout detection works, the brownout condition occurs when  $V_{DD}$  falls below the brownout falling trip voltage and is negated when  $V_{DD}$  rises above the brownout rising trip voltage.

For correct activation of brownout detect, the V<sub>DD</sub> rise and fall times must be observed. Please see <u>Table 13 "Static characteristics"</u> for specifications.

# 7.17.2 Power-on detection

The Power-on detect has a function similar to the brownout detect, but is designed to work as power comes up initially to ensure that the device is reset from Power-on. The POF flag in the RSTSRC register is set to indicate an initial power-up condition. The POF flag will remain set until cleared by software.

# 7.17.3 Power reduction modes

The P89LPC980/982/983/985 supports three different power reduction modes. These modes are Idle mode, Power-down mode, and total Power-down mode.

## 7.17.3.1 Idle mode

Idle mode leaves peripherals running in order to allow them to activate the processor

when an interrupt is generated. Any enabled interrupt source or reset may terminate Idle mode.

## 7.17.3.2 Power-down mode

The Power-down mode stops the oscillator in order to minimize power consumption. Brownout detection circuitry is disabled. The P89LPC980/982/983/985 exits Power-down mode via any reset, or certain interrupts.

Some chip functions continue to operate and draw power during Power-down mode, increasing the total power used during power-down. These include: watchdog timer, comparators and RTC/system timer (note that watchdog timer, comparators and RTC/system timer can be powered down separately). The internal RC oscillator is disabled unless both the RC oscillator has been selected as the system clock and the RTC is enabled.

# 7.17.3.3 Total Power-down mode

The total Power-down mode is a deeper power reduction mode. Brownout detection circuitry and analog comparators are disabled, as well as the internal RC oscillator.

Please use an external low frequency clock or 25 kHz watchdog oscillator to achieve low power with the RTC running during power-down.

## 7.17.4 Regulators

Internal regulators can be adjusted automatically to minimize power consumption during different power reduction modes. In Normal or Idle modes, power consumption can be further reduced by configuring PMUCON register.

In Normal or Idle mode, regulators have two operation modes: high speed mode and low current mode.

The regulators can be configured to low current mode to reduce the power consumption.

After power-on-reset, internal regulators enter into High-speed mode as default. PMUCON register is used to configure the regulators operation modes. LPMOD bit is used to select the regulator's mode and HCOK bit indicates whether the switch completed

# 8-bit microcontroller with accelerated two-clock 80C51 core

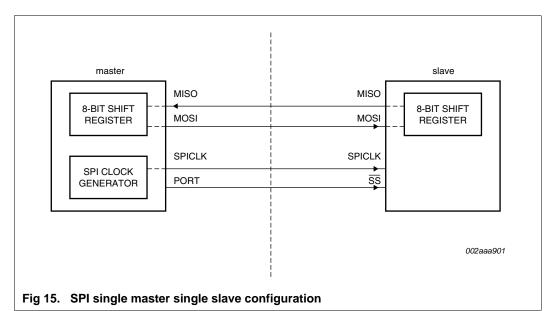

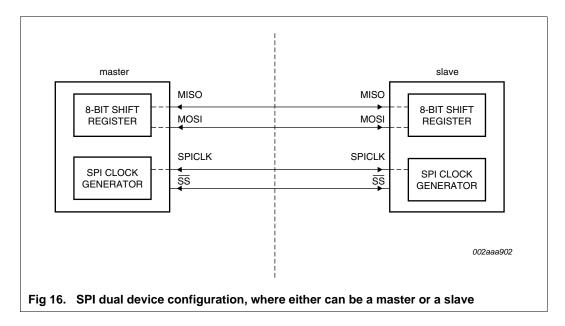

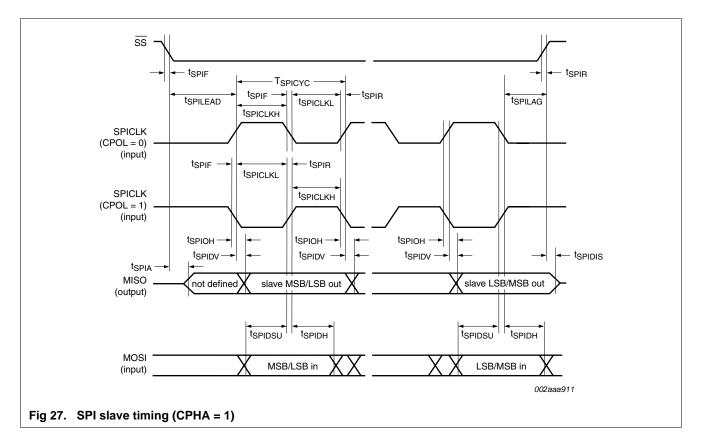

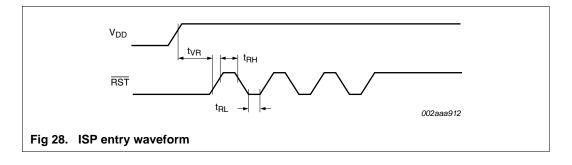

# 7.24.1 Typical SPI configurations

# 7.26 KBI

The Keypad Interrupt function (KBI) is intended primarily to allow a single interrupt to be generated when Port 0 is equal to or not equal to a certain pattern. This function can be used for bus address recognition or keypad recognition. The port can be configured via SFRs for different tasks.

The Keypad Interrupt Mask Register (KBMASK) is used to define which input pins connected to Port 0 can trigger the interrupt. The Keypad Pattern Register (KBPATN) is used to define a pattern that is compared to the value of Port 0. The Keypad Interrupt Flag (KBIF) in the Keypad Interrupt Control Register (KBCON) is set when the condition is matched while the Keypad Interrupt function is active. An interrupt will be generated if enabled. The PATN\_SEL bit in the Keypad Interrupt Control Register (KBCON) is used to define equal or not-equal for the comparison.

In order to use the Keypad Interrupt as an original KBI function like in P87LPC76x series, the user needs to set KBPATN = 0FFH and PATN\_SEL = 1 (not equal), then any key connected to Port 0 which is enabled by the KBMASK register will cause the hardware to set KBIF and generate an interrupt if it has been enabled. The interrupt may be used to wake-up the CPU from Idle or Power-down modes. This feature is particularly useful in handheld, battery-powered systems that need to carefully manage power consumption yet also need to be convenient to use.

In order to set the flag and cause an interrupt, the pattern on Port 0 must be held longer than six CCLKs.

# 7.27 Watchdog timer

The watchdog timer causes a system reset when it underflows as a result of a failure to feed the timer prior to the timer reaching its terminal count. It consists of a programmable 12-bit prescaler, and an 8-bit down counter. The down counter is decremented by a tap taken from the prescaler. The clock source for the prescaler can be the PCLK, the nominal 400 kHz/25 kHz watchdog oscillator or low speed crystal oscillator. The watchdog timer can only be reset by a power-on reset. When the watchdog feature is disabled, it can be used as an interval timer and may generate an interrupt. Figure 19 shows the watchdog timer in Watchdog mode. Feeding the watchdog requires a two-byte sequence. If PCLK is selected as the watchdog clock and the CPU is powered down, the watchdog is disabled. The watchdog timer has a time-out period that ranges from a few  $\mu$ s to a few seconds. Please refer to the *P89LPC980/982/983/985 User manual* for more details.

## 8.4.4 Auto scan, continuous conversion mode

Any combination of the eight input channels can be selected for conversion. A conversion of each selected input will be performed and the result placed in the result register pair which corresponds to the selected input channel. The user may select whether an interrupt, if enabled, will be generated after either the first four conversions have occurred or all selected channels have been converted. If the user selects to generate an interrupt after the four input channels have been converted, a second interrupt will be generated after the remaining input channels have been converted. After all selected channels have been converted, the process will repeat starting with the first selected channel. Additional conversion results will again cycle through the eight result register pairs, overwriting the previous results. Continuous conversions continue until terminated by the user.

## 8.4.5 Dual channel, continuous conversion mode

This is a variation of the auto scan continuous conversion mode where conversion occurs on two user-selectable inputs. The result of the conversion of the first channel is placed in the result register pair, AD0DAT0R and AD0DAT0L. The result of the conversion of the second channel is placed in result register pair, AD0DAT1R and AD0DAT1L. The first channel is again converted and its result stored in AD0DAT2R and AD0DAT2L. The second channel is again converted and its result placed in AD0DAT3R and AD0DAT3L. An interrupt is generated, if enabled, after every set of four or eight conversions (user selectable).

#### 8.4.6 Single step mode

This special mode allows 'single-stepping' in an auto scan conversion mode. Any combination of the eight input channels can be selected for conversion. After each channel is converted, an interrupt is generated, if enabled, and the A/D waits for the next start condition. May be used with any of the start modes.

# 8.5 Conversion start modes

## 8.5.1 Timer triggered start

An A/D conversion is started by the overflow of Timer 0. Once a conversion has started, additional Timer 0 triggers are ignored until the conversion has completed. The Timer triggered start mode is available in all ADC operating modes.

#### 8.5.2 Start immediately

Programming this mode immediately starts a conversion. This start mode is available in all ADC operating modes.

## 8.5.3 Edge triggered

An A/D conversion is started by rising or falling edge of P1.4. Once a conversion has started, additional edge triggers are ignored until the conversion has completed. The edge triggered start mode is available in all ADC operating modes.

#### 8-bit microcontroller with accelerated two-clock 80C51 core

# 11. Dynamic characteristics

#### Table 14. Dynamic characteristics (12 MHz)

$V_{DD} = 2.4 \text{ V to } 5.5 \text{ V unless otherwise specified.}$

$T_{amb} = -40 \text{ °C to } +85 \text{ °C for industrial applications, unless otherwise specified.}$

| Symbol               | Parameter                                        | Conditions                                                                                                                | Varia                  | able clock                                           | f <sub>osc</sub> = ' | Unit   |     |

|----------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------|----------------------|--------|-----|

|                      |                                                  |                                                                                                                           | Min                    | Max                                                  | Min                  | Max    |     |

| f <sub>osc(RC)</sub> | internal RC oscillator<br>frequency              | nominal f = 7.3728 MHz<br>trimmed to $\pm$ 1 % at<br>T <sub>amb</sub> = 25 °C; clock<br>doubler option = OFF<br>(default) | 7.189                  | 7.557                                                | 7.189                | 7.557  | MHz |

|                      |                                                  | nominal f = 14.7456 MHz;<br>clock doubler option = ON,<br>$V_{DD}$ = 2.7 V to 5.5 V                                       | 14.378                 | 15.114                                               | 14.378               | 15.114 | MHz |

| f <sub>osc(WD)</sub> | internal watchdog<br>oscillator frequency        |                                                                                                                           | 360                    | 440                                                  | 360                  | 440    | kHz |

| f <sub>osc</sub>     | oscillator frequency                             |                                                                                                                           | 0                      | 12                                                   | -                    | -      | MHz |

| T <sub>cy(clk)</sub> | clock cycle time                                 | see Figure 22                                                                                                             | 83                     | -                                                    | -                    | -      | ns  |

| f <sub>CLKLP</sub>   | low-power select clock<br>frequency              |                                                                                                                           | 0                      | 8                                                    | -                    | -      | MHz |

| Glitch filte         | r                                                |                                                                                                                           |                        |                                                      |                      |        |     |

| t <sub>gr</sub>      | glitch rejection time                            | P1.5/RST pin                                                                                                              | -                      | 50                                                   | -                    | 50     | ns  |

|                      |                                                  | any pin except P1.5/RST                                                                                                   | -                      | 15                                                   | -                    | 15     | ns  |

| t <sub>sa</sub>      | signal acceptance time                           | P1.5/RST pin                                                                                                              | 125                    | -                                                    | 125                  | -      | ns  |

|                      |                                                  | any pin except P1.5/RST                                                                                                   | 50                     | -                                                    | 50                   | -      | ns  |

| External c           | lock                                             |                                                                                                                           |                        |                                                      |                      |        |     |

| t <sub>CHCX</sub>    | clock HIGH time                                  | see Figure 22                                                                                                             | 33                     | ${\sf T}_{{\sf cy}({\sf clk})}-{\sf t}_{{\sf CLCX}}$ | 33                   | -      | ns  |

| t <sub>CLCX</sub>    | clock LOW time                                   | see Figure 22                                                                                                             | 33                     | ${\sf T}_{{\sf cy}({\sf clk})}-{\sf t}_{{\sf CHCX}}$ | 33                   | -      | ns  |

| t <sub>CLCH</sub>    | clock rise time                                  | see Figure 22                                                                                                             | -                      | 8                                                    | -                    | 8      | ns  |

| t <sub>CHCL</sub>    | clock fall time                                  | see Figure 22                                                                                                             | -                      | 8                                                    | -                    | 8      | ns  |

| Shift regis          | ter (UART mode 0)                                |                                                                                                                           |                        |                                                      |                      |        |     |

| T <sub>XLXL</sub>    | serial port clock cycle time                     | see Figure 23                                                                                                             | 16T <sub>cy(clk)</sub> | -                                                    | 1333                 | -      | ns  |

| t <sub>QVXH</sub>    | output data set-up to<br>clock rising edge time  | see <u>Figure 23</u>                                                                                                      | 13T <sub>cy(clk)</sub> | -                                                    | 1083                 | -      | ns  |

| t <sub>XHQX</sub>    | output data hold after<br>clock rising edge time | see <u>Figure 23</u>                                                                                                      | -                      | $T_{cy(clk)}$ + 20                                   | -                    | 103    | ns  |