### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18325-e-jq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F18325/18345

| TABLE 2: | 20-PIN ALLOCATION TABLE (PIC16(L)F18345) (CONTINUED) |

|----------|------------------------------------------------------|

|----------|------------------------------------------------------|

|                    |                       |             |      |           |                  |      |     |                       |        | ·····               |      |                |                                            |        |                       |      |           |         |       |

|--------------------|-----------------------|-------------|------|-----------|------------------|------|-----|-----------------------|--------|---------------------|------|----------------|--------------------------------------------|--------|-----------------------|------|-----------|---------|-------|

| l/O <sup>(2)</sup> | 20-Pin PDIP/SOIC/SSOP | 20-Pin UQFN | ADC  | Reference | Comparator       | NCO  | DAC | WSQ                   | Timers | ССР                 | MWd  | 9MC            | dssm                                       | EUSART | CLC                   | CLKR | Interrupt | Pull-up | Basic |

| RC3                | 7                     | 4           | ANC3 | _         | C1IN3-<br>C2IN3- |      | _   | MDMIN <sup>(1)</sup>  |        | CCP2 <sup>(1)</sup> | _    | -              | -                                          |        | CLCIN1 <sup>(1)</sup> |      | IOC       | Y       | _     |

| RC4                | 6                     | 3           | ANC4 | —         | _                | _    | _   | _                     | _      | _                   | _    | _              | _                                          | _      | _                     | —    | IOC       | Y       | _     |

| RC5                | 5                     | 2           | ANC5 | _         | —                | _    | —   | MDCIN2 <sup>(1)</sup> | —      | CCP1 <sup>(1)</sup> |      | _              | _                                          | _      | —                     | —    | IOC       | Y       | —     |

| RC6                | 8                     | 5           | ANC6 | —         | _                |      | _   | _                     |        | _                   | _    | -              | SS1 <sup>(1)</sup>                         |        | —                     | —    | IOC       | Y       | —     |

| RC7                | 9                     | 6           | ANC7 | _         | —                | _    | _   | _                     | _      | —                   | _    | _              | _                                          | _      | —                     | —    | IOC       | Y       | _     |

| Vdd                | 1                     | 18          | —    | —         | —                | _    | _   | _                     | _      | _                   | _    | _              | _                                          | _      | —                     | —    | —         | —       | Vdd   |

| Vss                | 20                    | 17          | _    | _         | —                | _    | _   | _                     | _      | —                   | _    | _              | _                                          | _      | —                     | —    | _         | —       | Vss   |

|                    | —                     |             | —    | —         | C1OUT            | NCO1 | —   | DSM                   | TMR0   | CCP1                | PWM5 | CWG1A<br>CWG2A | SDO1<br>SDO2                               | DT     | CLC1OUT               | CLKR | —         | —       | —     |

| OUT <sup>(2)</sup> | _                     |             | -    | —         | C2OUT            |      | —   | —                     |        | CCP2                | PWM6 | CWG1B<br>CWG2B | SCK1<br>SCK2                               | СК     | CLC2OUT               | _    | _         | —       | _     |

| 0010               | _                     | I           |      | —         | _                |      | _   | _                     |        | CCP3                |      | CWG1C<br>CWG2C | SCL1 <sup>(3)</sup><br>SCL2 <sup>(3)</sup> | ТΧ     | CLC3OUT               | —    | —         | _       |       |

|                    |                       |             | —    | _         | —                | _    | _   | _                     |        | CCP4                | _    | CWG1D<br>CWG2D | SDA1 <sup>(3)</sup><br>SDA2 <sup>(3)</sup> |        | CLC4OUT               | —    | _         | _       | —     |

**Note** 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I<sup>2</sup>C logic levels; clock and data signals may be assigned to any of these pins. Assignments to other pins (e.g. RA5) will operate, but logic levels will be standard TTL/ST as selected by the INLVL register.

| Name                                                                | Function | Input<br>Type | Output<br>Type | Description                      |

|---------------------------------------------------------------------|----------|---------------|----------------|----------------------------------|

| RC3/ANC3/C1IN3-/C2IN3-/                                             | RC3      | TTL/ST        | CMOS           | General purpose I/O.             |

| MDMIN <sup>(1)</sup> / CCP2 <sup>(1)</sup> /CLCIN1 <sup>(1)</sup> / | ANC3     | AN            | _              | ADC Channel C3 input.            |

|                                                                     | C1IN3-   | AN            | _              | Comparator C1 negative input.    |

|                                                                     | C2IN3-   | AN            | _              | Comparator C2 negative input.    |

|                                                                     | MDMIN    | TTL/ST        | _              | Modular Source input.            |

|                                                                     | CCP2     | TTL/ST        | CMOS           | Capture/Compare/PWM 2 input.     |

|                                                                     | CLCIN1   | TTL/ST        |                | Configurable Logic Cell 1 input. |

| RC4/ANC4                                                            | RC4      | TTL/ST        | CMOS           | General purpose I/O.             |

|                                                                     | ANC4     | AN            | _              | ADC Channel C4 input.            |

| RC5/ANC5/MDCIN2 <sup>(1)</sup> /CCP1 <sup>(1)</sup>                 | RC5      | TTL/ST        | CMOS           | General purpose I/O.             |

|                                                                     | ANC5     | AN            |                | ADC Channel C5 input.            |

|                                                                     | MDCIN2   | TTL/ST        |                | Modular Carrier input 2.         |

|                                                                     | CCP1     | TTL/ST        | CMOS           | Capture/Compare/PWM 1 input.     |

| RC6/ANC6/SS1 <sup>(1)</sup>                                         | RC6      | TTL/ST        | CMOS           | General purpose I/O.             |

|                                                                     | ANC6     | AN            |                | ADC Channel C6 input.            |

|                                                                     | SS1      | TTL/ST        | _              | Slave Select 1 input.            |

| RC7/ANC7                                                            | RC7      | TTL/ST        | CMOS           | General purpose I/O.             |

|                                                                     | ANC7     | AN            | _              | ADC Channel C7 input.            |

| VDD                                                                 | Vdd      | Power         | _              | Positive supply.                 |

| Vss                                                                 | Vss      | Power         | _              | Ground reference.                |

Legend: AN = Analog input or output CMOS= CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| TABLE   | 4-4: SP | ECIAL FU                         | NCTION RE |       | UMMARY B | ANKS 0-31 ( | CONTINUE | D)    |       |   |

|---------|---------|----------------------------------|-----------|-------|----------|-------------|----------|-------|-------|---|

| Address | Name    | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7     | Bit 6 | Bit 5    | Bit 4       | Bit 3    | Bit 2 | Bit 1 | I |

| Bank 31             | Bank 31 — only accessible from Debug Executive, unless otherwise specified |  |   |   |                                                             |                 |                   |                    |                  |                |   |           |           |  |  |

|---------------------|----------------------------------------------------------------------------|--|---|---|-------------------------------------------------------------|-----------------|-------------------|--------------------|------------------|----------------|---|-----------|-----------|--|--|

|                     | CPU CORE REGISTERS; see Table 4-2 for specifics                            |  |   |   |                                                             |                 |                   |                    |                  |                |   |           |           |  |  |

| F8Ch to<br>FE3h     | _                                                                          |  |   |   | Unimplemented                                               |                 |                   |                    |                  |                |   |           |           |  |  |

| FE4h <sup>(2)</sup> | STATUS_SHAD                                                                |  |   | — | -                                                           | —               | —                 | —                  | Z                | DC             | С | xxx       | uuu       |  |  |

| FE5h <sup>(2)</sup> | WREG_SHAD                                                                  |  |   |   |                                                             | Work            | ing Register Norr | nal (Non-ICD) Sh   | adow             |                |   | xxxx xxxx | uuuu uuuu |  |  |

| FE6h <sup>(2)</sup> | BSR_SHAD                                                                   |  |   | — | —                                                           | —               |                   | Bank Select Reg    | ister Normal (No | on-ICD) Shadow |   | x xxxx    | u uuuu    |  |  |

| FE7h <sup>(2)</sup> | PCLATH_SHAD                                                                |  |   | — | Program Counter Latch High Register Normal (Non-ICD) Shadow |                 |                   |                    |                  |                |   |           |           |  |  |

| FE8h <sup>(2)</sup> | FSR0L_SHAD                                                                 |  |   |   | Ind                                                         | irect Data Memo | ory Address 0 Lov | w Pointer Normal   | (Non-ICD) Shad   | ow             |   | xxxx xxxx | uuuu uuuu |  |  |

| FE9h <sup>(2)</sup> | FSR0H_SHAD                                                                 |  |   |   | Indi                                                        | rect Data Memo  | ory Address 0 Hig | h Pointer Normal   | (Non-ICD) Shad   | low            |   | xxxx xxxx | uuuu uuuu |  |  |

| FEAh <sup>(2)</sup> | FSR1L_SHAD                                                                 |  |   |   | Ind                                                         | irect Data Memo | ory Address 1 Lov | w Pointer Normal   | (Non-ICD) Shad   | ow             |   | xxxx xxxx | uuuu uuuu |  |  |

| FEBh <sup>(2)</sup> | FSR1H_SHAD                                                                 |  |   |   | Indi                                                        | rect Data Memo  | ory Address 1 Hig | h Pointer Normal   | (Non-ICD) Shad   | low            |   | xxxx xxxx | uuuu uuuu |  |  |

| FECh                | -                                                                          |  | - |   |                                                             |                 | Unimple           | emented            |                  |                |   | _         | _         |  |  |

| FEDh <sup>(2)</sup> | STKPTR                                                                     |  |   | _ | — — — Current Stack pointer                                 |                 |                   |                    |                  |                |   |           | 1 1111    |  |  |

| FEEh <sup>(2)</sup> | TOSL                                                                       |  |   |   | Top of Stack Low byte                                       |                 |                   |                    |                  |                |   |           |           |  |  |

| FEFh <sup>(2)</sup> | TOSH                                                                       |  |   | _ |                                                             |                 | То                | op of Stack High b | oyte             |                |   | -xxx xxxx | -xxx xxxx |  |  |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Only on PIC16F18325/18345. Legend:

Note 1:

2: Register accessible from both User and ICD Debugger. Value on

all other

Resets

Value on:

POR, BOR

Bit 0

| Name     | Bit 7   | Bit 6   | Bit 5               | Bit 4 | Bit 3      | Bit 2     | Bit 1 | Bit 0 | Register<br>on Page |  |  |

|----------|---------|---------|---------------------|-------|------------|-----------|-------|-------|---------------------|--|--|

| OSCCON1  |         | N       | OSC<2:0>            |       |            | NDIV<3:0> |       |       |                     |  |  |

| OSCCON2  | —       | C       | COSC<2:0> CDIV<3:0> |       |            |           |       |       | 90                  |  |  |

| OSCCON3  | CWSHOLD | SOSCPWR | SOSCBE              | ORDY  | NOSCR      | _         | _     | _     | 91                  |  |  |

| OSCSTAT1 | EXTOR   | HFOR    | —                   | LFOR  | SOR        | ADOR      | —     | PLLR  | 92                  |  |  |

| OSCEN    | EXTOEN  | HFOEN   | _                   | LFOEN | SOSCEN     | ADOEN     | _     | _     | 93                  |  |  |

| OSCFRQ   | _       | _       | —                   | _     | HFFRQ<3:0> |           |       |       | 94                  |  |  |

| OSCTUNE  |         |         |                     |       | HFTUN      | N<5:0>    |       |       | 95                  |  |  |

### TABLE 7-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

### TABLE 7-4:SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|----------|----------|---------------------|

| CONFIG1 | 13:8 |         | _       | FCMEN    |          | CSWEN    |          |          | CLKOUTEN |                     |

|         | 7:0  | _       | RSTOSC2 | RSTOSC1  | RSTOSC0  | _        | FEXTOSC2 | FEXTOSC1 | FEXTOSC0 | 64                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

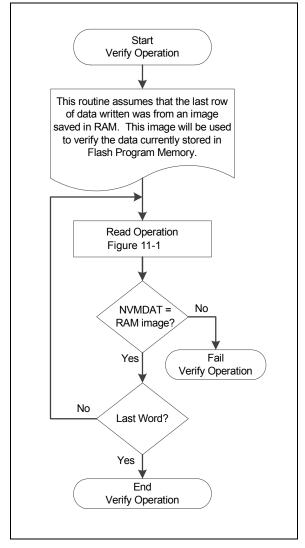

### 11.4.8 WRITE VERIFY

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full row, then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 11-7: PROGRAM FLASH MEMORY VERIFY FLOWCHART

### 12.2.6 ANALOG CONTROL

The ANSELA register (Register 12-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

### 12.2.7 WEAK PULL-UP CONTROL

The WPUA register (Register 12-5) controls the individual weak pull-ups for each PORT pin.

PORTA pin RA3 includes the  $\overline{\text{MCLR}}$ /VPP input. The MCLR input allows the device to be reset, and can be disabled by the MCLRE bit of Configuration Word 2. A weak pull-up is present on the RA3 port pin. This weak pull-up is enabled when  $\overline{\text{MCLR}}$  is enabled ( $\overline{\text{MCLRE}} = 1$ ) or the WPUA3 bit is set. The weak pull-up is disabled when is disabled and the WPUA3 bit is clear.

### 12.2.8 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions.

Each pin defaults to the PORT latch data after Reset. Other output functions are selected with the peripheral pin select logic. See **Section 13.0 "Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs are not shown in the peripheral pin select lists. Digital output functions may continue to control the pin when it is in Analog mode.

| U-0             | U-0                        | R/W-x/u           | R/W-x/u        | U-0                 | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|-----------------|----------------------------|-------------------|----------------|---------------------|------------------|------------------|-------------|

| _               | —                          | LATA5             | LATA4          | —                   | LATA2            | LATA1            | LATA0       |

| bit 7           |                            |                   |                |                     |                  |                  | bit 0       |

|                 |                            |                   |                |                     |                  |                  |             |

| Legend:         |                            |                   |                |                     |                  |                  |             |

| R = Readab      | ole bit                    | W = Writable      | bit            | U = Unimpler        | nented bit, read | as '0'           |             |

| u = Bit is un   | changed                    | x = Bit is unkr   | nown           | -n/n = Value a      | at POR and BOP   | R/Value at all o | ther Resets |

| '1' = Bit is se | et                         | '0' = Bit is clea | ared           |                     |                  |                  |             |

|                 |                            |                   |                |                     |                  |                  |             |

| bit 7-6         | Unimplemen                 | ted: Read as '    | 0'             |                     |                  |                  |             |

| bit 5-4         | <b>LATA&lt;5:4&gt;</b> : F | RA<5:4> Outpu     | it Latch Value | bits <sup>(1)</sup> |                  |                  |             |

| bit 3           | Unimplemen                 | ted: Read as '    | 0'             |                     |                  |                  |             |

| bit 2-0         | <b>LATA&lt;2:0&gt;</b> : F | RA<2:0> Outpu     | it Latch Value | bits <sup>(1)</sup> |                  |                  |             |

### REGISTER 12-3: LATA: PORTA DATA LATCH REGISTER

Note 1: Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

| REGISTER 12-4: | : ANS | ELA: PORTA A | ANALOG SEL | ECT REGI | STER    |     |

|----------------|-------|--------------|------------|----------|---------|-----|

| U-0            | U-0   | R/W-1/1      | R/W-1/1    | U-0      | R/W-1/1 | R/V |

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | ANSA5   | ANSA4   | —   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <ul> <li>ANSA&lt;5:4&gt;: Analog Select between Analog or Digital Function on pins RA&lt;5:4&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

| bit 3   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 2-0 | <ul> <li>ANSA&lt;2:0&gt;: Analog Select between Analog or Digital Function on pins RA&lt;2:0&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| U-0                                          | U-0                                                                                                                                                 | R/W-1/1           | R/W-1/1 | U-0            | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------|----------------|------------------|------------------|--------------|

| —                                            | —                                                                                                                                                   | SLRA5             | SLRA4   | —              | SLRA2            | SLRA1            | SLRA0        |

| bit 7                                        |                                                                                                                                                     |                   |         |                |                  |                  | bit 0        |

| Logond                                       |                                                                                                                                                     |                   |         |                |                  |                  |              |

| Legend:<br>R = Readable bit W = Writable bit |                                                                                                                                                     |                   |         | U = Unimpler   | mented bit, read | as '0'           |              |

| u = Bit is unch                              | anged                                                                                                                                               | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BOI   | R/Value at all c | other Resets |

| '1' = Bit is set                             |                                                                                                                                                     | '0' = Bit is clea | ared    |                |                  |                  |              |

|                                              |                                                                                                                                                     |                   |         |                |                  |                  |              |

| bit 7-6                                      | Unimplement                                                                                                                                         | ted: Read as '    | 0'      |                |                  |                  |              |

| bit 5-4                                      | · · · · · · · · · · · · · · · · · · ·                                                                                                               |                   |         |                |                  |                  |              |

| bit 3                                        | Unimplemented: Read as '0'                                                                                                                          |                   |         |                |                  |                  |              |

| bit 2-0                                      | SLRA<2:0>: PORTA Slew Rate Enable bits<br>For RA<2:0> pins, respectively<br>1 = Port pin slew rate is limited<br>0 = Port pin slews at maximum rate |                   |         |                |                  |                  |              |

### REGISTER 12-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

### REGISTER 12-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | —   | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 INLVLA<5:0>: PORTA Input Level Select bits

For RA<5:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

### 15.5 Register Definitions: Interrupt-on-Change Control

| U-0                                   | U-0                                     | R/W-0/0      | R/W-0/0                                               | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|---------------------------------------|-----------------------------------------|--------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

|                                       | _                                       | IOCAP5       | IOCAP4                                                | IOCAP3                             | IOCAP2  | IOCAP1  | IOCAP0  |  |

| bit 7                                 |                                         |              |                                                       |                                    |         |         | bit 0   |  |

|                                       |                                         |              |                                                       |                                    |         |         |         |  |

| Legend:                               |                                         |              |                                                       |                                    |         |         |         |  |

| R = Readable b                        | oit                                     | W = Writable | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is uncha                      | u = Bit is unchanged x = Bit is unknown |              | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared |                                         |              |                                                       |                                    |         |         |         |  |

### REGISTER 15-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCAP<5:0>:** Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

### REGISTER 15-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0              | U-0                               | R/W-0/0            | R/W-0/0 | R/W-0/0                                              | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------|-----------------------------------|--------------------|---------|------------------------------------------------------|---------|---------|---------|--|

| —                |                                   | IOCAN5             | IOCAN4  | IOCAN3                                               | IOCAN2  | IOCAN1  | IOCAN0  |  |

| bit 7 bit 0      |                                   |                    |         |                                                      |         |         |         |  |

|                  |                                   |                    |         |                                                      |         |         |         |  |

| Legend:          |                                   |                    |         |                                                      |         |         |         |  |

| R = Readable b   | R = Readable bit W = Writable bit |                    | bit     | U = Unimplemented bit, read as '0'                   |         |         |         |  |

| u = Bit is uncha | nged                              | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Reset |         |         |         |  |

### bit 7-6 Unimplemented: Read as '0'

1' = Bit is set

bit 5-0 IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

'0' = Bit is cleared

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

### 18.12 Register Definitions: Comparator Control

| R/W-0/0          | R-0/0                    | U-0                                                                                                                | R/W-0/0          | U-0             | R/W-1/1          | R/W-0/0       | R/W-0/0      |  |

|------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|---------------|--------------|--|

| CxON             | CxOUT                    |                                                                                                                    | CxPOL            | —               | CxSP             | CxHYS         | CxSYNC       |  |

| bit 7            |                          |                                                                                                                    |                  |                 |                  |               | bit (        |  |

| Legend:          |                          |                                                                                                                    |                  |                 |                  |               |              |  |

| R = Readable     | e bit                    | W = Writable                                                                                                       | bit              | U = Unimpler    | mented bit, read | d as '0'      |              |  |

| u = Bit is unc   |                          | x = Bit is unk                                                                                                     |                  |                 | at POR and BC    |               | other Resets |  |

| '1' = Bit is set | •                        | '0' = Bit is cle                                                                                                   |                  |                 |                  |               |              |  |

|                  |                          |                                                                                                                    |                  |                 |                  |               |              |  |

| bit 7            | CxON: Com                | parator Enable                                                                                                     | bit              |                 |                  |               |              |  |

|                  |                          | ator is enabled                                                                                                    |                  |                 |                  |               |              |  |

|                  |                          | ator is disabled                                                                                                   |                  | s no active pow | /er              |               |              |  |

| bit 6            |                          | mparator Outpu                                                                                                     |                  |                 |                  |               |              |  |

|                  |                          | 1 (inverted pola                                                                                                   | <u>rity):</u>    |                 |                  |               |              |  |

|                  | 1 = CxVP <<br>0 = CxVP > |                                                                                                                    |                  |                 |                  |               |              |  |

|                  |                          | 0 (non-inverted                                                                                                    | polarity):       |                 |                  |               |              |  |

|                  | 1 = CxVP >               |                                                                                                                    | <u>,</u>         |                 |                  |               |              |  |

|                  | 0 = CxVP <               | < CxVN                                                                                                             |                  |                 |                  |               |              |  |

| bit 5            | Unimpleme                | nted: Read as                                                                                                      | '0'              |                 |                  |               |              |  |

| bit 4            | CxPOL: Co                | mparator Outpu                                                                                                     | it Polarity Sele | ct bit          |                  |               |              |  |

|                  | 1 = Compara              | ator output is in                                                                                                  | verted           |                 |                  |               |              |  |

|                  | 0 = Compara              | ator output is n                                                                                                   | ot inverted      |                 |                  |               |              |  |

| bit 3            | Unimpleme                | nted: Read as                                                                                                      | '0'              |                 |                  |               |              |  |

| bit 2            | CxSP: Com                | parator Speed/l                                                                                                    | Power Select b   | bit             |                  |               |              |  |

|                  |                          | ator operates ir<br>ed. (do not use)                                                                               | Normal-Powe      | r, High-Speed ı | mode             |               |              |  |

| bit 1            | CxHYS: Cor               | mparator Hyste                                                                                                     | resis Enable b   | it              |                  |               |              |  |

|                  | •                        | CxHYS: Comparator Hysteresis Enable bit<br>1 = Comparator hysteresis enabled<br>0 = Comparator hysteresis disabled |                  |                 |                  |               |              |  |

| bit 0            | -                        | omparator Out                                                                                                      |                  | us Mode bit     |                  |               |              |  |

|                  | 1 = Compar               | rator output to                                                                                                    | Timer1 and I/C   | ) pin is synchr |                  | ges on Timer1 | clock source |  |

|                  |                          | updated on the<br>rator output to 기                                                                                |                  |                 |                  |               |              |  |

|                  |                          |                                                                                                                    |                  |                 |                  |               |              |  |

### REGISTER 18-1: CMxCON0: COMPARATOR Cx CONTROL REGISTER 0

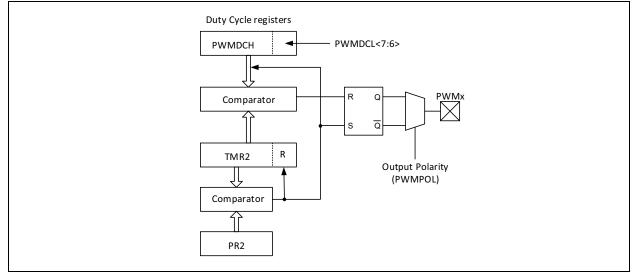

### FIGURE 19-2: SIMPLIFIED PWM BLOCK DIAGRAM

### 19.1.1 PWM PERIOD

Referring to Figure 19-1, the PWM output has a period and a pulse width. The frequency of the PWM is the inverse of the period (1/period).

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

### EQUATION 19-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)Note: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWMx pin is set (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM pulse width is latched from PWMxDC.

| Note: | If the pulse width value is greater than the | he   |  |  |  |  |

|-------|----------------------------------------------|------|--|--|--|--|

|       | period the assigned PWM pin(s) w             | vill |  |  |  |  |

|       | remain unchanged.                            |      |  |  |  |  |

### 19.1.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDC register. The PWMxDCH contains the eight MSbs and bits <7:6> of the PWMxDCL register contain the two LSbs.

The PWMDC register is double-buffered and can be updated at any time. This double buffering is essential for glitch-free PWM operation. New values take effect when TMR2 = PR2. Note that PWMDC is left-justified.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

Equation 19-2 is used to calculate the PWM pulse width.

Equation 19-3 is used to calculate the PWM duty cycle ratio.

### EQUATION 19-2: PULSE WIDTH

Pulse Width =

$$(PWMxDC) \bullet T_{OSC} \bullet$$

• (TMR2 Prescale Value)

### EQUATION 19-3: DUTY CYCLE RATIO

Duty Cycle Ratio =  $\frac{(PWMxDC)}{4(PR2+1)}$

### REGISTER 21-6: CLCxSEL3: GENERIC CLCx DATA 3 SELECT REGISTER

| U-0   | U-0 | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-------------|---------|---------|---------|---------|---------|

| —     | _   | LCxD4S<5:0> |         |         |         |         |         |

| bit 7 |     |             |         |         |         |         | bit 0   |

|       |     |             |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6Unimplemented: Read as '0'bit 5-0LCxD4S<5:0>: CLCx Data 4 Input Selection bits<br/>See Table 21-1.

### REGISTER 21-7: CLCxGLS0: GATE 0 LOGIC SELECT REGISTER

| R/W-x/u  |

|----------|----------|----------|----------|----------|----------|----------|----------|

| LCxG1D4T | LCxG1D4N | LCxG1D3T | LCxG1D3N | LCxG1D2T | LCxG1D2N | LCxG1D1T | LCxG1D1N |

| bit 7    | •        |          |          |          |          |          | bit 0    |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | LCxG1D4T: Gate 0 Data 4 True (non-inverted) bit                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = CLCIN3 (true) is gated into CLCx Gate 0</li> <li>0 = CLCIN3 (true) is not gated into CLCx Gate 0</li> </ul>         |

| bit 6 | LCxG1D4N: Gate 0 Data 4 Negated (inverted) bit                                                                                   |

|       | 1 = CLCIN3 (inverted) is gated into CLCx Gate 0<br>0 = CLCIN3 (inverted) is not gated into CLCx Gate 0                           |

| bit 5 | LCxG1D3T: Gate 0 Data 3 True (non-inverted) bit                                                                                  |

|       | <ul> <li>1 = CLCIN2 (true) is gated into CLCx Gate 0</li> <li>0 = CLCIN2 (true) is not gated into CLCx Gate 0</li> </ul>         |

| bit 4 | LCxG1D3N: Gate 0 Data 3 Negated (inverted) bit                                                                                   |

|       | <ul> <li>1 = CLCIN2 (inverted) is gated into CLCx Gate 0</li> <li>0 = CLCIN2 (inverted) is not gated into CLCx Gate 0</li> </ul> |

| bit 3 | LCxG1D2T: Gate 0 Data 2 True (non-inverted) bit                                                                                  |

|       | <ul> <li>1 = CLCIN1 (true) is gated into CLCx Gate 0</li> <li>0 = CLCIN1 (true) is not gated into CLCx Gate 0</li> </ul>         |

| bit 2 | LCxG1D2N: Gate 0 Data 2 Negated (inverted) bit                                                                                   |

|       | <ul> <li>1 = CLCIN1 (inverted) is gated into CLCx Gate 0</li> <li>0 = CLCIN1 (inverted) is not gated into CLCx Gate 0</li> </ul> |

| bit 1 | LCxG1D1T: Gate 0 Data 1 True (non-inverted) bit                                                                                  |

|       | <ul> <li>1 = CLCIN0 (true) is gated into CLCx Gate 0</li> <li>0 = CLCIN0 (true) is not gated into CLCx Gate 0</li> </ul>         |

| bit 0 | LCxG1D1N: Gate 0 Data 1 Negated (inverted) bit                                                                                   |

|       | <ul> <li>1 = CLCIN0 (inverted) is gated into CLCx Gate 0</li> <li>0 = CLCIN0 (inverted) is not gated into CLCx Gate 0</li> </ul> |

|       |                                                                                                                                  |

| R/W-x/u         | R/W-x/u                         | R/W-x/u                                              | R/W-x/u | R/W-x/u                            | R/W-x/u          | R/W-x/u      | R/W-x/u |

|-----------------|---------------------------------|------------------------------------------------------|---------|------------------------------------|------------------|--------------|---------|

| —               | —                               | —                                                    | —       | —                                  | —                | ADRES        | S<9:8>  |

| bit 7           |                                 |                                                      |         |                                    |                  |              | bit 0   |

|                 |                                 |                                                      |         |                                    |                  |              |         |

| Legend:         |                                 |                                                      |         |                                    |                  |              |         |

| R = Readable    | = Readable bit W = Writable bit |                                                      | bit     | U = Unimplemented bit, read as '0' |                  |              |         |

| u = Bit is unch | anged                           | nged x = Bit is unknown -n/n = Value at POR and BOR/ |         |                                    | R/Value at all o | other Resets |         |

### REGISTER 22-6: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

bit 7-2 **Reserved**: Do not use.

'1' = Bit is set

bit 1-0 **ADRES<9:8>**: ADC Result Register bits Upper two bits of 10-bit conversion result

### REGISTER 22-7: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

'0' = Bit is cleared

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---------|------------|---------|---------|---------|---------|---------|---------|

|         | ADRES<7:0> |         |         |         |         |         |         |

| bit 7   |            |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 **ADRES<7:0>**: ADC Result Register bits Lower eight bits of 10-bit conversion result

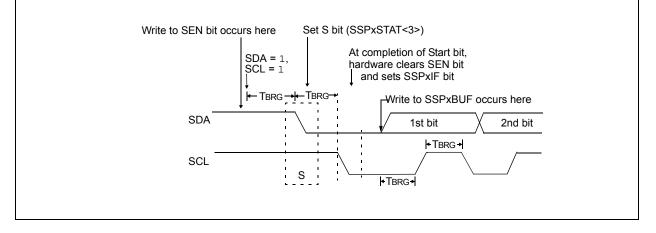

### 30.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 30-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSPxSTAT register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its idle state.

- **2:** The Philips I<sup>2</sup>C specification states that a bus collision cannot occur on a Start.

### FIGURE 30-26: FIRST START BIT TIMING

### **REGISTER 31-4:** RC1REG<sup>(1)</sup>: RECEIVE DATA REGISTER

| R-0              | R-0   | R-0                 | R-0  | R-0            | R-0              | R-0              | R-0         |

|------------------|-------|---------------------|------|----------------|------------------|------------------|-------------|

|                  |       |                     | RC1F | REG<7:0>       |                  |                  |             |

| bit 7            |       |                     |      |                |                  |                  | bit 0       |

|                  |       |                     |      |                |                  |                  |             |

| Legend:          |       |                     |      |                |                  |                  |             |

| R = Readable b   | bit   | W = Writable bit    |      | U = Unimpler   | mented bit, read | l as '0'         |             |

| u = Bit is uncha | inged | x = Bit is unknow   | /n   | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |       | '0' = Bit is cleare | d    |                |                  |                  |             |

bit 7-0 **RC1REG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 31-2)

**Note 1:** RC1REG (including the ninth bit) is double buffered, and data is available while new data is being received.

## REGISTER 31-5: TX1REG<sup>(1)</sup>: TRANSMIT DATA REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| TX1REG<7:0> |       |       |       |       |       |       |       |

| bit 7       |       |       |       |       |       |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TX1REG<7:0>:** Lower eight bits of the received data; read-only; see also RX9D (Register 31-1)

**Note 1:** TX1REG (including the ninth bit) is double buffered, and can be written when previous data has started shifting.

# REGISTER 31-6: SP1BRGL<sup>(1)</sup>: BAUD RATE GENERATOR REGISTER

| R/W-0           | R/W-0 | R/W-0             | R/W-0 | R/W-0         | R/W-0           | R/W-0  | R/W-0 |

|-----------------|-------|-------------------|-------|---------------|-----------------|--------|-------|

|                 |       |                   | SP1BF | RG<7:0>       |                 |        |       |

| bit 7           |       |                   |       |               |                 |        | bit 0 |

|                 |       |                   |       |               |                 |        |       |

| Legend:         |       |                   |       |               |                 |        |       |

| P - Poodablo bi | +     | M = M/ritable bit |       | II – Unimplor | nontod hit road | ac 'O' |       |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SP1BRG<7:0>: Lower eight bits of the Baud Rate Generator

**Note 1:** Writing to SP1BRG resets the BRG counter.

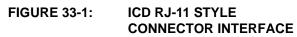

### 33.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process, allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the program memory, data EEPROM, user IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16(L)F183XX Memory Programming Specification" (DS40001738).

### 33.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

### 33.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC<sup>®</sup> Flash MCUs to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'. The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete, MCLR must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.4** "**MCLR**" for more information.

### 33.3 Common Programming Interfaces

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 33-1.

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 33-2.

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 33-3 for more information.

# PIC16(L)F18325/18345

$0 \leq f \leq 127$

$0 \rightarrow \text{dest} < 7 >$ (f<7:1>)  $\rightarrow \text{dest} < 6:0 >$ ,

$(f<0>) \rightarrow C,$

0-

The contents of register 'f' are shifted one bit to the right through the Carry flag. A '0' is shifted into the MSb. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'.

register f

С

C, Z

$d \in [0,1]$

Operands:

Operation:

Status Affected:

Description:

| LSLF                             | Logical Left Shift                     | MOVF             | Move f                                                                                                                                                                                                                                                                            |  |

|----------------------------------|----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                          | [ <i>label</i> ]LSLF f{,d}             | Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |  |

| Operands:                        | $0 \le f \le 127$<br>d $\in [0,1]$     | Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                |  |

| Operation:                       | $(f < 7 >) \rightarrow C$              | Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                          |  |

|                                  | $(f < 6:0 >) \rightarrow dest < 7:1 >$ | Status Affected: | Z                                                                                                                                                                                                                                                                                 |  |

| Status Affected:<br>Description: |                                        |                  | The contents of register f is moved to<br>a destination dependent upon the<br>status of d. If $d = 0$ , destination is W<br>register. If $d = 1$ , the destination is file<br>register f itself. $d = 1$ is useful to test a<br>file register since status flag Z is<br>affected. |  |

|                                  | C ← register f ← 0                     | Words:           | 1                                                                                                                                                                                                                                                                                 |  |

|                                  |                                        | Cycles:          | 1                                                                                                                                                                                                                                                                                 |  |

|                                  |                                        | Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                       |  |

| LSRF                             | Logical Right Shift                    |                  | After Instruction<br>W = value in FSR register                                                                                                                                                                                                                                    |  |

| Syntax:                          | [label]LSRF f{,d}                      |                  | Z = 1                                                                                                                                                                                                                                                                             |  |

| DC CHARACTERISTICS |      |                                      | Standard Operating Conditions (unless otherwise stated) |                     |               |              |                                                                                                                                                    |  |  |  |  |  |  |

|--------------------|------|--------------------------------------|---------------------------------------------------------|---------------------|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Param.<br>No.      | Sym. | Characteristic                       | Min.                                                    | Тур.†               | Max.          | Units        | Conditions                                                                                                                                         |  |  |  |  |  |  |

|                    | VIL  | Input Low Voltage                    |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |  |  |  |

|                    |      | I/O PORT:                            |                                                         | -                   |               | -            |                                                                                                                                                    |  |  |  |  |  |  |

| D300               |      | with TTL buffer                      | —                                                       | —                   | 0.8           | V            | 4.5V ≤ VDD ≤ 5.5V                                                                                                                                  |  |  |  |  |  |  |

| D301               |      |                                      | —                                                       | _                   | 0.15 VDD      | V            | $1.8V \leq VDD \leq 4.5V$                                                                                                                          |  |  |  |  |  |  |

| D302               |      | with Schmitt Trigger buffer          | —                                                       | _                   | 0.2 VDD       | V            | 2.0V ≤ VDD ≤ <del>5.5</del> V                                                                                                                      |  |  |  |  |  |  |

| D303               |      | with I <sup>2</sup> C levels         | _                                                       | _                   | 0.3 VDD       | V            | $\frown$                                                                                                                                           |  |  |  |  |  |  |

| D304               |      | with SMBus levels                    | —                                                       | _                   | 0.8           | V /          | $2.7V \leq VDD \leq 5.5V$                                                                                                                          |  |  |  |  |  |  |

| D305               |      | MCLR                                 |                                                         | _                   | 0.2 VDD       | K            |                                                                                                                                                    |  |  |  |  |  |  |

|                    | VIH  | Input High Voltage                   |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |  |  |  |

|                    |      | I/O PORT:                            |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |  |  |  |

| D320               |      | with TTL buffer                      | 2.0                                                     | _                   | _\ `          | $\checkmark$ | $4.5V \neq VDD \leq 5.5V$                                                                                                                          |  |  |  |  |  |  |

| D321               |      |                                      | 0.25 VDD + 0.8                                          | _                   | $  - \rangle$ | $\vee$       | $1.8V \le VDD \le 4.5V$                                                                                                                            |  |  |  |  |  |  |

| D322               |      | with Schmitt Trigger buffer          | 0.8 Vdd                                                 | <                   | <u> </u>      | $\sqrt{}$    | $2.0V \leq V\text{DD} \leq 5.5V$                                                                                                                   |  |  |  |  |  |  |

| D323               |      | with I <sup>2</sup> C levels         | 0.7 Vdd                                                 |                     | /-/           | $\vee$       |                                                                                                                                                    |  |  |  |  |  |  |

| D324               |      | with SMBus levels                    | 2.1 '                                                   | $\langle - \langle$ |               | > v          | $2.7V \le V\text{DD} \le 5.5V$                                                                                                                     |  |  |  |  |  |  |

| D325               |      | MCLR                                 | 0.7 VDD                                                 | $ \ge $             |               | V            |                                                                                                                                                    |  |  |  |  |  |  |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup> |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |  |  |  |

| D340               |      | I/O Ports                            | 7                                                       | ±5                  | ± 125         | nA           | $\label{eq:VSS} \begin{split} VSS &\leq V PIN \leq V DD, \\ Pin \ at \ high-impedance, \ 85^\circ C \end{split}$                                   |  |  |  |  |  |  |

| D341               |      | <                                    | A/                                                      | ₹5                  | ± 1000        | nA           | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at high-impedance, } 125^{\circ}{\sf C} \end{split}$ |  |  |  |  |  |  |

| D342               |      | MCLR <sup>(2)</sup>                  | $\square$                                               | ± 50                | ± 200         | nA           | VSS $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, 85°C                                                                                            |  |  |  |  |  |  |

|                    | IPUR | Weak Pull-up Current                 |                                                         |                     | •             |              |                                                                                                                                                    |  |  |  |  |  |  |

| D350               |      | $\land$                              | 25                                                      | 120                 | 200           | μA           | VDD = 3.0V, VPIN = VSS                                                                                                                             |  |  |  |  |  |  |

|                    | Vol  | Output Low Voltage <sup>(4)</sup>    | >                                                       |                     |               |              |                                                                                                                                                    |  |  |  |  |  |  |

| D360               |      | I/O ports                            | —                                                       | _                   | 0.6           | V            | IOL = 10.0 mA, VDD = 3.0V                                                                                                                          |  |  |  |  |  |  |

|                    | Vон  |                                      |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |  |  |  |

| D370               |      | I/Q ports                            | Vdd - 0.7                                               | _                   | _             | V            | Юн = 6.0 mA, VDD = 3.0V                                                                                                                            |  |  |  |  |  |  |