#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

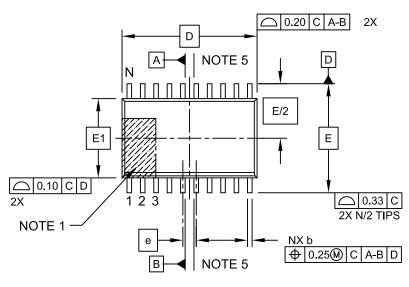

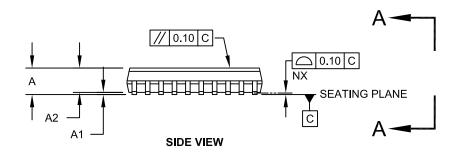

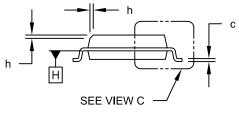

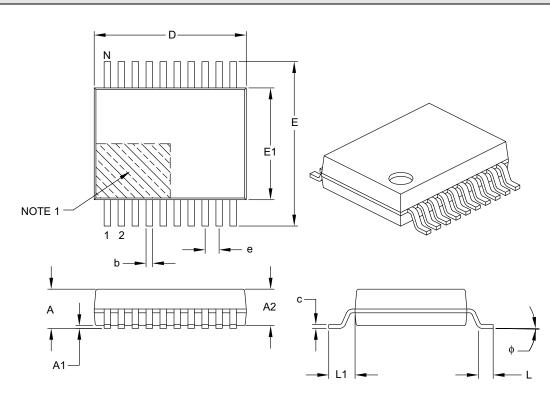

| Package / Case             | 16-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 16-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18325t-i-jq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.4 Stack

All devices have a 16-level x 15-bit wide hardware stack (refer to Figure 4-4 through Figure 4-7). The stack space is not part of either program or data space. The PC is PUSHed onto the stack when CALL or CALLW instructions are executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer and does not cause a Reset when either a Stack Overflow or Underflow occur if the STVREN bit is programmed to '0' (Configuration Words). This means that after the stack has been PUSHed sixteen times, the seventeenth PUSH overwrites the value that was stored from the first PUSH. The eighteenth PUSH overwrites the second PUSH (and so on). The STKOVF and STKUNF flag bits will be set on an Overflow/Underflow, regardless of whether the Reset is enabled.

If the STVREN bit in Configuration Words is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

Note 1: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, CALLW, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 4.4.1 ACCESSING THE STACK

The stack is accessible through the TOSH, TOSL and STKPTR registers. STKPTR is the current value of the Stack Pointer. TOSH:TOSL register pair points to the TOP of the stack. Both registers are read/writable. TOS is split into TOSH and TOSL due to the 15-bit size of the PC. To access the stack, adjust the value of STKPTR, which will position TOSH:TOSL, then read/write to TOSH:TOSL. STKPTR is five bits to allow detection of overflow and underflow.

| Note: | Care should be taken when modifying the |

|-------|-----------------------------------------|

|       | STKPTR while interrupts are enabled.    |

During normal program operation, CALL, CALLW and Interrupts will increment STKPTR while RETLW, RETURN, and RETFIE will decrement STKPTR. At any time, STKPTR can be read to see how many levels remain available on the stack. The STKPTR always points at the currently used place on the stack. Therefore, a CALL or CALLW will increment the STKPTR and then write the PC, and a return will write the PC and then decrement the STKPTR.

Reference Figure 4-4 through Figure 4-7 for examples of accessing the stack.

| REGISTER                                                                 | R 5-3: CONF      | -IGURATION                       | WORD 3: M | EMORY         |                   |              |            |  |

|--------------------------------------------------------------------------|------------------|----------------------------------|-----------|---------------|-------------------|--------------|------------|--|

|                                                                          |                  | R/P-1                            | U-1       | U-1           | U-1               | U-1          | U-1        |  |

|                                                                          |                  | LVP <sup>(1)</sup>               | —         | —             | —                 | _            | —          |  |

|                                                                          |                  | bit 13                           |           |               |                   |              | bit 8      |  |

|                                                                          |                  |                                  |           |               |                   |              |            |  |

| U-1                                                                      | U-1              | U-1                              | U-1       | U-1           | U-1               | R/P-1        | R/P-1      |  |

| _                                                                        | —                | —                                | —         | —             | _                 | WRT1         | WRT0       |  |

| bit 7                                                                    |                  |                                  |           |               |                   |              | bit 0      |  |

|                                                                          |                  |                                  |           |               |                   |              |            |  |

| Legend:                                                                  |                  |                                  |           |               |                   |              |            |  |

| R = Readable bit P = Programmable bit U = Unimplemented bit, read as '1' |                  |                                  |           |               |                   |              |            |  |

| '0' = Bit is c                                                           | leared           | '1' = Bit is set                 |           | n = Value whe | en blank or afte  | r Bulk Erase |            |  |

|                                                                          |                  |                                  |           |               |                   |              |            |  |

| bit 13                                                                   |                  | ltage Programn                   |           |               |                   |              |            |  |

|                                                                          |                  | ow-Voltage Pro                   | • •       | enabled. MC   | LR/VPP pin f      | unction is M | CLR. MCLRE |  |

|                                                                          |                  | onfiguration bit<br>V on MCLR/VP |           | for programm  | ina               |              |            |  |

| bit 12-2                                                                 |                  | ted: Read as '                   |           |               | ing.              |              |            |  |

| bit 1-0                                                                  | -                | Jser NVM Self-                   |           | n hita        |                   |              |            |  |

| DIL 1-0                                                                  |                  | Write protectio                  |           | IT DILS       |                   |              |            |  |

|                                                                          |                  | 0000h to 01FF                    |           | ed 0200h to 1 | -<br>FFh may be m | nodified     |            |  |

|                                                                          |                  | 0000h to 0FFF                    |           |               |                   |              |            |  |

|                                                                          |                  | 0000h to 1FFF                    | •         |               | •                 |              |            |  |

|                                                                          |                  | only to the self-                |           |               |                   |              | protected. |  |

| Note 1.                                                                  | The LVP hit cann | -                                |           |               |                   |              |            |  |

### **REGISTER 5-3: CONFIGURATION WORD 3: MEMORY**

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

| R-q/q           | R-q/q             | U-0                                                                       | R-q/q      | R-q/q             | R-q/q              | U-0              | R-q/q       |  |  |

|-----------------|-------------------|---------------------------------------------------------------------------|------------|-------------------|--------------------|------------------|-------------|--|--|

| EXTOR           | HFOR              | _                                                                         | LFOR       | SOR               | ADOR               |                  | PLLR        |  |  |

| bit 7           |                   |                                                                           |            |                   |                    |                  | bit 0       |  |  |

| Legend:         |                   |                                                                           |            |                   |                    |                  |             |  |  |

| R = Readab      | lo hit            | W = Writable                                                              | bit        | II – Unimploy     | nented bit, read   | ac '0'           |             |  |  |

| u = Bit is un   |                   | x = Bit is unkr                                                           |            |                   | at POR and BOI     |                  | thar Pacata |  |  |

| '1' = Bit is se | •                 | 6' = Bit is clear                                                         |            |                   | at FOR and BOI     | N value at all t |             |  |  |

|                 |                   |                                                                           | areu       |                   |                    |                  |             |  |  |

| q = Reset va    | alue is determine | a by hardware                                                             |            |                   |                    |                  |             |  |  |

| bit 7           | 1 = The osc       | TOSC (external<br>cillator is ready<br>cillator is not en                 | to be used | -                 | be used.           |                  |             |  |  |

| bit 6           | 1 = The osc       | TOSC Oscillato<br>cillator is ready<br>cillator is not en                 | to be used | ot yet ready to b | be used.           |                  |             |  |  |

| bit 5           | Unimplemer        | nted: Read as '                                                           | 0'         |                   |                    |                  |             |  |  |

| bit 4           | 1 = The osc       | LFOR: LFINTOSC Oscillator Ready<br>1 = The oscillator is ready to be used |            |                   |                    |                  |             |  |  |

| bit 3           | 1 = The osc       | dary Oscillator l<br>cillator is ready<br>cillator is not er              | to be used | ot yet ready to I | pe used.           |                  |             |  |  |

| bit 2           | 1 = The osc       | ADOR: ADCRC Oscillator Ready<br>1 = The oscillator is ready to be used    |            |                   |                    |                  |             |  |  |

| bit 1           | Unimplemer        | nted: Read as '                                                           | 0'         |                   |                    |                  |             |  |  |

| bit 0           |                   | L is ready to be                                                          |            | l input source is | s not ready, or th | ne PLL is not re | eady.       |  |  |

### REGISTER 7-4: OSCSTAT1: OSCILLATOR STATUS REGISTER 1

| R/W-0/0                                                                                                                                                                                                                                           | R/W-0/0                                                                                                                                                                                               | U-0                                                                                                                                                    | R/W-0/0 | R/W-0/0        | R/W-0/0          | U-0              | U-0          |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|------------------|------------------|--------------|--|--|

| EXTOEN                                                                                                                                                                                                                                            | HFOEN                                                                                                                                                                                                 | _                                                                                                                                                      | LFOEN   | SOSCEN         | ADOEN            | _                | _            |  |  |

| bit 7                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |                                                                                                                                                        |         |                |                  |                  | bit 0        |  |  |

|                                                                                                                                                                                                                                                   |                                                                                                                                                                                                       |                                                                                                                                                        |         |                |                  |                  |              |  |  |

| Legend:                                                                                                                                                                                                                                           |                                                                                                                                                                                                       |                                                                                                                                                        |         |                |                  |                  |              |  |  |

| R = Readable                                                                                                                                                                                                                                      | bit                                                                                                                                                                                                   | W = Writable                                                                                                                                           | bit     | U = Unimplen   | nented bit, read | d as '0'         |              |  |  |

| u = Bit is unch                                                                                                                                                                                                                                   | anged                                                                                                                                                                                                 | x = Bit is unkr                                                                                                                                        | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is set                                                                                                                                                                                                                                  |                                                                                                                                                                                                       | '0' = Bit is clea                                                                                                                                      | ared    |                |                  |                  |              |  |  |

| bit 7 EXTOEN: External Oscillator Manual Request Enable bit<br>1 = EXTOSC is explicitly enabled, operating as specified by FEXTOSC<br>0 = EXTOSC could be enabled by another module<br>bit 6 HEOEN: HEINTOSC Oscillator Manual Request Enable bit |                                                                                                                                                                                                       |                                                                                                                                                        |         |                |                  |                  |              |  |  |

| bit 6                                                                                                                                                                                                                                             | <b>HFOEN:</b> HFINTOSC Oscillator Manual Request Enable bit<br>1 = HFINTOSC is explicitly enabled, operating as specified by OSCFRQ (Register 7-6)<br>0 = HFINTOSC could be enabled by another module |                                                                                                                                                        |         |                |                  |                  |              |  |  |

| bit 5                                                                                                                                                                                                                                             | Unimplemen                                                                                                                                                                                            | ted: Read as '                                                                                                                                         | 0'      |                |                  |                  |              |  |  |

| bit 4                                                                                                                                                                                                                                             | 1 = LFINTOS                                                                                                                                                                                           | LFOEN: LFINTOSC (31 kHz) Oscillator Manual Request Enable bit<br>1 = LFINTOSC is explicitly enabled<br>0 = LFINTOSC could be enabled by another module |         |                |                  |                  |              |  |  |

| bit 3                                                                                                                                                                                                                                             | <b>SOSCEN:</b> Secondary Oscillator Manual Request Enable bit<br>1 = Secondary Oscillator is explicitly enabled<br>0 = Secondary Oscillator could be enabled by another module                        |                                                                                                                                                        |         |                |                  |                  |              |  |  |

| bit 2                                                                                                                                                                                                                                             | 1 = ADOSC is                                                                                                                                                                                          | ADOEN: ADOSC (600 kHz) Oscillator Manual Request Enable bit<br>1 = ADOSC is explicitly enabled<br>0 = ADOSC could be enabled by another module         |         |                |                  |                  |              |  |  |

| bit 1                                                                                                                                                                                                                                             | Unimplemen                                                                                                                                                                                            | ted: Read as '                                                                                                                                         | 0'      |                |                  |                  |              |  |  |

| bit 0                                                                                                                                                                                                                                             | Unimplemen                                                                                                                                                                                            |                                                                                                                                                        |         |                |                  |                  |              |  |  |

# REGISTER 7-5: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|-------|-------|-------|-------|-----------|-------|-------|--------|---------------------|

| STATUS | —     | _     | _     | TO    | PD        | Z     | DC    | С      | 30                  |

| WDTCON | —     | —     |       | ١     | WDTPS<4:0 | >     |       | SWDTEN | 121                 |

### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

| TABLE 10-4: S | SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER |

|---------------|---------------------------------------------------|

|---------------|---------------------------------------------------|

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 |         | _       | DEBUG    | STVREN   | PPS1WAY  |          | BORV    |         | 05                  |

| CONFIG2 | 7:0  | BOREN1  | BOREN0  | LPBOREN  |          | WDTE1    | WDTE0    | PWRTE   | MCLRE   | 65                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

| W-0/0                                                                | W-0/0  | W-0/0               | W-0/0 | W-0/0                                              | W-0/0 | W-0/0 | W-0/0 |  |

|----------------------------------------------------------------------|--------|---------------------|-------|----------------------------------------------------|-------|-------|-------|--|

|                                                                      |        |                     | NVN   | ICON2                                              |       |       |       |  |

| bit 7                                                                |        |                     |       |                                                    |       |       | bit 0 |  |

|                                                                      |        |                     |       |                                                    |       |       |       |  |

| Legend:                                                              |        |                     |       |                                                    |       |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |                     |       |                                                    |       |       |       |  |

| S = Bit can only b                                                   | oe set | x = Bit is unknow   | 'n    | -n/n = Value at POR and BOR/Value at all other Res |       |       |       |  |

| '1' = Bit is set                                                     |        | '0' = Bit is cleare | d     |                                                    |       |       |       |  |

### REGISTER 11-6: NVMCON2: NONVOLATILE MEMORY CONTROL 2 REGISTER

#### bit 7-0 NVMCON2<7:0>: Flash Memory Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the NVMCON1 register. The value written to this register is used to unlock the writes.

TABLE 11-5: SUMMARY OF REGISTERS ASSOCIATED WITH NONVOLATILE MEMORY (NVM)

| Name    | Bit 7            | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                                          |      |       |        |         |        | Register<br>on Page |     |

|---------|------------------|------------------------------------------------------------------------------------|------|-------|--------|---------|--------|---------------------|-----|

| INTCON  | GIE              | PEIE                                                                               | —    | —     | —      | —       | _      | INTEDG              | 101 |

| PIR2    | TMR6IF           | C2IF                                                                               | C1IF | NVMIF | SSP2IF | BLC2IF  | TMR4IF | NCO1IF              | 109 |

| PIE2    | TMR6IE           | C2IE                                                                               | C1IE | NVMIE | SSP2IE | BLC2IE  | TMR4IE | NCO1IE              | 104 |

| NVMCON1 | _                | NVMREGS         LWLO         FREE         WRERR         WREN         WR         RD |      |       |        |         |        |                     |     |

| NVMCON2 | NVMCON2          |                                                                                    |      |       |        |         |        |                     |     |

| NVMADRL | NVMADR<7:0>      |                                                                                    |      |       |        |         |        |                     |     |

| NVMADRH | (1) NVMADR<14:8> |                                                                                    |      |       |        |         |        |                     | 137 |

| NVMDATL | NVMDAT<7:0>      |                                                                                    |      |       |        |         |        |                     | 137 |

| NVMDATH |                  | _                                                                                  |      |       | NVMDA  | T<13:8> |        |                     | 137 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by NVM. **Note 1:** Unimplemented, read as '1'.

| TABLE 11-0. SUMIWART OF CONFIGURATION WORD WITH NONVOLATILE MEMORY (NYM) | TABLE 11-6: | SUMMARY OF CONFIGURATION WORD WITH NONVOLATILE MEMORY (NVM) |

|--------------------------------------------------------------------------|-------------|-------------------------------------------------------------|

|--------------------------------------------------------------------------|-------------|-------------------------------------------------------------|

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG3 | 13:8 | _       | _       | LVP      | —        | —        | —        | —       | _       | 66                  |

|         | 7:0  | _       | _       | _        | _        | _        | —        | WRT     | <1:0>   |                     |

| CONFIG4 | 13:8 | _       | _       | _        | _        | _        | —        | _       | _       | 67                  |

|         | 7:0  | _       | _       | _        | _        | _        | _        | CPD     | CP      |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by NVM.

© 2015-2016 Microchip Technology Inc.

## 22.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 22-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 22-4. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 22-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 22-1: ACQUISITION TIME EXAMPLE

sumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

As

$$Tc = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 2\mu s + 892ns + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| L = Right just<br>loaded.<br>) = Left just<br>loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADCS<2:0><br>W = Writable I<br>x = Bit is unkn<br>'0' = Bit is clea<br>Result Format S<br>stified. Six Most                                                                               | own<br>ared<br>Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n/n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADNREF<br>mented bit, read<br>at POR and BO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | EF<1:0><br>bit (<br>other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADFM: ADC<br>L = Right ju:<br>loaded.<br>) = Left just<br>loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkn<br>'0' = Bit is clea<br>Result Format S<br>stified. Six Most                                                                                                              | own<br>ared<br>Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n/n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ADFM: ADC<br>L = Right ju:<br>loaded.<br>) = Left just<br>loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkn<br>'0' = Bit is clea<br>Result Format S<br>stified. Six Most                                                                                                              | own<br>ared<br>Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n/n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADFM: ADC<br>L = Right ju:<br>loaded.<br>) = Left just<br>loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkn<br>'0' = Bit is clea<br>Result Format S<br>stified. Six Most                                                                                                              | own<br>ared<br>Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n/n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADFM: ADC<br>L = Right ju:<br>loaded.<br>) = Left just<br>loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkn<br>'0' = Bit is clea<br>Result Format S<br>stified. Six Most                                                                                                              | own<br>ared<br>Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n/n = Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADFM: ADC<br>= Right ju:<br>loaded.<br>) = Left just<br>loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | '0' = Bit is clea<br>Result Format s<br>stified. Six Most                                                                                                                                 | ared<br>Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | at POR and BO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/Value at all (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | other Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |