Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 16-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 16-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18325-e-jq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                                         | Function | Input<br>Type    | Output Type | Description                      |

|--------------------------------------------------------------------------------------------------------------|----------|------------------|-------------|----------------------------------|

| RC4/ANC4/T3G <sup>(1)</sup> / SCK2 <sup>(1)</sup> /                                                          | RC4      | TTL/ST           | CMOS        | General purpose I/O.             |

| SCL2 <sup>(1,3)</sup> / CLCIN1 <sup>(1)</sup>                                                                | ANC4     | AN               | —           | ADC Channel C4 input.            |

|                                                                                                              | T3G      | TTL/ST           | —           | TMR3 gate input.                 |

|                                                                                                              | SCK2     | TTL/ST           | CMOS        | SPI Clock 2.                     |

|                                                                                                              | SCL2     | l <sup>2</sup> C | OD          | I <sup>2</sup> C Clock 2.        |

|                                                                                                              | CLCIN1   | TTL/ST           | —           | Configurable Logic Cell 1 input. |

| RC5/ANC5/MDCIN2 <sup>(1)</sup> /                                                                             | RC5      | TTL/ST           | CMOS        | General purpose I/O.             |

| T3CKI <sup>(1)</sup> /CCP1 <sup>(1)</sup> /SDI2 <sup>(1)</sup> /<br>SDA2 <sup>(1,3)</sup> /RX <sup>(1)</sup> | ANC5     | AN               | —           | ADC Channel C5 input.            |

| SDAZ                                                                                                         | MDCIN2   | TTL/ST           | —           | Modular Carrier input 2.         |

|                                                                                                              | T3CKI    | TTL/ST           | —           | TMR3 Clock input.                |

|                                                                                                              | CCP1     | TTL/ST           | CMOS        | Capture/Compare/PWM 1 input.     |

|                                                                                                              | SDI2     | TTL/ST           | CMOS        | SPI Data 2.                      |

|                                                                                                              | SDA2     | l <sup>2</sup> C | OD          | I <sup>2</sup> C Data 2.         |

|                                                                                                              | RX       | TTL/ST           | CMOS        | EUSART asynchronous input.       |

| Vdd                                                                                                          | Vdd      | Power            | _           | Positive supply.                 |

| Vss                                                                                                          | Vss      | Power            | _           | Ground reference.                |

#### TABLE 1-2:PIC16(L)F18325 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS=CMOS compatible input or output OD = Open-Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

### TABLE 1-3: PIC16(L)F18345 PINOUT DESCRIPTION

| Name                                                                                                                                     | Function | Input<br>Type | Output<br>Type | Description                                           |

|------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|----------------|-------------------------------------------------------|

| RA0/ANA0/C1IN0+/DAC1OUT/                                                                                                                 | RA0      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| ICDDAT/ICSPDAT                                                                                                                           | ANA0     | AN            | _              | ADC Channel A0 input.                                 |

|                                                                                                                                          | C1IN0+   | AN            | _              | Comparator C1 positive input.                         |

|                                                                                                                                          | DAC1OUT  | _             | AN             | Digital-to-Analog Converter output.                   |

|                                                                                                                                          | ICDDAT   | TTL/ST        | CMOS           | In-Circuit Debug Data I/O.                            |

|                                                                                                                                          | ICSPDAT  | TTL/ST        | CMOS           | ICSP™ Data I/O.                                       |

| RA1/ANA1/VREF+/C1IN0-/                                                                                                                   | RA1      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| C2IN0-/ DAC1REF+/SS2 <sup>(1)</sup> /                                                                                                    | ANA1     | AN            | _              | ADC Channel A1 input.                                 |

| ICDCLK/ ICSPCLK                                                                                                                          | VREF+    | AN            | _              | ADC positive voltage reference input.                 |

|                                                                                                                                          | C1IN0-   | AN            | _              | Comparator C1 negative input.                         |

|                                                                                                                                          | C2IN0-   | AN            | _              | Comparator C2 negative input.                         |

|                                                                                                                                          | DAC1REF+ | AN            | _              | Digital-to-Analog Converter positive reference input. |

|                                                                                                                                          | SS2      | TTL/ST        | _              | Slave Select 2 input.                                 |

|                                                                                                                                          | ICDCLK   | TTL/ST        | CMOS           | In-Circuit Debug Clock I/O.                           |

|                                                                                                                                          | ICSPCLK  | TTL/ST        | CMOS           | ICSPTM Clock I/O.                                     |

| RA2/ANA2/VREF-/ DAC1REF-/                                                                                                                | RA2      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| T0CKI <sup>(1)</sup> / CCP3 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> /<br>CWG2IN <sup>(1)</sup> /CLCIN0 <sup>(1)</sup> / INT <sup>(1)</sup> | ANA2     | AN            | _              | ADC Channel A2 input.                                 |

|                                                                                                                                          | VREF-    | AN            | _              | ADC negative voltage reference input.                 |

|                                                                                                                                          | DAC1REF- | AN            | _              | Digital-to-Analog Converter negative reference input. |

|                                                                                                                                          | TOCKI    | TTL/ST        | _              | TMR0 Clock input.                                     |

|                                                                                                                                          | CCP3     | TTL/ST        | CMOS           | Capture/Compare/PWM 3 input.                          |

|                                                                                                                                          | CWG1IN   | TTL/ST        | —              | Complementary Waveform Generator 1 input.             |

|                                                                                                                                          | CWG2IN   | TTL/ST        | —              | Complementary Waveform Generator 2 input.             |

|                                                                                                                                          | CLCIN0   | TTL/ST        | —              | Configurable Logic Cell 0 input.                      |

|                                                                                                                                          | INT      | TTL/ST        | —              | External interrupt input.                             |

| RA3/MCLR/VPP                                                                                                                             | RA3      | TTL/ST        | CMOS           | General purpose I/O.                                  |

|                                                                                                                                          | MCLR     | TTL/ST        | _              | Master Clear with internal pull-up.                   |

|                                                                                                                                          | VPP      | HV            | —              | Programming voltage.                                  |

| RA4/ANA4/T1G <sup>(1)</sup> /T3G <sup>(1)</sup> /T5G <sup>(1)</sup> /                                                                    | RA4      | TTL/ST        | CMOS           | General purpose I/O.                                  |

| SOSCO/CCP4 <sup>(1)</sup> /CLKOUT/<br>OSC2                                                                                               | ANA4     | AN            | _              | ADC Channel A4 input.                                 |

| 0302                                                                                                                                     | T1G      | TTL/ST        | —              | TMR1 gate input.                                      |

|                                                                                                                                          | T3G      | TTL/ST        | _              | TMR3 gate input.                                      |

|                                                                                                                                          | T5G      | TTL/ST        | —              | TMR5 gate input.                                      |

|                                                                                                                                          | SOSCO    | —             | XTAL           | Secondary Oscillator connection.                      |

|                                                                                                                                          | CCP4     | TTL/ST        | CMOS           | Capture/Compare/PWM 4 input.                          |

|                                                                                                                                          | CLKOUT   | —             | CMOS           | FOSC/4 output.                                        |

|                                                                                                                                          | OSC2     | —             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                 |

Legend:AN= Analog input or outputCMOS= CMOS compatible input or outputOD= Open-DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levelsI<sup>2</sup>C= Schmitt Trigger input with I<sup>2</sup>CHV= High VoltageXTAL= Crystal levelsI<sup>2</sup>C= Schmitt Trigger input with I<sup>2</sup>C

**Note 1:** Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-2.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

# 9.0 POWER-SAVING OPERATION MODES

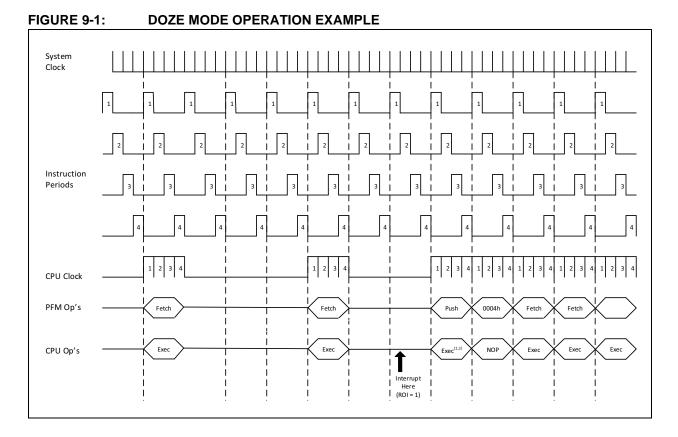

The purpose of the Power-Down modes is to reduce power consumption. There are three Power-Down modes: DOZE mode, IDLE mode, and Sleep mode.

# 9.1 DOZE Mode

Doze mode allows for power savings by reducing CPU operation and program memory access, without affecting peripheral operation. Doze mode differs from Sleep mode because the system oscillators continue to operate, while only the CPU and program memory are affected. The reduced execution saves power by eliminating unnecessary operations within the CPU and memory.

When the Doze Enable (DOZEN) bit is set (DOZEN = 1), the CPU executes only one instruction cycle out of every N cycles as defined by the DOZE<2:0> bits of the CPUDOZE register. For example, if DOZE<2:0> = 100, the instruction cycle ratio is 1:32. The CPU and memory execute for one instruction cycle and then lay idle for 31 instruction cycles. During the unused cycles, the peripherals continue to operate at the system clock speed.

### 9.1.1 DOZE OPERATION

The Doze operation is illustrated in Figure 9-1. For this example:

- Doze enable (DOZEN) bit set (DOZEN = 1)

- DOZE<2:0> = 001 (1:4) ratio

- Recover-on-Interrupt (ROI) bit set (ROI = 1)

As with normal operation, the program memory fetches for the next instruction cycle. The instruction clocks to the peripherals continue throughout.

#### 9.1.2 INTERRUPTS DURING DOZE

If an interrupt occurs and the Recover-on-Interrupt (ROI) bit is clear (ROI = 0) at the time of the interrupt, the Interrupt Service Routine (ISR) continues to execute at the rate selected by DOZE<2:0>. Interrupt latency is extended by the DOZE<2:0> ratio.

If an interrupt occurs and the ROI bit is set (ROI = 1) at the time of the interrupt, the DOZEN bit is cleared and the CPU executes at full speed. The prefetched instruction is executed and then the interrupt vector sequence is executed. In Figure 9-1, the interrupt occurs during the  $2^{nd}$  instruction cycle of the Doze period, and immediately brings the CPU out of Doze. If the Doze-on-Exit (DOE) bit is set (DOE = 1) when the RETFIE operation is executed, DOZEN is set, and the CPU executes at the reduced rate based on the DOZE<2:0> ratio.

© 2015-2016 Microchip Technology Inc.

# PIC16(L)F18325/18345

#### EXAMPLE 11-3: ERASING ONE ROW OF PROGRAM FLASH MEMORY

; This sample row erase routine assumes the following: ; 1.A valid address within the erase row is loaded in variables ADDRH:ADDRL ; 2.ADDRH and ADDRL are located in common RAM (locations 0x70 - 0x7F)

| BANKSEL | NVMADRL          |                                               |

|---------|------------------|-----------------------------------------------|

| MOVF    | ADDRL,W          |                                               |

| MOVWF   | NVMADRL          | ; Load lower 8 bits of erase address boundary |

| MOVF    | ADDRH,W          |                                               |

| MOVWF   | NVMADRH          | ; Load upper 6 bits of erase address boundary |

| BCF     | NVMCON1, NVMREGS | ; Choose Program Flash Memory area            |

| BSF     | NVMCON1, FREE    | ; Specify an erase operation                  |

| BSF     | NVMCON1,WREN     | ; Enable writes                               |

| BCF     | INTCON, GIE      | ; Disable interrupts during unlock sequence   |

| ;       | R                | EQUIRED UNLOCK SEQUENCE:                      |

| NOTATI  | <b>FF1</b>       |                                               |

| MOVLW   | 55h              | ; Load 55h to get ready for unlock sequence   |

| MOVWF   | NVMCON2          | ; First step is to load 55h into NVMCON2      |

| MOVLW   | AAh              | ; Second step is to load AAh into W           |

| MOVWF   | NVMCON2          | ; Third step is to load AAh into NVMCON2      |

| BSF     | NVMCON1,WR       | ; Final step is to set WR bit                 |

| ;       |                  |                                               |

|         |                  |                                               |

| BSF     | INTCON,GIE       | ; Re-enable interrupts, erase is complete     |

| BCF     | NVMCON1,WREN     | ; Disable writes                              |

|         |                  |                                               |

#### TABLE 11-2: NVM ORGANIZATION AND ACCESS INFORMATION

|                    | Master Values                             |                 | NV                          | MREG Acce        | FSR Access            |                |                               |  |  |   |       |  |     |                                         |

|--------------------|-------------------------------------------|-----------------|-----------------------------|------------------|-----------------------|----------------|-------------------------------|--|--|---|-------|--|-----|-----------------------------------------|

| Memory<br>Function | Program<br>Counter (PC),<br>ICSP™ Address | Memory<br>Type  | NVMREGS<br>bit<br>(NVMCON1) | NVMADR<br><14:0> | Allowed<br>Operations | FSR<br>Address | FSR<br>Programming<br>Address |  |  |   |       |  |     |                                         |

| Reset Vector       | 0000h                                     |                 | 0                           | 0000h            |                       | 8000h          |                               |  |  |   |       |  |     |                                         |

| User Memory        | 0001h                                     | Program         | 0                           | 0001h            |                       | 8001h          |                               |  |  |   |       |  |     |                                         |

|                    | 0003h                                     | Flash<br>Memory |                             | 0003h            | READ                  | 8003h          | READ-ONLY                     |  |  |   |       |  |     |                                         |

| INT Vector         | 0004h                                     |                 | 0                           | 0004h            | WRITE                 | 8004h          | READ-ONET                     |  |  |   |       |  |     |                                         |

| User Memory        | 0005h                                     |                 | 0                           | 0005h            |                       | 8005h          |                               |  |  |   |       |  |     |                                         |

|                    | 17FFh                                     |                 |                             | 17FFh            |                       | FFFFh          |                               |  |  |   |       |  |     |                                         |

| User ID            |                                           | Program         | 1                           | 0000h            |                       |                |                               |  |  |   |       |  |     |                                         |

|                    |                                           | Flash<br>Memory |                             | 0003h            | READ                  |                |                               |  |  |   |       |  |     |                                         |

| Reserved           |                                           | _               | —                           | 0004h            | —                     |                |                               |  |  |   |       |  |     |                                         |

| Rev ID             |                                           |                 | 1                           | 0005h            |                       | No Access      |                               |  |  |   |       |  |     |                                         |

| Device ID          | No PC Address                             | Program         | 0                           |                  |                       |                |                               |  |  | 1 | 0006h |  | 140 | /////////////////////////////////////// |

| CONFIG1            |                                           |                 |                             | 1                | 0007h                 |                |                               |  |  |   |       |  |     |                                         |

| CONFIG2            |                                           | Flash<br>Memory | 1                           | 0008h            | READ                  |                |                               |  |  |   |       |  |     |                                         |

| CONFIG3            |                                           | Wernory .       | 1                           | 0009h            |                       |                |                               |  |  |   |       |  |     |                                         |

| CONFIG4            |                                           |                 |                             | 000Ah            |                       |                |                               |  |  |   |       |  |     |                                         |

| User Memory        |                                           | EEPROM          | 1                           | 7000h            | READ                  | 7000h          | READ-ONLY                     |  |  |   |       |  |     |                                         |

|                    |                                           |                 |                             | 70FFh            | WRITE                 | 70FFh          |                               |  |  |   |       |  |     |                                         |

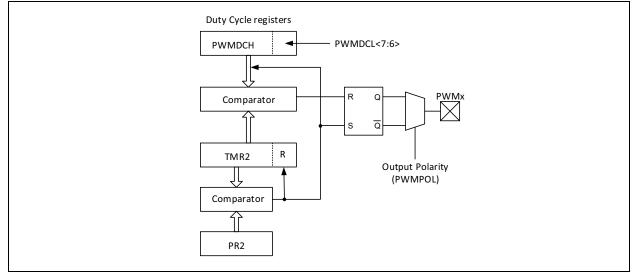

#### FIGURE 19-2: SIMPLIFIED PWM BLOCK DIAGRAM

#### 19.1.1 PWM PERIOD

Referring to Figure 19-1, the PWM output has a period and a pulse width. The frequency of the PWM is the inverse of the period (1/period).

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 19-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)Note: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The PWMx pin is set (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM pulse width is latched from PWMxDC.

| Note: | If the pulse width value is greater than the | he   |  |  |  |  |

|-------|----------------------------------------------|------|--|--|--|--|

|       | period the assigned PWM pin(s) w             | vill |  |  |  |  |

|       | remain unchanged.                            |      |  |  |  |  |

### 19.1.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to the PWMxDC register. The PWMxDCH contains the eight MSbs and bits <7:6> of the PWMxDCL register contain the two LSbs.

The PWMDC register is double-buffered and can be updated at any time. This double buffering is essential for glitch-free PWM operation. New values take effect when TMR2 = PR2. Note that PWMDC is left-justified.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (FOSC), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

Equation 19-2 is used to calculate the PWM pulse width.

Equation 19-3 is used to calculate the PWM duty cycle ratio.

# EQUATION 19-2: PULSE WIDTH

Pulse Width =

$$(PWMxDC) \bullet T_{OSC} \bullet$$

• (TMR2 Prescale Value)

#### EQUATION 19-3: DUTY CYCLE RATIO

Duty Cycle Ratio =  $\frac{(PWMxDC)}{4(PR2+1)}$

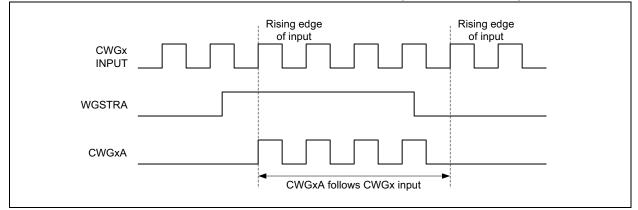

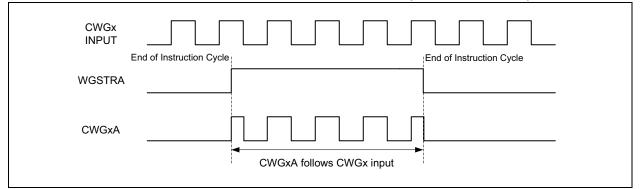

#### 20.2.3.1 Synchronous Steering Mode

In Synchronous Steering mode (MODE<2:0> bits = 001, Register 20-1), changes to steering selection registers take effect on the next rising edge of the modulated data input (Figure 20-3). In Synchronous Steering mode, the output will always produce a complete waveform.

#### 20.2.3.2 Asynchronous Steering Mode

In Asynchronous mode (MODE<2:0> bits = 000, Register 20-1), steering takes effect at the end of the instruction cycle that writes to WGxSTR. In Asynchronous Steering mode, the output signal may be an incomplete waveform (Register 20-4). This operation may be useful when the user firmware needs to immediately remove a signal from the output pin.

#### FIGURE 20-4: EXAMPLE OF ASYNCHRONOUS STEERING (MODE<2:0> = 000)

#### 20.2.3.3 Start-up Considerations

The application hardware must use the proper external pull-up and/or pull-down resistors on the CWG output pins. This is required because all I/O pins are forced to high-impedance at Reset.

The POLy bits (Register 20-2) allow the user to choose whether the output signals are active-high or active-low.

© 2015-2016 Microchip Technology Inc.

# 21.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR3 register will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP bit enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · CLCxIE bit of the PIE3 register

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the PIR3 register, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

### 21.3 Output Mirror Copies

Mirror copies of all LCxCON output bits are contained in the CLCDATA register. Reading this register samples the outputs of all CLCs simultaneously. This prevents any timing skew introduced by testing or reading the LCxOUT bits in the individual CLCxCON registers.

# 21.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

# 21.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 21.6 CLCx Setup Steps

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 21-1).

- · Clear any associated ANSEL bits.

- Set all TRIS bits associated with external CLC inputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxGyPOL bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the PIE3 register.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

# 23.2 Fixed Duty Cycle (FDC) Mode

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled. This provides a 50% duty cycle with a constant frequency, provided that the increment value remains constant. The FDC frequency can be calculated using Equation 23-2. The FDC frequency is half of the overflow frequency since it takes two overflow events to generate one FDC clock period. For more information, see Figure 23-2.

# EQUATION 23-2: FDC FREQUENCY

$F_{fdc} = F_{overflow}/2$

The FDC mode is selected by clearing the N1PFM bit in the NCO1CON register.

# 23.3 Pulse Frequency (PF) Mode

In Pulse Frequency (PF) mode, every time the accumulator overflows (NCO\_overflow), the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output. The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 23-2.

The value of the active and inactive states depends on the polarity bit, N1POL, in the NCO1CON register.

The PF mode is selected by setting the N1PFM bit in the NCO1CON register.

#### 23.3.1 OUTPUT PULSE WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the N1PWS<2:0> bits in the NCO1CLK register.

When the selected pulse width is greater than the accumulator overflow time frame, the output of the NCO1 does not toggle.

# 23.4 Output Polarity Control

The last stage in the NCO1 module is the output polarity. The N1POL bit in the NCO1CON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

The NCO1 output can be used internally by source code or other peripherals. Accomplish this by reading the N1OUT (read-only) bit of the NCO1CON register.

The NCO1 output signal is available to the following peripherals:

• CWG

© 2015-2016 Microchip Technology Inc.

#### **REGISTER 23-4:** NCO1ACCH: NCO1 ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0          | R/W-0/0                           | R/W-0/0            | R/W-0/0 | R/W-0/0                            | R/W-0/0       | R/W-0/0           | R/W-0/0    |  |

|------------------|-----------------------------------|--------------------|---------|------------------------------------|---------------|-------------------|------------|--|

|                  |                                   |                    | NCO1A   | CC<15:8>                           |               |                   |            |  |

| bit 7            |                                   |                    |         |                                    |               |                   | bit 0      |  |

|                  |                                   |                    |         |                                    |               |                   |            |  |

| Legend:          |                                   |                    |         |                                    |               |                   |            |  |

| R = Readable     | R = Readable bit W = Writable bit |                    |         | U = Unimplemented bit, read as '0' |               |                   |            |  |

| u = Bit is unch  | anged                             | x = Bit is unkno   | own     | -n/n = Value at                    | t POR and BOF | R/Value at all ot | her Resets |  |

| '1' = Bit is set |                                   | '0' = Bit is clear | red     |                                    |               |                   |            |  |

bit 7-0 NCO1ACC<15:8>: NCO1 Accumulator, high byte

### REGISTER 23-5: NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|----------------|---------|---------|---------|

| —     | —   | _   | —   | NCO1ACC<19:16> |         |         |         |

| bit 7 |     |     |     |                |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1ACC<19:16>: NCO1 Accumulator, upper byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH:NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real-time, asynchronously to the CPU; there is no provision to guarantee atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

# **REGISTER 23-6:** NCO1INCL<sup>(1,2)</sup>: NCO1 INCREMENT REGISTER – LOW BYTE

| R/W-0/0      | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 |  |  |  |

|--------------|-------------|---------|---------|---------|---------|---------|---------|--|--|--|

| NCO1INC<7:0> |             |         |         |         |         |         |         |  |  |  |

| bit 7        | bit 7 bit 0 |         |         |         |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

#### bit 7-0 NCO1INC<7:0>: NCO1 Increment, low byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

2: NCO1INC is double-buffered as INCBUF; INCBUF is updated on the next falling edge of NCOCLK after writing to NCO1INCL;NCO1INCU and NCO1INCH should be written prior to writing NCO1INCL.

# 30.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM<3:0> bits in the SSPxCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSPx module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPxIF, to be set (SSP interrupt, if enabled):

- Start condition generation

- Stop condition generation

- Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSPx module, when configured in I<sup>2</sup>C Master mode, does not allow queuing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

# 30.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 30.7** "**Baud Rate Generator**" for more detail.

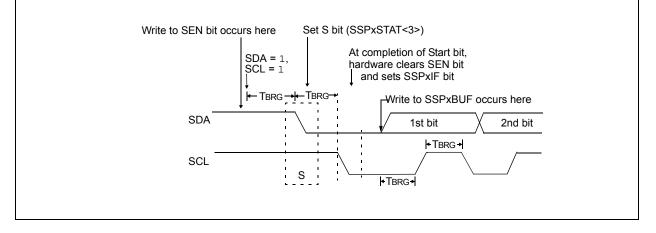

### 30.6.4 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a Start condition (Figure 30-26), the user sets the Start Enable bit, SEN bit of the SSPxCON2 register. If the SDA and SCL pins are sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and starts its count. If SCL and SDA are both sampled high when the Baud Rate Generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the Start condition and causes the S bit of the SSPxSTAT register to be set. Following this, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and resumes its count. When the Baud Rate Generator times out (TBRG), the SEN bit of the SSPxCON2 register will be automatically cleared by hardware; the Baud Rate Generator is suspended, leaving the SDA line held low and the Start condition is complete.

- Note 1: If at the beginning of the Start condition, the SDA and SCL pins are already sampled low, or if during the Start condition, the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag, BCLIF, is set, the Start condition is aborted and the I<sup>2</sup>C module is reset into its idle state.

- **2:** The Philips I<sup>2</sup>C specification states that a bus collision cannot occur on a Start.

# FIGURE 30-26: FIRST START BIT TIMING

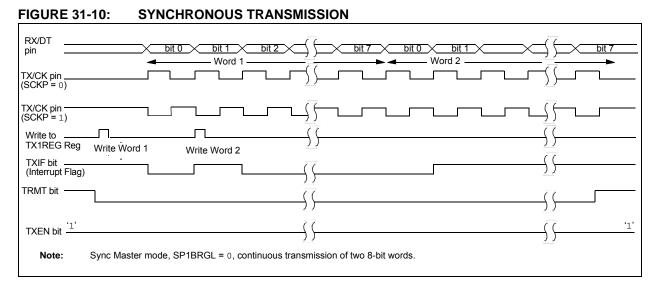

# 31.4.1.5 Synchronous Master Reception

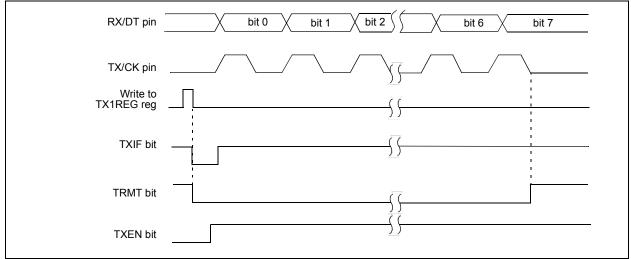

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART1 is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RC1STA register) or the Continuous Receive Enable bit (CREN of the RC1STA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence. To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RC1REG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

© 2015-2016 Microchip Technology Inc.

# 31.6 Register Definitions: EUSART1 Control

| R/W-0/0          | R/W-0/0                                                                  | R/W-0/0                                               | R/W-0/0                                            | R/W-0/0      | R/W-0/0          | R-1/1            | R/W-0/0      |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|--------------|------------------|------------------|--------------|

| CSRC             | TX9                                                                      | TXEN <sup>(1)</sup>                                   | SYNC                                               | SENDB        | BRGH             | TRMT             | TX9D         |

| bit 7            |                                                                          |                                                       |                                                    |              |                  |                  | bit          |

| Legend:          |                                                                          |                                                       |                                                    |              |                  |                  |              |

| R = Readable     | bit                                                                      | W = Writable                                          | bit                                                | U = Unimpler | nented bit, read | as '0'           |              |

| u = Bit is unch  | nanged                                                                   | x = Bit is unki                                       | nown                                               | •            | at POR and BOF   |                  | other Resets |

| '1' = Bit is set | -                                                                        | '0' = Bit is cle                                      | ared                                               |              |                  |                  |              |

| bit 7            | Asynchronou<br>Unused in thi<br>Synchronous<br>1 = Master                | is mode – value                                       | e ignored<br>nerated intern                        |              | )                |                  |              |

| bit 6            | <b>TX9:</b> 9-bit Tra<br>1 = Selects                                     | ansmit Enable I<br>9-bit transmiss<br>8-bit transmiss | oit<br>ion                                         | ,            |                  |                  |              |

| bit 5            | <b>TXEN:</b> Trans<br>1 = Transmit<br>0 = Transmit                       |                                                       | 1)                                                 |              |                  |                  |              |

| bit 4            | SYNC: EUSA<br>1 = Synchro<br>0 = Asynchro                                |                                                       | lect bit                                           |              |                  |                  |              |

| bit 3            | Asynchronou<br>1 = Send SY<br>bit; clear<br>0 = SYNCH<br>Synchronous     | NCH BREAK                                             | on next transr<br>e upon comple<br>iission disable | etion        | bit, followed by | 12 '0' bits, fol | lowed by Sto |

| bit 2            | BRGH: High<br>Asynchronouu<br>1 = High spe<br>0 = Low spe<br>Synchronous | Baud Rate Sel<br><u>is mode</u> :<br>eed<br>ed        | ect bit                                            |              |                  |                  |              |

| bit 1            | <b>TRMT:</b> Trans<br>1 = TSR em<br>0 = TSR full                         | mit Shift Regisi<br>pty                               | ter Status bit                                     |              |                  |                  |              |

| bit 0            | TX9D: Ninth<br>Can be addre                                              | bit of Transmit                                       |                                                    |              |                  |                  |              |

# REGISTER 31-1: TX1STA: TRANSMIT STATUS AND CONTROL REGISTER

Note 1: SREN/CREN overrides TXEN in Sync mode.

| R/W-0/0                                  | R/W-0/0                                                                      | R/W-0/0                                                                | R/W-0/0            | R/W-0/0         | R-0/0                                | R-0/0            | R-x/x      |  |  |  |

|------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------|-----------------|--------------------------------------|------------------|------------|--|--|--|

| SPEN <sup>(1)</sup>                      | RX9                                                                          | SREN                                                                   | CREN               | ADDEN           | FERR                                 | OERR             | RX9D       |  |  |  |

| bit 7                                    | ·                                                                            | ·                                                                      |                    |                 |                                      |                  | bit (      |  |  |  |

| Legend:                                  |                                                                              |                                                                        |                    |                 |                                      |                  |            |  |  |  |

| R = Readable                             | e bit                                                                        | W = Writable                                                           | bit                | U = Unimplei    | mented bit, read                     | 1 as '0'         |            |  |  |  |

| u = Bit is unchanged<br>'1' = Bit is set |                                                                              | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reso |                    |                 |                                      |                  |            |  |  |  |

|                                          |                                                                              | '0' = Bit is cleared                                                   |                    |                 |                                      |                  |            |  |  |  |

| bit 7                                    | SPEN: Seria                                                                  | al Port Enable b                                                       | <sub>oit</sub> (1) |                 |                                      |                  |            |  |  |  |

|                                          | 1 = Serial p<br>0 = Serial p                                                 | ort enabled<br>ort disabled (he                                        | eld in Reset)      |                 |                                      |                  |            |  |  |  |

| bit 6                                    | <b>RX9:</b> 9-bit R                                                          | eceive Enable                                                          | bit                |                 |                                      |                  |            |  |  |  |

|                                          |                                                                              | 9-bit reception<br>8-bit reception                                     |                    |                 |                                      |                  |            |  |  |  |

| bit 5                                    | SREN: Sing                                                                   | le Receive Ena                                                         | ble bit            |                 |                                      |                  |            |  |  |  |

|                                          | Asynchronous mode:                                                           |                                                                        |                    |                 |                                      |                  |            |  |  |  |

|                                          |                                                                              | iis mode – valu<br><u>s mode – Mast</u> e                              | •                  |                 |                                      |                  |            |  |  |  |

|                                          | 1 = Enables single receive                                                   |                                                                        |                    |                 |                                      |                  |            |  |  |  |

|                                          | 0 = Disables single receive                                                  |                                                                        |                    |                 |                                      |                  |            |  |  |  |

|                                          | This bit is cleared after reception is complete.<br>Synchronous mode – Slave |                                                                        |                    |                 |                                      |                  |            |  |  |  |

|                                          |                                                                              | is mode – valu                                                         | -                  |                 |                                      |                  |            |  |  |  |

| bit 4                                    | CREN: Continuous Receive Enable bit                                          |                                                                        |                    |                 |                                      |                  |            |  |  |  |

|                                          | Asynchrono                                                                   | <u>us mode</u> :                                                       |                    |                 |                                      |                  |            |  |  |  |

|                                          |                                                                              | s continuous ree<br>s continuous re<br>s mode:                         |                    | ble bit CREN is | s cleared                            |                  |            |  |  |  |

|                                          | 1 = Enables                                                                  |                                                                        |                    | ble bit CREN is | s cleared (CREI                      | N overrides SR   | EN)        |  |  |  |

| bit 3                                    | ADDEN: Ad                                                                    | dress Detect Ei                                                        | nable bit          |                 |                                      |                  |            |  |  |  |

|                                          | Asynchronous mode 9-bit (RX9 = 1):                                           |                                                                        |                    |                 |                                      |                  |            |  |  |  |

|                                          | the rece                                                                     | eive buffer is se                                                      | t                  | -               | ad of the receiv<br>nd ninth bit can |                  |            |  |  |  |

|                                          |                                                                              | us mode 8-bit (                                                        |                    |                 |                                      |                  | <b>)</b>   |  |  |  |

|                                          | Unused in th                                                                 | iis mode – valu                                                        | e ignored          |                 |                                      |                  |            |  |  |  |

| bit 2                                    | FERR: Fram                                                                   | ning Error bit                                                         |                    |                 |                                      |                  |            |  |  |  |

|                                          | 1 = Framing<br>0 = No fram                                                   |                                                                        | updated by rea     | iding RC1REG    | register and re                      | ceive next valio | d byte)    |  |  |  |

| bit 1                                    | OERR: Over                                                                   | rrun Error bit                                                         |                    |                 |                                      |                  |            |  |  |  |

|                                          | 1 = Overrur<br>0 = No over                                                   | n error (can be o<br>run error                                         | cleared by clea    | ring bit CREN   | )                                    |                  |            |  |  |  |

| bit 0                                    | RX9D: Ninth                                                                  | bit of Received                                                        | d Data             |                 |                                      |                  |            |  |  |  |

|                                          | This can be                                                                  | address/data b                                                         | it or a parity bit | and must be     | calculated by us                     | ser firmware.    |            |  |  |  |

|                                          | e EUSART1 m<br>sociated TRIS                                                 |                                                                        |                    |                 | -state to drive a                    | s needed. Con    | figure the |  |  |  |

# ....

| ABLE 35-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS |                |                        |         |                     |             |       |                |  |  |

|----------------------------------------------------------|----------------|------------------------|---------|---------------------|-------------|-------|----------------|--|--|

| Standard Operating Conditions (unless otherwise stated)  |                |                        |         |                     |             |       |                |  |  |

| Param.<br>No.                                            | Sym.           | Characteristic         | Min.    | Typ.†               | Max.        | Units | Conditions     |  |  |

| ECL Os                                                   | cillator       |                        |         |                     |             |       |                |  |  |

| OS1                                                      | FECL           | Clock Frequency        | —       | —                   | 500         | kHz   |                |  |  |

| OS2                                                      | TECL_DC        | Clock Duty Cycle       | 40      | —                   | 60          | %     |                |  |  |

| ECM Os                                                   | ECM Oscillator |                        |         |                     |             |       |                |  |  |

| OS3                                                      | Fecm           | Clock Frequency        | —       | —                   | 4           | MHz   | Nøte 4         |  |  |

| OS4                                                      | TECM_DC        | Clock Duty Cycle       | 40      | —                   | 60          | %     |                |  |  |

| ECH Os                                                   | cillator       |                        |         |                     |             |       |                |  |  |

| OS5                                                      | Fech           | Clock Frequency        | —       | —                   | 32          | MHz   |                |  |  |

| OS6                                                      | TECH_DC        | Clock Duty Cycle       | 40      | —                   | 60          | %     |                |  |  |

| LP Osci                                                  | llator         |                        |         |                     | ~           |       |                |  |  |

| OS7                                                      | Flp            | Clock Frequency        | —       | —                   | (100        | KHz   | Note 4         |  |  |

| XT Oscillator                                            |                |                        |         |                     |             |       |                |  |  |

| OS8                                                      | Fхт            | Clock Frequency        | —       | ~                   | 4           | MHz   | Note 4         |  |  |

| HS Oscillator                                            |                |                        |         |                     |             |       |                |  |  |

| OS9                                                      | FHS            | Clock Frequency        | - /     |                     | 20          | ∕∕MHz | Note 4         |  |  |

| System Clock                                             |                |                        |         |                     |             |       |                |  |  |

| OS20                                                     | Fosc           | System Clock Frequency |         | $\langle - \rangle$ | 32          | MHz   | Note 2, Note 3 |  |  |

| OS21                                                     | FCY            | Instruction Frequency  | $\sum$  | Fosc/4              | $\rangle -$ | MHz   |                |  |  |

| OS22                                                     | Тсү            | Instruction Period     | 125     | 1/Fey               | —           | ns    |                |  |  |

|                                                          | <b>.</b>       |                        | <u></u> | <u> </u>            |             |       |                |  |  |

#### TABLE 35-7: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS

These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (Tcy) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" no clock) for all devices.

- 2: The system clock frequency (Fosc) is selected by the "main clock switch controls" as described in Section 7.3 "Clock Switching".

- 3: The system clock frequency (Fosc) must meet the voltage requirements defined in the Section 35.2 "Standard Operating Conditions". LP, XT and HS oscillator modes require an appropriate crystal or resonator to be connected to the device.

- 4: For clocking the device with an external square wave, one of the EC mode selections must be used.

#### TABLE 35-10: CLKOUT AND I/O TIMING SPECIFICATIONS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                                                    |   |                      |      |       |                                  |  |

|---------------|---------------------------------------------------------|------------------------------------------------------------------------------------|---|----------------------|------|-------|----------------------------------|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                                                     |   | Тур.†                | Max. | Units | Conditions                       |  |

| 101           | Тськоитн                                                | CLKOUT rising edge delay<br>(rising edge Fosc (Q1 cycle) to<br>falling edge CLKOUT |   | —                    |      | ns    |                                  |  |

| 102           | TCLKOUTL                                                | CLKOUT falling edge delay<br>(rising edge Fosc (Q3 cycle) to<br>rising edge CLKOUT | — | —                    | _    | ns    |                                  |  |

| 103           | TIO_VALID                                               | Port output valid time<br>(rising edge Fosc (Q1 cycle) to<br>port valid)           | _ | —                    | —    | ns    |                                  |  |

| 104           | TIO_SETUP                                               | Port input setup time<br>(Setup time before rising edge<br>Fosc - Q2 cycle)        | _ | _                    |      | ns    |                                  |  |

| 105           | TIO_HOLD                                                | Port input hold time<br>(Hold time after rising edge<br>Fosc - Q2 cycle)           | _ | —                    | _    | ris   |                                  |  |

| IO6           | TIOR_SLREN                                              | Port I/O rise time, slew rate<br>enabled                                           | — | - <                  |      | ns    | VDD = 3.0V, Load conditions      |  |

| 107           | TIOR_SLRDIS                                             | Port I/O rise time, slew rate disabled                                             | _ | $\overline{\langle}$ |      | ns    | $W_{DD}$ = 3.0V, Load conditions |  |

| IO8           | TIOF_SLREN                                              | Port I/O fall time, slew rate<br>enabled                                           |   | _                    | X    | ns    | VDD = 3.0V, Load conditions      |  |

| IO9           | TIOF_SLRDIS                                             | Port I/O fall time, slew rate disabled                                             |   |                      |      | ns    | VDD = 3.0V, Load conditions      |  |

| IO10          | Τιντ                                                    | INT pin high or low time to trigger<br>an interrupt                                | A | $\sum$               | _    | ns    |                                  |  |

| IO11          | Tioc                                                    | Interrupt-on-Change minimum<br>high or low time to trigger interrupt               |   |                      |      | ns    |                                  |  |

\*

These parameters are characterized but not tested. Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. t

# PIC16(L)F18325/18345

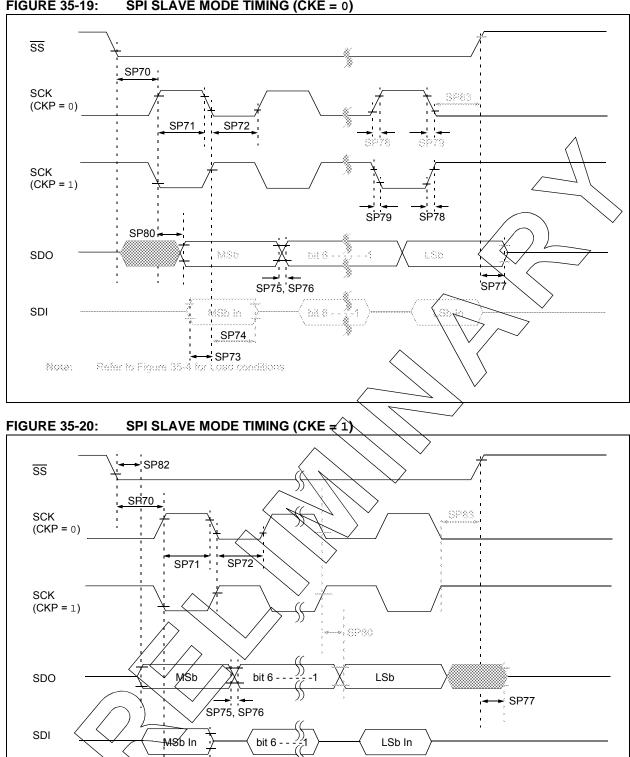

#### FIGURE 35-19: SPI SLAVE MODE TIMING (CKE = 0)

lota

SP74 Refer to Figure 35-4 for Load conditions.

# 37.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- MPLAB Xpress IDE Software

- Microchip Code Configurator (MCC)

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

### 37.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

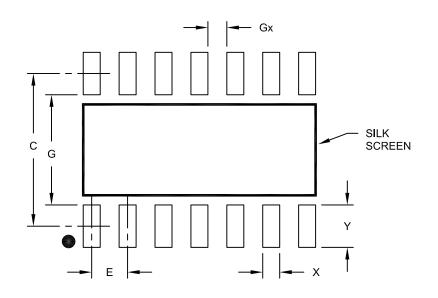

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                       | Units            |      |      | MILLIMETERS |  |  |  |

|-----------------------|------------------|------|------|-------------|--|--|--|

| Dimensio              | Dimension Limits |      | NOM  | MAX         |  |  |  |

| Contact Pitch         | 1.27 BSC         |      |      |             |  |  |  |

| Contact Pad Spacing   | С                |      | 5.40 |             |  |  |  |

| Contact Pad Width     | X                |      |      | 0.60        |  |  |  |

| Contact Pad Length    | Y                |      |      | 1.50        |  |  |  |

| Distance Between Pads | Gx               | 0.67 |      |             |  |  |  |

| Distance Between Pads | G                | 3.90 |      |             |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

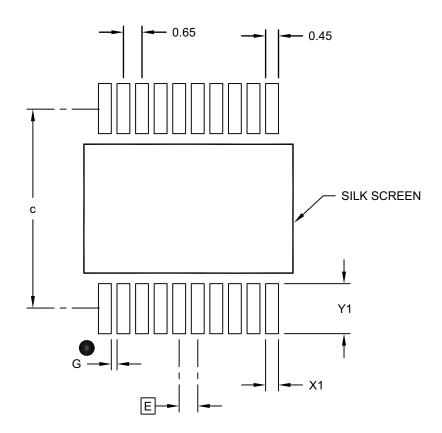

# 20-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | MILLIMETERS      |      |          |      |

|--------------------------|------------------|------|----------|------|

| Dimension                | Dimension Limits |      | NOM      | MAX  |

| Contact Pitch            |                  |      | 0.65 BSC |      |

| Contact Pad Spacing      | С                |      | 7.20     |      |

| Contact Pad Width (X20)  | X1               |      |          | 0.45 |

| Contact Pad Length (X20) | Y1               |      |          | 1.75 |

| Distance Between Pads    | G                | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2072B