Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

ĿXFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18325-e-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|------------|----------------------------------------------------------|

| Address | Name       | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7 | Bit 6 | Bit 5       | Bit 4         | Bit 3             | Bit 2         | Bit 1  | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------|----------------------------------|-------|-------|-------------|---------------|-------------------|---------------|--------|-----------|-----------------------|---------------------------------|

| Bank 28 | В          |                                  |       |       |             |               |                   |               |        |           |                       |                                 |

|         |            |                                  |       |       | CPU CORE RE | EGISTERS; see | Table 4-2 for spe | ecifics       |        |           |                       |                                 |

| E0Ch    | _          |                                  |       |       |             | Unimple       | mented            |               |        |           | _                     | _                               |

| E0Dh    | _          | _                                |       |       |             | Unimple       |                   |               |        |           | _                     |                                 |

| E0Eh    |            |                                  |       |       |             | Unimple       |                   |               |        |           | _                     |                                 |

| E0Fh    | PPSLOCK    |                                  | _     | _     | _           | _             | _                 | _             | _      | PPSLOCKED | 0                     |                                 |

| E10h    | INTPPS     |                                  | _     | _     | _           |               |                   | INTPPS<4:0>   |        |           | 0 0010                | u uuu                           |

| E11h    | TOCKIPPS   |                                  | _     | _     | _           |               |                   | T0CKIPPS<4:0> |        |           | 0 0010                | u uuu                           |

| E12h    | T1CKIPPS   |                                  | _     | —     | _           |               |                   |               | 0 0101 | u uuu     |                       |                                 |

| E13h    | T1GPPS     |                                  | _     | —     | _           |               |                   |               | 0 0100 | u uuu     |                       |                                 |

| E14h    | CCP1PPS    |                                  | _     | _     | _           |               | CCP1PPS<4:0>      |               |        |           |                       | u uuu                           |

| E15h    | CCP2PPS    |                                  | _     | _     | _           |               | CCP2PPS<4:0>      |               |        |           |                       | u uuu                           |

| E16h    | CCP3PPS    |                                  | _     | _     | _           | CCP3PPS<4:0>  |                   |               |        |           | 0 0010                | u uuu                           |

| E17h    | CCP4PPS    | X —                              | _     | _     | _           |               | CCP4PPS<4:0>      |               |        |           |                       | u uuu                           |

|         |            | — X                              | _     | _     | _           |               |                   | CCP4PPS<4:0>  |        |           | 0 0100                | u uuu                           |

| E18h    | CWG1PPS    |                                  | —     | _     | _           |               |                   | CWG1PPS<4:0>  |        |           | 0 0010                | u uuuu                          |

| E19h    | CWG2PPS    |                                  | —     | —     |             |               |                   | CWG2PPS<4:0>  |        |           | 0 0010                | u uuui                          |

| E1Ah    | MDCIN1PPS  |                                  | _     | _     |             |               | N                 | IDCIN1PPS<4:0 | >      |           | 1 0010                | u uuu                           |

| E1Bh    | MDCIN2PPS  |                                  | _     | _     |             |               | N                 | IDCIN2PPS<4:0 | >      |           | 1 0101                | u uuu                           |

| E1Ch    | MDMINPPS   |                                  | _     | —     | _           |               | 1                 | MDMINPPS<4:0> |        |           | 1 0011                | u uuuu                          |

| E1Dh    | SSP2CLKPPS | X —                              | _     | —     | -           |               | S                 | SP2CLKPPS<4:0 | )>     |           | 1 0100                | u uuu                           |

|         |            | — X                              | _     | _     | _           |               | S                 | SP2CLKPPS<4:0 | )>     |           | 0 1111                | u uuu                           |

| E1Eh    | SSP2DATPPS | Х —                              | _     | —     | _           |               | -                 | SP2DATPPS<4:0 |        |           | 1 0101                | u uuuu                          |

|         |            | — X                              | _     | _     | _           |               |                   | SP2DATPPS<4:0 |        |           | 0 1101                | u uuuu                          |

| E1Fh    | SSP2SSPPS  | Х —                              | _     | _     | _           |               |                   | SP2SSPPS<4:0  |        |           | 0 0000                | u uuuu                          |

|         |            | — X                              | —     | —     | —           |               |                   | SP2SSPPS<4:0  |        |           | 0 0001                | u uuuu                          |

| E20h    | SSP1CLKPPS | X —                              | —     | _     | _           |               |                   | SP1CLKPPS<4:0 |        |           | 1 0000                | u uuuu                          |

|         |            | — X                              | —     | —     | _           |               | S                 | SP1CLKPPS<4:0 | )>     |           | 0 1110                | u uuu                           |

e on ther sets PIC16(L)F18325/18345

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Only on PIC16F18325/18345.

2: Register accessible from both User and ICD Debugger.

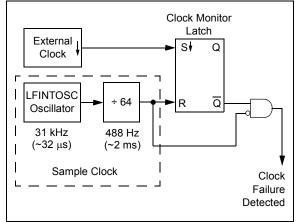

# 7.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, ECL, ECM, ECH, and Secondary Oscillator).

# 7.4.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 7-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

# 7.4.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to the HFINTOSC at 1 MHz clock frequency and sets the bit flag OSFIF of the PIR3 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE3 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC<2:0> and NDIV<3:0>bits of the OSCCON1 register.

# 7.4.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC<2:0> and NDIV<3:0> bits of the OSCCON1 register. When switching to the external oscillator or external oscillator with PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSFIF flag will again be set by hardware.

| R/W-0/0          | R/W-0/0                                                                                                                                                                              | U-0                                                                                                                                                                     | R/W-0/0        | R/W-0/0                                           | R/W-0/0          | U-0              | U-0          |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------|------------------|------------------|--------------|--|--|--|

| EXTOEN           | HFOEN                                                                                                                                                                                | _                                                                                                                                                                       | LFOEN          | SOSCEN                                            | ADOEN            | _                | _            |  |  |  |

| bit 7            |                                                                                                                                                                                      |                                                                                                                                                                         |                |                                                   |                  |                  | bit 0        |  |  |  |

|                  |                                                                                                                                                                                      |                                                                                                                                                                         |                |                                                   |                  |                  |              |  |  |  |

| Legend:          |                                                                                                                                                                                      |                                                                                                                                                                         |                |                                                   |                  |                  |              |  |  |  |

| R = Readable     | bit                                                                                                                                                                                  | W = Writable                                                                                                                                                            | bit            | U = Unimplen                                      | nented bit, read | d as '0'         |              |  |  |  |

| u = Bit is unch  | anged                                                                                                                                                                                | x = Bit is unkr                                                                                                                                                         | nown           | -n/n = Value a                                    | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                      | '0' = Bit is clea                                                                                                                                                       | ared           |                                                   |                  |                  |              |  |  |  |

| bit 7            | <b>EXTOEN:</b> External Oscillator Manual Request Enable bit<br>1 = EXTOSC is explicitly enabled, operating as specified by FEXTOSC<br>0 = EXTOSC could be enabled by another module |                                                                                                                                                                         |                |                                                   |                  |                  |              |  |  |  |

| bit 6            | 1 = HFINTOS                                                                                                                                                                          |                                                                                                                                                                         | enabled, opera | quest Enable b<br>ating as specifie<br>aer module |                  | (Register 7-6)   |              |  |  |  |

| bit 5            | Unimplemen                                                                                                                                                                           | ted: Read as '                                                                                                                                                          | 0'             |                                                   |                  |                  |              |  |  |  |

| bit 4            | 1 = LFINTOS                                                                                                                                                                          | ITOSC (31 kHz<br>C is explicitly e<br>C could be ena                                                                                                                    | nabled         | anual Request<br>er module                        | Enable bit       |                  |              |  |  |  |

| bit 3            | 1 = Secondar                                                                                                                                                                         | SOSCEN: Secondary Oscillator Manual Request Enable bit<br>1 = Secondary Oscillator is explicitly enabled<br>0 = Secondary Oscillator could be enabled by another module |                |                                                   |                  |                  |              |  |  |  |

| bit 2            | 1 = ADOSC is                                                                                                                                                                         | ADOEN: ADOSC (600 kHz) Oscillator Manual Request Enable bit<br>1 = ADOSC is explicitly enabled<br>0 = ADOSC could be enabled by another module                          |                |                                                   |                  |                  |              |  |  |  |

| bit 1            | Unimplemen                                                                                                                                                                           | ted: Read as '                                                                                                                                                          | 0'             |                                                   |                  |                  |              |  |  |  |

| bit 0            | Unimplemen                                                                                                                                                                           |                                                                                                                                                                         |                |                                                   |                  |                  |              |  |  |  |

# REGISTER 7-5: OSCEN: OSCILLATOR MANUAL ENABLE REGISTER

# 12.0 I/O PORTS

TABLE 12-1: PORT AVAILABILITY PER DEVICE

| DEMO           | _     | -     | _     |

|----------------|-------|-------|-------|

| Device         | PORTA | PORTB | РОКТС |

| PIC16(L)F18325 | ٠     |       | •     |

| PIC16(L)F18345 | ٠     | •     | ٠     |

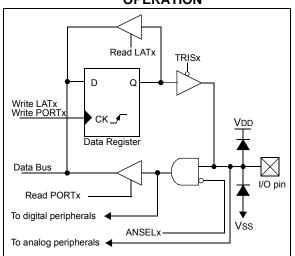

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- · ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- · SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

### FIGURE 12-1: GENERIC I/O PORT OPERATION

# 12.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 13.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

| TABLE 13-1.           |       |       |       |       |       |          |        |       | ,                   |

|-----------------------|-------|-------|-------|-------|-------|----------|--------|-------|---------------------|

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1  | Bit 0 | Register<br>on page |

| RXPPS                 | —     | _     |       |       |       | RXPPS<   | 4:0>   |       | 162                 |

| CLCIN0PPS             |       |       |       |       | (     | CLCIN0PP | S<4:0> |       | 162                 |

| CLCIN1PPS             | —     | —     | _     |       | (     | CLCIN1PP | S<4:0> |       | 162                 |

| CLCIN2PPS             | —     | _     |       |       | (     | CLCIN2PP | S<4:0> |       | 162                 |

| CLCIN3PPS             | —     | _     | —     |       | (     | CLCIN3PP | S<4:0> |       | 162                 |

| RA0PPS                | —     | —     | _     |       |       | RA0PPS<  | :4:0>  |       | 163                 |

| RA1PPS                | —     | —     | _     |       |       | RA1PPS<  | :4:0>  |       | 163                 |

| RA2PPS                | —     | —     | _     |       |       | RA2PPS<  | :4:0>  |       | 163                 |

| RA4PPS                |       |       |       |       |       | RA4PPS<  | :4:0>  |       | 163                 |

| RA5PPS                |       |       |       |       |       | RA5PPS<  | :4:0>  |       | 163                 |

| RB4PPS <sup>(1)</sup> |       |       |       |       |       | RB4PPS<  | :4:0>  |       | 163                 |

| RB5PPS <sup>(1)</sup> |       |       |       |       |       | RB5PPS<  | :4:0>  |       | 163                 |

| RB6PPS <sup>(1)</sup> | —     | —     | _     |       |       | RB6PPS<  | :4:0>  |       | 163                 |

| RB7PPS <sup>(1)</sup> | —     | —     | _     |       |       | RB7PPS<  | :4:0>  |       | 163                 |

| RC0PPS                | —     | —     | _     |       |       | RC0PPS<  | :4:0>  |       | 163                 |

| RC1PPS                | —     | —     | _     |       |       | RC1PPS<  | :4:0>  |       | 163                 |

| RC2PPS                | —     | —     | _     |       |       | RC2PPS<  | :4:0>  |       | 163                 |

| RC3PPS                | —     | —     | _     |       |       | RC3PPS<  | :4:0>  |       | 163                 |

| RC4PPS                | —     | —     | —     |       |       | RC4PPS<  | :4:0>  |       | 163                 |

| RC5PPS                | —     | —     | —     |       |       | RC5PPS<  | :4:0>  |       | 163                 |

| RC6PPS <sup>(1)</sup> | —     |       |       |       |       | RC6PPS<  | :4:0>  |       | 163                 |

| RC7PPS <sup>(1)</sup> | —     |       |       |       |       | RC7PPS<  | :4:0>  |       | 163                 |

### SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE (CONTINUED) **TABLE 13-1:**

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

Note 1: PIC16(L)F18345 only.

| OVRD<br>bit 7     | OVRC                                                                                  | OVRB                                            | OVRA          | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | OTD (2)             |  |  |  |

|-------------------|---------------------------------------------------------------------------------------|-------------------------------------------------|---------------|---------------------|---------------------|---------------------|---------------------|--|--|--|

| hit 7             |                                                                                       |                                                 |               |                     | 00                  | 0110.7              | STRA <sup>(2)</sup> |  |  |  |

|                   |                                                                                       |                                                 |               |                     |                     |                     | bit 0               |  |  |  |

| Legend:           |                                                                                       |                                                 |               |                     |                     |                     |                     |  |  |  |

| R = Readable bi   | t                                                                                     | W = Writable I                                  | bit           | U = Unimpler        | nented bit, read    | as '0'              |                     |  |  |  |

| u = Bit is unchar | nged                                                                                  | x = Bit is unkn                                 | own           | -n/n = Value a      | at POR and BO       | R/Value at all o    | ther Resets         |  |  |  |

| '1' = Bit is set  |                                                                                       | '0' = Bit is clea                               | ared          | q = Value dep       | pends on condit     | ion                 |                     |  |  |  |

|                   |                                                                                       |                                                 |               |                     |                     |                     |                     |  |  |  |

| bit 7             | OVRD: Steeri                                                                          | ng Data D bit                                   |               |                     |                     |                     |                     |  |  |  |

| bit 6             | OVRC: Steeri                                                                          | ng Data C bit                                   |               |                     |                     |                     |                     |  |  |  |

| pit 5 🛛           | OVRB: Steeri                                                                          | ng Data B bit                                   |               |                     |                     |                     |                     |  |  |  |

| pit 4 🛛           | OVRA: Steeri                                                                          | ng Data A bit                                   |               |                     |                     |                     |                     |  |  |  |

| oit 3             | STRD: Steering Enable bit D <sup>(2)</sup>                                            |                                                 |               |                     |                     |                     |                     |  |  |  |

| -                 | 1 = CWGxD c                                                                           | output has the Q                                | CWGx data inp | out waveform w      | ith polarity conf   | rol from POLD       | bit                 |  |  |  |

|                   |                                                                                       | = CWGxD output is assigned to value of OVRD bit |               |                     |                     |                     |                     |  |  |  |

| bit 2             | STRC: Steerin                                                                         | ng Enable bit C                                 | (2)           |                     |                     |                     |                     |  |  |  |

| 1                 | 1 = CWGxC output has the CWGx data input waveform with polarity control from POLC bit |                                                 |               |                     |                     |                     |                     |  |  |  |

|                   |                                                                                       | output is assign                                |               | OVRC bit            |                     |                     |                     |  |  |  |

|                   |                                                                                       | ng Enable bit B                                 |               |                     |                     |                     |                     |  |  |  |

|                   | 1 = CWGxB output has the CWGx data input waveform with polarity control from POLB bit |                                                 |               |                     |                     |                     |                     |  |  |  |

|                   |                                                                                       | utput is assign                                 |               | OVRB bit            |                     |                     |                     |  |  |  |

|                   |                                                                                       | ng Enable bit A                                 |               |                     |                     |                     |                     |  |  |  |

|                   |                                                                                       |                                                 | •             |                     | vith polarity cont  | rol from POLA       | bit                 |  |  |  |

|                   |                                                                                       | output is assign                                |               |                     |                     |                     |                     |  |  |  |

|                   | •                                                                                     | ister apply only                                |               |                     | egister 20-1, st    | eering modes).      |                     |  |  |  |

# **REGISTER 20-5:** CWGxSTR<sup>(1)</sup>: CWG STEERING CONTROL REGISTER

**2:** This bit is double-buffered when MODE < 2:0 > = 0.01.

| R/W/HS/SC-0/0     | R/W-0/0                                                        | R/W-0/0                                                                 | R/W-1/1                                                    | R/W-0/0                                                                                                             | R/W-1/1                                                             | U-0            | U-0         |

|-------------------|----------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------|-------------|

| SHUTDOWN          | REN                                                            | LSBD                                                                    | )<1:0>                                                     | LSAC                                                                                                                | <1:0>                                                               | —              | —           |

| bit 7             |                                                                |                                                                         |                                                            |                                                                                                                     |                                                                     |                | bit 0       |

|                   |                                                                |                                                                         |                                                            |                                                                                                                     |                                                                     |                |             |

| Legend:           |                                                                |                                                                         |                                                            |                                                                                                                     |                                                                     |                |             |

| R = Readable bit  | t                                                              | W = Writable                                                            | bit                                                        | U = Unimplem                                                                                                        | ented bit, read                                                     | as '0'         |             |

| u = Bit is unchan | ged                                                            | x = Bit is unkr                                                         | nown                                                       | -n/n = Value at                                                                                                     | POR and BOR                                                         | Value at all o | ther Resets |

| '1' = Bit is set  |                                                                | '0' = Bit is clea                                                       | ared                                                       | q = Value depe                                                                                                      | ends on condition                                                   | on             |             |

| bit 7             | 1 = An auto                                                    | : Auto-Shutdov<br>-shutdown stat<br>-shutdown eve                       | e is in effect                                             |                                                                                                                     |                                                                     |                |             |

| bit 6             | 1 = Auto-re                                                    | estart Enable b<br>start is enabled<br>start is disabled                |                                                            |                                                                                                                     |                                                                     |                |             |

| bit 5-4           | 11 = A logic<br>10 = A logic<br>01 = Pin is tr<br>00 = The ina | 1' is placed on<br>0' is placed on<br>i-stated on CW<br>active state of | CWGxB/D wl<br>CWGxB/D wl<br>GxB/D when a<br>the pin, inclu | Shutdown State (<br>hen an auto-shut<br>hen an auto-shut<br>an auto-shutdow<br>ding polarity, is<br>utdown event oc | down event occ<br>down event occ<br>n event occurs.<br>placed on CW | curs.          | he required |

| bit 3-2           | 11 = A logic<br>10 = A logic<br>01 = Pin is tr<br>00 = The ina | 1' is placed on<br>0' is placed on<br>i-stated on CW<br>ictive state of | CWGxA/C wl<br>CWGxA/C wl<br>G1A/C when a<br>the pin, inclu | Shutdown State (<br>hen an auto-shut<br>hen an auto-shut<br>an auto-shutdow<br>ding polarity, is<br>utdown event oc | down event occ<br>down event occ<br>n event occurs.<br>placed on CW | curs.          | he required |

| bit 1-0           | Unimplemer                                                     | ted: Read as '                                                          | 0'                                                         |                                                                                                                     |                                                                     |                |             |

|                   | •                                                              |                                                                         |                                                            | 0-1), to place the                                                                                                  | •                                                                   |                | •           |

# REGISTER 20-6: CWGxAS0: CWG AUTO-SHUTDOWN CONTROL REGISTER 0

2: The outputs will remain in auto-shutdown state until the next rising edge of the CWG data input after this bit is cleared.

© 2015-2016 Microchip Technology Inc.

DS40001795C-page 225

# 23.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCO1 Interrupt Flag bit, NCO1IF, of the PIR2 register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- N1EN bit of the NCO1CON register

- NCO1IE bit of the PIE2 register

- · PEIE bit of the INTCON register

- · GIE bit of the INTCON register

The interrupt must be cleared by software by clearing the NCO1IF bit in the Interrupt Service Routine.

# 23.6 Effects of a Reset

All of the NCO1 registers are cleared to zero as the result of a Reset.

# 23.7 Operation in Sleep

The NCO1 module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO1 module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO1 clock source, when the NCO1 is enabled, the CPU will go idle during Sleep, but the NCO1 will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

# 27.2.1 TIMER1 (SECONDARY) OSCILLATOR

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is designed to be used in conjunction with an external 32.768 kHz crystal. The oscillator circuit is enabled by setting the T1SOSC bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1SOSC should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

# 27.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 27.4 Timer1 Operation in Asynchronous Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 27.4.1 "Reading and Writing Timer1 in Asynchronous Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

# 27.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 27.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

# 27.5.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 27-3 for timing details.

| TABLE 27-3: | TIMER1 GATE ENABLE |

|-------------|--------------------|

|             | SELECTIONS         |

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| 1          | 0      | 1   | Holds Count      |

| 1          | 1      | 0   | Holds Count      |

| 1          | 1      | 1   | Counts           |

# 28.5 Register Definitions: Timer2/4/6 Control

| REGISTER       |                        |                                                                              |                    |                |                   |                            |         |  |  |

|----------------|------------------------|------------------------------------------------------------------------------|--------------------|----------------|-------------------|----------------------------|---------|--|--|

| U-0            | R/W-0/0                |                                                                              | R/W-0/0<br>PS<3:0> | R/W-0/0        | R/W-0/0<br>TMRxON | R/W-0/0                    | R/W-0/0 |  |  |

|                |                        | TXOUT                                                                        | -2<3:0>            |                | TWIRXON           | TXCKP                      | S<1:0>  |  |  |

| bit 7          |                        |                                                                              |                    |                |                   |                            | bit     |  |  |

| Legend:        |                        |                                                                              |                    |                |                   |                            |         |  |  |

| R = Readal     | ble bit                | W = Writable                                                                 | bit                | U = Unimpler   | mented bit, read  | l as '0'                   |         |  |  |

| u = Bit is ur  | nchanged               | x = Bit is unkr                                                              | nown               | -n/n = Value a | at POR and BO     | OR/Value at all other Rese |         |  |  |

| '1' = Bit is s | set                    | '0' = Bit is clea                                                            | ared               |                |                   |                            |         |  |  |

| bit 7          | Unimplem               | ented: Read as '                                                             | ٥'                 |                |                   |                            |         |  |  |

| bit 6-3        | •                      |                                                                              |                    | er Select hits |                   |                            |         |  |  |

|                |                        | TxOUTPS<3:0>: Timerx Output Postscaler Select bits<br>1111 = 1:16 Postscaler |                    |                |                   |                            |         |  |  |

|                |                        | 1111 – 1.16 Postscaler                                                       |                    |                |                   |                            |         |  |  |

|                |                        | 4 Postscaler                                                                 |                    |                |                   |                            |         |  |  |

|                | 1100 <b>= 1</b> :1     | 1100 = 1:13 Postscaler                                                       |                    |                |                   |                            |         |  |  |

|                | 1011 <b>= 1</b> :1     | 1011 = 1:12 Postscaler                                                       |                    |                |                   |                            |         |  |  |

|                | 1010 <b>= 1</b> :1     | 1010 = 1:11 Postscaler                                                       |                    |                |                   |                            |         |  |  |

|                | 1001 <b>= 1</b> :1     | 0 Postscaler                                                                 |                    |                |                   |                            |         |  |  |

|                | 1000 <b>= 1</b> :9     | Postscaler                                                                   |                    |                |                   |                            |         |  |  |

|                |                        | :8 Postscaler                                                                |                    |                |                   |                            |         |  |  |

|                |                        | 0110 = 1:7 Postscaler                                                        |                    |                |                   |                            |         |  |  |

|                |                        | 0101 = 1:6 Postscaler<br>0100 = 1:5 Postscaler                               |                    |                |                   |                            |         |  |  |

|                |                        |                                                                              |                    |                |                   |                            |         |  |  |

|                |                        | Postscaler<br>Postscaler                                                     |                    |                |                   |                            |         |  |  |

|                |                        | Postscaler                                                                   |                    |                |                   |                            |         |  |  |

|                |                        | Postscaler                                                                   |                    |                |                   |                            |         |  |  |

| bit 2          |                        | Timer2 On bit                                                                |                    |                |                   |                            |         |  |  |

|                | 1 = Timer<br>0 = Timer |                                                                              |                    |                |                   |                            |         |  |  |

| bit 1-0        |                        | 1:0>: Timerx Cloc                                                            | k Prescale Se      | elect bits     |                   |                            |         |  |  |

|                | 11 <b>= Pres</b> o     | aler is 64                                                                   |                    |                |                   |                            |         |  |  |

|                | 10 = Preso             | aler is 16                                                                   |                    |                |                   |                            |         |  |  |

|                | 01 = Preso             | aler is 4                                                                    |                    |                |                   |                            |         |  |  |

|                | 00 <b>= Presc</b>      | aler is 1                                                                    |                    |                |                   |                            |         |  |  |

| Note 1:        | 'x' refers to eith     | er '2.' 4' or '6' for                                                        | the respective     | Timer2/4/6 rec | listers           |                            |         |  |  |

# **REGISTER 28-1:** TxCON<sup>(1)</sup>: TIMERX CONTROL REGISTER

**Note 1:** 'x' refers to either '2,' 4' or '6' for the respective Timer2/4/6 registers.

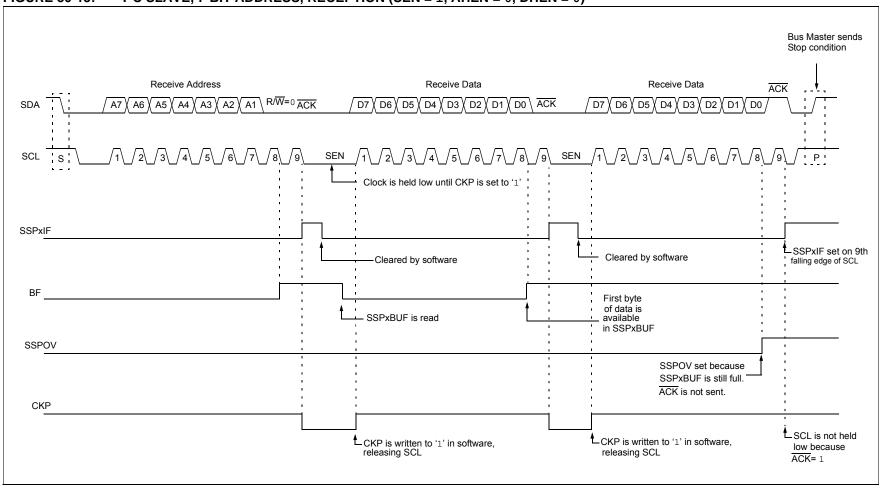

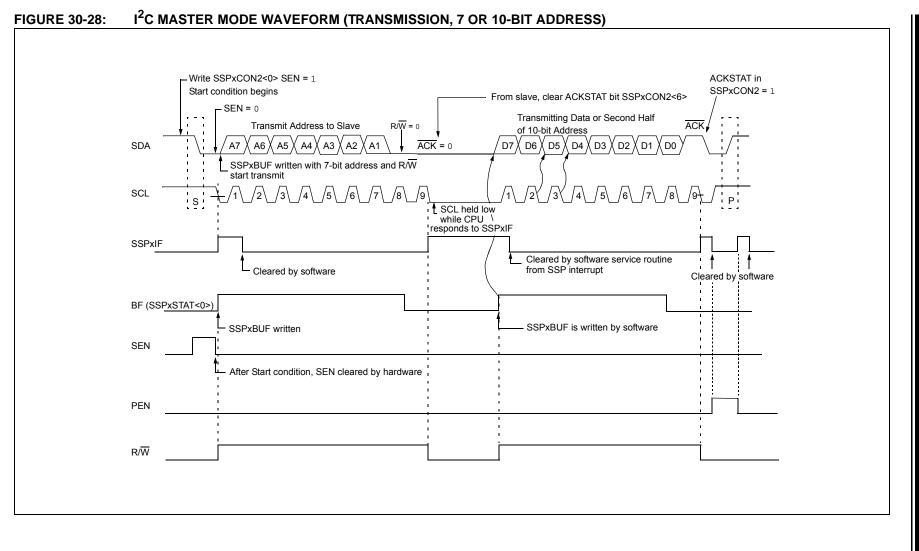

# FIGURE 30-15: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 0, DHEN = 0)

© 2015-2016 Microchip Technology Inc

Preliminary

PIC16(L)F18325/18345

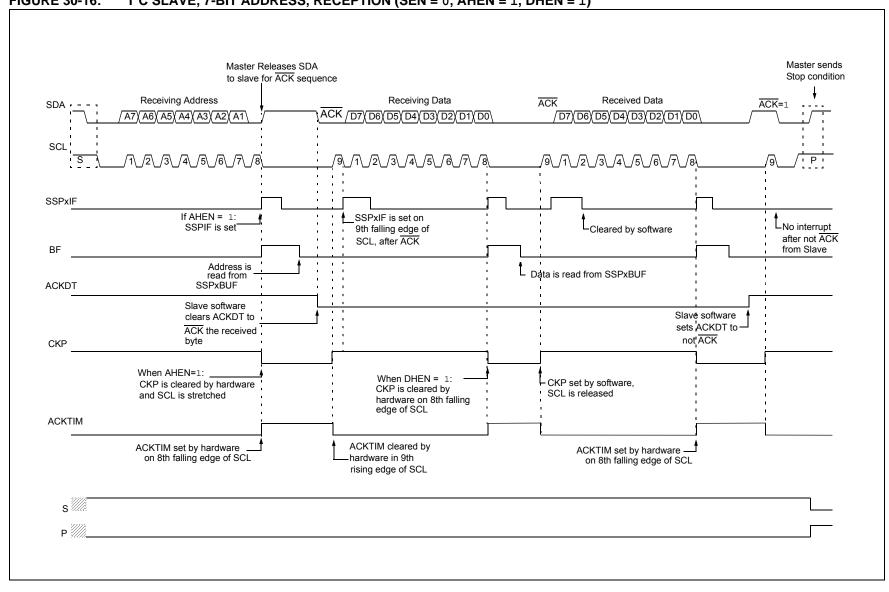

# FIGURE 30-16: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 1, DHEN = 1)

PIC16(L)F18325/18345

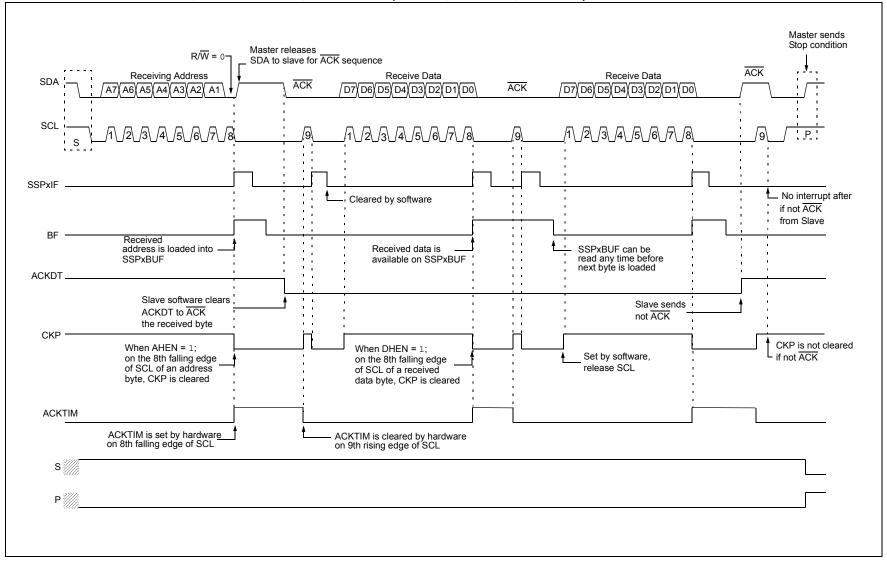

# FIGURE 30-17: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 1, DHEN = 1)

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<6:3>) → PC<14:11>                                                                                                                                                                             |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return address<br>(PC + 1) is pushed onto the stack.<br>The 11-bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a 2-cycle<br>instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                           |

| Operands:        | None                                                                                                                                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow \underline{WDT} \text{ prescaler,} \\ 1 \rightarrow \underline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$    |

| Status Affected: | TO, PD                                                                                                                                                                   |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$<br>are set. |

| CALLW Subroutine Call With W |                                                                                                                                                                                                                       |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                      | [ label ] CALLW                                                                                                                                                                                                       |  |  |  |

| Operands:                    | None                                                                                                                                                                                                                  |  |  |  |

| Operation:                   | (PC) +1 $\rightarrow$ TOS,<br>(W) $\rightarrow$ PC<7:0>,<br>(PCLATH<6:0>) $\rightarrow$ PC<14:8>                                                                                                                      |  |  |  |

| Status Affected:             | None                                                                                                                                                                                                                  |  |  |  |

| Description:                 | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |  |  |  |

| COMF             | Complement f                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

| CLRF             | Clear f                                                               |  |  |

|------------------|-----------------------------------------------------------------------|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |

| Status Affected: | Z                                                                     |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0', the<br>result is stored in the W register. If 'd'<br>is '1', the result is stored back in<br>register 'f'. |

# CLRWClear WSyntax:[ label ] CLRWOperands:NoneOperation: $00h \rightarrow (W)$ <br/> $1 \rightarrow Z$ Status Affected:ZDescription:W register is cleared. Zero bit (Z) is<br/>set.

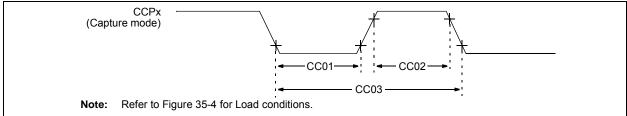

### FIGURE 35-13: **CAPTURE/COMPARE/PWM TIMINGS (CCP)**

# TABLE 35-18: CAPTURE/COMPARE/PWM CHARACTERISTICS (CCP)

| Daram | Sym. | ating Conditions (unless otherwise sta<br>Characteristic |                | Min.                  | Тур.†     | Max.       | Units | Conditions         |

|-------|------|----------------------------------------------------------|----------------|-----------------------|-----------|------------|-------|--------------------|

| CC01* | TccL | CCPx Input Low Time                                      | No Prescaler   | 0.5Tcy +<br>20        | —         | —          | ns    |                    |

|       |      |                                                          | With Prescaler | 20                    | —         | —          | ns    |                    |

| CC02* | ТссН | CCPx Input High<br>Time                                  | No Prescaler   | 0.5Tcy +<br>20        | —         | <i>, ,</i> | æ//   |                    |

|       |      |                                                          | With Prescaler | 20                    | —         | _/         | ns    | $\sim$             |

| CC03* | TccP | CCPx Input Period                                        |                | <u>3Tcy + 40</u><br>N | $\langle$ | _ `        | ns    | N = prescale value |

These parameters are characterized but not tested.

t Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Example

# 38.0 PACKAGING INFORMATION

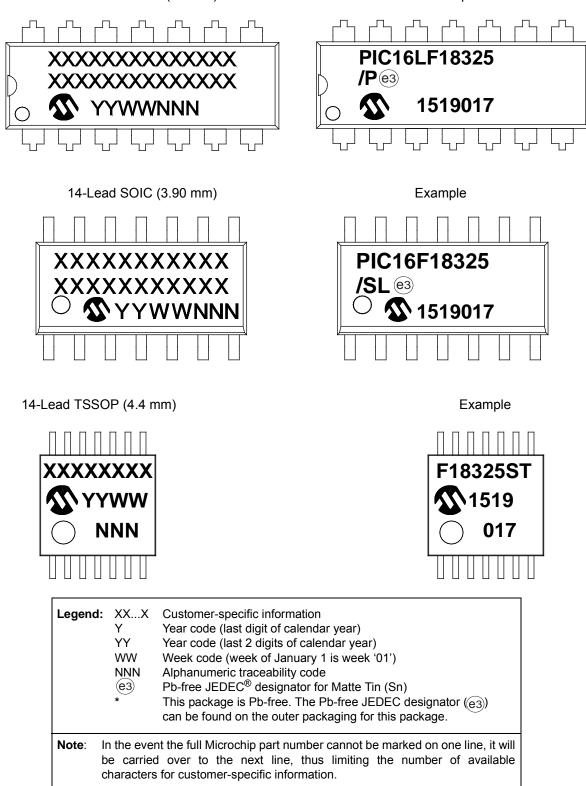

38.1 Package Marking Information

14-Lead PDIP (300 mil)

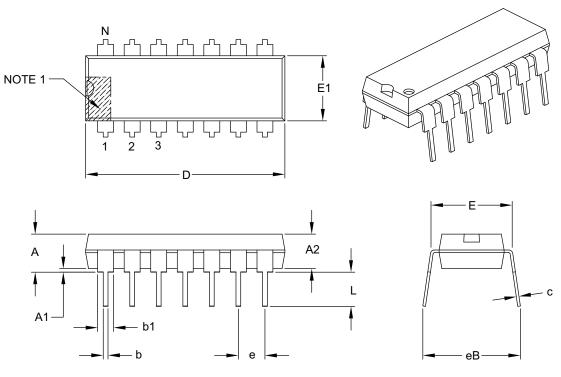

# 38.2 Package Details

The following sections give the technical details of the packages.

# 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |      |          | INCHES |  |  |  |

|----------------------------|------------------|------|----------|--------|--|--|--|

| Dimension                  | Dimension Limits |      | NOM      | MAX    |  |  |  |

| Number of Pins             | N                |      | 14       |        |  |  |  |

| Pitch                      | е                |      | .100 BSC | _      |  |  |  |

| Top to Seating Plane       | Α                | -    | -        | .210   |  |  |  |

| Molded Package Thickness   | A2               | .115 | .130     | .195   |  |  |  |

| Base to Seating Plane      | A1               | .015 | -        | -      |  |  |  |

| Shoulder to Shoulder Width | E                | .290 | .310     | .325   |  |  |  |

| Molded Package Width       | E1               | .240 | .250     | .280   |  |  |  |

| Overall Length             | D                | .735 | .750     | .775   |  |  |  |

| Tip to Seating Plane       | L                | .115 | .130     | .150   |  |  |  |

| Lead Thickness             | С                | .008 | .010     | .015   |  |  |  |

| Upper Lead Width           | b1               | .045 | .060     | .070   |  |  |  |

| Lower Lead Width           | b                | .014 | .018     | .022   |  |  |  |

| Overall Row Spacing §      | eB               | -    | -        | .430   |  |  |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

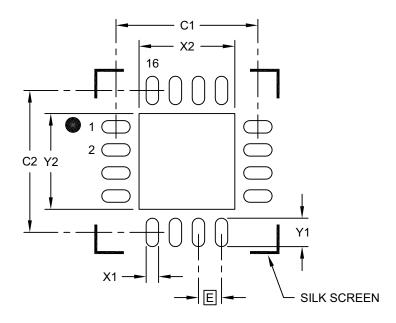

# 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                            | MILLIMETERS      |          |      |       |

|----------------------------|------------------|----------|------|-------|

| Units                      |                  | MIN      |      | MAX   |

| Dimensio                   | Dimension Limits |          | _    | IVIAA |

| Contact Pitch              | E                | 0.65 BSC |      |       |

| Optional Center Pad Width  | X2               |          |      | 2.70  |

| Optional Center Pad Length | Y2               |          |      | 2.70  |

| Contact Pad Spacing        | C1               |          | 4.00 |       |

| Contact Pad Spacing        | C2               |          | 4.00 |       |

| Contact Pad Width (X16)    | X1               |          |      | 0.35  |

| Contact Pad Length (X16)   | Y1               |          |      | 0.80  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A