# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

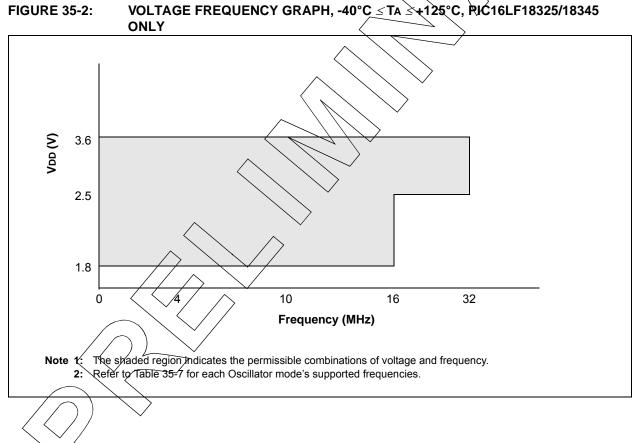

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18345-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 8.5 "Automatic Context Saving"** for more information.

#### 3.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON0 register, and if enabled, will cause a software Reset. See **Section 4.4 "Stack**" for more details.

## 3.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers, program memory, and data EEPROM, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. See **Section 4.5** "Indirect Addressing" for more details.

## 3.4 Instruction Set

There are 48 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 34.0** "Instruction Set Summary" for more details.

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 ( | (CONTINUED) | ) |

|------------|------------------------------------------------|-------------|---|

|            |                                                |             |   |

| Address | s Name | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7   | Bit 6   | Bit 5       | Bit 4           | Bit 3             | Bit 2   | Bit 1   | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------------------|---------|---------|-------------|-----------------|-------------------|---------|---------|---------|-----------------------|---------------------------------|

| Bank 7  | 1      |                                  | •       |         |             | •               | •                 | -       | •       | •       | ·                     |                                 |

|         |        |                                  |         |         | CPU CORE RI | EGISTERS; see 1 | Table 4-2 for spe | ecifics |         |         |                       |                                 |

| 38Ch    | INLVLA |                                  |         | _       | INLVLA5     | INLVLA4         | INLVLA3           | INLVLA2 | INLVLA1 | INLVLA0 | 11 1111               | 11 111                          |

| 38Dh    | INLVLB | X —                              |         |         |             | Unimple         | mented            |         |         |         | _                     | —                               |

|         |        | — X                              | INLVLB7 | INLVLB6 | INLVLB5     | INLVLB4         | _                 | _       | _       | _       | 1111                  | 1111                            |

| 38Eh    | INLVLC | X —                              | —       | —       | INLVLC5     | INLVLC4         | INLVLC3           | INLVLC2 | INLVLC1 | INLVLC0 | 11 1111               | 11 1111                         |

|         |        | — X                              | INLVLC7 | INLVLC6 | INLVLC5     | INLVLC4         | INLVLC3           | INLVLC2 | INLVLC1 | INLVLC0 | 1111 1111             | 1111 1111                       |

| 38Fh    | —      | —                                |         |         |             | Unimple         | mented            |         |         |         | -                     | —                               |

| 390h    | —      | —                                |         |         |             | Unimple         | mented            |         |         |         | _                     | —                               |

| 391h    | IOCAP  |                                  | —       | _       | IOCAP5      | IOCAP4          | IOCAP3            | IOCAP2  | IOCAP1  | IOCAP0  | 00 0000               | 00 0000                         |

| 392h    | IOCAN  |                                  | _       | —       | IOCAN5      | IOCAN4          | IOCAN3            | IOCAN2  | IOCAN1  | IOCAN0  | 00 0000               | 00 0000                         |

| 393h    | IOCAF  |                                  | —       | —       | IOCAF5      | IOCAF4          | IOCAF3            | IOCAF2  | IOCAF1  | IOCAF0  | 00 0000               | 00 0000                         |

| 394h    | IOCBP  | X —                              |         |         |             | Unimple         | mented            |         |         |         | _                     | —                               |

|         |        | — X                              | IOCBP7  | IOCBP6  | IOCBP5      | IOCBP4          | —                 | —       | _       | —       | 0000                  | 0000                            |

| 395h    | IOCBN  | X —                              |         |         |             | Unimple         | mented            |         |         |         | _                     | _                               |

|         |        | — X                              | IOCBN7  | IOCBN6  | IOCBN5      | IOCBN4          | _                 | —       | _       | —       | 0000                  | 0000                            |

| 396h    | IOCBF  | X —                              |         |         |             | Unimple         | mented            |         |         |         | —                     | _                               |

|         |        | — X                              | IOCBF7  | IOCBF6  | IOCBF5      | IOCBF4          | _                 | —       | _       | —       | 0000                  | 0000                            |

| 397h    | IOCCP  | X —                              | —       | —       | IOCCP5      | IOCCP4          | IOCCP3            | IOCCP2  | IOCCP1  | IOCCP0  | 00 0000               | 00 0000                         |

|         |        | — X                              | IOCCP7  | IOCCP6  | IOCCP5      | IOCCP4          | IOCCP3            | IOCCP2  | IOCCP1  | IOCCP0  | 0000 0000             | 0000 0000                       |

| 398h    | IOCCN  | X —                              | —       | _       | IOCCN5      | IOCCN4          | IOCCN3            | IOCCN2  | IOCCN1  | IOCCN0  | 00 0000               | 00 0000                         |

|         |        | — X                              | IOCCN7  | IOCCN6  | IOCCN5      | IOCCN4          | IOCCN3            | IOCCN2  | IOCCN1  | IOCCN0  | 0000 0000             | 0000 0000                       |

| 399h    | IOCCF  | X —                              | —       | _       | IOCCF5      | IOCCF4          | IOCCF3            | IOCCF2  | IOCCF1  | IOCCF0  | 00 0000               | 00 0000                         |

|         |        | — X                              | IOCCF7  | IOCCF6  | IOCCF5      | IOCCF4          | IOCCF3            | IOCCF2  | IOCCF1  | IOCCF0  | 0000 0000             | 0000 0000                       |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Only on PIC16F18325/18345. Legend:

Note 1:

Register accessible from both User and ICD Debugger. 2:

## TABLE 4-4: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

MDCLPOL

| Address | Name                                            | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7  | Bit 6   | Bit 5    | Bit 4   | Bit 3  | Bit 2                | Bit 1        | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------------------|----------------------------------|--------|---------|----------|---------|--------|----------------------|--------------|---------|-----------------------|---------------------------------|

| Bank 7  |                                                 |                                  |        |         |          |         |        |                      |              |         |                       |                                 |

|         | CPU CORE REGISTERS; see Table 4-2 for specifics |                                  |        |         |          |         |        |                      |              |         |                       |                                 |

| 39Ah    | CLKRCON                                         |                                  | CLKREN | —       | —        | CLKRD   | C<1:0> |                      | CLKRDIV<2:0> | 01 0000 | 01 0001               |                                 |

| 39Bh    | —                                               | —                                |        |         |          | Unimple | mented |                      |              |         | -                     | _                               |

| 39Ch    | MDCON                                           |                                  | MDEN   | _       | _        | MDOPOL  | MDOUT  | DUT — MDBIT 00 00 0- |              |         |                       |                                 |

| 39Dh    | MDSRC                                           |                                  | _      | _       | _        | _       |        | MDMS<3:0> xxxx 0     |              |         |                       |                                 |

| 39Eh    | MDCARH                                          |                                  |        | MDCHPOL | MDCHSYNC | _       |        | MDCH                 | 1<3:0>       |         | -xx- xxxx             | -uu- uuuu                       |

MDCL<3:0>

-xx- xxxx

-uu- uuuu

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

MDCLSYNC

Note 1: Only on PIC16F18325/18345.

MDCARL

2: Register accessible from both User and ICD Debugger.

39Fh

| TABLE   | 4-4: SPEC  | IAL F                            | <b>UNCTION RE</b> | GISTER S      | UMMARY B      | ANKS 0-31 (   | CONTINUE          | <b>)</b> |           |         |                       |                                 |

|---------|------------|----------------------------------|-------------------|---------------|---------------|---------------|-------------------|----------|-----------|---------|-----------------------|---------------------------------|

| Address | Name       | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7             | Bit 6         | Bit 5         | Bit 4         | Bit 3             | Bit 2    | Bit 1     | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

| Bank 1  | 3          |                                  |                   |               |               |               |                   |          |           |         |                       |                                 |

|         |            |                                  |                   |               | CPU CORE RE   | EGISTERS; see | Table 4-2 for spe | cifics   |           |         |                       |                                 |

| 68Ch    | _          | _                                |                   | Unimplemented |               |               |                   |          |           | —       | -                     |                                 |

| 68Dh    | —          | —                                |                   |               | Unimplemented |               |                   |          |           | _       | -                     |                                 |

| 68Eh    | —          | —                                |                   |               |               | Unimple       | mented            |          |           |         | -                     | _                               |

| 68Fh    | —          | —                                |                   |               |               | Unimple       | mented            |          |           |         | -                     | —                               |

| 690h    |            | _                                |                   |               |               | Unimple       | mented            |          |           |         | _                     | _                               |

| 691h    | CWG1CLKCON |                                  | _                 | _             | —             | _             | _                 | —        | —         | CS      | 0                     | 0                               |

| 692h    | CWG1DAT    |                                  | —                 | —             | —             | _             |                   | DAT      | <3:0>     |         | 0000                  | 0000                            |

| 693h    | CWG1DBR    |                                  | _                 | —             |               |               | DBR               | <5:0>    |           |         | 00 0000               | 00 0000                         |

| 694h    | CWG1DBF    |                                  | _                 | _             | DBF<5:0>      |               |                   |          |           | 00 0000 | 00 0000               |                                 |

| 695h    | CWG1CON0   |                                  | EN                | LD            | —             | _             | —                 |          | MODE<2:0> |         | 00000                 | 00000                           |

| 696h    | CWG1CON1   |                                  |                   | —             | IN            | _             | POLD              | POLC     | POLB      | POLA    | x- 0000               | x- 0000                         |

| 697h    | CWG1AS0    |                                  | SHUTDOWN          | REN           | LSBE          | 0<1:0>        | LSAC              | <1:0>    | —         | —       | 0001 01               | 0001 01                         |

AS4E

OVRA

Unimplemented

AS2E

STRC

AS3E

STRD

AS1E

STRB

AS0E

STRA

---0 0000

0000 0000 0000 0000

---0 0000

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

\_

OVRB

Only on PIC16F18325/18345. Note 1:

CWG1AS1

CWG1STR

Register accessible from both User and ICD Debugger. 2:

\_

\_

OVRD

\_

OVRC

698h

699h

69Fh

69Ah to

| Address | Name   | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7 | Bit 6 | Bit 5       | Bit 4         | Bit 3             | Bit 2       | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|----------------------------------|-------|-------|-------------|---------------|-------------------|-------------|-------|-------|-----------------------|---------------------------------|

| Bank 2  | 9      |                                  |       |       |             |               |                   |             |       |       |                       |                                 |

|         |        |                                  |       |       | CPU CORE RI | EGISTERS; see | Table 4-2 for spe | ecifics     |       |       |                       |                                 |

| E8Dh    | _      | _                                |       |       |             | Unimple       | mented            |             |       |       | _                     | _                               |

| E8Eh    | _      | _                                |       |       |             | Unimple       |                   |             |       |       | _                     | _                               |

| E8Fh    | —      |                                  |       |       |             | Unimple       |                   |             |       |       | _                     | _                               |

| E90h    | RA0PPS |                                  |       | _     | _           |               |                   | RA0PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E91h    | RA1PPS |                                  | _     | _     | _           |               |                   | RA1PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E92h    | RA2PPS |                                  | _     | _     | _           |               | RA2PPS<4:0>       |             |       |       |                       |                                 |

| E93h    | —      | —                                |       |       |             | Unimple       | Unimplemented     |             |       |       |                       |                                 |

| E94h    | RA4PPS |                                  | —     | —     | —           |               | RA4PPS<4:0>       |             |       |       |                       |                                 |

| E95h    | RA5PPS |                                  | —     | —     |             |               |                   | RA5PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E96h    | —      | —                                |       |       |             | Unimple       | emented           |             |       |       | —                     | —                               |

| E97h    | —      | —                                |       |       |             | Unimple       | mented            |             |       |       | -                     | _                               |

| E98h    | —      | _                                |       |       |             | Unimple       | mented            |             |       |       |                       | —                               |

| E99h    | —      |                                  |       |       |             | Unimple       | mented            |             |       |       | -                     | —                               |

| E9Ah    | —      | —                                |       |       |             | Unimple       | mented            |             |       |       | -                     | —                               |

| E9Bh    | —      | _                                |       |       |             | Unimple       |                   |             |       |       | —                     | —                               |

| E9Ch    | RB4PPS | X —                              |       | 1     |             | Unimple       | mented            |             |       |       | -                     | —                               |

|         |        | — ×                              | —     | —     | —           |               |                   | RB4PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E9Dh    | RB5PPS | × —                              |       |       |             | Unimple       | mented            |             |       |       | -                     | -                               |

|         |        | — ×                              |       | —     | —           |               |                   | RB5PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E9Eh    | RB6PPS | × —                              |       |       |             | Unimple       | mented            |             |       |       | -                     | —                               |

|         |        | — X                              |       | —     | —           |               |                   | RB6PPS<4:0> |       |       | 0 0000                | u uuuu                          |

| E9Fh    | RB7PPS | X —                              |       |       |             | Unimple       | mented            |             |       |       | -                     | —                               |

|         |        | — X                              | —     | —     | _           |               |                   | RB7PPS<4:0> |       |       | 0 0000                | u uuuu                          |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Only on PIC16F18325/18345.

2: Register accessible from both User and ICD Debugger.

| Address | Name | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7         | Bit 6 | Bit 5       | Bit 4           | Bit 3            | Bit 2  | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------|----------------------------------|---------------|-------|-------------|-----------------|------------------|--------|-------|-------|-----------------------|---------------------------------|

| Bank 30 |      |                                  |               |       |             |                 |                  |        |       |       |                       |                                 |

|         |      |                                  |               |       | CPU CORE RE | EGISTERS; see 1 | able 4-2 for spe | cifics |       |       |                       |                                 |

| F0Ch -  | _    | _                                | Unimplemented |       |             |                 |                  |        |       |       |                       |                                 |

| F0Ch | —        | - |          |          |                                                          | Unimple                                                                                                                                                                                                                           | mented   |          |              |           |           | _         |

|------|----------|---|----------|----------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------------|-----------|-----------|-----------|

| F0Dh | —        | - |          |          |                                                          | Unimple                                                                                                                                                                                                                           | mented   |          |              |           | —         | _         |

| F0Eh | —        | - |          |          |                                                          | Unimple                                                                                                                                                                                                                           | mented   |          |              |           | —         | _         |

| F0Fh | CLCDATA  |   | _        | —        | _                                                        | _                                                                                                                                                                                                                                 | MLC4OUT  | MLC3OUT  | MLC2OUT      | MLC1OUT   | 0000      | 0000      |

| F10h | CLC1CON  |   | LC1EN    | —        | LC10UT                                                   | LC1INTP                                                                                                                                                                                                                           | LC1INTN  |          | LC1MODE<2:0> | >         | 0-00 0000 | 0-00 0000 |

| F11h | CLC1POL  |   | LC1POL   | —        | —                                                        | —                                                                                                                                                                                                                                 | LC1G4POL | LC1G3POL | LC1G2POL     | LC1G1POL  | 0 xxxx    | 0 uuuu    |

| F12h | CLC1SEL0 |   | —        | —        |                                                          | LC1D1S<5:0>            LC1D2S<5:0>            LC1D3S<5:0>            LC1D4S<5:0>                                                                                                                                                  |          |          |              |           |           | uu uuuu   |

| F13h | CLC1SEL1 |   | _        | —        |                                                          | LC1D2S<5:0> -<br>LC1D3S<5:0> -<br>LC1D4S<5:0> -                                                                                                                                                                                   |          |          |              |           |           | uu uuuu   |

| F14h | CLC1SEL2 |   | —        | —        |                                                          | LC1D3S<5:0><br>LC1D4S<5:0>                                                                                                                                                                                                        |          |          |              |           |           | uu uuuu   |

| F15h | CLC1SEL3 |   | —        | —        |                                                          | LC1D4S<5:0>                                                                                                                                                                                                                       |          |          |              |           |           | uu uuuu   |

| F16h | CLC1GLS0 |   | LC1G1D4T | LC1G1D4N | LC1G1D3T LC1G1D3N LC1G1D2T LC1G1D2N LC1G1D1T LC1G1D1N xx |                                                                                                                                                                                                                                   |          |          |              |           | xxxx xxxx | uuuu uuuu |

| F17h | CLC1GLS1 |   | LC1G2D4T | LC1G2D4N |                                                          |                                                                                                                                                                                                                                   |          |          |              | xxxx xxxx | uuuu uuuu |           |

| F18h | CLC1GLS2 |   | LC1G3D4T | LC1G3D4N |                                                          |                                                                                                                                                                                                                                   |          |          |              | xxxx xxxx | uuuu uuuu |           |

| F19h | CLC1GLS3 |   | LC1G4D4T | LC1G4D4N | LC1G4D3T                                                 | LC1G4D3N                                                                                                                                                                                                                          | LC1G4D2T | LC1G4D2N | LC1G4D1T     | LC1G4D1N  | xxxx xxxx | uuuu uuuu |

| F1Ah | CLC2CON  |   | LC2EN    | —        | LC2OUT                                                   | LC2INTP                                                                                                                                                                                                                           | LC2INTN  |          | LC2MODE<2:0> | >         | 0-00 0000 | 0-00 0000 |

| F1Bh | CLC2POL  |   | LC2POL   | —        | _                                                        | _                                                                                                                                                                                                                                 | LC2G4POL | LC2G3POL | LC2G2POL     | LC2G1POL  | 0 xxxx    | 0 uuuu    |

| F1Ch | CLC2SEL0 |   | —        | —        | LC2D1S<5:0>                                              |                                                                                                                                                                                                                                   |          |          |              |           | xx xxxx   | uu uuuu   |

| F1Dh | CLC2SEL1 |   | —        | _        | LC2D2S<5:0>                                              |                                                                                                                                                                                                                                   |          |          |              |           | xx xxxx   | uu uuuu   |

| F1Eh | CLC2SEL2 |   | —        | —        |                                                          |                                                                                                                                                                                                                                   | LC2D3    | S<5:0>   |              |           | xx xxxx   | uu uuuu   |

| F1Fh | CLC2SEL3 |   | —        | _        |                                                          | IG2D3TLC1G2D3NLC1G2D2TLC1G2D2NLC1G2D1TLC1G2D1NIG3D3TLC1G3D3NLC1G3D2TLC1G3D2NLC1G3D1TLC1G3D1NIG4D3TLC1G4D3NLC1G4D2TLC1G4D2NLC1G4D1TLC1G4D1NIG4D3TLC2INTPLC2INTNLC2MODE<2:0>LC2G4POLLC2G3POLLC2G2POLLC2G1POLLC2D1S<5:0>LC2LC2LC2LC2 |          |          |              |           |           | uu uuuu   |

x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Only on PIC16F18325/18345. Legend:

Note 1:

2: Register accessible from both User and ICD Debugger.

## 5.2 Register Definitions: Configuration Words

## REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

|                   |                                 |                                  |                   | OOILEATON      |                    |                    |               |

|-------------------|---------------------------------|----------------------------------|-------------------|----------------|--------------------|--------------------|---------------|

|                   |                                 | R/P-1                            | U-1               | R/P-1          | U-1                | U-1                | R/P-1         |

|                   |                                 | FCMEN                            | —                 | CSWEN          | —                  | —                  | CLKOUTEN      |

|                   |                                 | bit 13                           |                   |                |                    | •                  | bit 8         |

|                   |                                 |                                  |                   |                |                    |                    |               |

| U-1               | R/P-1                           | R/P-1                            | R/P-1             | U-1            | R/P-1              | R/P-1              | R/P-1         |

|                   | RSTOSC2                         | RSTOSC1                          | RSTOSC0           |                | FEXTOSC2           | FEXTOSC1           | FEXTOSC0      |

| bit 7             |                                 |                                  |                   |                |                    |                    | bit 0         |

|                   |                                 |                                  |                   |                |                    |                    |               |

| Legend:           |                                 |                                  |                   |                |                    |                    |               |

| R = Readable      | e bit                           | P = Program                      | mable bit         | U = Unimpler   | nented bit, read   | 1 as '1'           |               |

| '0' = Bit is clea | ared                            | '1' = Bit is set                 |                   | n = Value wh   | en blank           |                    |               |

|                   |                                 |                                  |                   |                |                    |                    |               |

| bit 13            | FCMEN: Fail-                    | Safe Clock Mo                    | nitor Enable b    | oit            |                    |                    |               |

|                   |                                 | SCM timer ena                    |                   |                |                    |                    |               |

|                   |                                 | SCM timer disa                   |                   |                |                    |                    |               |

| bit 12            | -                               | ted: Read as '                   |                   |                |                    |                    |               |

| bit 11            |                                 | ck Switch Enat<br>riting to NOSC |                   | allowed        |                    |                    |               |

|                   |                                 | •                                |                   |                | d by user softwa   | are                |               |

| bit 10-9          |                                 | ted: Read as '                   |                   | <b>J</b>       | ,                  |                    |               |

| bit 8             |                                 | Clock Out Ena                    |                   |                |                    |                    |               |

|                   | If FEXTOSC =                    | = EC, HS, HT (                   | or LP, then this  |                |                    |                    |               |

|                   |                                 |                                  |                   |                | r function on OS   |                    |               |

|                   |                                 |                                  |                   | -OSC/4 clock a | ppears at OSC      | 2                  |               |

| bit 7             | -                               | ted: Read as '                   |                   |                |                    |                    |               |

| bit 6-4           |                                 | >: Power-up E                    |                   |                | ects the oscillato | or first used by a | isor software |

|                   | 111 = EXT1                      |                                  |                   | r FEXTOSC<2    |                    | n mst used by t    | user soltware |

|                   | 110 = HFIN'                     |                                  | SC (1 MHz)        |                |                    |                    |               |

|                   | 101 = <b>Rese</b>               |                                  |                   |                |                    |                    |               |

|                   | 100 = LFIN                      |                                  |                   |                |                    |                    |               |

|                   | 011 = SOSC<br>010 = <b>Rese</b> |                                  | 2.768 kHz)        |                |                    |                    |               |

|                   | 001 = EXT4                      |                                  | with 4x PLL;      | EXTOSC oper    | ating per FEXT     | OSC<2:0> bits      |               |

|                   | 000 = HFIN                      | T32 HFINTO                       | SC (32 MHz)       | -              |                    |                    |               |

| bit 3             | Unimplement                     | ted: Read as '                   | 1'                |                |                    |                    |               |

| bit 2-0           |                                 | 0>: FEXTOSC                      |                   |                | election bits      |                    |               |

|                   |                                 | EC (External C                   | ,                 |                |                    |                    |               |

|                   |                                 | EC (External C<br>EC (External C |                   |                |                    |                    |               |

|                   |                                 | Oscillator not                   |                   |                |                    |                    |               |

|                   | 011 = Unim                      |                                  |                   |                |                    |                    |               |

|                   |                                 | HS (Crystal os                   |                   |                |                    |                    |               |

|                   |                                 | HT (Crystal os                   | ,                 |                |                    |                    |               |

|                   | 000 = LP                        | LP (Crystal os                   | ciliator) optimiz | 20101 32.768   | ĸnz                |                    |               |

| R/W-0/0                                                                                                         | R/W-0/0                          | R/W-0/0                                                     | R/W-0/0    | R/W-0/0     | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------|------------|-------------|------------------|------------------|--------------|--|--|--|

| CWG2IE                                                                                                          | CWG1IE                           | TMR5GIE                                                     | TMR5IE     | CCP4IE      | CCP3IE           | CCP2IE           | CCP1IE       |  |  |  |

| bit 7                                                                                                           |                                  |                                                             |            |             | •                |                  | bit          |  |  |  |

|                                                                                                                 |                                  |                                                             |            |             |                  |                  |              |  |  |  |

| Legend:                                                                                                         |                                  |                                                             | ,          |             |                  |                  |              |  |  |  |

| R = Readable                                                                                                    |                                  | W = Writable                                                |            | -           | mented bit, read |                  |              |  |  |  |

| u = Bit is unch                                                                                                 | anged                            | x = Bit is unkr                                             |            |             | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set                                                                                                |                                  | '0' = Bit is clea                                           | ared       | HS = Hardwa | are set          |                  |              |  |  |  |

| bit 7                                                                                                           | 1 = CWG2 in                      | VG 2 Interrupt E<br>Iterrupt enabled                        |            |             |                  |                  |              |  |  |  |

| bit 6 <b>CWG1IE:</b> CWG 1 Interrupt Enable bit<br>1 = CWG1 interrupt enabled<br>0 = CWG1 interrupt not enabled |                                  |                                                             |            |             |                  |                  |              |  |  |  |

| bit 5                                                                                                           | 1 = TMR5 Ga                      | imer5 Gate Inte<br>ate interrupt is e<br>ate interrupt is r | nabled     | oit         |                  |                  |              |  |  |  |

| bit 4                                                                                                           | 1 = TMR5 ov                      | R5 Overflow Int<br>erflow interrupt<br>erflow interrupt     | is enabled |             |                  |                  |              |  |  |  |

| bit 3                                                                                                           | 1 = CCP4 int                     | P4 Interrupt En<br>errupt is enable<br>errupt is not en     | d          |             |                  |                  |              |  |  |  |

| bit 2                                                                                                           | 1 = CCP3 int                     | P3 Interrupt En<br>errupt is enable<br>errupt is not en     | d          |             |                  |                  |              |  |  |  |

| bit 1                                                                                                           | 1 = CCP2 ii                      | P2 Interrupt En<br>nterrupt is enab<br>nterrupt is not e    | led        |             |                  |                  |              |  |  |  |

| bit 0                                                                                                           | <b>CCP1IE:</b> CC<br>1 = CCP1 ii | P1 Interrupt En                                             |            |             |                  |                  |              |  |  |  |

## REGISTER 8-6: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### 9.2 IDLE Mode

When the IDLE Enable (IDLEN) bit is clear (IDLEN = 0), the SLEEP instruction will put the device into full Sleep mode (see **Section 9.3 "Sleep Mode"**). When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into IDLE mode. In IDLE mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to DOZE mode, except that in IDLE both the CPU and program memory are shut off.

| Note: | Peripherals using Fosc will continue      |

|-------|-------------------------------------------|

|       | running while in IDLE (but not in Sleep). |

|       | Peripherals using HFINTOSC,               |

|       | LFINTOSC, or SOSC will continue           |

|       | operation in both IDLE and SLEEP.         |

| Note: | If CLKOUT is enabled (CLKOUT = 0,      |

|-------|----------------------------------------|

|       | Configuration Word 1), the output will |

|       | continue operating while in IDLE.      |

#### 9.2.1 IDLE AND INTERRUPTS

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can re-enter IDLE by executing the SLEEP instruction.

If Recover-on-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of IDLE also restores full-speed CPU execution when DOZE is also enabled.

#### 9.2.2 IDLE AND WDT

When in IDLE, the WDT Reset is blocked and will instead wake the device. The WDT wake-up is not an interrupt, therefore ROI does not apply.

Note: The WDT can bring the device out of IDLE, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

#### 9.3 Sleep Mode

Sleep mode is entered by executing the SLEEP instruction, while the Idle Enable (IDLEN) bit of the CPUDOZE register is clear (IDLEN = 0). If the SLEEP instruction is executed while the IDLEN bit is set (IDLEN = 1), the CPU will enter the Idle mode (Section 9.3.3 "Low-Power Sleep Mode").

Upon entering Sleep mode, the following conditions exist:

- 1. Resets other than WDT are not affected by Sleep mode; WDT will be cleared but keeps running if enabled for operation during Sleep.

- 2. The  $\overline{PD}$  bit of the STATUS register is cleared.

- 3. The  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. The CPU and System clocks are disabled.

- 31 kHz LFINTOSC, HFINTOSC and SOSC will remain enabled if any peripheral has requested them as a clock source or if the HFOEN, LFOEN, or SOSCEN bits of the OSCEN register are set.

- ADC is unaffected if the dedicated ADCRC oscillator is selected. When the ADC clock source is something other than ADCRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

- 7. I/O ports maintain the status they had before Sleep was executed (driving high, low, or high-impedance) only if no peripheral connected to the I/O port is active.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using any oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or VSS externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 24.0 "5-bit Digital-to-Analog Converter (DAC1) Module" and Section 16.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

## 11.4.9 WRERR BIT

The WRERR bit can be used to determine if a write error occurred.

WRERR will be set if one of the following conditions occurs:

- If WR is set while the NVMADRH:NMVADRL points to a write-protected address

- A Reset occurs while a self-write operation was in progress

- An unlock sequence was interrupted

The WRERR bit is normally set by hardware, but can be set by the user for test purposes. Once set, WRERR must be cleared in software.

#### TABLE 11-4: ACTIONS FOR PROGRAM FLASH MEMORY WHEN WR = 1

| Free | LWLO | Actions for Program Flash Memory when WR = 1                                                                                            | Comments                                                                                                                                              |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | Write the write latch data to program Flash memory<br>row. See Section 11.4.4 "NVMREG Erase of Pro-<br>gram Flash Memory"               | <ul> <li>If WP is enabled, WR is cleared<br/>and WRERR is set</li> <li>Write latches are reset to 3FFh</li> <li>NVMDATH:NVMDATL is ignored</li> </ul> |

| 0    | 1    | Copy NVMDATH:NVMDATL to the write latch corre-<br>sponding to NVMADR LSBs. See Section 11.4.4<br>"NVMREG Erase of Program Flash Memory" | <ul><li>Write protection is ignored</li><li>No memory access occurs</li></ul>                                                                         |

| 1    | х    | Erase the 32-word row of NVMADRH:NVMADRL<br>location. See <b>Section 11.4.3 "NVMREG Write to</b><br><b>EEPROM"</b>                      | <ul> <li>If WP is enabled, WR is cleared<br/>and WRERR is set</li> <li>All 32 words are erased</li> <li>NVMDATH:NVMDATL is ignored</li> </ul>         |

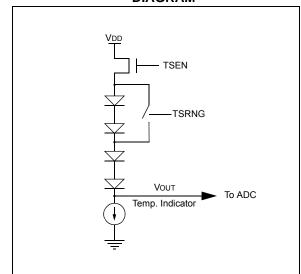

## 17.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN2092, *"Using the Temperature Indicator Module"* (DS0002092) for more details regarding the calibration process.

## 17.1 Circuit Operation

Figure 17-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 17-1 describes the output characteristics of the temperature indicator.

## EQUATION 17-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 16.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower VDD voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 17-1: TEMPERATURE CIRCUIT DIAGRAM

## 17.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 17-1 shows the recommended minimum  $\mathsf{V}\mathsf{D}\mathsf{D}$  vs. range setting.

#### TABLE 17-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

## 17.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is provided for the temperature circuit output. Refer to **Section 22.0** "**Analog-to-Digital Converter (ADC) Module**" for detailed information.

|                  | 0-7. CWOA                                                                                                             |                                 |                |                | NOL NEOISI       |                  |              |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|----------------|------------------|------------------|--------------|--|

| U-0              | U-0                                                                                                                   | U-0                             | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

| —                | —                                                                                                                     | —                               | AS4E           | AS3E           | AS2E             | AS1E             | AS0E         |  |

| bit 7            |                                                                                                                       |                                 |                |                |                  |                  | bit C        |  |

| Legend:          |                                                                                                                       |                                 |                |                |                  |                  |              |  |

| R = Readable     | bit                                                                                                                   | W = Writable                    | bit            | U = Unimpler   | mented bit, read | l as '0'         |              |  |

| u = Bit is unch  | anged                                                                                                                 | x = Bit is unkr                 | iown           | -n/n = Value : | at POR and BO    | R/Value at all o | other Resets |  |

| '1' = Bit is set |                                                                                                                       | '0' = Bit is clea               | ared           | q = Value de   | pends on condit  | ion              |              |  |

|                  |                                                                                                                       |                                 |                |                |                  |                  |              |  |

| bit 7-5          | Unimplemen                                                                                                            | ted: Read as '                  | כ'             |                |                  |                  |              |  |

| bit 4            | AS4E: CWG Auto-Shutdown Source 4 (CLC4) Enable bit                                                                    |                                 |                |                |                  |                  |              |  |

|                  | 1 = Auto-shutdown for CLC4 is enabled                                                                                 |                                 |                |                |                  |                  |              |  |

|                  | 0 = Auto-shutdown for CLC4 is disabled                                                                                |                                 |                |                |                  |                  |              |  |

| bit 3            |                                                                                                                       | Auto-Shutdowr                   | •              | ,              | t                |                  |              |  |

|                  | 1 = Auto-shutdown from CLC2 is enabled                                                                                |                                 |                |                |                  |                  |              |  |

| 1.1.0            | <ul> <li>0 = Auto-shutdown from CLC2 is disabled</li> <li>AS2E: CWG Auto-Shutdown Source 2 (C2) Enable bit</li> </ul> |                                 |                |                |                  |                  |              |  |

| bit 2            |                                                                                                                       | Auto-Shutdowr<br>utdown from Co | •              | ,              |                  |                  |              |  |

|                  |                                                                                                                       | utdown from Co                  | •              |                |                  |                  |              |  |

| bit 1            | AS1E: CWG Auto-Shutdown Source 1 (C1) Enable bit                                                                      |                                 |                |                |                  |                  |              |  |

|                  | 1 = Auto-shutdown from Comparator 1 is enabled                                                                        |                                 |                |                |                  |                  |              |  |

|                  | 0 = Auto-shi                                                                                                          | utdown from Co                  | omparator 1 is | disabled       |                  |                  |              |  |

| bit 0            | AS0E: CWG                                                                                                             | Auto-Shutdowr                   | n Source 0 (CV | VGxPPS) Enal   | ble bit          |                  |              |  |

|                  |                                                                                                                       | utdown from C                   |                |                |                  |                  |              |  |

|                  | 0 = Auto-shi                                                                                                          | utdown from C                   | NGxPPS is dis  | sabled         |                  |                  |              |  |

|                  |                                                                                                                       |                                 |                |                |                  |                  |              |  |

## REGISTER 20-7: CWGxAS1: CWG AUTO-SHUTDOWN CONTROL REGISTER 1

#### REGISTER 20-8: CWGxDBR: CWGx RISING DEAD-BAND COUNT REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

|       | _   |         |         | DBR     | <5:0>   |         |         |

| bit 7 | •   |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7-6 Unimplemented: Read as '0' bit 5-0 DBR<5:0>: CWG Rising Edge Triggered Dead-Band Count bits 11 1111 = 63-64 CWG clock periods 11 1110 = 62-63 CWG clock periods . . . 00 0010 = 2-3 CWG clock periods 00 0001 = 1-2 CWG clock periods 00 0000 = 0 CWG clock periods. Dead-band generation is bypassed.

#### 22.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

| _       |                                          |

2: The ADC operates during Sleep only when the ADCRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

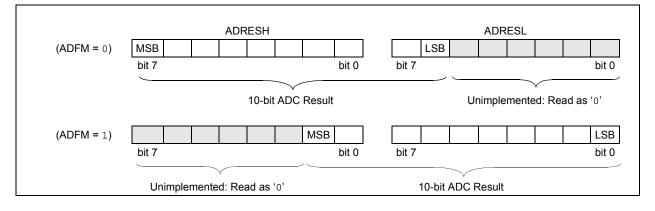

#### 22.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 22-3 shows the two output formats.

## FIGURE 22-3: 10-BIT ADC CONVERSION RESULT FORMAT

| R/W-0/0                 | R/W-0/0                                                                                                                                                                                                                                                   | R/W-0/0                                  | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0 | R/W-0/0     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|-----------------|------------------|---------|-------------|

|                         | T0CS<2:0>                                                                                                                                                                                                                                                 |                                          | <b>T0ASYNC</b> |                 | TOCKP            | °S<3:0> |             |

| bit 7                   |                                                                                                                                                                                                                                                           |                                          |                |                 |                  |         | bit (       |

| Logondi                 |                                                                                                                                                                                                                                                           |                                          |                |                 |                  |         |             |

| Legend:<br>R = Readable | bit                                                                                                                                                                                                                                                       | W = Writable                             | hit            | II = I Inimpler | nented bit, read | las 'N' |             |

| u = Bit is unch         |                                                                                                                                                                                                                                                           | x = Bit is unkr                          |                | •               | at POR and BO    |         | ther Resets |

| '1' = Bit is set        | •                                                                                                                                                                                                                                                         | 0' = Bit is clear                        |                |                 |                  |         |             |

|                         |                                                                                                                                                                                                                                                           |                                          | aieu           |                 |                  |         |             |

| bit 7-5                 | 000 = T0CKI                                                                                                                                                                                                                                               | PPS (Inverted)<br>4<br>OSC<br>OSC<br>ved | ource Select b | its             |                  |         |             |

| bit 4                   | <b>TOASYNC:</b> TMR0 Input Asynchronization<br>1 = The input to the TMR0 counter is not s<br>0 = The input to the TMR0 counter is sync                                                                                                                    |                                          |                | synchronized t  |                  | S       |             |

| bit 3-0                 | <b>TOCKPS&lt;3:0</b><br>0000 = 1:1<br>0001 = 1:2<br>0010 = 1:4<br>0011 = 1:8<br>0100 = 1:16<br>0101 = 1:32<br>0110 = 1:64<br>0111 = 1:126<br>1000 = 1:512<br>1010 = 1:102<br>1011 = 1:204<br>1100 = 1:405<br>1101 = 1:815<br>1110 = 1:163<br>1111 = 1:327 | 5<br>2<br>24<br>48<br>96<br>92<br>384    | ate Select bit |                 |                  |         |             |

#### REGISTER 26-4: T0CON1: TIMER0 CONTROL REGISTER 1

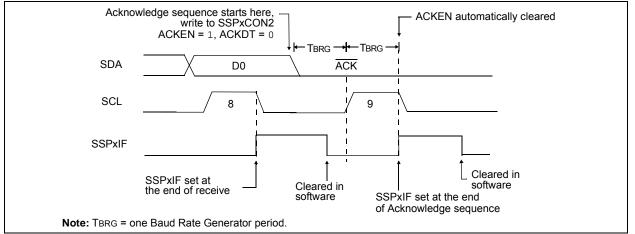

#### 30.6.8 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN bit of the SSPxCON2 register. When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSPx module then goes into Idle mode (Figure 30-30).

#### 30.6.8.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

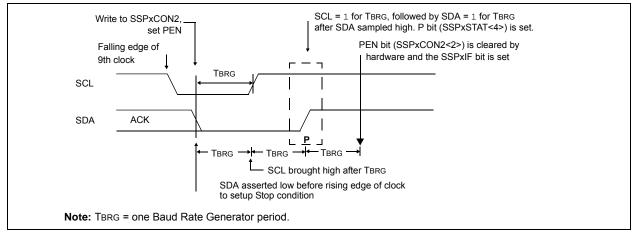

#### 30.6.9 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN bit of the SSPxCON2 register. At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit of the SSPxSTAT register is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 30-31).

#### 30.6.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

## FIGURE 30-30: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 30-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

## 31.3.2 AUTO-BAUD OVERFLOW

During the course of automatic-baud detection, the ABDOVF bit of the BAUD1CON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SP1BRGH:SP1BRGL register pair. The Overflow condition will set the RCIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RC1REG is read after the overflow occurs but before the fifth rising edge, then the fifth rising edge will set the RCIF again.

Terminating the auto-baud process early to clear an Overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared, then those will be falsely detected as Start bits. The following steps are recommended to clear the Overflow condition:

- 1. Read RC1REG to clear RCIF

- 2. If RCIDL is zero, then wait for RCIF and repeat step 1

- 3. Clear the ABDOVF bit

#### 31.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART1 are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUD1CON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART1 remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART1 module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 31-7), and asynchronously if the device is in Sleep mode (Figure 31-8). The Interrupt condition is cleared by reading the RC1REG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART1 module is in Idle mode waiting to receive the next character.

#### 31.3.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be ten or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART1.

#### WUE Bit

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The Interrupt condition is then cleared in software by reading the RC1REG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

| RETLW            | Return with literal in W                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             |