#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

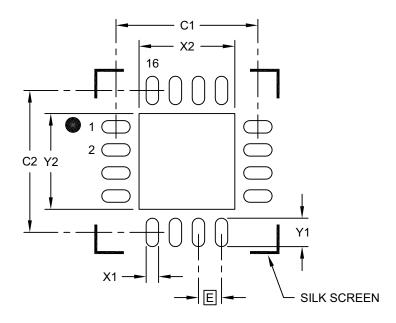

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 20-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18345-e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-1:DEVICE PERIPHERAL<br/>SUMMARY (CONTINUED)

| Peripheral   |      | PIC16(L)F18325 | PIC16(L)F18345 |

|--------------|------|----------------|----------------|

| Timers (TMR) |      |                |                |

|              | TMR0 | •              | •              |

|              | TMR1 | •              | •              |

|              | TMR2 | •              | •              |

|              | TMR3 | •              | •              |

|              | TMR4 | •              | •              |

|              | TMR5 | •              | •              |

|              | TMR6 | •              | •              |

# 7.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 7.3 "Clock Switching" for more information.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- 1. The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates up to 32 MHz.

- The LFINTOSC (Low-Frequency Internal Oscillator) is factory calibrated and operates at 31 kHz.

# 7.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 32 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (1 MHz) or '000' (32 MHz) to set the oscillator upon device Power-up or Reset

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time

The HFINTOSC frequency can be selected by setting the HFFRQ<2:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the output of the selected clock source by a range between 1:1 and 1:512.

# 7.2.2.2 2x PLL

The oscillator module contains a PLL that can be used with the HFINTOSC clock source to provide a system clock source. The input frequency to the PLL is limited to 8, 12, or 16 MHz, which will yield a system clock source of 16, 24, or 32 MHz, respectively.

The PLL may be enabled for use by one of two methods:

- Program the RSTOSC bits in the Configuration Word 1 to '000' to enable the HFINTOSC (32 MHz). This setting configures the HFFRQ<2:0> bits to '110' (16 MHz) and activates the 2x PLL.

- Write '000' the NOSC<2:0> bits in the OSCCON1 register to enable the 2x PLL, and write the correct value into the HFFRQ<3:0> bits of the OSCFRQ register to select the desired system clock frequency. See Register 6-6 for more information.

#### **Register Definitions: Interrupt Control** 8.6

| W = Writable bit<br>x = Bit is unknow<br>'0' = Bit is cleare<br>HC = Hardware<br>I Interrupt Enable bi | vn<br>ed<br>clear                                                                                                                                                                            |                                                                                                                    | emented bit, rea                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             | INTEDG<br>bit 0                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x = Bit is unknow<br>'0' = Bit is cleare<br>HC = Hardware                                              | vn<br>ed<br>clear                                                                                                                                                                            |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

| x = Bit is unknow<br>'0' = Bit is cleare<br>HC = Hardware                                              | vn<br>ed<br>clear                                                                                                                                                                            |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             | ll other Resets                                                                                                                                                                                                                             |

| x = Bit is unknow<br>'0' = Bit is cleare<br>HC = Hardware                                              | vn<br>ed<br>clear                                                                                                                                                                            |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             | ll other Resets                                                                                                                                                                                                                             |

| '0' = Bit is cleare<br>HC = Hardware                                                                   | ed<br>clear                                                                                                                                                                                  | -n/n = Value                                                                                                       | at POR and BC                                                                                                                                                                                                                                | DR/Value at al                                                                                                                                                                                                                              | II other Resets                                                                                                                                                                                                                             |

| HC = Hardware                                                                                          | clear                                                                                                                                                                                        |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

|                                                                                                        |                                                                                                                                                                                              |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

| I Interrupt Enable bi                                                                                  | it                                                                                                                                                                                           |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

|                                                                                                        |                                                                                                                                                                                              |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

| s all active interrupts                                                                                | S                                                                                                                                                                                            |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

| s all active peripher                                                                                  | al interru                                                                                                                                                                                   | ıpts                                                                                                               |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

| ented: Read as '0'.                                                                                    |                                                                                                                                                                                              |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

| ot on rising edge of                                                                                   | INT pin                                                                                                                                                                                      |                                                                                                                    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                             |

|                                                                                                        | as all interrupts<br>oberal Interrupt Ena<br>s all active peripher<br>as all peripheral inte<br>ented: Read as '0'.<br>Interrupt Edge Selec<br>of on rising edge of<br>ot on falling edge of | es all interrupts<br>oheral Interrupt Enable bit<br>s all active peripheral interru<br>s all peripheral interrupts | es all interrupts<br>oberal Interrupt Enable bit<br>is all active peripheral interrupts<br>is all peripheral interrupts<br>ented: Read as '0'.<br>Interrupt Edge Select bit<br>ot on rising edge of INT pin<br>ot on falling edge of INT pin | es all interrupts<br>oberal Interrupt Enable bit<br>s all active peripheral interrupts<br>es all peripheral interrupts<br>ented: Read as '0'.<br>Interrupt Edge Select bit<br>ot on rising edge of INT pin<br>ot on falling edge of INT pin | es all interrupts<br>oberal Interrupt Enable bit<br>s all active peripheral interrupts<br>es all peripheral interrupts<br>ented: Read as '0'.<br>Interrupt Edge Select bit<br>ot on rising edge of INT pin<br>ot on falling edge of INT pin |

#### **REGISTER 8-1:** INTCON: INTERRUPT CONTROL REGISTER

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

### 9.3.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled.

- 3. POR Reset.

- 4. Watchdog Timer, if enabled

- 5. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information).

The first three events will cause a device Reset. The last two events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.11 "Determining the Cause of a Reset"**.

The WDT is cleared when the device wakes-up from Sleep, regardless of the source of wake-up.

# 9.3.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| U-0              | R/W-0/0                           | R/W-0/0                                                                                                                                      | R/W/HC-0/0                           | R/W/HC-x/q     | R/W-0/0                           | R/S/HC-0/0          | R/S/HC-0/0    |  |  |  |

|------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|-----------------------------------|---------------------|---------------|--|--|--|

| —                | NVMREGS                           | LWLO                                                                                                                                         | FREE                                 | WRERR          | WREN                              | WR                  | RD            |  |  |  |

| bit 7            |                                   |                                                                                                                                              |                                      |                |                                   |                     | bit (         |  |  |  |

|                  |                                   |                                                                                                                                              |                                      |                |                                   |                     |               |  |  |  |

| Legend:          |                                   |                                                                                                                                              |                                      |                |                                   |                     |               |  |  |  |

| R = Readable     |                                   | W = Writable                                                                                                                                 |                                      | •              | mented bit, read                  |                     |               |  |  |  |

| S = Bit can onl  | y be set                          | x = Bit is unk                                                                                                                               |                                      |                | at POR and BO                     |                     | ther Resets   |  |  |  |

| '1' = Bit is set |                                   | '0' = Bit is cle                                                                                                                             | ared                                 | HC = BIt is ci | eared by hardw                    | are                 |               |  |  |  |

| bit 7            | Unimplemen                        | ted: Read as '                                                                                                                               | 0'                                   |                |                                   |                     |               |  |  |  |

| bit 6            | •                                 | Configuration S                                                                                                                              |                                      |                |                                   |                     |               |  |  |  |

|                  | 1 = Access E                      | EPROM, Con                                                                                                                                   | figuration, user                     | ID and device  | e ID registers                    |                     |               |  |  |  |

|                  |                                   | rogram Flash                                                                                                                                 | -                                    |                |                                   |                     |               |  |  |  |

| bit 5            |                                   | Write Latches                                                                                                                                | Only bit                             |                |                                   |                     |               |  |  |  |

|                  | -                                 | When FREE = 0:<br>1 = The next WR command updates the write latch for this word within the row; no memory operation                          |                                      |                |                                   |                     |               |  |  |  |

|                  | is initiate                       | d.                                                                                                                                           | -                                    |                |                                   |                     |               |  |  |  |

|                  |                                   | WR command<br>the bit is ignore                                                                                                              | l writes data or<br>ਜ                | erases.        |                                   |                     |               |  |  |  |

| bit 4            |                                   | 0                                                                                                                                            | ory Erase Enal                       | ble bit        |                                   |                     |               |  |  |  |

|                  | When NVMR                         | EGS:NVMADF                                                                                                                                   | R points to a pro                    | ogram Flash m  | nemory location:                  |                     |               |  |  |  |

|                  |                                   | •                                                                                                                                            |                                      |                | and; the row co                   | ntaining the indi   | cated addres  |  |  |  |

|                  |                                   |                                                                                                                                              | repare for writi<br>ve completed r   |                |                                   |                     |               |  |  |  |

| bit 3            |                                   | -                                                                                                                                            | ror Flag bit <sup>(1,2</sup>         | -              |                                   |                     |               |  |  |  |

|                  |                                   | This bit is normally set by hardware.<br>1 = A write operation was interrupted by a Reset, interrupted unlock sequence, or WR was written to |                                      |                |                                   |                     |               |  |  |  |

|                  |                                   |                                                                                                                                              | nterrupted by a<br>ints to a write-p |                |                                   | quence, or WR       | was written t |  |  |  |

|                  |                                   |                                                                                                                                              | peration comp                        |                |                                   |                     |               |  |  |  |

| bit 2            | WREN: Progr                       | am/Erase Ena                                                                                                                                 | ble bit                              |                |                                   |                     |               |  |  |  |

|                  |                                   | ogram/erase o                                                                                                                                |                                      | <b>-</b>       |                                   |                     |               |  |  |  |

| bit 1            | WR: Write Co                      |                                                                                                                                              | rasing of progra                     | am Flash       |                                   |                     |               |  |  |  |

|                  |                                   |                                                                                                                                              | points to a EEF                      | PROM location  | 1:                                |                     |               |  |  |  |

|                  | 1 = Initiates a                   | an erase/progr                                                                                                                               | am cycle at the                      | e correspondin | g EEPROM loca                     | ation               |               |  |  |  |

|                  |                                   |                                                                                                                                              | eration is com                       |                |                                   |                     |               |  |  |  |

|                  |                                   |                                                                                                                                              | ndicated by Tat                      | -              | emory location:                   |                     |               |  |  |  |

|                  |                                   | •                                                                                                                                            | eration is com                       |                | tive                              |                     |               |  |  |  |

| bit 0            | RD: Read Co                       |                                                                                                                                              |                                      |                |                                   |                     |               |  |  |  |

|                  |                                   |                                                                                                                                              |                                      |                | data to NVMDA<br>omplete. The bit |                     |               |  |  |  |

|                  | in softwa                         |                                                                                                                                              |                                      |                | inpiete. The bit                  | can only be se      |               |  |  |  |

|                  | 0 = NVM rea                       | d operation is                                                                                                                               | complete and i                       | nactive.       |                                   |                     |               |  |  |  |

|                  |                                   |                                                                                                                                              |                                      |                | ration it may be                  | '0' <b>or</b> '1'). |               |  |  |  |

|                  | must be cleared<br>may be written |                                                                                                                                              |                                      |                |                                   |                     |               |  |  |  |

|                  |                                   |                                                                                                                                              |                                      |                | ection 11.4.2 "                   | NVM Unlock S        | equence".     |  |  |  |

|                  |                                   |                                                                                                                                              |                                      |                | are when comp                     | lete.               |               |  |  |  |

|                  | ce a write opera                  |                                                                                                                                              | I, Setting this b                    |                |                                   |                     |               |  |  |  |

### REGISTER 11-5: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

7: Reading from EEPROM loads only NVMDATL<7:0> (Register 11-1).

# 13.8 Register Definitions: PPS Input Selection

# REGISTER 13-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

| U-0              | U-0                                                                | U-0                                   | R/W-q/u | R/W-q/u        | R/W-q/u          | R/W-q/u          | R/W-q/u     |  |  |  |

|------------------|--------------------------------------------------------------------|---------------------------------------|---------|----------------|------------------|------------------|-------------|--|--|--|

|                  | —                                                                  |                                       |         |                | xxxPPS<4:0>      |                  |             |  |  |  |

| bit 7            |                                                                    |                                       |         |                |                  |                  | bit         |  |  |  |

|                  |                                                                    |                                       |         |                |                  |                  |             |  |  |  |

| Legend:          |                                                                    |                                       |         |                |                  |                  |             |  |  |  |

| R = Readable     | e bit                                                              | W = Writable                          | bit     | U = Unimpler   | mented bit, read | l as '0'         |             |  |  |  |

| u = Bit is unc   | hanged                                                             | x = Bit is unkr                       | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set |                                                                    | '0' = Bit is cle                      | ared    | q = value dep  | ends on periph   | eral             |             |  |  |  |

|                  |                                                                    | mtadi Daad aa (                       | 0'      |                |                  |                  |             |  |  |  |

| bit 7-5          | -                                                                  | ented: Read as '                      |         | tion hite      |                  |                  |             |  |  |  |

| bit 4-0          | xxxPPS<4:0>: Peripheral xxx Input Selection bits                   |                                       |         |                |                  |                  |             |  |  |  |

|                  | 11xxx = Reserved. Do not use.                                      |                                       |         |                |                  |                  |             |  |  |  |

|                  | 10111 = Peripheral input is RC7 <sup>(1)</sup>                     |                                       |         |                |                  |                  |             |  |  |  |

|                  | 10110 = Peripheral input is RC6 <sup>(1)</sup>                     |                                       |         |                |                  |                  |             |  |  |  |

|                  | 10101 = Peripheral input is RC5                                    |                                       |         |                |                  |                  |             |  |  |  |

|                  | 10100 = Peripheral input is RC4                                    |                                       |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is                    |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | 10010 = Peripheral input is RC2       |         |                |                  |                  |             |  |  |  |

|                  | 10001 = Peripheral input is RC1<br>10000 = Peripheral input is RC0 |                                       |         |                |                  |                  |             |  |  |  |

|                  | · · · · · · · · · · · · · · · · · · ·                              |                                       |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is                    |         |                |                  |                  |             |  |  |  |

|                  | 01110 = Pe                                                         | eripheral input is                    | RB6(')  |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is                    |         |                |                  |                  |             |  |  |  |

|                  | 01100 = Peripheral input is RB4 <sup>(1)</sup>                     |                                       |         |                |                  |                  |             |  |  |  |

|                  | <br>0011x = Reserved. Do not use.                                  |                                       |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is                    |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is                    |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is                    |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is                    |         |                |                  |                  |             |  |  |  |

|                  |                                                                    | eripheral input is eripheral input is |         |                |                  |                  |             |  |  |  |

| Note 1. DI       |                                                                    | • •                                   |         |                |                  |                  |             |  |  |  |

**Note 1:** PIC16(L)F18345 only.

# 19.1.3 PWM RESOLUTION

PWM resolution, expressed in number of bits, defines the maximum number of discrete steps that can be present in a single PWM period. For example, a 10-bit resolution will result in 1024 discrete steps, whereas an 8-bit resolution will result in 256 discrete steps.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 19-4.

# EQUATION 19-4:

Resolution =  $\frac{\log[4(PR2+1)]}{\log(2)}$  bits

**Note:** If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

# 19.1.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 19.1.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 7.0, Oscillator Module** for additional details.

# 19.1.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWMx registers to their Reset states.

# 19.1.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the module for using the PWMx outputs:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Configure the PWM output polarity by configuring the PWMxPOL bit of the PWMxCON register.

- 3. Load the PR2 register with the PWM period value, as determined by Equation 19-1.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value, as determined by Equation 19-2.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Select the Timer2 prescale value by configuring the T2CKPS bit of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Wait until the TMR2IF is set.

- 7. When the TMR2IF flag bit is set:

- Clear the associated TRIS bit(s) to enable the output driver.

- Route the signal to the desired pin by configuring the RxyPPS register.

- Enable the PWMx module by setting the PWMxEN bit of the PWMxCON register.

In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then the PWM module can be enabled during Step 2 by setting the PWMxEN bit of the PWMxCON register.

# PIC16(L)F18325/18345

# 21.2 CLCx Interrupts

An interrupt will be generated upon a change in the output value of the CLCx when the appropriate interrupt enables are set. A rising edge detector and a falling edge detector are present in each CLC for this purpose.

The CLCxIF bit of the associated PIR3 register will be set when either edge detector is triggered and its associated enable bit is set. The LCxINTP bit enables rising edge interrupts and the LCxINTN bit enables falling edge interrupts. Both are located in the CLCxCON register.

To fully enable the interrupt, set the following bits:

- · CLCxIE bit of the PIE3 register

- LCxINTP bit of the CLCxCON register (for a rising edge detection)

- LCxINTN bit of the CLCxCON register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The CLCxIF bit of the PIR3 register, must be cleared in software as part of the interrupt service. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

# 21.3 Output Mirror Copies

Mirror copies of all LCxCON output bits are contained in the CLCDATA register. Reading this register samples the outputs of all CLCs simultaneously. This prevents any timing skew introduced by testing or reading the LCxOUT bits in the individual CLCxCON registers.

# 21.4 Effects of a Reset

The CLCxCON register is cleared to zero as the result of a Reset. All other selection and gating values remain unchanged.

# 21.5 Operation During Sleep

The CLC module operates independently from the system clock and will continue to run during Sleep, provided that the input sources selected remain active.

The HFINTOSC remains active during Sleep when the CLC module is enabled and the HFINTOSC is selected as an input source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and as a CLC input source, when the CLC is enabled, the CPU will go idle during Sleep, but the CLC will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

# 21.6 CLCx Setup Steps

The following steps should be followed when setting up the CLCx:

- Disable CLCx by clearing the LCxEN bit.

- Select desired inputs using CLCxSEL0 through CLCxSEL3 registers (See Table 21-1).

- · Clear any associated ANSEL bits.

- Set all TRIS bits associated with external CLC inputs.

- Enable the chosen inputs through the four gates using CLCxGLS0, CLCxGLS1, CLCxGLS2, and CLCxGLS3 registers.

- Select the gate output polarities with the LCxGyPOL bits of the CLCxPOL register.

- Select the desired logic function with the LCxMODE<2:0> bits of the CLCxCON register.

- Select the desired polarity of the logic output with the LCxPOL bit of the CLCxPOL register. (This step may be combined with the previous gate output polarity step).

- If driving a device pin, set the desired pin PPS control register and also clear the TRIS bit corresponding to that output.

- If interrupts are desired, configure the following bits:

- Set the LCxINTP bit in the CLCxCON register for rising event.

- Set the LCxINTN bit in the CLCxCON register for falling event.

- Set the CLCxIE bit of the PIE3 register.

- Set the GIE and PEIE bits of the INTCON register.

- Enable the CLCx by setting the LCxEN bit of the CLCxCON register.

| U-0                                                                                    | U-0                                                              | R/W-x/u                                                                                  | R/W-x/u                                      | R/W-x/u                                            | R/W-x/u            | R/W-x/u                      | R/W-x/u     |  |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------|--------------------|------------------------------|-------------|--|

| _                                                                                      |                                                                  |                                                                                          | LCxD1S<5:0>                                  |                                                    |                    |                              |             |  |

| bit 7                                                                                  |                                                                  |                                                                                          |                                              |                                                    |                    |                              | bit         |  |

| Legend:                                                                                |                                                                  |                                                                                          |                                              |                                                    |                    |                              |             |  |

| R = Readable                                                                           | e bit                                                            | W = Writable                                                                             | bit                                          | U = Unimplem                                       | nented bit, read   | as '0'                       |             |  |

| u = Bit is uncł                                                                        | hanged                                                           | x = Bit is unkr                                                                          | nown                                         | -n/n = Value a                                     | t POR and BO       | R/Value at all o             | ther Resets |  |

| '1' = Bit is set                                                                       | t                                                                | '0' = Bit is cle                                                                         | ared                                         |                                                    |                    |                              |             |  |

| bit 7-6                                                                                | Unimpleme                                                        | nted: Read as '                                                                          | 0'                                           |                                                    |                    |                              |             |  |

| bit 5-0                                                                                | LCxD1S<5:0<br>See Table 21                                       | <b>)&gt;:</b> CLCx Data1<br> -1.                                                         | Input Selection                              | on bits                                            |                    |                              |             |  |

| REGISTER                                                                               | 21-4: CLCx                                                       | SEL1: GENE                                                                               | RIC CLCx D                                   | ATA 1 SELEC                                        | CT REGISTEI        | R                            |             |  |

| U-0                                                                                    |                                                                  |                                                                                          |                                              |                                                    |                    | R/W-x/u                      |             |  |

| 0-0                                                                                    | U-0                                                              | R/W-x/u                                                                                  | R/W-x/u                                      | R/W-x/u                                            | R/W-x/u            | R/W-X/U                      | R/W-x/u     |  |

| _                                                                                      | 0-0                                                              | R/W-x/u                                                                                  | R/W-x/u                                      |                                                    | R/W-x/u<br>2S<5:0> | R/W-X/U                      |             |  |

|                                                                                        | <u> </u>                                                         | R/w-x/u                                                                                  | R/W-x/u                                      |                                                    |                    | R/W-X/U                      | R/W-x/u     |  |

| bit 7                                                                                  | <u> </u>                                                         | R/W-x/u                                                                                  | R/W-x/u                                      |                                                    |                    | R/W-X/U                      |             |  |

| bit 7                                                                                  | -                                                                | W = Writable                                                                             |                                              | LCxD2                                              |                    |                              |             |  |

| bit 7<br>Legend:<br>R = Readable                                                       | e bit                                                            |                                                                                          | bit                                          | LCxD2<br>U = Unimplem                              | 2S<5:0>            | as '0'                       | bit         |  |

|                                                                                        | e bit<br>hanged                                                  | W = Writable                                                                             | bit                                          | LCxD2<br>U = Unimplem                              | ented bit, read    | as '0'                       | bit         |  |

| bit 7<br>Legend:<br>R = Readable<br>u = Bit is unch<br>'1' = Bit is set                | e bit<br>hanged                                                  | W = Writable<br>x = Bit is unkr<br>'0' = Bit is cle                                      | bit<br>nown<br>ared                          | LCxD2<br>U = Unimplem                              | ented bit, read    | as '0'                       | bit         |  |

| <br>bit 7<br>Legend:<br>R = Readable<br>u = Bit is unch<br>'1' = Bit is set<br>bit 7-6 | e bit<br>hanged<br>t<br>Unimplemen                               | W = Writable<br>x = Bit is unki<br>'0' = Bit is cle<br>hted: Read as '<br>>: CLCx Data 2 | bit<br>nown<br>ared                          | LCxD2<br>U = Unimplem<br>-n/n = Value a            | ented bit, read    | as '0'                       | bit         |  |

| _                                                                                      | e bit<br>hanged<br>t<br>Unimplemen<br>LCxD2S<5:0<br>See Table 21 | W = Writable<br>x = Bit is unki<br>'0' = Bit is cle<br>hted: Read as '<br>>: CLCx Data 2 | bit<br>nown<br>ared<br>0'<br>2 Input Selecti | LCxD2<br>U = Unimplem<br>-n/n = Value a<br>on bits | ented bit, read    | l as '0'<br>R/Value at all c | bit         |  |

|   | U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|---|-------|-----|---------|---------|---------|---------|---------|---------|

|   | —     | —   |         |         | LCxD3   | 3S<5:0> |         |         |

| t | oit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

# bit 7-6 Unimplemented: Read as '0'

bit 5-0 LCxD3S<5:0>: CLCx Data 3 Input Selection bits See Table 21-1.

#### 22.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |  |  |  |  |  |  |  |

|---------|------------------------------------------|--|--|--|--|--|--|--|

|         | every conversion, regardless of whether  |  |  |  |  |  |  |  |

|         | or not the ADC interrupt is enabled.     |  |  |  |  |  |  |  |

| _       |                                          |  |  |  |  |  |  |  |

2: The ADC operates during Sleep only when the ADCRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the ADIE bit of the PIE1 register and the PEIE bit of the INTCON register must both be set and the GIE bit of the INTCON register must be cleared. If all three of these bits are set, the execution will switch to the Interrupt Service Routine.

# 22.1.6 RESULT FORMATTING

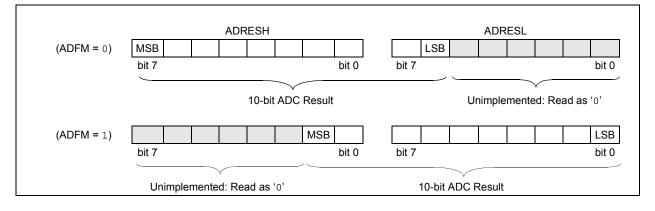

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 22-3 shows the two output formats.

# FIGURE 22-3: 10-BIT ADC CONVERSION RESULT FORMAT

| R/W-0/0         | R/W-0/0                                                                                                                                                                                                                                                                      | R/W-0/0           | R/W-0/0       | U-0             | R/W-0/0                                  | R/W-0/0         | R/W-0/0      |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|-----------------|------------------------------------------|-----------------|--------------|--|

| ADFM            |                                                                                                                                                                                                                                                                              | ADCS<2:0>         |               | —               | ADNREF                                   | ADPRE           | EF<1:0>      |  |

| bit 7           |                                                                                                                                                                                                                                                                              |                   |               |                 |                                          |                 | bit C        |  |

| Legend:         |                                                                                                                                                                                                                                                                              |                   |               |                 |                                          |                 |              |  |

| R = Readab      | le hit                                                                                                                                                                                                                                                                       | W = Writable      | hit           |                 | emented bit, read                        | 1 as 'O'        |              |  |

| u = Bit is un   |                                                                                                                                                                                                                                                                              | x = Bit is unkr   |               | •               | at POR and BO                            |                 | other Resets |  |

| '1' = Bit is se | •                                                                                                                                                                                                                                                                            | '0' = Bit is clea |               |                 |                                          |                 |              |  |

| 1 – Dit 13 30   |                                                                                                                                                                                                                                                                              |                   | arcu          |                 |                                          |                 |              |  |

| bit 7           | 1 = Right ju<br>loaded.                                                                                                                                                                                                                                                      |                   | Significant b |                 | H are set to '0' w<br>. are set to '0' w |                 |              |  |

| bit 6-4         | loaded.<br>ADCS<2:0>: ADC Conversion Clock Select bits<br>111 = ADCRC (dedicated RC oscillator)<br>110 = Fosc/64<br>101 = Fosc/16<br>100 = Fosc/4<br>011 = ADCRC (dedicated RC oscillator)<br>010 = Fosc/32<br>001 = Fosc/8<br>000 = Fosc/2                                  |                   |               |                 |                                          |                 |              |  |

| bit 3           | Unimpleme                                                                                                                                                                                                                                                                    | nted: Read as '   | 0'            |                 |                                          |                 |              |  |

| bit 2           | Unimplemented: Read as '0'<br>ADNREF: A/D Negative Voltage Reference Configuration bit<br>When ADON = 0, all multiplexer inputs are disconnected.<br>0 = VREF- is connected to Vss<br>1 = VREF- is connected to external VREF-                                               |                   |               |                 |                                          |                 |              |  |

| bit 1-0         | ADPREF<1:0>: ADC Positive Voltage Reference Configuration bits<br>11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module <sup>(1)</sup><br>10 = VREF+ is connected to external VREF+ pin <sup>(1)</sup><br>01 = Reserved<br>00 = VREF+ is connected to VDD |                   |               |                 |                                          |                 |              |  |

| Note 1: W       | Vhen selecting t                                                                                                                                                                                                                                                             | he VREE+ nin as   | the source of | the positive re | eference, be awa                         | re that a minir | mum voltage  |  |

#### REGISTER 22-2: ADCON1: ADC CONTROL REGISTER 1

**Note 1:** When selecting the VREF+ pin as the source of the positive reference, be aware that a minimum voltage specification exists. See Table 35-13 for details.

| U-0                                     | U-0                               | U-0 | R/W-0/0    | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------------------------------------|-----------------------------------|-----|------------|-------------------------------------------------------|---------|---------|---------|--|

| —                                       | —                                 | —   | DAC1R<4:0> |                                                       |         |         |         |  |

| bit 7 bit                               |                                   |     |            |                                                       |         |         |         |  |

|                                         |                                   |     |            |                                                       |         |         |         |  |

| Legend:                                 |                                   |     |            |                                                       |         |         |         |  |

| R = Readable I                          | R = Readable bit W = Writable bit |     |            | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |                                   |     | NOWN       | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

#### REGISTER 24-2: DACCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

bit 7-5 **Unimplemented:** Read as '0'

1' = Bit is set

bit 4-0 DAC1R<4:0>: DAC1 Voltage Output Select bits VOUT = (VSRC+ - VSRC-)\*(DAC1R<4:0>/32) + VSRC

'0' = Bit is cleared

#### TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4               | Bit 3  | Bit 2   | Bit 1 | Bit 0   | Register<br>on page |

|---------|--------|--------|--------|---------------------|--------|---------|-------|---------|---------------------|

| DACCON0 | DAC1EN | _      | DAC10E | —                   | DAC1PS | SS<1:0> | —     | DAC1NSS | 263                 |

| DACCON1 | —      | —      | _      | DAC1R<4:0>          |        |         |       |         | 264                 |

| CMxCON1 | CxINTP | CxINTN | C>     | PCH<2:0> CxNCH<2:0> |        |         | 191   |         |                     |

| ADCON0  |        |        | CHS<   | 5:0> GO/DONE ADON   |        |         |       | 244     |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

# PIC16(L)F18325/18345

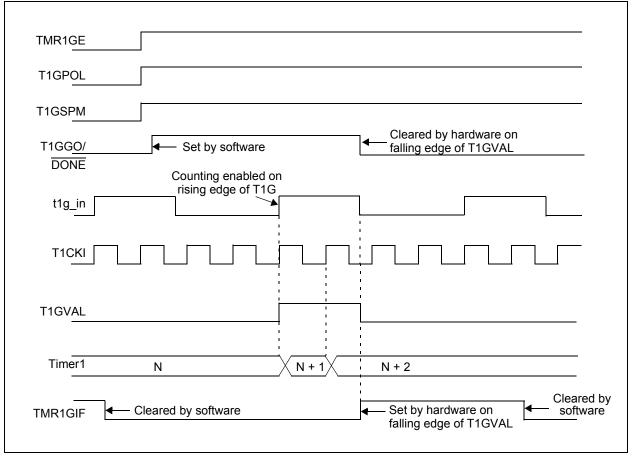

# FIGURE 27-5: TIMER1 GATE SINGLE-PULSE MODE

| Name                  | Bit 7                 | Bit 6                | Bit 5   | Bit 4           | Bit 3         | Bit 2             | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|----------------------|---------|-----------------|---------------|-------------------|--------|--------|---------------------|

| TRISA                 | _                     | —                    | TRISA5  | TRISA4          | (2)           | TRISA2            | TRISA1 | TRISA0 | 143                 |

| ANSELA                |                       | —                    | ANSA5   | ANSA4           | _             | ANSA2             | ANSA1  | ANSA0  | 144                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6               | TRISB5  | TRISB4          | _             | —                 |        | —      | 149                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                | ANSB5   | ANSB4           | _             |                   |        | —      | 150                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6(1)            | TRISC5  | TRISC4          | TRISC3        | TRISC2            | TRISC1 | TRISC0 | 156                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup> | ANSC5   | ANSC4           | ANSC3         | ANSC2             | ANSC1  | ANSC0  | 157                 |

| INTCON                | GIE                   | PEIE                 |         | _               | —             |                   | _      | INTEDG | 101                 |

| PIR1                  | TMR1GIF               | ADIF                 | RCIF    | TXIF            | SSP1IF        | BCL1IF            | TMR2IF | TMR1IF | 108                 |

| PIE1                  | TMR1GIE               | ADIE                 | RCIE    | TXIE            | SSP1IE        | BCL1IE            | TMR2IE | TMR1IE | 103                 |

| PIR3                  | OSFIF                 | CSWIF                | TMR3GIF | TMR3IF          | CLC4IF        | CLC3IF            | CLC2IF | CLC1IF | 110                 |

| PIE3                  | OSFIE                 | CSWIE                | TMR3GIE | TMR3IE          | CLC4IE        | CLC3IE            | CLC2IE | CLC1IE | 105                 |

| PIR4                  | CWG2IF                | CWG1IF               | TMR5GIF | TMR5IF          | CCP4IF        | CCP3IF            | CCP2IF | CCP1IF | 111                 |

| PIE4                  | CWG2IE                | CWG1IE               | TMR5GIE | TMR5IE          | CCP4IE        | CCP3IE            | CCP2IE | CCP1IE | 106                 |

| T1CON                 | TMR1C                 | S<1:0>               | T1CKP   | S<1:0>          | T1SOSC        | T1SYNC            | _      | TMR10N | 292                 |

| T1GCON                | TMR1GE                | T1GPOL               | T1GTM   | T1GSPM          | T1GGO/DONE    | T1GVAL T1GSS<1:0> |        |        | 293                 |

| TMR1L                 |                       | L                    |         | TMR             | 1L<7:0>       |                   |        |        | 294                 |

| TMR1H                 |                       |                      |         | TMR1H<7:0>      |               |                   |        |        |                     |

| T1CKIPPS              | _                     | _                    | —       | - T1CKIPPS<4:0> |               |                   |        |        |                     |

| T1GPPS                | _                     | —                    | _       | - T1GPPS<4:0>   |               |                   |        |        |                     |

| T3CON                 | TMR3C                 | S<1:0>               | T3CKP   | S<1:0>          | T3SOSC        | T3SYNC – TMR3ON   |        | 292    |                     |

| T3GCON                | TMR3GE                | T3GPOL               | T3GTM   | T3GSPM          | T3GGO/DONE    | T3GVAL T3GSS<1:0> |        |        | 293                 |

| TMR3L                 |                       |                      |         | TMR             | 3L<7:0>       |                   |        |        | 294                 |

| TMR3H                 |                       |                      |         | TMR             | 3H<7:0>       |                   |        |        | 294                 |