Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 18                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 20-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18345-i-gz |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name               | Function            | Input<br>Type    | Output Type | Description                                   |

|--------------------|---------------------|------------------|-------------|-----------------------------------------------|

| DUT <sup>(2)</sup> | C1                  | —                | CMOS        | Comparator C1 output.                         |

|                    | C2                  | _                | CMOS        | Comparator C2 output.                         |

|                    | NCO1                | _                | CMOS        | Numerically Controlled Oscillator output.     |

|                    | DSM                 | _                | CMOS        | Digital Signal Modulator output.              |

|                    | TMR0                | _                | CMOS        | TMR0 clock output.                            |

|                    | CCP1                | _                | CMOS        | Capture/Compare/PWM 1 output.                 |

|                    | CCP2                | _                | CMOS        | Capture/Compare/PWM 2 output.                 |

|                    | CCP3                | _                | CMOS        | Capture/Compare/PWM 3 output.                 |

|                    | CCP4                | _                | CMOS        | Capture/Compare/PWM 4 output.                 |

|                    | PWM5                | _                | CMOS        | Pulse-Width Modulator 5 output.               |

|                    | PWM6                | _                | CMOS        | Pulse-Width Modulator 6 output.               |

|                    | CWG1A               | _                | CMOS        | Complementary Waveform Generator 1 output A.  |

|                    | CWG2A               | —                | CMOS        | Complementary Waveform Generator 2 output A   |

|                    | CWG1B               | _                | CMOS        | Complementary Waveform Generator 1 output B   |

|                    | CWG2B               | _                | CMOS        | Complementary Waveform Generator 2 output B   |

|                    | CWG1C               | —                | CMOS        | Complementary Waveform Generator 1 output C   |

|                    | CWG2C               | _                | CMOS        | Complementary Waveform Generator 2 output C   |

|                    | CWG1D               | —                | CMOS        | Complementary Waveform Generator 1 output D   |

|                    | CWG2D               | —                | CMOS        | Complementary Waveform Generator 2 output D   |

|                    | SDA1 <sup>(3)</sup> | l <sup>2</sup> C | OD          | I <sup>2</sup> C data output.                 |

|                    | SDA2 <sup>(3)</sup> | l <sup>2</sup> C | OD          | I <sup>2</sup> C data output.                 |

|                    | SCL1 <sup>(3)</sup> | l <sup>2</sup> C | OD          | I <sup>2</sup> C clock output.                |

|                    | SCL2 <sup>(3)</sup> | l <sup>2</sup> C | OD          | I <sup>2</sup> C clock output.                |

|                    | SDO1                | _                | CMOS        | SPI1 data output.                             |

|                    | SD02                | _                | CMOS        | SPI2 data output.                             |

|                    | SCK1                | _                | CMOS        | SPI1 clock output.                            |

|                    | SCK2                | _                | CMOS        | SPI2 clock output.                            |

|                    | TX/CK               | _                | CMOS        | Asynchronous TX data/synchronous clock output |

|                    | DT                  | _                | CMOS        | EUSART synchronous data output.               |

|                    | CLC10UT             | _                | CMOS        | Configurable Logic Cell 1 source output.      |

|                    | CLC2OUT             | _                | CMOS        | Configurable Logic Cell 2 source output.      |

|                    | CLC3OUT             | _                | CMOS        | Configurable Logic Cell 3 source output.      |

|                    | CLC4OUT             | _                | CMOS        | Configurable Logic Cell 4 source output.      |

|                    | CLKR                | _                | CMOS        | Clock Reference output.                       |

#### TABLE 1-2: PIC16(L)F18325 PINOUT DESCRIPTION (CONTINUED)

Legend:

AN = Analog input or output

CMOS = CMOS compatible input or output

OD

= Open-Drain

TTL = TTL compatible input

ST

= Schmitt Trigger input with CMOS levels

I<sup>2</sup>C

= Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage

XTAL

= Crystal levels

I

= Schmitt Trigger input with I<sup>2</sup>C

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

**3:** These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| Address                                      | Name  | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7 | Bit 6 | Bit 5       | Bit 4         | Bit 3             | Bit 2  | Bit 1 | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------------------------------|-------|----------------------------------|-------|-------|-------------|---------------|-------------------|--------|-------|---------|-----------------------|---------------------------------|

| Bank 0                                       |       |                                  |       |       |             |               |                   |        |       |         |                       |                                 |

|                                              |       |                                  |       |       | CPU CORE RI | EGISTERS; see | Table 4-2 for spe | cifics |       |         |                       |                                 |

| 00Ch                                         | PORTA |                                  |       | _     | RA5         | RA4           | RA3               | RA2    | RA1   | RA0     | xx xxxx               | uu uuu                          |

| 00Dh                                         | PORTB | X —                              |       |       |             | Unimple       | emented           |        |       |         | _                     | —                               |

|                                              |       | — X                              | RB7   | RB6   | RB5         | RB4           | _                 | —      | _     | _       | xxxx                  | uuuu                            |

| 00Eh PORTC X – – – RC5 RC4 RC3 RC2 RC1 RC0 – |       |                                  |       |       |             |               |                   |        |       | xx xxxx | uu uuu                |                                 |

|                                              |       | — X                              | RC7   | RC6   | RC5         | RC4           | RC3               | RC2    | RC1   | RC0     | xxxx xxxx             | uuuu uuu                        |

| 00Fh                                         | —     | —                                |       |       |             | Unimple       | emented           |        |       |         | —                     | —                               |

| 010h                                         | PIR0  |                                  |       |       | TMR0IF      | IOCIF         |                   |        |       | INTF    | 000                   | 00                              |

|      |        | — X | RB7     | RB6        | RB5     | RB4      | —              | —      | —       | —       | xxxx      | uuuu      |

|------|--------|-----|---------|------------|---------|----------|----------------|--------|---------|---------|-----------|-----------|

| 00Eh | PORTC  | X — | _       | —          | RC5     | RC4      | RC3            | RC2    | RC1     | RC0     | xx xxxx   | uu uuuu   |

|      |        | — X | RC7     | RC6        | RC5     | RC4      | RC3            | RC2    | RC1     | RC0     | xxxx xxxx | uuuu uuuu |

| 00Fh | —      | -   |         |            |         | Unimple  | mented         |        |         |         | _         | —         |

| 010h | PIR0   |     | _       |            | TMR0IF  | IOCIF    | _              | _      | _       | INTF    | 000       | 000       |

| 011h | PIR1   |     | TMR1GIF | ADIF       | RCIF    | TXIF     | SSP1IF         | BCL1IF | TMR2IF  | TMR1IF  | 0000 0000 | 0000 0000 |

| 012h | PIR2   |     | TMR6IF  | C2IF       | C1IF    | NVMIF    | SSP2IF         | BCL2IF | TMR4IF  | NCO1IF  | 0000 0000 | 0000 0000 |

| 013h | PIR3   |     | OSFIF   | CSWIF      | TMR3GIF | TMR3IF   | CLC4IF         | CLC3IF | CLC2IF  | CLC1IF  | 0000 0000 | 0000 0000 |

| 014h | PIR4   |     | CWG2IF  | CWG1IF     | TMR5GIF | TMR5IF   | CCP4IF         | CCP3IF | CCP2IF  | CCP1IF  | 0000 0000 | 0000 0000 |

| 015h | TMR0L  |     |         | TMR0L<7:0> |         |          |                |        |         |         | xxxx xxxx | xxxx xxxx |

| 016h | TMR0H  |     |         | TMR0H<7:0> |         |          |                |        |         |         | 1111 1111 | 1111 1111 |

| 017h | T0CON0 |     | T0EN    |            | TOOUT   | T016BIT  |                | TOOUTI | PS<3:0> |         | 0-00 0000 | 0-00 0000 |

| 018h | T0CON1 |     |         | T0CS<2:0>  |         | TOASYNC  |                | TOCKP  | S<3:0>  |         | 0000 0000 | 0000 0000 |

| 019h | TMR1L  |     |         |            |         | TMR1I    | _<7:0>         |        |         |         | xxxx xxxx | uuuu uuuu |

| 01Ah | TMR1H  |     |         |            |         | TMR1     | H<7:0>         |        |         |         | xxxx xxxx | uuuu uuuu |

| 01Bh | T1CON  |     | TMR1CS  | 6<1:0>     | T1CKF   | PS<1:0>  | T1SOSC         | T1SYNC | _       | TMR10N  | 0000 00-0 | uuuu uu-u |

| 01Ch | T1GCON |     | TMR1GE  | T1GPOL     | T1GTM   | T1GSPM   | T1GGO/<br>DONE | T1GVAL | T1GS    | S<1:0>  | 00x0 0x00 | uuuu uxuu |

| 01Dh | TMR2   |     |         | TMR2<7:0>  |         |          |                |        |         |         | 0000 0000 | 0000 0000 |

| 01Eh | PR2    |     |         | PR2<7:0>   |         |          |                |        |         |         | 1111 1111 | 1111 1111 |

| 01Fh | T2CON  |     | _       |            | T2OU    | TPS<3:0> |                | TMR2ON | T2CKF   | PS<1:0> | -000 0000 | -000 0000 |

Legend:

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note

1:

Only on PIC16F18325/18345.

2:

Register accessible from both User and ICD Debugger.

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|------------|----------------------------------------------------------|

|------------|----------------------------------------------------------|

| Address | Name                                            | PIC16(L)F18325<br>PIC16(L)F18345 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------------------------------------------|----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| Bank 1  |                                                 |                                  |       |       |       |       |       |       |       |       |                       |                                 |

|         | CPU CORE REGISTERS; see Table 4-2 for specifics |                                  |       |       |       |       |       |       |       |       |                       |                                 |

| Resets    | 6(                           |

|-----------|------------------------------|

|           |                              |

|           |                              |

| 11 -111   |                              |

|           | 8325/                        |

| 1111      | Ň                            |

| 11 1111   | 5                            |

| 1111 1111 | $\mathbf{\Sigma}$            |

| _         | $\overline{\mathbf{\omega}}$ |

| 000       | 83                           |

| 0000 0000 | 4                            |

| 0000 0000 | ្រ                           |

| 0000 0000 |                              |

| 0000 0000 |                              |

| _         |                              |

| —         |                              |

PIC1

| _ | TRISA5 | TRISA4   | _      | TRISA2 |  |

|---|--------|----------|--------|--------|--|

|   |        | Linimple | mented |        |  |

| 08Ch | TRISA  |   |   | —       | _                                                         | TRISA5    | TRISA4  | _          | TRISA2     | TRISA1  | TRISA0    | 11 -111   | 11 -111   |

|------|--------|---|---|---------|-----------------------------------------------------------|-----------|---------|------------|------------|---------|-----------|-----------|-----------|

| 08Dh | TRISB  | Х | _ |         |                                                           |           | Unimple | mented     |            |         |           | —         | —         |

|      |        |   | Х | TRISB7  | TRISB6                                                    | TRISB5    | TRISB4  | _          | _          | _       |           | 1111      | 1111      |

| 08Eh | TRISC  | Х | _ | —       | —                                                         | TRISC5    | TRISC4  | TRISC3     | TRISC2     | TRISC1  | TRISC0    | 11 1111   | 11 1111   |

|      |        |   | Х | TRISC7  | TRISC6                                                    | TRISC5    | TRISC4  | TRISC3     | TRISC2     | TRISC1  | TRISC0    | 1111 1111 | 1111 1111 |

| 08Fh | —      | - | - |         |                                                           |           | Unimple | mented     |            |         |           | —         | _         |

| 090h | PIE0   |   |   | —       | —                                                         | TMR0IE    | IOCIE   | —          | —          | —       | INTE      | 000       | 000       |

| 091h | PIE1   |   |   | TMR1GIE | ADIE                                                      | RCIE      | TXIE    | SSP1IE     | BCL1IE     | TMR2IE  | TMR1IE    | 0000 0000 | 0000 0000 |

| 092h | PIE2   |   |   | TMR6IE  | C2IE                                                      | C1IE      | NVMIE   | SSP2IE     | BCL2IE     | TMR4IE  | NCO1IE    | 0000 0000 | 0000 0000 |

| 093h | PIE3   |   |   | OSFIE   | CSWIE                                                     | TMR3GIE   | TMR3IE  | CLC4IE     | CLC3IE     | CLC2IE  | CLC1IE    | 0000 0000 | 0000 0000 |

| 094h | PIE4   |   |   | CWG2IE  | WG2IE CWG1IE TMR5GIE TMR5IE CCP4IE CCP3IE CCP2IE CCP1IE C |           |         |            |            |         | 0000 0000 | 0000 0000 |           |

| 095h | —      | - | - |         | Unimplemented                                             |           |         |            |            |         | _         | _         |           |

| 096h | —      | - | - |         |                                                           |           | Unimple | mented     |            |         |           | —         | _         |

| 097h | WDTCON |   |   | _       | —                                                         |           |         | WDTPS<4:0> |            |         | SWDTEN    | 01 0110   | 01 0110   |

| 098h | —      | - | - |         |                                                           |           | Unimple | mented     |            |         |           | —         | _         |

| 099h | —      | - | - |         |                                                           |           | Unimple | mented     |            |         |           | —         | _         |

| 09Ah | —      | - | - |         |                                                           |           | Unimple | mented     |            |         |           | —         | _         |

| 09Bh | ADRESL |   |   |         |                                                           |           | ADRES   | L<7:0>     |            |         |           | xxxx xxxx | uuuu uuuu |

| 09Ch | ADRESH |   |   |         |                                                           |           | ADRES   | H<7:0>     |            |         |           | xxxx xxxx | uuuu uuuu |

| 09Dh | ADCON0 |   |   |         |                                                           | CHS       | <5:0>   |            |            | GO/DONE | ADON      | 0000 0000 | 0000 0000 |

| 09Eh | ADCON1 |   |   | ADFM    |                                                           | ADCS<2:0> |         | _          | ADNREF     | ADPRE   | F<1:0>    | 0000 -000 | 0000 -000 |

| 09Fh | ADACT  |   |   | _       | —                                                         | —         |         |            | ADACT<4:0> | •       |           | 0 0000    | 0 0000    |

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

Only on PIC16F18325/18345. Note 1:

2: Register accessible from both User and ICD Debugger.

## 5.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory are controlled independently. Internal access to the program memory is unaffected by any code protection setting.

#### 5.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Self-write writing the program memory is dependent upon the write protection setting. See **Section 5.4** "Write **Protection**" for more information.

#### 5.3.2 DATA MEMORY PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit in the Configuration Words. When CPD = 0, external reads and writes of EEPROM memory are inhibited and a read will return all '0's. The CPU can continue to read and write EEPROM memory, regardless of the protection bit settings.

## 5.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 5.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 11.4.7 "NVMREG EEPROM, User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16(L)F183XX Memory Programming Specification"* (DS40001738).

## 5.6 Device ID and Revision ID

The 14-bit device ID word is located at 8006h and the 14-bit revision ID is located at 8005h. These locations are read-only and cannot be erased or modified. See **Section 11.4.7 "NVMREG EEPROM, User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

| Name     | Bit 7   | Bit 6   | Bit 5      | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 | Register<br>on Page |

|----------|---------|---------|------------|-------|--------|-------|--------|-------|---------------------|

| OSCCON1  |         | N       | OSC<2:0>   |       |        | NDIV  | <3:0>  |       | 90                  |

| OSCCON2  | —       | C       | OSC<2:0>   |       |        | CDIV  | <3:0>  |       | 90                  |

| OSCCON3  | CWSHOLD | SOSCPWR | SOSCBE     | ORDY  | NOSCR  | _     | _      | _     | 91                  |

| OSCSTAT1 | EXTOR   | HFOR    | —          | LFOR  | SOR    | ADOR  | —      | PLLR  | 92                  |

| OSCEN    | EXTOEN  | HFOEN   | _          | LFOEN | SOSCEN | ADOEN | _      | _     | 93                  |

| OSCFRQ   | _       | _       | _          | _     |        | HFFRC | Q<3:0> |       | 94                  |

| OSCTUNE  |         |         | HFTUN<5:0> |       |        |       |        | 95    |                     |

## TABLE 7-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 7-4:SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|----------|----------|---------------------|

|         | 13:8 |         | _       | FCMEN    |          | CSWEN    |          |          | CLKOUTEN |                     |

| CONFIG1 | 7:0  | _       | RSTOSC2 | RSTOSC1  | RSTOSC0  | _        | FEXTOSC2 | FEXTOSC1 | FEXTOSC0 | 64                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

# PIC16(L)F18325/18345

| TADLE 9-1.             | SUMMART OF REGISTERS ASSOCIATED WITH FOWER-DOWN MODE |                       |         |        |          |        |        |        |                     |  |

|------------------------|------------------------------------------------------|-----------------------|---------|--------|----------|--------|--------|--------|---------------------|--|

| Name                   | Bit 7                                                | Bit 6                 | Bit 5   | Bit 4  | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

| INTCON                 | GIE                                                  | PEIE                  |         | —      | —        |        |        | INTEDG | 101                 |  |

| PIE0                   | _                                                    | _                     | TMR0IE  | IOCIE  | —        | _      | _      | INTE   | 102                 |  |

| PIE1                   | TMR1GIE                                              | ADIE                  | RCIE    | TXIE   | SSP1IE   | BCL1IE | TMR2IE | TMR1IE | 103                 |  |

| PIE2                   | TMR6IE                                               | C2IE                  | C1IE    | NVMIE  | SSP2IE   | BCL2IE | TMR4IE | NCO1IE | 104                 |  |

| PIE3                   | OSFIE                                                | CSWIE                 | TMR3GIE | TMR3IE | CLC4IE   | CLC3IE | CLC2IE | CLC1IE | 105                 |  |

| PIE4                   | CWG2IE                                               | CWG1IE                | TMR5GIE | TMR5IE | CCP4IE   | CCP3IE | CCP2IE | CCP1IE | 106                 |  |

| PIR0                   | _                                                    | _                     | TMR0IF  | IOCIF  | —        | _      |        | INTF   | 107                 |  |

| PIR1                   | TMR1GIF                                              | ADIF                  | RCIF    | TXIF   | SSP1IF   | BCL1IF | TMR2IF | TMR1IF | 108                 |  |

| PIR2                   | TMR6IF                                               | C2IF                  | C1IF    | NVMIF  | SSP2IF   | BCL2IF | TMR4IF | NCO1IF | 109                 |  |

| PIR3                   | OSFIF                                                | CSWIF                 | TMR3GIF | TMR3IF | CLC4IF   | CLC3IF | CLC2IF | CLC1IF | 110                 |  |

| PIR4                   | CWG2IF                                               | CWG1IF                | TMR5GIF | TMR5IF | CCP4IF   | CCP3IF | CCP2IF | CCP1IF | 111                 |  |

| IOCAP                  | _                                                    |                       | IOCAP5  | IOCAP4 | IOCAP3   | IOCAP2 | IOCAP1 | IOCAP0 | 174                 |  |

| IOCAN                  | _                                                    |                       | IOCAN5  | IOCAN4 | IOCAN3   | IOCAN2 | IOCAN1 | IOCAN0 | 174                 |  |

| IOCAF                  | _                                                    |                       | IOCAF5  | IOCAF4 | IOCAF3   | IOCAF2 | IOCAF1 | IOCAF0 | 175                 |  |

| IOCBP <sup>(1)</sup>   | IOCBP7                                               | IOCBP6                | IOCBP5  | IOCBP4 | —        | _      | _      | -      | 175                 |  |

| IOCBN <sup>(1)</sup>   | IOCBN7                                               | IOCBN6                | IOCBN5  | IOCBN4 | —        | _      | _      | -      | 176                 |  |

| IOCBF <sup>(1)</sup>   | IOCBF7                                               | IOCBF6                | IOCBF5  | IOCBF4 | —        | _      | _      | -      | 176                 |  |

| IOCCP                  | IOCCP7 <sup>(1)</sup>                                | IOCCP6 <sup>(1)</sup> | IOCCP5  | IOCCP4 | IOCCP3   | IOCCP2 | IOCCP1 | IOCCP0 | 177                 |  |

| IOCCN                  | IOCCN7 <sup>(1)</sup>                                | IOCCN6 <sup>(1)</sup> | IOCCN5  | IOCCN4 | IOCCN3   | IOCCN2 | IOCCN1 | IOCCN0 | 177                 |  |

| IOCCF                  | IOCCF7 <sup>(1)</sup>                                | IOCCF6 <sup>(1)</sup> | IOCCF5  | IOCCF4 | IOCCF3   | IOCCF2 | IOCCF1 | IOCCF0 | 178                 |  |

| STATUS                 | _                                                    | _                     | —       | TO     | PD       | Z      | DC     | С      | 30                  |  |

| VREGCON <sup>(2)</sup> | —                                                    | —                     | —       | —      | —        | —      | VREGPM | —      | 117                 |  |

| CPUDOZE                | IDLEN                                                | DOZEN                 | ROI     | DOE    | —        |        | 117    |        |                     |  |

| WDTCON                 | _                                                    |                       |         | V      | VDTPS<4: | 0>     |        | SWDTEN | 121                 |  |

## TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

**Note 1:** PIC16(L)F18345 only.

**2:** PIC16F18325/18345 only.

## 12.0 I/O PORTS

TABLE 12-1: PORT AVAILABILITY PER DEVICE

| DEMO           | _     | -     | _     |

|----------------|-------|-------|-------|

| Device         | PORTA | PORTB | РОКТС |

| PIC16(L)F18325 | ٠     |       | •     |

| PIC16(L)F18345 | ٠     | •     | ٠     |

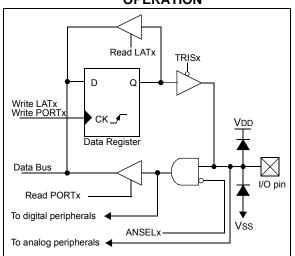

Each port has ten standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- · ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- · SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

## 12.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 13.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

| R/W-x/u                                 | R/W-x/u | R/W-x/u                            | R/W-x/u       | U-0              | U-0         | U-0 | U-0   |

|-----------------------------------------|---------|------------------------------------|---------------|------------------|-------------|-----|-------|

| LATB7                                   | LATB6   | LATB5                              | LATB4         | —                | —           | —   | —     |

| bit 7                                   |         |                                    |               |                  |             |     | bit 0 |

|                                         |         |                                    |               |                  |             |     |       |

| Legend:                                 |         |                                    |               |                  |             |     |       |

| R = Readable bit W = Writable bit       |         | U = Unimplemented bit, read as '0' |               |                  |             |     |       |

| u = Bit is unchanged x = Bit is unknown |         | -n/n = Value a                     | at POR and BO | R/Value at all o | ther Resets |     |       |

| '1' = Bit is set '0' = Bit is cleared   |         | ared                               |               |                  |             |     |       |

#### REGISTER 12-11: LATB: PORTB DATA LATCH REGISTER

bit 7-4 LATB<7:4>: RB<5:4> Output Latch Value bits<sup>(1)</sup>

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to LATB are equivalent with writes to the corresponding PORTB register.Reads from LATB register return register values, not I/O pin values.

#### REGISTER 12-12: ANSELB: PORTB ANALOG SELECT REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| ANSB7   | ANSB6   | ANSB5   | ANSB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 ANSB<7:4>: Analog Select between Analog or Digital Function 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

#### bit 3-0 Unimplemented: Read as '0'

**Note 1:** Setting ANSB[n] = 1 disables the digital input circuitry. Weak pull-ups, if available, are unaffected. The corresponding TRIS bit must be set to Input mode by the user to allow external control of the voltage on the pin.

## 18.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 18-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- · Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 18-2) contains Control bits for the following:

- · Interrupt on positive/negative edge enables

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 13-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

## 18.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-2 shows the output state versus input conditions, including polarity control.

#### TABLE 18-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

## 18.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See Comparator Specifications in Table 35-14 for more information.

## 18.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 27.5** "**Timer1 Gate**" for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 18.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from a comparator can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. This allows the timer/counter to synchronize with the CxOUT bit so that the software sees no ambiguity due to timing. See the Comparator Block Diagram (Figure 18-2) and the Timer1 Block Diagram (Figure 27-1) for more information.

## 24.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC1) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DAC1OUT pin

The Digital-to-Analog Converter (DAC) is enabled by setting the DAC1EN bit of the DAC1CON0 register.

## EQUATION 24-1: DAC OUTPUT VOLTAGE

#### 24.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DAC1R<4:0> bits of the DAC1CON1 register.

The DAC output voltage is determined by Equation 24-1:

$$V_{OUT} = \left( \left( V_{SOURCE+} - V_{SOURCE-} \right) \times \frac{DAC1R\langle 4:0 \rangle}{2^5} \right) + \left( V_{SOURCE-} \right)$$

$$V_{SOURCE+} = V_{DD} \text{ or } V_{REF+} \text{ or } FVR$$

$$V_{SOURCE-} = V_{SS} \text{ or } V_{REF-}$$

## 24.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Table 35-15.

## 24.3 DAC Voltage Reference Output

The DAC voltage can be output to the DAC1OUT pin by setting the DAC1OE bit of the DAC1CON0 register. Selecting the DAC reference voltage for output on the DAC1OUT pin automatically overrides the digital output buffer and digital input threshold detector functions, it disables the weak pull-up and the constant-current drive function of that pin. Reading the DAC1OUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to the DAC1OUT pin. Figure 24-2 shows an example buffering technique.

© 2015-2016 Microchip Technology Inc.

#### 29.2.2 TIMER1/3/5 MODE RESOURCE

Timer1/3/5 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 27.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1/3/5.

**Note:** Clocking Timer1/3/5 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1/3/5 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 29.2.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE4 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR4 register following any change in Operating mode.

## 29.2.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

#### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

|         |             |                         |

## 29.2.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1/3/5 module for proper operation. There are two options for driving the Timer1/3/5 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1/3/5 is clocked by Fosc/4, Timer1/3/5 will not increment during Sleep. When the device wakes from Sleep, Timer1/3/5 will continue from its previous state.

Capture mode will operate during Sleep when Timer1/3/5 is clocked by an external clock source.

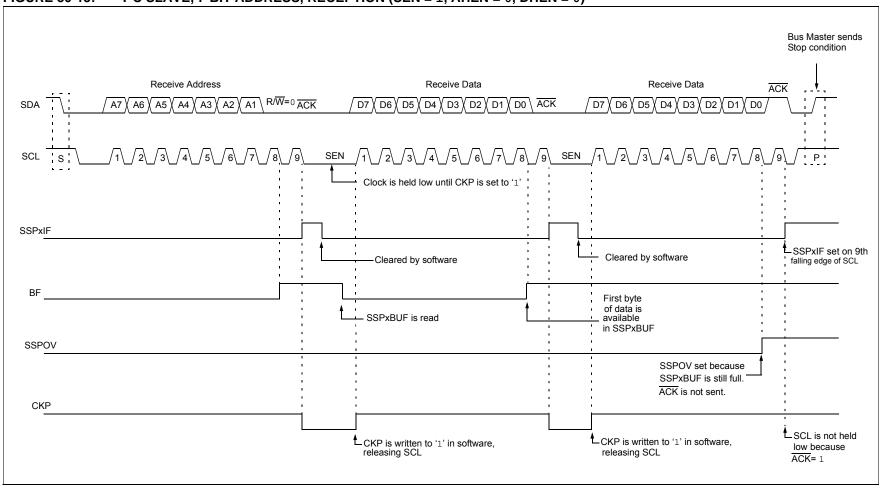

## FIGURE 30-15: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 1, AHEN = 0, DHEN = 0)

© 2015-2016 Microchip Technology Inc

Preliminary

PIC16(L)F18325/18345

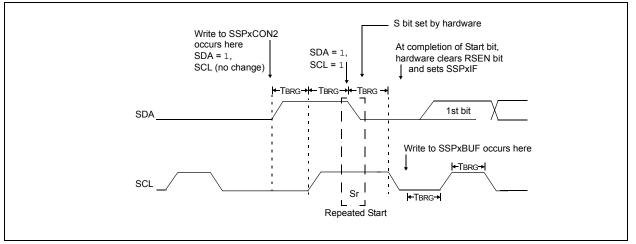

## 30.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 30-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

**Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## FIGURE 30-27: REPEATED START CONDITION WAVEFORM

| R-0/0                 | R/W-0/0                                                                                       | R/W-0/0                                                                                                                                                                                                                                                      | R/W-0/0                       | R/W-0/0                     | R/W-0/0                               | R/W-0/0          | R/W-0/0        |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|---------------------------------------|------------------|----------------|--|--|--|

| ACKTIM <sup>(3)</sup> | PCIE                                                                                          | SCIE                                                                                                                                                                                                                                                         | BOEN                          | SDAHT                       | SBCDE                                 | AHEN             | DHEN           |  |  |  |

| bit 7                 |                                                                                               |                                                                                                                                                                                                                                                              |                               |                             |                                       |                  | bit (          |  |  |  |

|                       |                                                                                               |                                                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

| Legend:               |                                                                                               |                                                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

| R = Readable          | bit                                                                                           | W = Writable                                                                                                                                                                                                                                                 | bit                           | U = Unimpler                | mented bit, read                      | l as '0'         |                |  |  |  |

| u = Bit is unch       | nanged                                                                                        | x = Bit is unk                                                                                                                                                                                                                                               | nown                          | -n/n = Value                | at POR and BO                         | R/Value at all c | ther Resets    |  |  |  |

| '1' = Bit is set      |                                                                                               | '0' = Bit is cle                                                                                                                                                                                                                                             | ared                          |                             |                                       |                  |                |  |  |  |

| bit 7                 | ACKTIM: Ac                                                                                    | knowledge Tim                                                                                                                                                                                                                                                | ie Status bit (I <sup>2</sup> | C mode only)                | 3)                                    |                  |                |  |  |  |

|                       | 1 = Indicates                                                                                 | the I <sup>2</sup> C bus is                                                                                                                                                                                                                                  | in an Acknowle                | edge sequenc                | e, set on eighth<br>ng edge of SCL    |                  | SCL clock      |  |  |  |

| bit 6                 | PCIE: Stop C                                                                                  | Condition Interru                                                                                                                                                                                                                                            | upt Enable bit (              | I <sup>2</sup> C mode only  | /)                                    |                  |                |  |  |  |

|                       |                                                                                               | nterrupt on dete                                                                                                                                                                                                                                             |                               |                             |                                       |                  |                |  |  |  |

| bit 5                 | SCIE: Start C                                                                                 | Condition Interro                                                                                                                                                                                                                                            | upt Enable bit (              | (I <sup>2</sup> C mode only | ()                                    |                  |                |  |  |  |

|                       |                                                                                               | nterrupt on dete                                                                                                                                                                                                                                             |                               |                             | litions                               |                  |                |  |  |  |

| bit 4                 |                                                                                               | er Overwrite En                                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

|                       | In SPI Slave                                                                                  | In SPI Slave mode: <sup>(1)</sup>                                                                                                                                                                                                                            |                               |                             |                                       |                  |                |  |  |  |

|                       | 1 = SSPBUF updates every time that a new data byte is shifted in ignoring the BF bit          |                                                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

|                       | 0 = If new byte is received with BF bit of the SSPSTAT register already set, SSPOV bit of the |                                                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

|                       |                                                                                               | SSPCON1 register is set, and the buffer is not updated <u>Master mode and SPI Master mode:</u>                                                                                                                                                               |                               |                             |                                       |                  |                |  |  |  |

|                       |                                                                                               | s ignored.                                                                                                                                                                                                                                                   |                               | <u>.</u>                    |                                       |                  |                |  |  |  |

|                       | In I <sup>2</sup> C Slave                                                                     |                                                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

|                       |                                                                                               |                                                                                                                                                                                                                                                              | l and ACK is ge               | enerated for a r            | eceived addres                        | s/data byte, ign | oring the stat |  |  |  |

|                       |                                                                                               | e SSPOV bit o<br>BUF is only up                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

| bit 3                 | SDAHT: SDA                                                                                    | A Hold Time Se                                                                                                                                                                                                                                               | lection bit (I <sup>2</sup> C | mode only)                  |                                       |                  |                |  |  |  |

|                       |                                                                                               | n of 300 ns hold<br>n of 100 ns hold                                                                                                                                                                                                                         |                               |                             |                                       |                  |                |  |  |  |

| bit 2                 | SBCDE: Sla                                                                                    | ve Mode Bus C                                                                                                                                                                                                                                                | Collision Detect              | Enable bit (I <sup>2</sup>  | C Slave mode c                        | only)            |                |  |  |  |

|                       |                                                                                               | ing edge of SC<br>f the PIR1 regis                                                                                                                                                                                                                           |                               |                             | n the module is                       | s outputting a l | nigh state, th |  |  |  |

|                       |                                                                                               | lave bus collisions inter                                                                                                                                                                                                                                    |                               | led                         |                                       |                  |                |  |  |  |

| bit 1                 |                                                                                               |                                                                                                                                                                                                                                                              | -                             |                             |                                       |                  |                |  |  |  |

|                       | 1 = Followin                                                                                  | <ul> <li>AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)</li> <li>1 = Following the eighth falling edge of SCL for a matching received address byte; CKP bit of the SSPCON1 register will be cleared and the SCL will be held low.</li> </ul> |                               |                             |                                       |                  |                |  |  |  |

|                       | 0 = Address holding is disabled                                                               |                                                                                                                                                                                                                                                              |                               |                             |                                       |                  |                |  |  |  |

| bit 0                 | DHEN: Data                                                                                    | Hold Enable bi                                                                                                                                                                                                                                               | it (I <sup>2</sup> C Slave m  | ode only)                   |                                       |                  |                |  |  |  |

|                       | bit of the                                                                                    | g the eighth fall<br>SSPCON1 reg<br>ding is disabled                                                                                                                                                                                                         | gister and SCL                |                             | ed data byte; sla                     | ave hardware c   | lears the CK   |  |  |  |

| wh                    | en a new byte i                                                                               | is received and                                                                                                                                                                                                                                              | BF = 1, but ha                | rdware continu              | but the last rece<br>ues to write the | most recent by   | te to SSPBUR   |  |  |  |

|                       |                                                                                               | us bit is only ac                                                                                                                                                                                                                                            |                               | -                           | dition detection<br>HEN bit is set.   |                  |                |  |  |  |

## REGISTER 30-4: SSPxCON3: SSP CONTROL REGISTER 3

| R/W-1/1                               | R/W-1/1                                                                                          | R/W-1/1                                                                         | R/W-1/1       | R/W-1/1                                       | R/W-1/1                         | R/W-1/1       | R/W-1/1 |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------|-----------------------------------------------|---------------------------------|---------------|---------|--|--|

|                                       |                                                                                                  |                                                                                 | SSPxN         | /ISK<7:0>                                     |                                 |               |         |  |  |

| bit 7                                 |                                                                                                  |                                                                                 |               |                                               |                                 |               | bit 0   |  |  |

| Legend:                               |                                                                                                  |                                                                                 |               |                                               |                                 |               |         |  |  |

| R = Readable bit V                    |                                                                                                  | W = Writable                                                                    | bit           | U = Unimpler                                  | mented bit, read                | l as '0'      |         |  |  |

| u = Bit is unchanged x                |                                                                                                  | x = Bit is unk                                                                  | nown          | -n/n = Value at POR and BOR/Value at all othe |                                 | other Resets  |         |  |  |

| '1' = Bit is set '0' = Bit is cleared |                                                                                                  | ared                                                                            |               |                                               |                                 |               |         |  |  |

|                                       |                                                                                                  |                                                                                 |               |                                               |                                 |               |         |  |  |

| bit 7-1                               |                                                                                                  | 7:1>: Mask bits                                                                 |               |                                               |                                 |               |         |  |  |

|                                       | 1 = The rec                                                                                      | eived address b                                                                 | it n is compa | red to SSPADD                                 | <n> to detect I<sup>2</sup></n> | C address mat | ch      |  |  |

|                                       | 0 = The rec                                                                                      | The received address bit n is not used to detect I <sup>2</sup> C address match |               |                                               |                                 |               |         |  |  |

| bit 0                                 | SSPxMSK<0>: Mask bit for I <sup>2</sup> C Slave mode, 10-bit Address                             |                                                                                 |               |                                               |                                 |               |         |  |  |

|                                       | <u>I<sup>2</sup>C Slave mode, 10-bit address (SSPM&lt;3:0&gt; = 0111 or 1111):</u>               |                                                                                 |               |                                               |                                 |               |         |  |  |

|                                       | 1 = The received address bit 0 is compared to SSPADD<0> to detect I <sup>2</sup> C address match |                                                                                 |               |                                               |                                 |               |         |  |  |

|                                       |                                                                                                  | eived address b                                                                 |               |                                               |                                 |               |         |  |  |

|                                       | I <sup>2</sup> C Slave mode, 7-bit address:                                                      |                                                                                 |               |                                               |                                 |               |         |  |  |

|                                       |                                                                                                  |                                                                                 |               |                                               |                                 |               |         |  |  |

#### REGISTER 30-5: SSPxMSK: SSP MASK REGISTER

| REGISTER 30-6 | SSPYADD MSSP ADDRESS AND BAUD RATE REGISTER (1 <sup>2</sup> C | (MODF) |

|---------------|---------------------------------------------------------------|--------|

| REGISTER 3                        | 0-6: 33PX                | add: M35P F | ADDRESS A                          | ND BAUD RA                                            | ATE REGISTI |         | )<br>)  |

|-----------------------------------|--------------------------|-------------|------------------------------------|-------------------------------------------------------|-------------|---------|---------|

| R/W-0/0                           | R/W-0/0                  | R/W-0/0     | R/W-0/0                            | R/W-0/0                                               | R/W-0/0     | R/W-0/0 | R/W-0/0 |

|                                   |                          |             | SSPxAD                             | )D<7:0>                                               |             |         |         |

| bit 7                             |                          |             |                                    |                                                       |             |         | bit 0   |

|                                   |                          |             |                                    |                                                       |             |         |         |

| Legend:                           |                          |             |                                    |                                                       |             |         |         |

| R = Readable bit W = Writable bit |                          | oit         | U = Unimplemented bit, read as '0' |                                                       |             |         |         |

| u = Bit is unch                   | anged x = Bit is unknown |             | own                                | -n/n = Value at POR and BOR/Value at all other Resets |             |         |         |

#### Master mode:

'1' = Bit is set

| bit 7-0 | SSPxADD<7:0>: Baud Rate Clock Divider bits      |

|---------|-------------------------------------------------|

|         | SCL pin clock period = ((ADD<7:0> + 1) *4)/Fosc |

#### 10-bit Slave mode – Most Significant Address Byte:

MSK0 bit is ignored.

- bit 7-3 **Not used:** Unused for Most Significant Address Byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 SSPxADD<2:1>: Two Most Significant bits of 10-bit address

'0' = Bit is cleared

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 10-bit Slave mode – Least Significant Address Byte:

bit 7-0 SSPxADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-bit Slave mode:

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

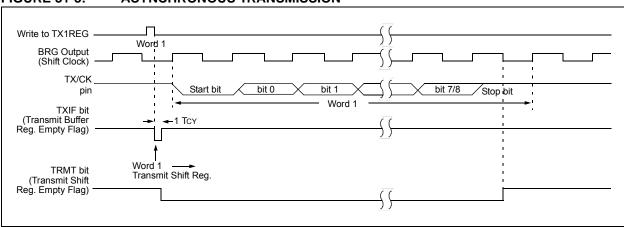

## 31.1.1.5 TSR Status

The TRMT bit of the TX1STA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TX1REG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 31.1.1.6 Transmitting 9-bit Characters

The EUSART1 supports 9-bit character transmissions. When the TX9 bit of the TX1STA register is set, the EUSART1 will shift nine bits out for each character transmitted. The TX9D bit of the TX1STA register is the ninth, and Most Significant data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TX1REG. All nine bits of data will be transferred to the TSR shift register immediately after the TX1REG is written.

A special 9-bit Address mode is available for use with multiple receivers. See **Section 31.1.2.7** "Address **Detection**" for more information on the Address mode.

#### 31.1.1.7 Asynchronous Transmission Set-up

- Initialize the SP1BRGH, SP1BRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 31.3 "EUSART1 Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- 4. Set SCKP bit if inverted transmit is desired.

- 5. Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 8. Load 8-bit data into the TX1REG register. This will start the transmission.

#### FIGURE 31-3: ASYNCHRONOUS TRANSMISSION

## 37.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- MPLAB Xpress IDE Software

- Microchip Code Configurator (MCC)

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer