#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 18                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 20-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf18345-i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER       | R 5-3: CONF                                                                                         | -IGURATION                       | WORD 3: M | EMORY         |                  |              |            |

|----------------|-----------------------------------------------------------------------------------------------------|----------------------------------|-----------|---------------|------------------|--------------|------------|

|                |                                                                                                     | R/P-1                            | U-1       | U-1           | U-1              | U-1          | U-1        |

|                |                                                                                                     | LVP <sup>(1)</sup>               | —         | —             | —                | _            | —          |

|                |                                                                                                     | bit 13                           |           |               |                  |              | bit 8      |

|                |                                                                                                     |                                  |           |               |                  |              |            |

| U-1            | U-1                                                                                                 | U-1                              | U-1       | U-1           | U-1              | R/P-1        | R/P-1      |

| _              | —                                                                                                   | —                                | —         | —             | _                | WRT1         | WRT0       |

| bit 7          |                                                                                                     |                                  |           |               |                  |              | bit 0      |

|                |                                                                                                     |                                  |           |               |                  |              |            |

| Legend:        |                                                                                                     |                                  |           |               |                  |              |            |

| R = Readal     | ble bit                                                                                             | P = Programn                     | nable bit | U = Unimplem  | nented bit, read | as '1'       |            |

| '0' = Bit is c | leared                                                                                              | '1' = Bit is set                 |           | n = Value whe | en blank or afte | r Bulk Erase |            |

|                |                                                                                                     |                                  |           |               |                  |              |            |

| bit 13         |                                                                                                     | ltage Programn                   |           |               |                  |              |            |

|                | 1 = ON Low-Voltage Programming is enabled. MCLR/VPP pin function is MCLR. MCLRE                     |                                  |           |               |                  |              |            |

|                |                                                                                                     | onfiguration bit<br>V on MCLR/VP |           | for programm  | ina              |              |            |

| bit 12-2       |                                                                                                     | ted: Read as '                   |           |               | ing.             |              |            |

| bit 1-0        | -                                                                                                   | Jser NVM Self-                   |           | n hita        |                  |              |            |

| DIL 1-0        |                                                                                                     | Write protectio                  |           | IT DILS       |                  |              |            |

|                | 10 = BOOT 0000h to 01FFh write-protected, 0200h to 1FFFh may be modified                            |                                  |           |               |                  |              |            |

|                | 01 = HALF 0000h to 0FFFh write-protected, 1000h to 1FFFh may be modified                            |                                  |           |               |                  |              |            |

|                | 01 = ALL 0000h to 1FFFh write-protected, no addresses may be modified                               |                                  |           |               |                  |              |            |

|                |                                                                                                     |                                  |           |               |                  |              | protected. |

| Note 1.        | WRT applies only to the self-write feature of the device; writing through ICSP™ is never protected. |                                  |           |               |                  |              |            |

#### **REGISTER 5-3: CONFIGURATION WORD 3: MEMORY**

Note 1: The LVP bit cannot be programmed to '0' when Programming mode is entered via LVP.

## 6.13 Register Definitions: Power Control

| R/W/HS-0/q       | R/W/HS-0/q                                                                                                                                                           | U-0                             | R/W/HC-1/q             | R/W/HC-1/q      | R/W/HC-1/q       | R/W/HC-q/u      | R/W/HC-q/u   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------|-----------------|------------------|-----------------|--------------|

| STKOVF           | STKUNF                                                                                                                                                               | —                               | RWDT                   | RMCLR           | RI               | POR             | BOR          |

| bit 7            |                                                                                                                                                                      |                                 |                        |                 |                  |                 | bit C        |

|                  |                                                                                                                                                                      |                                 |                        |                 |                  |                 |              |

| Legend:          |                                                                                                                                                                      |                                 |                        |                 |                  |                 |              |

| HC = Bit is clea | ared by hardwa                                                                                                                                                       | are                             |                        | HS = Bit is se  | et by hardware   |                 |              |

| R = Readable     | bit                                                                                                                                                                  | W = Writable                    | bit                    | U = Unimpler    | nented bit, read | l <b>as</b> '0' |              |

| u = Bit is uncha | anged                                                                                                                                                                | x = Bit is unk                  | nown                   | -m/n = Value    | at POR and BC    | R/Value at all  | other Resets |

| '1' = Bit is set |                                                                                                                                                                      | '0' = Bit is cle                | eared                  | q = Value dep   | pends on condit  | ion             |              |

| bit 7            |                                                                                                                                                                      | ack Overflow F<br>Overflow occu | -                      |                 |                  |                 |              |

|                  |                                                                                                                                                                      |                                 |                        | has been clea   | red by firmware  | ;               |              |

| bit 6            |                                                                                                                                                                      | ck Underflow                    |                        |                 |                  |                 |              |

|                  | 1 = A Stack Underflow occurred                                                                                                                                       |                                 |                        |                 |                  |                 |              |

|                  |                                                                                                                                                                      |                                 |                        | r has been cle  | ared by firmwa   | re              |              |

| bit 5            | Unimplemen                                                                                                                                                           | ted: Read as                    | '0'                    |                 |                  |                 |              |

| bit 4            | 1 = A Watcho                                                                                                                                                         |                                 | set has not occ        |                 | '1' by firmware  |                 |              |

|                  |                                                                                                                                                                      |                                 | set has occurre        | d (cleared by h | hardware)        |                 |              |

| bit 3            |                                                                                                                                                                      | LR Reset Flag                   | bit<br>toccurred or se | tto (1) by firm | wara             |                 |              |

|                  |                                                                                                                                                                      |                                 | curred (cleared        |                 | ware             |                 |              |

| bit 2            |                                                                                                                                                                      | struction Flag                  | -                      | ,<br>,          |                  |                 |              |

|                  | <ul> <li>1 = A RESET instruction has not been executed or set to '1' by firmware</li> <li>0 = A RESET instruction has been executed (cleared by hardware)</li> </ul> |                                 |                        |                 |                  |                 |              |

| bit 1            |                                                                                                                                                                      | on Reset Stat                   |                        | , j             | ,                |                 |              |

|                  | 1 = No Power-on Reset occurred                                                                                                                                       |                                 |                        |                 |                  |                 |              |

|                  | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                                                                                |                                 |                        |                 |                  |                 |              |

| bit 0            |                                                                                                                                                                      |                                 |                        |                 |                  |                 |              |

|                  |                                                                                                                                                                      | n-out Reset or                  |                        | sot in softwar  | after a Dower    | on Posot or Pr  |              |

|                  | 0 = A Brown-<br>occurs)                                                                                                                                              | -out Reset OCC                  | unea (must be          | set in soltware | e after a Power- | on Reset of Bro |              |

|                  |                                                                                                                                                                      |                                 |                        |                 |                  |                 |              |

#### REGISTER 6-2: PCON0: POWER CONTROL REGISTER 0

| Name   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|-------|-------|-----------|-------|-------|--------|---------------------|

| BORCON | SBOREN | _      | _     |       | _         |       |       | BORRDY | 76                  |

| PCON0  | STKOVF | STKUNF |       | RWDT  | RMCLR     | RI    | POR   | BOR    | 77                  |

| STATUS | _      | _      | _     | TO    | PD        | Z     | DC    | С      | 30                  |

| WDTCON |        |        |       | V     | VDTPS<4:0 | >     |       | SWDTEN | 121                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

<sup>© 2015-2016</sup> Microchip Technology Inc.

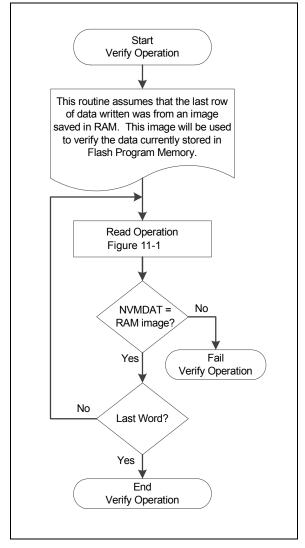

#### 11.4.8 WRITE VERIFY

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full row, then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 11-7: PROGRAM FLASH MEMORY VERIFY FLOWCHART

## **19.2 Register Definitions: PWM Control**

| REGISTER 1       |                                                 |                   | CONTROL R      |                  |                  |                  |              |

|------------------|-------------------------------------------------|-------------------|----------------|------------------|------------------|------------------|--------------|

| R/W-0/0          | U-0                                             | R-0               | R/W-0/0        | U-0              | U-0              | U-0              | U-0          |

| PWMxEN           | —                                               | PWMxOUT           | PWMxPOL        | —                | —                | —                | —            |

| bit 7            |                                                 |                   |                |                  |                  |                  | bit 0        |

|                  |                                                 |                   |                |                  |                  |                  |              |

| Legend:          |                                                 |                   |                |                  |                  |                  |              |

| R = Readable I   | bit                                             | W = Writable      | bit            | U = Unimpler     | nented bit, read | l as '0'         |              |

| u = Bit is uncha | anged                                           | x = Bit is unkr   | iown           | -n/n = Value a   | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                                 | '0' = Bit is clea | ared           |                  |                  |                  |              |

|                  |                                                 |                   |                |                  |                  |                  |              |

| bit 7            | PWMxEN: PV                                      | VM Module En      | able bit       |                  |                  |                  |              |

|                  | 1 = PWM mo                                      | dule is enable    | t              |                  |                  |                  |              |

|                  | 0 = PWM mo                                      | dule is disable   | d              |                  |                  |                  |              |

| bit 6            | Unimplemen                                      | ted: Read as '    | D'             |                  |                  |                  |              |

| bit 5            | PWMxOUT: F                                      | WM Module C       | utput Level wi | hen bit is read. |                  |                  |              |

| bit 4            | <b>PWMxPOL:</b> PWMx Output Polarity Select bit |                   |                |                  |                  |                  |              |

|                  | 1 = PWM output is active-low.                   |                   |                |                  |                  |                  |              |

|                  | 0 = PWM output is active-high.                  |                   |                |                  |                  |                  |              |

| bit 3-0          | Unimplemented: Read as '0'                      |                   |                |                  |                  |                  |              |

#### REGISTER 19-1: PWMxCON: PWM CONTROL REGISTER

#### REGISTER 19-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u     | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------------|-------------|---------|---------|---------|---------|---------|---------|

|             | PWMxDC<9:2> |         |         |         |         |         |         |

| bit 7 bit 0 |             |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **PWMxDC<9:2>:** PWM Duty Cycle Most Significant bits

These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 19-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| PWMxD   | C<1:0>  | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 **PWMxDC<1:0>:** PWM Duty Cycle Least Significant bits These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register.

bit 5-0 Unimplemented: Read as '0'

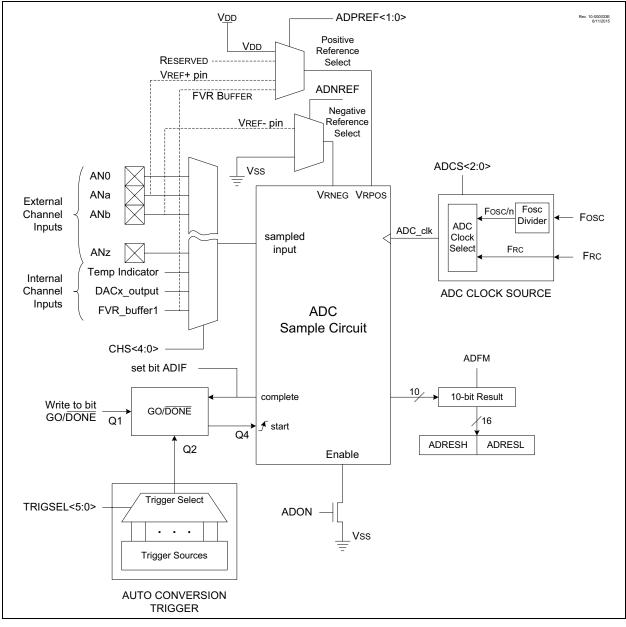

## 22.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 22-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

#### FIGURE 22-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

## 22.2 ADC Operation

#### 22.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 22.2.6 "ADC Conver-     |

|       | sion Procedure".                         |

#### 22.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- · Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 22.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

**Note:** A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 22.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the ADCRC option. When the ADCRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than ADCRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 22.2.5 AUTO-CONVERSION TRIGGER

The Auto-conversion Trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The Auto-conversion Trigger source is selected with the ADACT<4:0> bits of the ADACT register.

See Table 22-2 for auto-conversion sources.

## TABLE 22-2: ADC AUTO-CONVERSION TABLE

| Source<br>Peripheral | Description                  |

|----------------------|------------------------------|

| TMR0                 | Timer0 Overflow condition    |

| TMR1                 | Timer1 Overflow condition    |

| TMR3                 | Timer3 Overflow condition    |

| TMR5                 | Timer5 Overflow condition    |

| TMR2                 | Match between Timer2 and PR2 |

| TMR4                 | Match between Timer4 and PR4 |

| TMR6                 | Match between Timer6 and PR6 |

| C1                   | Comparator C1 output         |

| C2                   | Comparator C2 output         |

| CLC1                 | CLC1 output                  |

| CLC2                 | CLC2 output                  |

| CLC3                 | CLC3 output                  |

| CLC4                 | CLC4 output                  |

| CCP1                 | CCP1 output                  |

| CCP2                 | CCP2 output                  |

| CCP3                 | CCP3 output                  |

| CCP4                 | CCP4 output                  |

## 25.0 DATA SIGNAL MODULATOR (DSM) MODULE

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of key modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- Carrier Source Polarity Select

- Carrier Source Pin Disable

- Programmable Modulator Data

- Modulator Source Pin Disable

- Modulated Output Polarity Select

- Slew Rate Control

Figure 25-1 shows a simplified block diagram of the Data Signal Modulator peripheral.

# PIC16(L)F18325/18345

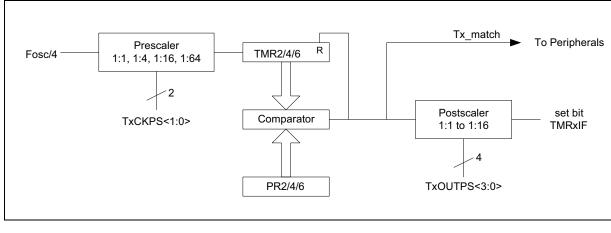

## 28.0 TIMER2/4/6 MODULE

Timer2/4/6 modules are 8-bit timers that incorporate the following features:

- 8-bit Timer and Period registers (TMR2/4/6 and PR2/4/6, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2/4/6 match with PR2/4/6

- Optional use as the shift clock for the MSSPx module

See Figure 28-1 for a block diagram of Timer2/4/6.

- Note 1: In devices with more than one Timer module, it is very important to pay close attention to the register names used. A number placed after the module acronym is used to distinguish between separate modules. For example, the T2CON and T4CON control the same operational aspects of two completely different Timer modules.

- 2: Throughout this section, generic references to Timer2 module in any of its operating modes may be interpreted as being equally applicable to Timerx module. Register names, module signals, I/O pins and bit names may use the generic designator 'x' to indicate the use of a numeral to distinguish a particular module, when required.

## FIGURE 28-1: TIMER2/4/6 BLOCK DIAGRAM

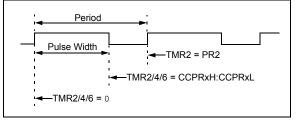

#### 29.4 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 29-3 shows a typical waveform of the PWM signal.

SIMPLIFIED PWM BLOCK DIAGRAM

**FIGURE 29-4:**

#### 29.4.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2/4/6 registers

- T2/4/6CON registers

- CCPRxL registers

- CCPxCON registers

Figure 29-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

FIGURE 29-3:

CCP PWM OUTPUT SIGNAL

#### Rev. 10-000157E Duty cycle registers CCPRxH CCPRxL CCPx out To Peripherals set CCPIF 10-bit Latch<sup>(2)</sup> (Not accessible by user) Comparator R Q CCPx s **TRIS** Control TMR2 Module R TMR2 (1) **ERS** logic CCPx\_pset Comparator PR2 1. 8-bit timer is concatenated with two bits generated by Fosc or two bits of the internal prescaler to Notes: create 10-bit time-base. 2. The alignment of the 10 bits from the CCPR register is determined by the CCPxFMT bit.

## 30.4.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicates to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPxCON2 register.

Slave software, when the AHEN and DHEN bits are set, the clock is stretched, allowing the slave time to change the  $\overrightarrow{ACK}$  value before it is sent back to the transmitter. The ACKDT bit of the SSPxCON2 register is set/cleared to determine the response.

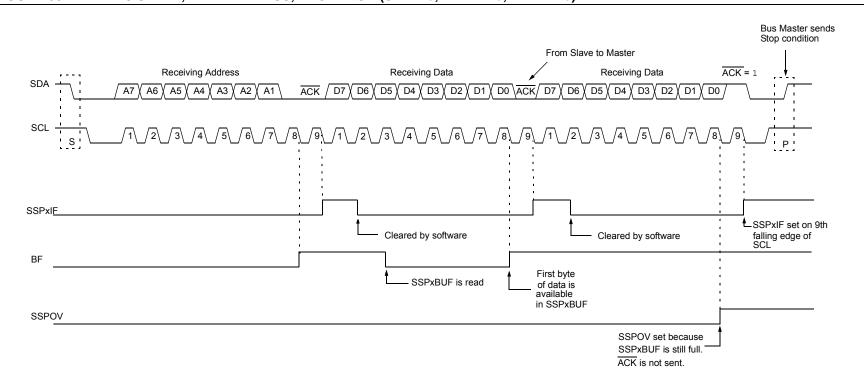

There are certain conditions where an  $\overline{ACK}$  will not be sent by the slave. If the BF bit of the SSPxSTAT register or the SSPOV bit of the SSPxCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPxCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

## 30.5 I<sup>2</sup>C SLAVE MODE OPERATION

The MSSP Slave mode operates in one of four modes selected by the SSPM bits of SSPxCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operate the same as the other modes with SSPxIF additionally getting set upon detection of a Start, Restart, or Stop condition.

#### 30.5.1 SLAVE MODE ADDRESSES

The SSPxADD register (Register 30-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPxBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 30-5) affects the address matching process. See **Section 30.5.9** "**SSP Mask Register**" for more information.

#### 30.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

#### 30.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb's of the 10-bit address and stored in bits 2 and 1 of the SSPxADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPxADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPxADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPxADD is updated to receive a high byte again. When SSPxADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

## FIGURE 30-14: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 0, DHEN = 0)

PIC16(L)F18325/18345

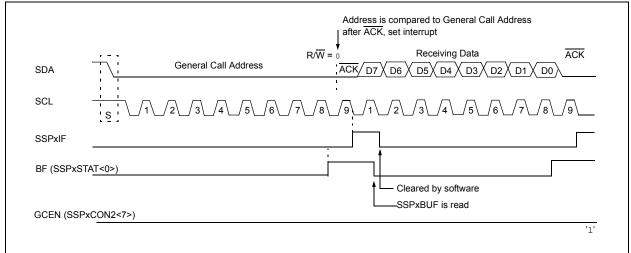

#### 30.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^{2}C$  protocol, defined as address 0x00. When the GCEN bit of the SSPxCON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSPxADD. After the slave clocks in an address of all zeros with

the  $R/\overline{W}$  bit clear, an interrupt is generated and slave software can read SSPxBUF and respond. Figure 30-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPxCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### FIGURE 30-24: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE

#### 30.5.9 SSP MASK REGISTER

An SSP Mask (SSPMSK) register (Register 30-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPxSR register during an address comparison operation. A zero ('0') bit in the SSPxMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

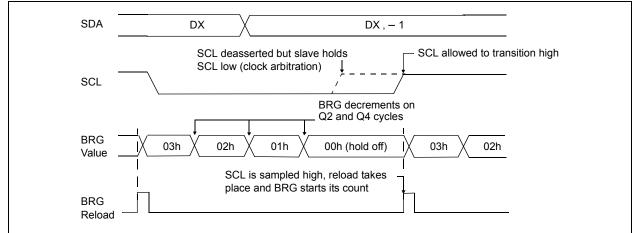

#### 30.6.2 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, releases the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the

SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<7:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 30-25).

#### 30.6.3 WCOL STATUS FLAG

If the user writes the SSPxBUF when a Start, Restart, Stop, Receive or Transmit sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur). Any time the WCOL bit is set it indicates that an action on SSPxBUF was attempted while the module was not idle.

| Note: | Because queuing of events is not allowed,  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | writing to the lower five bits of SSPxCON2 |  |  |  |  |  |  |  |

|       | is disabled until the Start condition is   |  |  |  |  |  |  |  |

|       | complete.                                  |  |  |  |  |  |  |  |

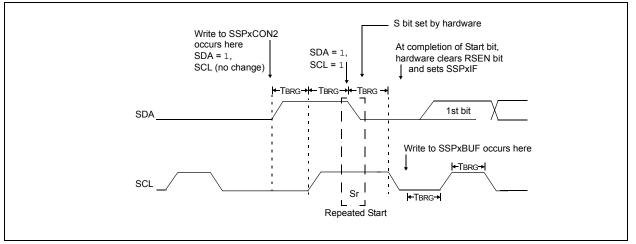

#### 30.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 30-27) occurs when the RSEN bit of the SSPxCON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPxCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPxSTAT register will be set. The SSPxIF bit will not be set until the Baud Rate Generator has timed out.

**Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## FIGURE 30-27: REPEATED START CONDITION WAVEFORM

## 34.0 INSTRUCTION SET SUMMARY

Each instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- · Literal and Control

The literal and control category contains the most varied instruction word format.

Table 34-3 lists the instructions recognized by the MPASM<sup>™</sup> assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine entry takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 34.1 Read-Modify-Write Operations

Any write instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the working (W) register, or the originating file register, depending on the state of the destination designator 'd' (see Table 34-1 for more information). A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 34-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.                                                                                        |

| n     | FSR or INDF number. (0-1)                                                                                                                                                       |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                     |

#### TABLE 34-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |  |  |

|-------|-----------------|--|--|

| PC    | Program Counter |  |  |

| TO    | Time-Out bit    |  |  |

| С     | Carry bit       |  |  |

| DC    | Digit Carry bit |  |  |

| Z     | Zero bit        |  |  |

| PD    | Power-Down bit  |  |  |

| PIC16LF | 18325/18345            | Standard Operating Conditions (un                       | less c | otherwi | se stat | ed)   |            |          |

|---------|------------------------|---------------------------------------------------------|--------|---------|---------|-------|------------|----------|

| PIC16F1 | 8325/18345             | Standard Operating Conditions (unless otherwise stated) |        |         |         |       |            |          |

| Param.  | Symbol                 | Device Characteristics                                  | Min    | Typ.†   | Max.    | Units | Conditions |          |

| No.     | Cymbol                 |                                                         |        | 1,46.1  | max.    | onits | Vdd        | Note     |

| D100    | IDDxt4                 | XT = 4 MHz                                              | —      | 321     | 455     | uA    | 3.0V       | $\wedge$ |

| D100    | IDDxt4                 | XT = 4 MHz                                              | —      | 332     | 479     | uA    | 3.0V       |          |

| D101    | IDDHF016               | HFINTOSC = 16 MHz                                       | —      | 1.3     | 1.8     | mA    | 3.0V/      |          |

| D101    | IDDHF016               | HFINTOSC = 16 MHz                                       | —      | 1.4     | 1.9     | mA    | 3.0V       |          |

| D102    | IDDHFOPLL              | HFINTOSC = 32 MHz                                       | —      | 2.2     | 2.8     | mA    | 3.0V       | $\sim$   |

| D102    | IDDHFOPLL              | HFINTOSC = 32 MHz                                       |        | 2.3     | 2.9     | mA    | /3.0Y      |          |

| D103    | IDDHSPLL32             | HS+PLL = 32 MHz                                         | -      | 2.2     | 2.8     | ſmA<  | 3.ØV       |          |

| D103    | IDDHSPLL32             | HS+PLL = 32 MHz                                         |        | 2.3     | 2.9     | mÀ    | 3.0√       |          |

| D104    | IDDIDLE                | IDLE Mode, HFINTOSC = 16 MHz                            | —      | 804     | 1283    | uA    | 3.QV       | $\geq$   |

| D104    | IDDIDLE                | IDLE Mode, HFINTOSC = 16 MHz                            | _      | 816     | (1284   | ∕₽Ą   | 3.0V       | /        |

| D105    | IDDDOZE <sup>(3)</sup> | DOZE mode, HFINTOSC = 16 MHz,<br>DOZE Ratio = 16        | _      | 863     | f       | ZuA   | 3.0V       |          |

| D105    | IDDDOZE <sup>(3)</sup> | DOZE mode, HFINTOSC = 16 MHz,<br>DOZE Ratio = 16        | _<     | 875     |         | A     | 3.0V       |          |

#### TABLE 35-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup>

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: IDDDOZE =  $[IDDIDLE^{(N-1)/N}] + IDDHFO16/N where N = DOZE Ration (see Register 9-2).$

| DC CHA        | RACTI | ERISTICS                             | Standard Operating Conditions (unless otherwise stated) |                     |               |              |                                                                                                                                                    |  |  |  |

|---------------|-------|--------------------------------------|---------------------------------------------------------|---------------------|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Sym.  | Characteristic                       | Min.                                                    | Тур.†               | Max.          | Units        | Conditions                                                                                                                                         |  |  |  |

|               | VIL   | Input Low Voltage                    |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |

|               |       |                                      |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |

| D300          |       | with TTL buffer                      | —                                                       | —                   | 0.8           | V            | $4.5V \le VDD \le 5.5V$                                                                                                                            |  |  |  |

| D301          |       |                                      | —                                                       | _                   | 0.15 VDD      | V            | $1.8V \leq VDD \leq 4.5V$                                                                                                                          |  |  |  |

| D302          |       | with Schmitt Trigger buffer          | _                                                       | _                   | 0.2 Vdd       | V            | 2.0V ≤ VDD ≤ <del>5.5</del> V                                                                                                                      |  |  |  |

| D303          |       | with I <sup>2</sup> C levels         | _                                                       | _                   | 0.3 Vdd       | V            | $\frown$                                                                                                                                           |  |  |  |

| D304          |       | with SMBus levels                    | —                                                       | _                   | 0.8           | V /          | $2.7V \leq VDD \leq 5.5V$                                                                                                                          |  |  |  |

| D305          |       | MCLR                                 |                                                         | _                   | 0.2 VDD       | K            |                                                                                                                                                    |  |  |  |

|               | VIH   | Input High Voltage                   |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |

|               |       | I/O PORT:                            | _                                                       |                     | $\frown$      |              | $\searrow$                                                                                                                                         |  |  |  |

| D320          |       | with TTL buffer                      | 2.0                                                     | _                   | _/ _          | $\checkmark$ | $4.5V \neq VDD \leq 5.5V$                                                                                                                          |  |  |  |

| D321          |       |                                      | 0.25 VDD + 0.8                                          | _                   | $  - \rangle$ | $\vee$       | $1.8V \le VDD \le 4.5V$                                                                                                                            |  |  |  |

| D322          |       | with Schmitt Trigger buffer          | 0.8 Vdd                                                 | <                   | <u> </u>      | $\sqrt{}$    | $2.0V \leq V\text{DD} \leq 5.5V$                                                                                                                   |  |  |  |

| D323          |       | with I <sup>2</sup> C levels         | 0.7 Vdd                                                 |                     | /-/           | $\bigvee$    |                                                                                                                                                    |  |  |  |

| D324          |       | with SMBus levels                    | 2.1 '                                                   | $\langle - \langle$ |               | > v          | $2.7V \le V\text{DD} \le 5.5V$                                                                                                                     |  |  |  |

| D325          |       | MCLR                                 | 0.7 VDD                                                 | $ \ge $             |               | V            |                                                                                                                                                    |  |  |  |

|               | lı∟   | Input Leakage Current <sup>(2)</sup> |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |

| D340          |       | I/O Ports                            | 7                                                       | ±5                  | ± 125         | nA           | $\label{eq:VSS} \begin{split} VSS &\leq V PIN \leq V DD, \\ Pin \ at \ high-impedance, \ 85^\circ C \end{split}$                                   |  |  |  |

| D341          |       | <                                    | A/                                                      | ₹5                  | ± 1000        | nA           | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at high-impedance, } 125^{\circ}{\sf C} \end{split}$ |  |  |  |

| D342          |       | MCLR <sup>(2)</sup>                  | $\square$                                               | ± 50                | ± 200         | nA           | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 85°C                                                                                         |  |  |  |

|               | IPUR  | Weak Pull-up Current                 |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |

| D350          |       | $\land$                              | 25                                                      | 120                 | 200           | μA           | VDD = 3.0V, VPIN = VSS                                                                                                                             |  |  |  |

|               | Vol   | Output Low Voltage <sup>(4)</sup>    | >                                                       |                     | •             |              |                                                                                                                                                    |  |  |  |

| D360          |       | I/O ports                            | _                                                       | _                   | 0.6           | V            | IOL = 10.0 mA, VDD = 3.0V                                                                                                                          |  |  |  |

|               | Vон   | Output High Vøltage <sup>(4)</sup>   |                                                         |                     |               |              |                                                                                                                                                    |  |  |  |

| D370          |       | I/Q ports                            | Vdd - 0.7                                               | _                   | —             | V            | Іон = 6.0 mA, Vdd = 3.0V                                                                                                                           |  |  |  |

| D380          | CIO   | All VO pins                          | _                                                       | 5                   | 50            | рF           |                                                                                                                                                    |  |  |  |

#### TABLE 35-4: I/O PORTS

These parameters are characterized but not tested. €

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as current sourced by the pin.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

2;

| Param.<br>No. | Symbol  | Charact               | eristic      | Min.                          | Max.          | Units                     | Conditions                                  |

|---------------|---------|-----------------------|--------------|-------------------------------|---------------|---------------------------|---------------------------------------------|

| SP100*        | Тнідн   | Clock high time       | 100 kHz mode | 4.0                           | _             | μS                        | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 0.6                           | —             | μS                        | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP module   | 1.5Tcy                        | —             |                           |                                             |

| SP101*        | TLOW    | Clock low time        | 100 kHz mode | 4.7                           | _             | μS                        | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 1.3                           | —             | μS                        | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP module   | 1.5Tcy                        | —             | $\langle \langle \rangle$ |                                             |

| SP102* TR     | TR      | SDA and SCL rise time | 100 kHz mode | —                             | 1000          | ns                        |                                             |

|               |         |                       | 400 kHz mode | 20 +<br>0.1Св                 | 300           | ns                        | CB is specified to be from 10-400 pF        |

| SP103*        | TF      | SDA and SCL fall      | 100 kHz mode | _                             | 250           | ris ~                     | $\square$                                   |

|               |         | time                  | 400 kHz mode | 20 +<br>0.1Св                 | 250           | ns                        | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT | Data input hold       | 100 kHz mode | 0                             | $\mathcal{F}$ | ns                        |                                             |

|               |         | time                  | 400 kHz mode | 0                             | 0.9           | μs                        |                                             |

| SP107*        | TSU:DAT | Data input setup      | 100 kHz mode | 250                           |               | ns                        | (Note 2)                                    |

|               |         | time                  | 400 kHz mode | 100                           | $\geq -$      | ns                        |                                             |

| SP109*        | ΤΑΑ     | Output valid from     | 100 kHz mode | $\langle \mathcal{F} \rangle$ | 3500          | ns                        | (Note 1)                                    |

|               |         | clock                 | 400 kHz mode | $\searrow$                    | _             | ns                        |                                             |

| SP110*        | TBUF    | Bus free time         | 100 kHz mode | 4.7                           | —             | μS                        | Time the bus must be free                   |

|               |         |                       | 400 kHz mode | 1.3                           | —             | μS                        | before a new transmission<br>can start      |

| SP111         | Св      | Bus capacitive loadi  | ng           | _                             | 400           | pF                        |                                             |

## TABLE 35-24: I<sup>2</sup>C BUS DATA CHARACTERISTICS

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

**2:** A Fast mode (400 kHz)  $|^{2}$ C bus device can be used in a Standard mode (100 kHz)  $|^{2}$ C bus system, but the requirement Tsy:Dat  $\geq$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode  $1^{2}$  bus specification), before the SCL line is released.

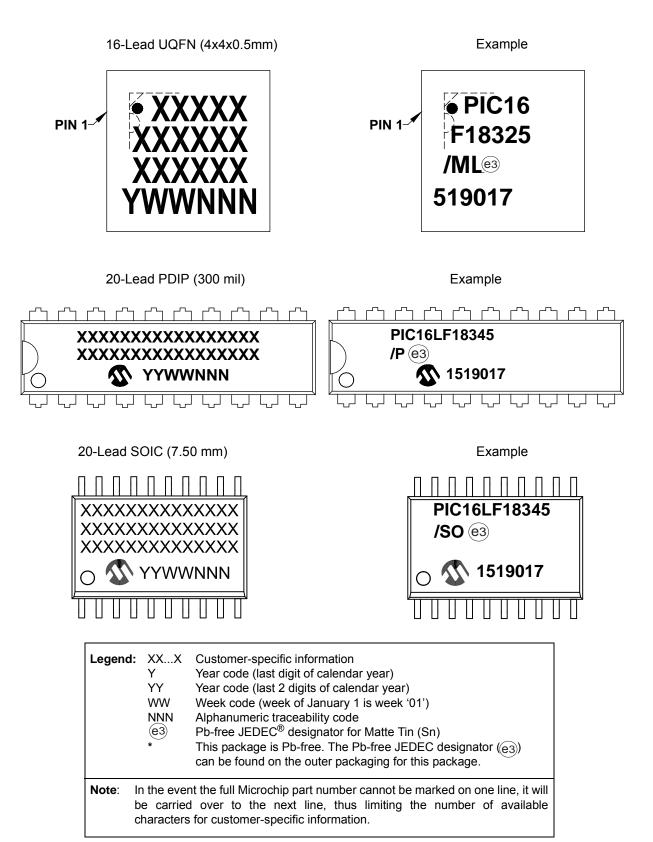

## Package Marking Information (Continued)

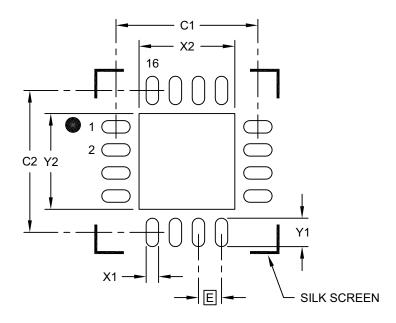

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                               | MILLIMETERS |      |      |      |  |

|-------------------------------|-------------|------|------|------|--|

| Dimensio                      |             |      |      |      |  |

| Dimensio                      | IVIIIN      | NOM  | MAX  |      |  |

| Contact Pitch                 | 0.65 BSC    |      |      |      |  |

| Optional Center Pad Width     | X2          | 2.70 |      |      |  |

| Optional Center Pad Length Y2 |             |      |      | 2.70 |  |

| Contact Pad Spacing           | C1          |      | 4.00 |      |  |

| Contact Pad Spacing           | C2          |      | 4.00 |      |  |

| Contact Pad Width (X16)       | X1          |      |      | 0.35 |  |

| Contact Pad Length (X16)      |             |      |      | 0.80 |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A