# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I²C, SCI                                                              |

| Peripherals                | LED, LVD, POR, PWM                                                    |

| Number of I/O              | 23                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 28-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908jl16cdwe |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

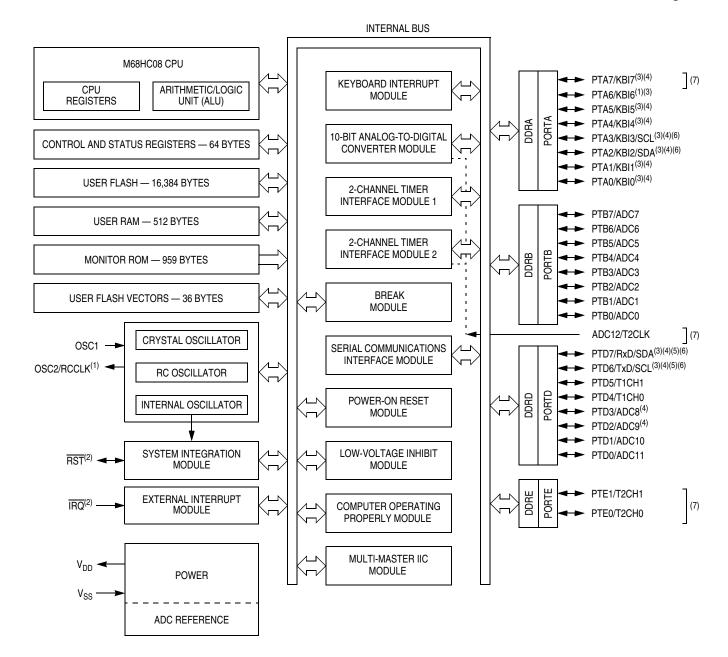

#### **MCU Block Diagram**

NOTES:

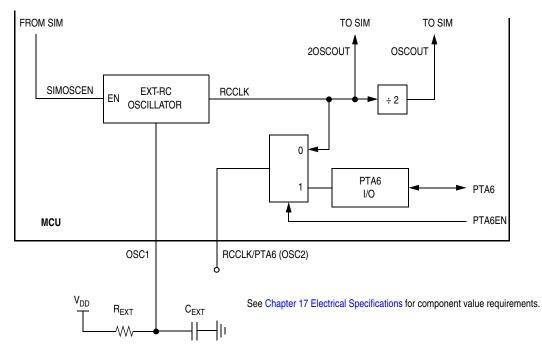

- 1. Shared pin: OSC2/RCCLK/PTA6/KBI6

- 2. Pin contains integrated pull-up device

- 3. Pin contains programmable pull-up device

- 4. LED direct sink pin

- 5. 25-mA output drive pin

- 6. Pin is open-drain output when MMIIC function enabled;

- position of SDA and SCL are selected in CONFIG2 register.

- 7. Pins available on 32-pin packages only

### Figure 1-1. MC68HC908JL16 Block Diagram

# Chapter 4 System Integration Module (SIM)

# 4.1 Introduction

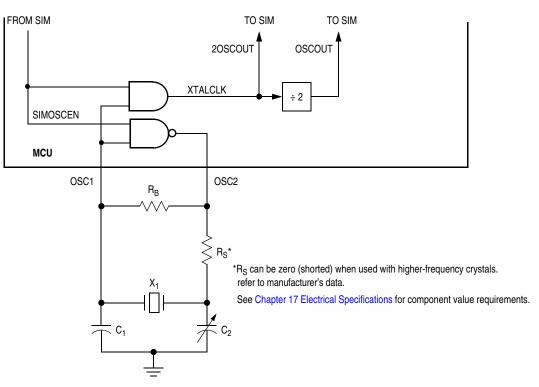

This section describes the system integration module (SIM), which supports up to 24 external and/or internal interrupts. Together with the CPU, the SIM controls all MCU activities. A block diagram of the SIM is shown in Figure 4-1. Figure 4-2 is a summary of the SIM I/O registers. The SIM is a system state controller that coordinates CPU and exception timing. The SIM is responsible for:

- · Bus clock generation and control for CPU and peripherals

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and COP timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

- Modular architecture expandable to 128 interrupt sources

| Signal Name | Description                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICLK        | Internal oscillator clock                                                                                                                                  |

| OSCOUT      | The XTAL or RC frequency divided by two. This signal is again divided by two in the SIM to generate the internal bus clocks. (Bus clock = OSCOUT $\div$ 2) |

| IAB         | Internal address bus                                                                                                                                       |

| IDB         | Internal data bus                                                                                                                                          |

| PORRST      | Signal from the power-on reset module to the SIM                                                                                                           |

| IRST        | Internal reset signal                                                                                                                                      |

| R/W         | Read/write signal                                                                                                                                          |

### Table 4-1. Signal Name Conventions

#### **SIM Registers**

Figure 4-19. Stop Mode Recovery from Interrupt or Break

## 4.7 SIM Registers

The SIM has three memory mapped registers.

- Break Status Register (BSR)

- Reset Status Register (RSR)

- Break Flag Control Register (BFCR)

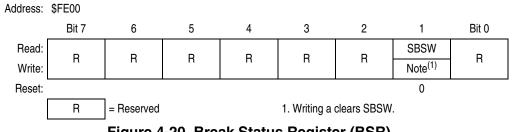

### 4.7.1 Break Status Register (BSR)

The break status register contains a flag to indicate that a break caused an exit from stop or wait mode.

Figure 4-20. Break Status Register (BSR)

### SBSW — SIM Break Stop/Wait

This status bit is useful in applications requiring a return to wait or stop mode after exiting from a break interrupt. Clear SBSW by writing a logic zero to it. Reset clears SBSW.

1 = Stop mode or wait mode was exited by break interrupt

0 = Stop mode or wait mode was not exited by break interrupt

### Serial Communications Interface (SCI)

### 7.4.3.3 Data Sampling

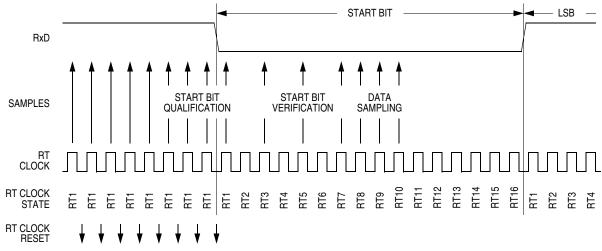

The receiver samples the RxD pin at the RT clock rate. The RT clock is an internal signal with a frequency 16 times the baud rate. To adjust for baud rate mismatch, the RT clock is resynchronized at the following times (see Figure 7-6):

- After every start bit

- After the receiver detects a data bit change from logic 1 to logic 0 (after the majority of data bit samples at RT8, RT9, and RT10 returns a valid logic 1 and the majority of the next RT8, RT9, and RT10 samples returns a valid logic 0)

To locate the start bit, data recovery logic does an asynchronous search for a logic 0 preceded by three logic 1s. When the falling edge of a possible start bit occurs, the RT clock begins to count to 16.

Figure 7-6. Receiver Data Sampling

To verify the start bit and to detect noise, data recovery logic takes samples at RT3, RT5, and RT7. Table 7-2 summarizes the results of the start bit verification samples.

| RT3, RT5, and RT7<br>Samples | Start Bit<br>Verification | Noise Flag |

|------------------------------|---------------------------|------------|

| 000                          | Yes                       | 0          |

| 001                          | Yes                       | 1          |

| 010                          | Yes                       | 1          |

| 011                          | No                        | 0          |

| 100                          | Yes                       | 1          |

| 101                          | No                        | 0          |

| 110                          | No                        | 0          |

| 111                          | No                        | 0          |

Table 7-2. Start Bit Verification

Start bit verification is not successful if any two of the three verification samples are logic 1s. If start bit verification is not successful, the RT clock is reset and a new search for a start bit begins.

### Serial Communications Interface (SCI)

# 7.8 I/O Registers

These I/O registers control and monitor SCI operation:

- SCI control register 1 (SCC1)

- SCI control register 2 (SCC2)

- SCI control register 3 (SCC3)

- SCI status register 1 (SCS1)

- SCI status register 2 (SCS2)

- SCI data register (SCDR)

- SCI baud rate register (SCBR)

### 7.8.1 SCI Control Register 1

SCI control register 1:

- Enables loop mode operation

- Enables the SCI

- Controls output polarity

- Controls character length

- Controls SCI wakeup method

- Controls idle character detection

- Enables parity function

- Controls parity type

Address: \$0013

|                 | Bit 7 | 6     | 5     | 4 | 3    | 2    | 1   | Bit 0 |

|-----------------|-------|-------|-------|---|------|------|-----|-------|

| Read:<br>Write: | LOOPS | ENSCI | TXINV | М | WAKE | ILTY | PEN | PTY   |

| Reset:          | 0     | 0     | 0     | 0 | 0    | 0    | 0   | 0     |

### Figure 7-9. SCI Control Register 1 (SCC1)

### LOOPS — Loop Mode Select Bit

This read/write bit enables loop mode operation. In loop mode the RxD pin is disconnected from the SCI, and the transmitter output goes into the receiver input. Both the transmitter and the receiver must be enabled to use loop mode. Reset clears the LOOPS bit.

1 = Loop mode enabled

0 = Normal operation enabled

### ENSCI — Enable SCI Bit

This read/write bit enables the SCI and the SCI baud rate generator. Clearing ENSCI sets the SCTE and TC bits in SCI status register 1 and disables transmitter interrupts. Reset clears the ENSCI bit.

1 = SCI enabled

0 = SCI disabled

### **TXINV** — Transmit Inversion Bit

This read/write bit reverses the polarity of transmitted data. Reset clears the TXINV bit.

- 1 = Transmitter output inverted

- 0 = Transmitter output not inverted

### NOTE

Setting the TXINV bit inverts all transmitted values, including idle, break, start, and stop bits.

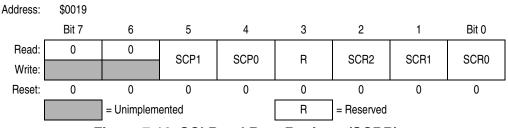

## 7.8.7 SCI Baud Rate Register

The baud rate register (SCBR) selects the baud rate for both the receiver and the transmitter.

Figure 7-16. SCI Baud Rate Register (SCBR)

### SCP1 and SCP0 — SCI Baud Rate Prescaler Bits

These read/write bits select the baud rate prescaler divisor as shown in Table 7-6. Reset clears SCP1 and SCP0.

| lable | 7-6. 3 | SCI B | aud F | tate F | rescal | ing |

|-------|--------|-------|-------|--------|--------|-----|

|       |        |       |       |        |        |     |

| SCP1 and SCP0 | Prescaler Divisor (PD) |

|---------------|------------------------|

| 00            | 1                      |

| 01            | 3                      |

| 10            | 4                      |

| 11            | 13                     |

### SCR2–SCR0 — SCI Baud Rate Select Bits

These read/write bits select the SCI baud rate divisor as shown in Table 7-7. Reset clears SCR2–SCR0.

Table 7-7. SCI Baud Rate Selection

| SCR2, SCR1, and SCR0 | Baud Rate Divisor (BD) |

|----------------------|------------------------|

| 000                  | 1                      |

| 001                  | 2                      |

| 010                  | 4                      |

| 011                  | 8                      |

| 100                  | 16                     |

| 101                  | 32                     |

| 110                  | 64                     |

| 111                  | 128                    |

Use this formula to calculate the SCI baud rate:

baud rate =

$$\frac{\text{SCI clock source}}{64 \times \text{PD} \times \text{BD}}$$

where:

SCI clock source = bus clock

PD = prescaler divisor

BD = baud rate divisor

Table 7-8 shows the SCI baud rates that can be generated with a 4.9152 MHz bus clock.

# 8.3 I/O Pins

The MMIIC module uses two I/O pins, shared with standard port I/O pins. The full name of the MMIIC I/O pins are listed in Table 8-1. The generic pin name appear in the text that follows.

| MMIIC<br>Generic Pin Names:           | Full MCU Pin Names:          |

|---------------------------------------|------------------------------|

| SDA                                   | PTA2/KBI2/SDA <sup>(1)</sup> |

| J J J J J J J J J J J J J J J J J J J | PTD7/RxD/SDA                 |

| SCL                                   | PTA3/KBI3/SCL <sup>(1)</sup> |

| 50L                                   | PTD6/TxD/SCL                 |

### Table 8-1. Pin Name Conventions

1. Position of MMIIC module pins is user selectable using CONFIG2 option bit. Refer to Chapter 3 Configuration and Mask Option Registers (CONFIG and MOR) for additional information.

| Addr.  | Register Name                              |                 | Bit 7  | 6          | 5      | 4          | 3      | 2         | 1      | Bit 0   |

|--------|--------------------------------------------|-----------------|--------|------------|--------|------------|--------|-----------|--------|---------|

|        | Multi-Master IIC                           | Read:           | MMALIF | MMNAKIF    | MMBB   | MMAST      | MMRW   | MMBR2     | MMBR1  | MMBR0   |

| \$0040 | Master Control Register                    | Write:          | 0      | 0          |        | IVIIVIA3 I |        | IVIIVIDNZ |        |         |

|        | (MIMCR)                                    | Reset:          | 0      | 0          | 0      | 0          | 0      | 0         | 0      | 0       |

| \$0041 | Multi-Master IIC Address<br>Register       | Read:<br>Write: | MMAD7  | MMAD6      | MMAD5  | MMAD4      | MMAD3  | MMAD2     | MMAD1  | MMEXTAD |

|        | (MMADR)                                    | Reset:          | 1      | 0          | 1      | 0          | 0      | 0         | 0      | 0       |

|        | Multi-Master IIC Control Reg-              | Read:           | MMEN   | MMIEN      | 0      | 0          | MMTXAK | REPSEN    | 0      | 0       |

| \$0042 | ister                                      | Write:          |        |            |        |            |        | NEFSEN    |        |         |

|        | (MMCR)                                     | Reset:          | 0      | 0          | 0      | 0          | 0      | 0         | 0      | 0       |

|        | Multi-Master IIC                           | Read:           | MMRXIF | MMTXIF     | MMATCH | MMSRW      | MMRXAK | 0         | MMTXBE | MMRXBF  |

| \$0043 | Status Register                            | Write:          | 0      | 0          |        |            |        |           |        |         |

|        | (MMSR)                                     | Reset:          | 0      | 0          | 0      | 0          | 1      | 0         | 1      | 0       |

| \$0044 | Multi-Master IIC<br>Data Transmit Register | Read:<br>Write: | MMTD7  | MMTD6      | MMTD5  | MMTD4      | MMTD3  | MMTD2     | MMTD1  | MMTD0   |

|        | (MMDTR)                                    | Reset:          | 1      | 1          | 1      | 1          | 1      | 1         | 1      | 1       |

|        | Multi-Master IIC                           | Read:           | MMRD7  | MMRD6      | MMRD5  | MMRD4      | MMRD3  | MMRD2     | MMRD1  | MMRD0   |

| \$0045 | Data Receive Register<br>(MMDRR)           | Write:          |        |            |        |            |        |           |        |         |

|        | ( )                                        | Reset:          | 0      | 0          | 0      | 0          | 0      | 0         | 0      | 0       |

|        |                                            | [               |        | = Unimpler | nented |            |        |           |        |         |

| Figure | 8-1.    | /0   | Reaister | Summary                               |

|--------|---------|------|----------|---------------------------------------|

|        | • • • • | <br> |          | • • • • • • • • • • • • • • • • • • • |

# Chapter 9 Analog-to-Digital Converter (ADC)

## 9.1 Introduction

This section describes the 10-bit successive approximation analog-to-digital converter (ADC10).

The ADC10 on this MCU uses  $V_{DD}$  and  $V_{SS}$  as its supply and reference pins. This MCU uses OSCOUT as its alternate clock source for the ADC. This MCU does not have a hardware conversion trigger.

# 9.2 Features

Features of the ADC10 module include:

- Linear successive approximation algorithm with 10-bit resolution

- Output formatted in 10- or 8-bit right-justified format

- Single or continuous conversion (automatic power-down in single conversion mode)

- Configurable sample time and conversion speed (to save power)

- Conversion complete flag and interrupt

- Input clock selectable from up to three sources

- Operation in wait and stop modes for lower noise operation

- Selectable asynchronous hardware conversion trigger

Figure 9-1 provides a summary of the input/output (I/O) registers.

| Addr.  | Register Name                   |        | Bit 7 | 6        | 5     | 4       | 3     | 2     | 1       | Bit 0    |

|--------|---------------------------------|--------|-------|----------|-------|---------|-------|-------|---------|----------|

|        | ADC Status and Control Reg-     | Read:  | 0000  | AIEN     | ADCO  | ADCH4   | ADCH3 | ADCH2 | ADCH1   | ADCH0    |

| \$003C | ister                           | Write: |       |          |       |         |       |       |         |          |

|        | (ADCSC)                         | Reset: | 0     | 0        | 0     | 1       | 1     | 1     | 1       | 1        |

|        | ADC10 Data Register High        | Read:  | 0     | 0        | 0     | 0       | 0     | 0     | 0/AD9   | 0/AD8    |

| \$003D | <b>v</b>                        |        |       | Reserved |       |         |       |       |         |          |

|        | (ADRH)                          | Reset: | 0     | 0        | 0     | 0       | 0     | 0     | 0       | 0        |

|        | ADC10 Data Register             | Read:  | AD7   | AD6      | AD5   | AD4     | AD3   | AD2   | AD1     | AD0      |

| \$003E | Low                             | Write: |       | Reserved |       |         |       |       |         |          |

|        | (ADRL)                          | Reset: | 0     | 0        | 0     | 0       | 0     | 0     | 0       | 0        |

| #000F  |                                 | Read:  | ADLPC | ADIV1    | ADIV0 | ADICLK  | MODE1 | MODE0 | ADLSMP  | ACLKEN   |

| \$003F | ADC10 Clock Register<br>(ADCLK) | Write: | ADEFU |          |       | ADIOLIN | WODET | WODEU | ADLOWIF | AULINEIN |

|        |                                 | Reset: | 0     | 0        | 0     | 0       | 0     | 0     | 0       | 0        |

|        |                                 |        |       |          |       | -       |       |       |         |          |

Figure 9-1. ADC I/O Register Summary

### NOTE

# Route $V_{REFH}$ carefully for maximum noise immunity and place bypass capacitors as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the V<sub>REFH</sub> and V<sub>REFL</sub> loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between V<sub>REFH</sub> and V<sub>REFL</sub> and must be placed as close as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

## 9.7.4 ADC10 Voltage Reference Low Pin (V<sub>REFL</sub>)

$V_{\text{REFL}}$  is the power supply for setting the low-reference voltage for the converter. In some packages,  $V_{\text{REFL}}$  is connected internally to  $V_{\text{SSA}}$ . If externally available, connect the  $V_{\text{REFL}}$  pin to the same voltage potential as  $V_{\text{SSA}}$ . There will be a brief current associated with  $V_{\text{REFL}}$  when the sampling capacitor is charging. If externally available, connect the  $V_{\text{REFL}}$  pin to the same potential as  $V_{\text{SSA}}$  at the single point ground location.

### 9.7.5 ADC10 Channel Pins (ADn)

The ADC10 has multiple input channels. Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. 0.01  $\mu$ F capacitors with good high-frequency characteristics are sufficient. These capacitors are not necessary in all cases, but when used they must be placed as close as possible to the package pins and be referenced to V<sub>SSA</sub>.

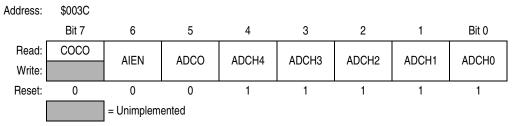

# 9.8 Registers

These registers control and monitor operation of the ADC10:

- ADC10 status and control register, ADCSC

- ADC10 data registers, ADRH and ADRL

- ADC10 clock register, ADCLK

## 9.8.1 ADC10 Status and Control Register

This section describes the function of the ADC10 status and control register (ADCSC). Writing ADCSC aborts the current conversion and initiates a new conversion (if the ADCH[4:0] bits are equal to a value other than all 1s).

Figure 9-3. ADC10 Status and Control Register (ADCSC)

## 11.3.1 IRQ Pin

A logic zero on the IRQ pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

If the MODE bit is set, the IRQ pin is both falling-edge-sensitive and low-level-sensitive. With MODE set, both of the following actions must occur to clear IRQ:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the latch. Software may generate the interrupt acknowledge signal by writing a logic one to the ACK bit in the interrupt status and control register (INTSCR). The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to the ACK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to the ACK bit latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the vector address at locations \$FFFA and \$FFFB.

- Return of the IRQ pin to logic one As long as the IRQ pin is at logic zero, IRQ remains active.

The vector fetch or software clear and the return of the IRQ pin to logic one may occur in any order. The interrupt request remains pending as long as the IRQ pin is at logic zero. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

If the MODE bit is clear, the IRQ pin is falling-edge-sensitive only. With MODE clear, a vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH or BIL instruction to read the logic level on the IRQ pin.

### NOTE

When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

### NOTE

An internal pull-up resistor to  $V_{DD}$  is connected to the  $\overline{IRQ}$  pin; this can be disabled by setting the IRQPUD bit in the CONFIG2 register (\$001E).

## 11.4 IRQ Module During Break Interrupts

The system integration module (SIM) controls whether the IRQ latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear the latches during the break state. (See Chapter 4 System Integration Module (SIM).)

To allow software to clear the IRQ latch during a break interrupt, write a logic one to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latches during the break state, write a logic zero to the BCFE bit. With BCFE at logic zero (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ latch.

Keyboard Interrupt Module (KBI)

**Monitor Module (MON)**

### **Development Support**

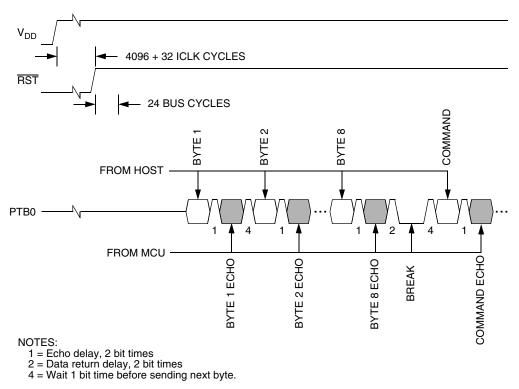

Upon power-on reset, if the received bytes of the security code do not match the data at locations \$FFF6-\$FFFD, the host fails to bypass the security feature. The MCU remains in monitor mode, but reading a FLASH location returns an invalid value and trying to execute code from FLASH causes an illegal address reset. After receiving the eight security bytes from the host, the MCU transmits a break character, signifying that it is ready to receive a command.

### NOTE

The MCU does not transmit a break character until after the host sends the eight security bytes.

To determine whether the security code entered is correct, check to see if bit 6 of RAM address \$60 is set. If it is, then the correct security code has been entered and FLASH can be accessed.

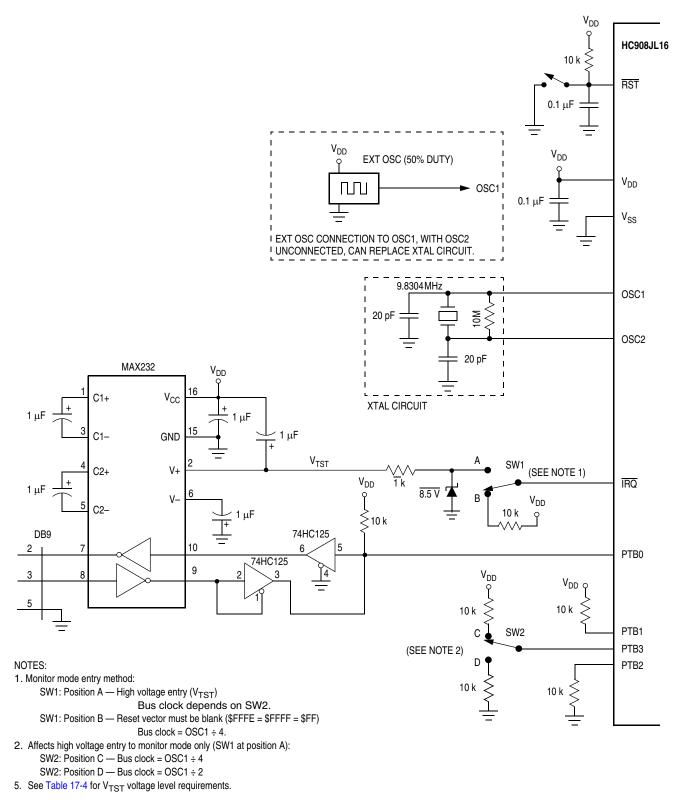

Figure 16-14. Monitor Mode Entry Timing

If the security sequence fails, the device should be reset by a power-on reset and brought up in monitor mode to attempt another entry. After failing the security sequence, the FLASH module can also be mass erased by executing an erase routine that was downloaded into internal RAM. The mass erase operation clears the security code locations so that all eight security bytes become \$FF (blank).

## 16.3.9 ROM-Resident Routines

Eight routines stored in the monitor ROM area (thus ROM-resident) are provided for FLASH memory manipulation. Six of the eight routines are intended to simplify FLASH program, erase, and load operations. The other two routines are intended to simplify the use of the FLASH memory as EEPROM. Table 16-10 shows a summary of the ROM-resident routines.

| Routine Name | Routine Description                                                   | Call Address | Stack Used <sup>(1)</sup><br>(bytes) |

|--------------|-----------------------------------------------------------------------|--------------|--------------------------------------|

| PRGRNGE      | Program a range of locations                                          | \$FC06       | 11                                   |

| ERARNGE      | Erase a page or the entire array                                      | \$FCBE       | 7                                    |

| LDRNGE       | Loads data from a range of locations                                  | \$FF30       | 9                                    |

| MON_PRGRNGE  | Program a range of locations in monitor mode                          | \$FF28       | 13                                   |

| MON_ERARNGE  | Erase a page or the entire array in monitor mode                      | \$FF2C       | 9                                    |

| MON_LDRNGE   | Loads data from a range of locations in monitor mode                  | \$FF24       | 11                                   |

| EE_WRITE     | Emulated EEPROM write. Data size ranges from 2 to 15 bytes at a time. | \$FD3F       | 24                                   |

| EE_READ      | Emulated EEPROM read. Data size ranges from 2 to 15 bytes at a time.  | \$FDD0       | 18                                   |

### Table 16-10. Summary of ROM-Resident Routines

1. The listed stack size excludes the 2 bytes used by the calling instruction, JSR.

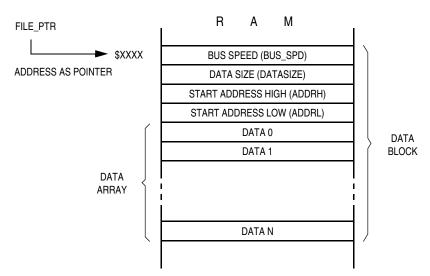

The routines are designed to be called as stand-alone subroutines in the user program or monitor mode. The parameters that are passed to a routine are in the form of a contiguous data block, stored in RAM. The index register (H:X) is loaded with the address of the first byte of the data block (acting as a pointer), and the subroutine is called (JSR). Using the start address as a pointer, multiple data blocks can be used, any area of RAM can be used. A data block has the control and data bytes in a defined order, as shown in Figure 16-15.

During the software execution, it does not consume any dedicated RAM location, the run-time heap will extend the system stack, all other RAM location will not be affected.

Figure 16-15. Data Block Format for ROM-Resident Routines

### Development Support

### 16.3.9.6 MON\_LDRNGE

In monitor mode, LDRNGE is used to load the data array in RAM with data from a range of FLASH locations.

| Routine Name        | MON_LDRNGE                                                                                                     |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Routine Description | Loads data from a range of locations, in monitor mode                                                          |  |  |  |  |

| Calling Address     | \$FF24                                                                                                         |  |  |  |  |

| Stack Used          | 11 bytes                                                                                                       |  |  |  |  |

| Data Block Format   | Bus speed<br>Data size<br>Starting address (high byte)<br>Starting address (low byte)<br>Data 1<br>:<br>Data N |  |  |  |  |

### Table 16-16. ICP\_LDRNGE Routine

The MON\_LDRNGE routine is designed to be used in monitor mode. It performs the same function as the LDRNGE routine (see 16.3.9.3 LDRNGE), except that MON\_LDRNGE returns to the main program via an SWI instruction. After a MON\_LDRNGE call, the SWI instruction will return the control back to the monitor code.

### 16.3.9.7 EE\_WRITE

EE\_WRITE is used to write a set of data from the data array to FLASH.

| Routine Name                                                                           | EE_WRITE                                                                                                                                                                  |  |  |  |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Routine DescriptionEmulated EEPROM write. Data size ranges from 2 to 1bytes at a time. |                                                                                                                                                                           |  |  |  |  |

| Calling Address                                                                        | \$FD3F                                                                                                                                                                    |  |  |  |  |

| Stack Used                                                                             | 24 bytes                                                                                                                                                                  |  |  |  |  |

| Data Block Format                                                                      | Bus speed (BUS_SPD)<br>Data size (DATASIZE) <sup>(1)</sup><br>Starting address (ADDRH) <sup>(2)</sup><br>Starting address (ADDRL) <sup>(1)</sup><br>Data 1<br>:<br>Data N |  |  |  |  |

Table 16-17. EE\_WRITE Routine

1. The minimum data size is 2 bytes. The maximum data size is 15 bytes.

2. The start address must be a page boundary start address: \$xx00, \$xx40, \$xx80,

or \$00C0.

The start location of the FLASH to be programmed is specified by the address ADDRH:ADDRL and the number of bytes in the data array is specified by DATASIZE. The minimum number of bytes that can be programmed in one routine call is 2 bytes, the maximum is 15 bytes. ADDRH:ADDRL must always be the

**Electrical Specifications**

| Table 17-4. | <b>DC Electrical</b> | Characteristics | (5V) |

|-------------|----------------------|-----------------|------|

|-------------|----------------------|-----------------|------|

| Characteristic <sup>(1)</sup>                 | Symbol             | Min  | Typ <sup>(2)</sup> | Мах  | Unit |

|-----------------------------------------------|--------------------|------|--------------------|------|------|

| Low-voltage inhibit, trip falling voltage     | V <sub>TRIPF</sub> | 3.90 | 4.20               | 4.50 | V    |

| Low-voltage inhibit, trip rising voltage      | V <sub>TRIPR</sub> | 4.00 | 4.30               | 4.60 | V    |

| Low-voltage inhibit reset/recovery hysteresis | V <sub>HYS</sub>   | —    | 100                | —    | mV   |

1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H,$  unless otherwise noted.

2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

3. Run (operating) I<sub>DD</sub> measured using external square wave clock source ( $f_{OP} = 8$ MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run I<sub>DD</sub>. Measured with all modules enabled.

4. Wait I<sub>DD</sub> measured using external square wave clock source (f<sub>OP</sub> = 8MHz). All inputs 0.2V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>.

5. Stop I<sub>DD</sub> measured with OSC1 grounded; no port pins sourcing current.

6. Maximum is highest voltage that POR is guaranteed.

7. If minimum  $V_{DD}$  is not reached before the internal POR reset is released, RST must be driven low externally until minimum  $V_{DD}$  is reached.

8.  $R_{PU}$  is measured at  $V_{DD} = 5.0$  V.

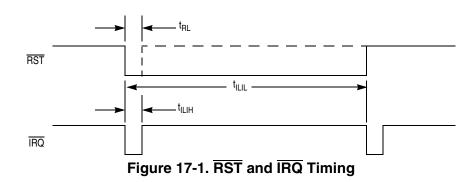

# 17.6 5-V Control Timing

Table 17-5. Control Timing (5V)

| Characteristic <sup>(1)</sup>                                 | Symbol             | Min                 | Max | Unit             |

|---------------------------------------------------------------|--------------------|---------------------|-----|------------------|

| Internal operating frequency                                  | f <sub>OP</sub>    | —                   | 8   | MHz              |

| RST input pulse width low <sup>(2)</sup>                      | t <sub>IRL</sub>   | 750                 | —   | ns               |

| TIM2 external clock input                                     | f <sub>T2CLK</sub> | _                   | 4   | MHz              |

| IRQ interrupt pulse width low (edge-triggered) <sup>(3)</sup> | t <sub>ILIH</sub>  | 100                 | _   | ns               |

| IRQ interrupt pulse period <sup>(3)</sup>                     | t <sub>ILIL</sub>  | Note <sup>(4)</sup> | _   | t <sub>CYC</sub> |

1. V<sub>DD</sub> = 4.5 to 5.5 Vdc, V<sub>SS</sub> = 0 Vdc, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub>; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>SS</sub>, unless otherwise noted.

2. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

3. Values are based on characterization results, not tested in production.

4. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1 t<sub>CYC</sub>.

Electrical Specifications

# **17.8 3-V DC Electrical Characteristics**

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                    | Symbol                              | Min                  | Тур <sup>(2)</sup>               | Мах                           | Unit                       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------|----------------------------------|-------------------------------|----------------------------|--|--|

| Output high voltage (I <sub>LOAD</sub> = -1.0 mA)<br>PTA0-PTA7, PTB0-PTB7, PTD0-PTD7, PTE0-PTE1                                                                                                                                                                                                                                                                                                                                                                  | V <sub>OH</sub>                     | V <sub>DD</sub> -0.4 | _                                | —                             | v                          |  |  |

| Output low voltage (I <sub>LOAD</sub> = 0.8 mA)<br>PTA6, PTB0–PTB7, PTD0, PTD1, PTD4, PTD5,<br>PTE0–PTE1                                                                                                                                                                                                                                                                                                                                                         | V <sub>OL</sub>                     | _                    | _                                | 0.4                           | v                          |  |  |

| Output low voltage (I <sub>LOAD</sub> = 20 mA)<br>PTD6, PTD7                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>OL</sub>                     | _                    | _                                | 0.5                           | v                          |  |  |

| LED drives (V <sub>OL</sub> = 1.8V)<br>PTA0–PTA5, PTA7, PTD2, PTD3, PTD6, PTD7                                                                                                                                                                                                                                                                                                                                                                                   | I <sub>OL</sub>                     | 8                    | 18                               | 26                            | mA                         |  |  |

| Input high voltage<br>PTA0–PTA7, PTB0–PTB7, PTD0–PTD7, PTE0–PTE1,<br>RST, IRQ, OSC1                                                                                                                                                                                                                                                                                                                                                                              | V <sub>IH</sub>                     | $0.7 	imes V_{DD}$   | _                                | V <sub>DD</sub>               | v                          |  |  |

| Input low voltage<br>PTA0–PTA7, PTB0–PTB7, PTD0–PTD7,<br>PTE0–PTE1,RST, IRQ, OSC1                                                                                                                                                                                                                                                                                                                                                                                | V <sub>IL</sub>                     | V <sub>SS</sub>      | _                                | $0.3 	imes V_{DD}$            | v                          |  |  |

| $\label{eq:VDD} \begin{array}{l} \text{Supply current, } f_{OP} = 4\text{MHz} \\ \begin{array}{l} \text{Run}^{(3)} \\ \text{XTAL oscillator option} \\ \text{RC oscillator option} \\ \text{Wait}^{(4)} \\ \text{XTAL oscillator option} \\ \text{RC oscillator option} \\ \text{Stop}^{(5)} \\ (-40^\circ\text{C to } 85^\circ\text{C}) \\ \text{XTAL or RC oscillator option (LVI enabled)} \\ \text{XTAL or RC oscillator option (LVI disabled)} \end{array}$ | I <sub>DD</sub>                     |                      | 4.5<br>4<br>2<br>1<br>130<br>0.5 | 10<br>9<br>7<br>6<br>200<br>3 | mA<br>mA<br>mA<br>μA<br>μA |  |  |

| Digital I/O ports Hi-Z leakage current                                                                                                                                                                                                                                                                                                                                                                                                                           | Ι <sub>ΙL</sub>                     | —                    | —                                | ± 10                          | μA                         |  |  |

| Input current                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I <sub>IN</sub>                     |                      | —                                | ± 1                           | μA                         |  |  |

| Capacitance<br>Ports (as input or output)                                                                                                                                                                                                                                                                                                                                                                                                                        | C <sub>OUT</sub><br>C <sub>IN</sub> |                      |                                  | 12<br>8                       | pF                         |  |  |

| POR rearm voltage <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>POR</sub>                    | 750                  | —                                | —                             | mV                         |  |  |

| POR rise time ramp rate <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                           | R <sub>POR</sub>                    | 0.035                | —                                | —                             | V/ms                       |  |  |

| Monitor mode entry voltage                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>TST</sub>                    | $1.5 \times V_{DD}$  | —                                | 8.5                           | V                          |  |  |

| Pullup resistors <sup>(8)</sup><br>RST, IRQ, PTA0–PTA7, PTD6, PTD7                                                                                                                                                                                                                                                                                                                                                                                               | R <sub>PU</sub>                     | 16                   | 24                               | 32                            | kΩ                         |  |  |

# Table 17-7. DC Electrical Characteristics (3V)

Table continued on next page

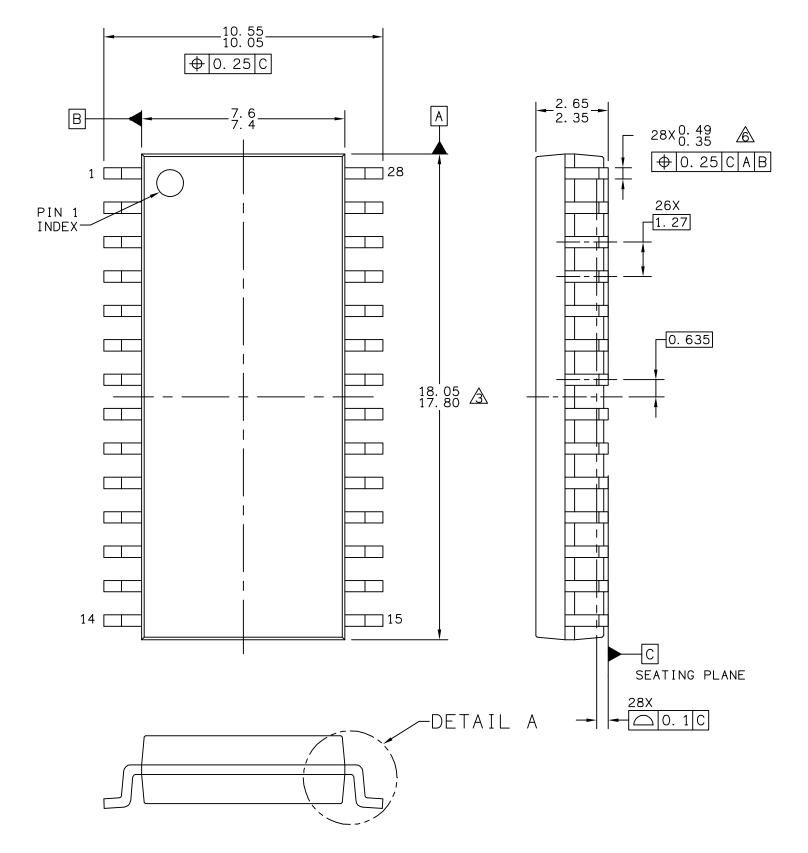

| © FREESCALE SEMICONDUCTOR, INC.<br>All Rights reserved. |  | OUTLINE            | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|--|--------------------|------------------|-------------|

| TITLE: SOIC, WIDE BODY,<br>28 LEAD<br>CASEOUTLINE       |  | DOCUMENT NO        | : 98ASB42345B    | REV: G      |

|                                                         |  | CASE NUMBER        | : 751F-05        | 10 MAR 2005 |

|                                                         |  | STANDARD: MS-013AE |                  |             |