Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I²C, SCI                                                               |

| Peripherals                | LED, LVD, POR, PWM                                                     |

| Number of I/O              | 23                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 28-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908jl16cdwer |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC68HC908JL16

# **Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

# http://freescale.com/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

# **Table of Contents**

| 7.4.2.5      | Inversion of Transmitted Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.4.2.6      | Transmitter Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90  |

| 7.4.3        | Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 7.4.3.1      | Character Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90  |

| 7.4.3.2      | Character Reception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 90  |

| 7.4.3.3      | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 7.4.3.4      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 7.4.3.5      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 7.4.3.6      | Receiver Wakeup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95  |

| 7.4.3.7      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 7.4.3.8      | Error Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 96  |

| 7.5          | Low-Power Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96  |

| 7.5.1        | Wait Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 7.5.2        | Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 7.6          | SCI During Break Module Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 7.7          | I/O Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 7.7.1        | TxD (Transmit Data).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 7.7.1        | RxD (Receive Data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 7.8          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 7.8.1        | I/O Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| 7.8.2        | SCI Control Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8.3        | SCI Control Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8.4        | SCI Status Register 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8.5        | SCI Status Register 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 7.8.6        | SCI Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 7.8.7        | SCI Baud Rate Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|              | 56. Bada Hato Hogiston 11. 11. 11. 11. 11. 11. 11. 11. 11. 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|              | Chapter 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|              | Multi-Master IIC Interface (MMIIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 8.1          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 109 |

| 8.2          | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 8.3          | I/O Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 8.4<br>8.4.1 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 8.4.2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 8.4.3        | START Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 8.4.4        | Data Transfer Data Data Transfer Data Data Data Data Data Data Data Dat |     |

| 8.4.5        | STOP Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 8.4.6        | Repeated START Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 8.4.7        | Arbitration Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 8.4.8        | Clock Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 8.4.9        | Handshaking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 8.4.10       | Clock Stretching.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| 8.4.11       | Modes of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 8.5          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|              | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 8.6          | Low-Power Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 8.6.1        | Wait Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 114 |

#### Memory

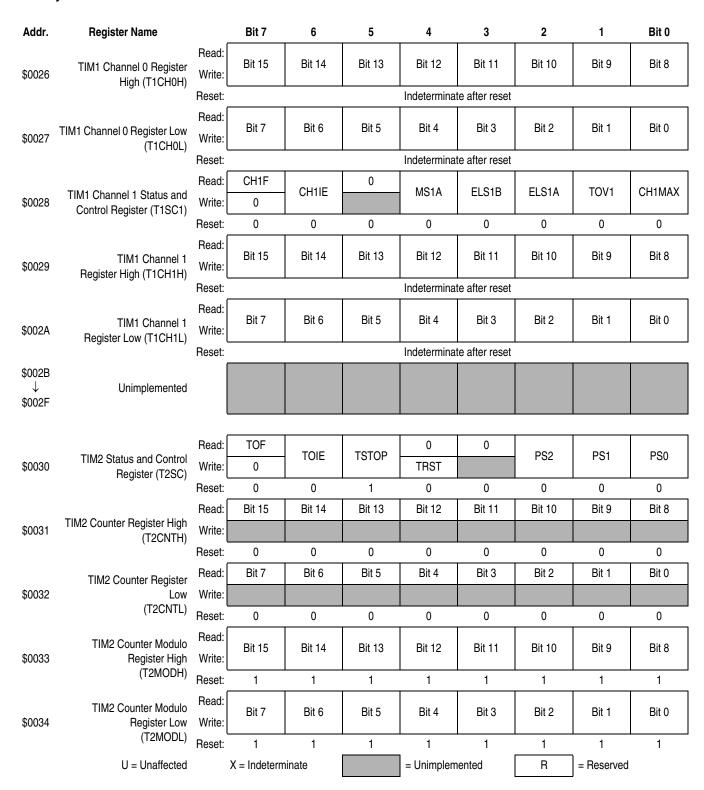

Figure 2-2. Control, Status, and Data Registers (Sheet 4 of 7)

#### Memory

## 2.5.6 FLASH Block Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect blocks of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either erase or program operations.

#### NOTE

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit

When the FLBPR is program with all 0s, the entire memory is protected from being programmed and erased. When all the bits are erased (all 1s), the entire memory is accessible for program and erase.

When bits within the FLBPR are programmed, they lock a block of memory, address ranges as shown in 2.5.7 FLASH Block Protect Register. Once the FLBPR is programmed with a value other than \$FF, any erase or program of the FLBPR or the protected block of FLASH memory is prohibited. The FLBPR itself can be erased or programmed only with an external voltage,  $V_{TST}$ , present on the  $\overline{IRQ}$  pin. This voltage also allows entry from reset into the monitor mode.

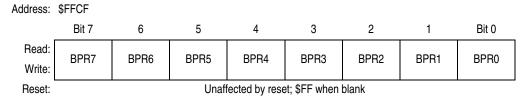

# 2.5.7 FLASH Block Protect Register

The FLASH block protect register (FLBPR) is implemented as a byte within the FLASH memory, and therefore can only be written during a programming sequence of the FLASH memory. The value in this register determines the starting location of the protected range within the FLASH memory.

Non-volatile FLASH register; write by programming.

Figure 2-5. FLASH Block Protect Register (FLBPR)

## BPR[7:0] — FLASH Block Protect Bits

BPR[7:0] represent bits [13:6] of a 16-bit memory address. Bits [15:14] are 1s and bits [5:0] are 0s.

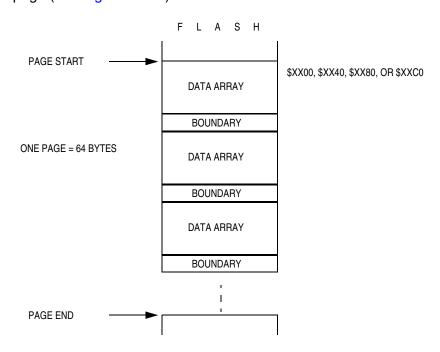

The resultant 16-bit address is used for specifying the start address of the FLASH memory for block protection. The FLASH is protected from this start address to the end of FLASH memory, at \$FFFF. With this mechanism, the protect start address can be XX00, XX40, XX80, or XXC0 (at page boundaries — 64 bytes) within the FLASH memory.

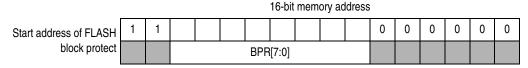

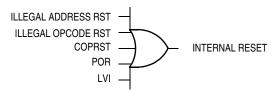

#### 4.3.2 Active Resets from Internal Sources

All internal reset sources actively pull the  $\overline{RST}$  pin low for 32 ICLK cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (Figure 4-5). An internal reset can be caused by an illegal address, illegal opcode, COP time-out, or POR. (See Figure 4-6. Sources of Internal Reset.) Note that for POR resets, the SIM cycles through 4096 ICLK cycles during which the SIM forces the  $\overline{RST}$  pin low. The internal reset signal then follows the sequence from the falling edge of  $\overline{RST}$  shown in Figure 4-5.

Figure 4-5. Internal Reset Timing

The COP reset is asynchronous to the bus clock.

Figure 4-6. Sources of Internal Reset

The active reset feature allows the part to issue a reset to peripherals and other chips within a system built around the MCU.

#### 4.3.2.1 Power-On Reset

When power is first applied to the MCU, the power-on reset module (POR) generates a pulse to indicate that power-on has occurred. The external reset pin (RST) is held low while the SIM counter counts out 4096 ICLK cycles. Sixty-four ICLK cycles later, the CPU and memories are released from reset to allow the reset vector sequence to occur.

At power-on, the following events occur:

- A POR pulse is generated.

- The internal reset signal is asserted.

- The SIM enables OSCOUT.

- Internal clocks to the CPU and modules are held inactive for 4096 ICLK cycles to allow stabilization

of the oscillator.

- The RST pin is driven low during the oscillator stabilization time.

- The POR bit of the reset status register (RSR) is set and all other bits in the register are cleared.

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared).

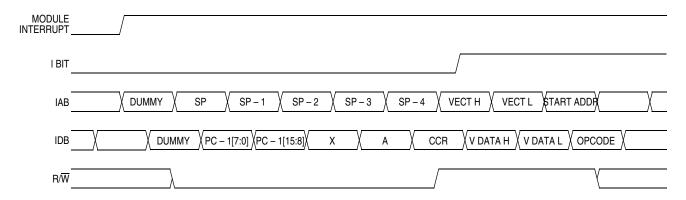

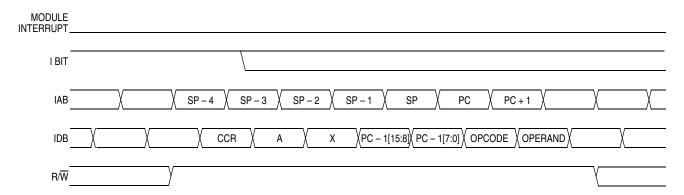

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the RTI instruction recovers the CPU register contents from the stack so that normal processing can resume. Figure 4-9 shows interrupt entry timing. Figure 4-10 shows interrupt recovery timing.

Figure 4-9. Interrupt Entry

Figure 4-10. Interrupt Recovery

# 4.5.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register), and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

Freescale Semiconductor 53

System Integration Module (SIM)

# Chapter 5 Oscillator (OSC)

# 5.1 Introduction

The oscillator module provides the reference clocks for the MCU system and bus. Two oscillators are running on the device:

Selectable oscillator — for bus clock

- Crystal oscillator (XTAL) built-in oscillator that requires an external crystal or ceramic-resonator. This option also allows an external clock that can be driven directly into OSC1.

- RC oscillator (RC) built-in oscillator that requires an external resistor-capacitor connection only.

The selected oscillator is used to drive the bus clock, the SIM, and other modules on the MCU. The oscillator type is selected by programming a bit FLASH memory. The RC and crystal oscillator cannot run concurrently; one is disabled while the other is selected; because the RC and XTAL circuits share the same OSC1 pin.

Non-selectable oscillator — for COP

• Internal oscillator — built-in RC oscillator that requires no external components.

This internal oscillator is used to drive the computer operating properly (COP) module and the SIM. The internal oscillator runs continuously after a POR or reset, and is always available.

# 5.2 Oscillator Selection

The oscillator type is selected by programming a bit in a FLASH memory location; the mask option register (MOR), at \$FFD0. (See 3.5 Mask Option Register (MOR).)

#### NOTE

On the ROM device, the oscillator is selected by a ROM-mask layer at factory.

# **Chapter 8 Multi-Master IIC Interface (MMIIC)**

# 8.1 Introduction

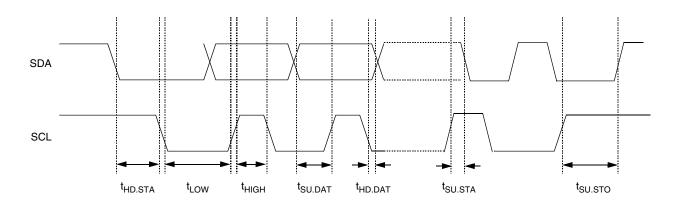

The Multi-master IIC (MMIIC) Interface is designed for internal serial communication between the MCU and other IIC devices. A hardware circuit generates "start" and "stop" signal, while byte by byte data transfer is interrupt driven by the software algorithm. Therefore, it can greatly help the software in dealing with other devices to have higher system efficiency in a typical digital monitor system.

The MMIIC not only can be applied in internal communications, but can also be used as a typical command reception serial bus for factory setup and alignment purposes. It also provides the flexibility of hooking additional devices to an existing system for future expansion without adding extra hardware.

This Multi-master IIC module uses the SCL clock line and the SDA data line to communicate with external DDC host or IIC interface. These two pins are user selectable using the CONFIG2 register (see Figure 3-3. Configuration Register 2 (CONFIG2)) to share either PTA2/PTA3 or PTD6/PTD7 based on their application needs.

The maximum data rate typically is 400k-bps. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400pF.

#### NOTE

The outputs of SCL and SDA pins are open-drain type, these pins contain ESD clamping diodes to  $V_{DD}$  and therefore cannot be driven to higher than  $V_{DD} + 0.3 \ V$ .

# 8.2 Features

- Compatibility with multi-master IIC bus standard

- Software controllable acknowledge bit generation

- Interrupt driven byte by byte data transfer

- Calling address identification interrupt

- Auto detection of R/W bit and switching of transmit or receive mode

- Detection of START, repeated START, and STOP signals

- Auto generation of START and STOP condition in master mode

- Arbitration loss detection and No-ACK awareness in master mode

- 8 selectable baud rate master clocks

- Automatic recognition of the received acknowledge bit

109

#### NOTE

Route V<sub>REFH</sub> carefully for maximum noise immunity and place bypass capacitors as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as close as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

# 9.7.4 ADC10 Voltage Reference Low Pin (V<sub>REFL</sub>)

$V_{REFL}$  is the power supply for setting the low-reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSA}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSA}$ . There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. If externally available, connect the  $V_{REFL}$  pin to the same potential as  $V_{SSA}$  at the single point ground location.

# 9.7.5 ADC10 Channel Pins (ADn)

The ADC10 has multiple input channels. Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. 0.01  $\mu$ F capacitors with good high-frequency characteristics are sufficient. These capacitors are not necessary in all cases, but when used they must be placed as close as possible to the package pins and be referenced to  $V_{SSA}$ .

# 9.8 Registers

These registers control and monitor operation of the ADC10:

- ADC10 status and control register, ADCSC

- ADC10 data registers, ADRH and ADRL

- ADC10 clock register, ADCLK

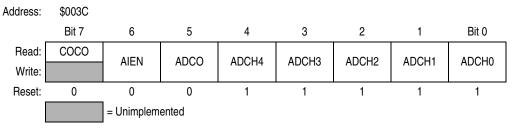

# 9.8.1 ADC10 Status and Control Register

This section describes the function of the ADC10 status and control register (ADCSC). Writing ADCSC aborts the current conversion and initiates a new conversion (if the ADCH[4:0] bits are equal to a value other than all 1s).

Figure 9-3. ADC10 Status and Control Register (ADCSC)

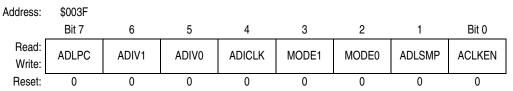

# 9.8.4 ADC10 Clock Register (ADCLK)

This register selects the clock frequency for the ADC10 and the modes of operation.

Figure 9-7. ADC10 Clock Register (ADCLK)

# ADLPC — ADC10 Low-Power Configuration Bit

ADLPC controls the speed and power configuration of the successive approximation converter. This is used to optimize power consumption when higher sample rates are not required.

- 1 = Low-power configuration: The power is reduced at the expense of maximum clock speed.

- 0 = High-speed configuration

# ADIV[1:0] — ADC10 Clock Divider Bits

ADIV1 and ADIV0 select the divide ratio used by the ADC10 to generate the internal clock ADCK. Table 9-3 shows the available clock configurations.

| ADIV1 | ADIV0 | Divide Ratio (ADIV) | Clock Rate      |

|-------|-------|---------------------|-----------------|

| 0     | 0     | 1                   | Input clock ÷ 1 |

| 0     | 1     | 2                   | Input clock ÷ 2 |

| 1     | 0     | 4                   | Input clock ÷ 4 |

| -1    | -1    | 0                   | Input clock : 9 |

Table 9-3. ADC10 Clock Divide Ratio

## **ADICLK** — Input Clock Select Bit

If ACLKEN is clear, ADICLK selects either the bus clock or an alternate clock source as the input clock source to generate the internal clock ADCK. If the alternate clock source is less than the minimum clock speed, use the internally-generated bus clock as the clock source. As long as the internal clock ADCK, which is equal to the selected input clock divided by ADIV, is at a frequency (f<sub>ADCK</sub>) between the minimum and maximum clock speeds (considering ALPC), correct operation can be guaranteed.

- 1 = The internal bus clock is selected as the input clock source

- 0 = The alternate clock source IS SELECTED

## MODE[1:0] — 10- or 8-Bit or External-Triggered Mode Selection

This bit selects between 10- or 8-bit operation. The successive approximation converter generates a result which is rounded to 8- or 10-bit value based on the mode selection. This rounding process sets the transfer function to transition at the midpoint between the ideal code voltages, causing a quantization error of 1/2LSB.

Reset returns 8-bit mode.

**Table 9-4. Mode Selection**

| MODE1 | MODE0 | Mode                                                        |

|-------|-------|-------------------------------------------------------------|

| 0     | 0     | 8-bit, right-justified, ADCSC write-triggered mode enabled  |

| 0     | 1     | 10-bit, right-justified, ADCSC write-triggered mode enabled |

| 1     | 0     | Reserved.                                                   |

| 1     | 1     | 10-bit, right-justified, external triggered mode enabled    |

MC68HC908JL16 Data Sheet, Rev. 1.1

## KBIE7-KBIE0 — Port-A Keyboard Interrupt Enable Bits

Each of these read/write bits enables the corresponding keyboard interrupt pin on port-A to latch interrupt requests. Reset clears the keyboard interrupt enable register.

- 1 = KBIx pin enabled as keyboard interrupt pin

- 0 = KBIx pin not enabled as keyboard interrupt pin

## 12.6 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

## 12.6.1 Wait Mode

The keyboard modules remain active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

# **12.6.2 Stop Mode**

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

# 12.7 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect.

MC68HC908JL16 Data Sheet, Rev. 1.1 Freescale Semiconductor 159

# **Chapter 13 Computer Operating Properly (COP)**

# 13.1 Introduction

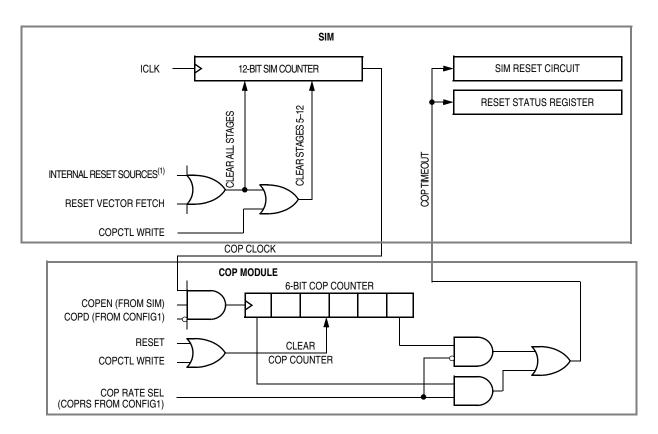

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the CONFIG1 register.

# 13.2 Functional Description

Figure 13-1 shows the structure of the COP module.

Figure 13-1. COP Block Diagram

## **Computer Operating Properly (COP)**

## **13.7.1 Wait Mode**

The COP continues to operate during wait mode. To prevent a COP reset during wait mode, periodically clear the COP counter in a CPU interrupt routine.

# **13.7.2 Stop Mode**

Stop mode turns off the ICLK input to the COP and clears the COP prescaler. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

To prevent inadvertently turning off the COP with a STOP instruction, a configuration option is available that disables the STOP instruction. When the STOP bit in the configuration register has the STOP instruction is disabled, execution of a STOP instruction results in an illegal opcode reset.

# 13.8 COP Module During Break Mode

The COP is disabled during a break interrupt when  $V_{TST}$  is present on the  $\overline{RST}$  pin.

Low-Voltage Inhibit (LVI)

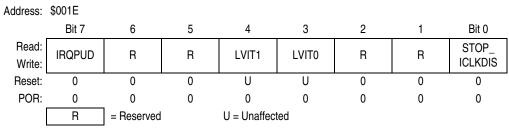

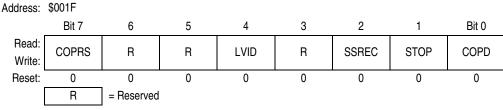

# 14.4 LVI Control Register (CONFIG2/CONFIG1)

The LVI module is controlled by three bits in the configuration registers, CONFIG1 and CONFIG2.

Figure 14-2. Configuration Register 2 (CONFIG2)

Figure 14-3. Configuration Register 1 (CONFIG1)

# LVID — Low Voltage Inhibit Disable Bit

LVID disables the LVI module. Reset clears LVID.

- 1 = Low voltage inhibit disabled

- 0 = Low voltage inhibit enabled

# LVIT1, LVIT0 — LVI Trip Voltage Selection Bits

These two bits determine at which level of  $V_{DD}$  the LVI module will come into action. LVIT1 and LVIT0 are cleared by a power-on reset only.

LVIT1

LVIT0

Comments<sup>(1)</sup>

0

0

For V<sub>DD</sub> = 3 V operation

0

1

For V<sub>DD</sub> = 3 V operation

1

0

For V<sub>DD</sub> = 5 V operation

1

1

Reserved

**Table 14-1. Trip Voltage Selection**

# 14.5 Low-Power Modes

The STOP and WAIT instructions put the MCU in low power-consumption standby modes.

# **14.5.1 Wait Mode**

The LVI module, when enabled, will continue to operate in wait mode.

# **14.5.2 Stop Mode**

The LVI module, when enabled, will continue to operate in stop mode.

MC68HC908JL16 Data Sheet, Rev. 1.1

<sup>1.</sup> See Chapter 17 Electrical Specifications for full parameters.

# **Central Processor Unit (CPU)**

# Table 15-1. Instruction Set Summary (Sheet 3 of 6)

| Source                                                                                         | Operation Description            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |   |   | ect<br>CCR |   | Address<br>Mode                                     | Opcode                                           | Operand                                         | les                                  |

|------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|------------|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | operation:                       | 2000p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ٧ | Н | I | N | Z          | С | Add                                                 | Opc                                              | Ope                                             | Cycles                               |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                           | Clear                            | M ← \$00<br>A ← \$00<br>X ← \$00<br>H ← \$00<br>M ← \$00<br>M ← \$00<br>M ← \$00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 | _ | _ | 0 | 1          | _ | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1        | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F         | dd<br>ff<br>ff                                  | 3<br>1<br>1<br>3<br>2<br>4           |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP  | Compare A with M                 | (A) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Î | _ | _ | ‡ | ‡          | ţ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                   | Complement (One's Complement)    | $\begin{array}{l} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \end{array}$                                                                                                                                                                                                                   | 0 | _ | ı | ‡ | <b>‡</b>   | 1 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                          | Compare H:X with M               | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1 | - | - | ‡ | 1          | ‡ | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3<br>4                               |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP  | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ţ | _ | _ | ‡ | 1          | ‡ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff          | 23443245                             |

| DAA                                                                                            | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U | - | _ | 1 | 1          | 1 | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel      | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A)-1 \text{ or } M \leftarrow (M)-1 \text{ or } X \leftarrow (X)-1 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+3+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+2+\mathit{rel}? \text{ (result)} \neq 0 \\ PC \leftarrow (PC)+4+\mathit{rel}? \text{ (result)} \neq 0 \end{array}$ | _ | _ | _ | - | ı          | - | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 5<br>3<br>3<br>5<br>4<br>6           |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                   | Decrement                        | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                       | ţ | - | - | ‡ | 1          | - | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>4<br>3<br>5                |

| DIV                                                                                            | Divide                           | A ← (H:A)/(X)<br>H ← Remainder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - | - | - | - | 1          | 1 | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 | _ | _ | ‡ | ‡          | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                   | Increment                        | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                       | ţ | _ | _ | ‡ | 1          | _ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

197

# 16.3.9.4 MON\_PRGRNGE

In monitor mode, MON\_PRGRNGE is used to program a range of FLASH locations with data loaded into the data array.

Routine Name MON\_PRGRNGE

Routine Description Program a range of locations, in monitor mode

Calling Address \$FC28

Stack Used 13 bytes

Bus speed Data size Starting address (high byte)

Starting address (low byte)

Data 1

:

Data N

Table 16-14. MON\_PRGRNGE Routine

The MON\_PRGRNGE routine is designed to be used in monitor mode. It performs the same function as the PRGRNGE routine (see 16.3.9.1 PRGRNGE), except that MON\_PRGRNGE returns to the main program via an SWI instruction. After a MON\_PRGRNGE call, the SWI instruction will return the control back to the monitor code.

## 16.3.9.5 MON\_ERARNGE

In monitor mode, ERARNGE is used to erase a range of locations in FLASH.

| Routine Name        | MON_ERARNGE                                                                  |

|---------------------|------------------------------------------------------------------------------|

| Routine Description | Erase a page or the entire array, in monitor mode                            |

| Calling Address     | \$FF2C                                                                       |

| Stack Used          | 9 bytes                                                                      |

| Data Block Format   | Bus speed Data size Starting address (high byte) Starting address (low byte) |

Table 16-15. MON\_ERARNGE Routine

The MON\_ERARNGE routine is designed to be used in monitor mode. It performs the same function as the ERARNGE routine (see 16.3.9.2 ERARNGE), except that MON\_ERARNGE returns to the main program via an SWI instruction. After a MON\_ERARNGE call, the SWI instruction will return the control back to the monitor code.

start of boundary address (the page start address: \$XX00, \$XX40, \$XX80, or \$00C0) and DATASIZE must be the same size when accessing the same page.

In some applications, the user may want to repeatedly store and read a set of data from an area of non-volatile memory. This can be easily implemented when EEPROM memory is used because the byte erase is allowed in EEPROM. On the other hand in FLASH memory, a minimum erase size is a page (64 bytes), so unused locations in a page will be wasted when it is used for data storage.

The EE\_WRITE routine is designed to emulate EEPROM using FLASH. This allows a FLASH page to implement data storage more efficiently. Each call of the EE\_WRITE routine will automatically transfer the data in the data array (in RAM) to the next available blank locations in a page. Once the page is filled up with data, the EE\_WRITE routine automatically erases the page and programs updated data in the same page. In a FLASH page, data is programmed to FLASH with in a block that consists of the data array and one boundary byte. The boundary byte contains the remaining number of bytes which can be programmed in the page (see Figure 16-16).

Figure 16-16. EE\_WRITE FLASH Memory Usage