Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                      |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 34MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SCI, SmartCard                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                            |

| Number of I/O              | 83                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 24K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b; D/A 2x8b                                                          |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 120-TQFP                                                                      |

| Supplier Device Package    | 120-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2361vte34v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                             | Page | Revisi                                                           | on (See                                                                                                   | e Manu                      | al fo         | or De          | etails)               |                           |                  |                            |                   |                |                    |

|--------------------------------------------------|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|---------------|----------------|-----------------------|---------------------------|------------------|----------------------------|-------------------|----------------|--------------------|

| 9.13.4 Pin Functions                             | 391  | Table amended                                                    |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  |      | • PF7/6                                                          |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  |      | (Before                                                          | e) PFDE                                                                                                   | $DR \to ($                  | Afte          | r) PF          | 7DDF                  | 3                         |                  |                            |                   |                |                    |

|                                                  | 393  |                                                                  | Table amended                                                                                             |                             |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  |      |                                                                  | 1/ <u>CS5</u> /L                                                                                          |                             |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  |      | r                                                                | 1/035/0                                                                                                   |                             |               |                |                       |                           | -1               |                            |                   |                | -1                 |

|                                                  |      | PF1DDR<br>Pin function                                           | n UCAS<br>output                                                                                          | 0 1<br>PF1 CS<br>input outp | 5 PF          | 1 PF           | 1 PF1                 | 1<br>PF <b>1</b><br>outpu |                  | -                          | 1<br>CSS<br>outpo |                | 1<br>PF1<br>output |

| 14.3.7 Serial Status                             | 558  | Note a                                                           | mendeo                                                                                                    | ł                           |               |                |                       |                           |                  |                            |                   |                |                    |

| Register (SSR)                                   |      | Note:                                                            | * On                                                                                                      | nly 0 ca                    | n be          | writ           | ten, to               | cle                       | ar th            | e flag.                    | Alt               | ernat          | ely,               |

| Normal Serial                                    |      | use the bit clear instruction to clear the flag                  |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

| Communication Interface                          |      |                                                                  |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

| Mode (When SMIF in                               |      |                                                                  |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

| SCMR is 0)                                       | -    |                                                                  |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

| Smart Card Interface                             | 562  | Note amended                                                     |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

| Mode (When SMIF in<br>SCMR is 1)                 |      | Notes: 1. Only 0 can be written, to clear the flag. Alternately, |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  |      |                                                                  | use the bit clear instruction to clear the flag.<br>2. etu: Elementary Time Unit: (time for transfer of 1 |                             |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  |      |                                                                  | 2. etu<br>bit                                                                                             |                             | emer          | ntary          | Time                  | Uni                       | t: (tim          | ne for                     | tran              | sfer           | of 1               |

| 14.0.0 Dit Data Dagiatar                         | 505  | Table                                                            |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

| 14.3.9 Bit Rate Register (BRR)                   | 565  | I able a                                                         | amende                                                                                                    | a                           |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  | _    |                                                                  |                                                                                                           | 8                           |               | Opera<br>9.830 | iting Free            | quenc                     | :уф(МН<br>10     | lz)                        |                   | 12             |                    |

| Table 14.3 BRR Settings<br>for Various Bit Rates | 5    | Bit Rate                                                         |                                                                                                           | Error                       |               | 3.000          | Error                 |                           | 10               | Error                      |                   | 12             | Error              |

| (Asynchronous Mode)                              |      | (bit/s)                                                          | n N                                                                                                       | (%)                         | n             | N              | (%)                   | n                         | N                | (%)                        | n                 | N              | (%)                |

|                                                  |      | 9600<br>19200                                                    | 0 25                                                                                                      | 0.16                        | 0             | 31<br>15       | 0.00                  | 0                         | 32<br>15         | -1.36                      | 0                 | 38<br>19       | 0.16               |

|                                                  |      | 31250                                                            | 0 12                                                                                                      | 0.00                        | 0             | 9              | -1.70                 | 0                         | 9                | 0.00                       | 0                 | 19             | 0.00               |

|                                                  |      | 38400                                                            |                                                                                                           | _                           | 0             | 7              | 0.00                  | 0                         | 7                | -1.73                      | 0                 | 9              | -2.34              |

|                                                  |      |                                                                  |                                                                                                           |                             |               |                |                       |                           |                  |                            |                   |                |                    |

|                                                  |      |                                                                  |                                                                                                           |                             |               | Onora          | ting Ero              |                           | >>/ ★ /ML        |                            |                   |                |                    |

|                                                  |      |                                                                  | 12.                                                                                                       | 288                         |               | Opera<br>14    | ting Free             | quenc                     | ≿yφ(MH<br>14.74  |                            |                   | 16             |                    |

|                                                  |      | Bit Rate                                                         |                                                                                                           | Error                       |               | 14             | Error                 |                           | 14.74            | 56<br>Error                |                   | -              | Error              |

|                                                  |      | (bit/s)                                                          | n N                                                                                                       | Error<br>(%)                | <b>n</b>      | 14<br>N        | Error<br>(%)          | n                         | 14.74<br>N       | 56<br>Error<br>(%)         | <b>n</b>          | N              | (%)                |

|                                                  |      |                                                                  |                                                                                                           | Error                       | <b>n</b><br>0 | 14             | Error                 |                           | 14.74            | 56<br>Error                | <b>n</b><br>0     | -              |                    |

|                                                  |      | (bit/s)<br>9600                                                  | <b>n N</b><br>0 39                                                                                        | Error<br>(%)<br>0.00        | 0             | 14<br>N<br>45  | Error<br>(%)<br>-0.93 | <b>n</b><br>0             | 14.74<br>N<br>47 | 56<br>Error<br>(%)<br>0.00 | 0                 | <b>N</b><br>51 | <b>(%)</b><br>0.16 |

# Section 2 CPU

The H8S/2000 CPU is a high-speed central processing unit with an internal 32-bit architecture that is upward-compatible with the H8/300 and H8/300H CPUs. The H8S/2000 CPU has sixteen 16-bit general registers, can address a 16-Mbyte linear address space, and is ideal for realtime control.

This section describes the H8S/2000 CPU. The usable modes and address spaces differ depending on the product. For details on each product, refer to section 3, MCU Operating Modes.

## 2.1 Features

- Upward-compatibility with H8/300 and H8/300H CPUs

- Can execute H8/300 and H8/300H CPU object programs

- General-register architecture

- Sixteen 16-bit general registers also usable as sixteen 8-bit registers or eight 32-bit registers

- Sixty-five basic instructions

- 8/16/32-bit arithmetic and logic instructions

- Multiply and divide instructions

- Powerful bit-manipulation instructions

- Eight addressing modes

- Register direct [Rn]

- Register indirect [@ERn]

- Register indirect with displacement [@(d:16,ERn) or @(d:32,ERn)]

- Register indirect with post-increment or pre-decrement [@ERn+ or @-ERn]

- Absolute address [@aa:8, @aa:16, @aa:24, or @aa:32]

- Immediate [#xx:8, #xx:16, or #xx:32]

- Program-counter relative [@(d:8,PC) or @(d:16,PC)]

- Memory indirect [@@aa:8]

- 16-Mbyte address space

- Program: 16 Mbytes

- Data: 16 Mbytes

- High-speed operation

- All frequently-used instructions are executed in one or two states

- 8/16/32-bit register-register add/subtract: 1 state

- 8 × 8-bit register-register multiply: 12 states (MULXU.B), 13 states (MULXS.B)

- 16 ÷ 8-bit register-register divide: 12 states (DIVXU.B)

| Table 2.4   | Arithmeti          | ic Operations Instructions                                                                                                                                                                                                                            |  |  |  |  |  |

|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Instruction | Size <sup>*1</sup> | Function                                                                                                                                                                                                                                              |  |  |  |  |  |

| ADD         | B/W/L              | $Rd \pm Rs \to Rd,  Rd \pm \#IMM \to Rd$                                                                                                                                                                                                              |  |  |  |  |  |

| SUB         |                    | Performs addition or subtraction on data in two general registers, or on immediate data and data in a general register. (Subtraction on immediate data and data in a general register cannot be performed in bytes. Use the SUBX or ADD instruction.) |  |  |  |  |  |

| ADDX        | В                  | $Rd \pm Rs \pm C \to Rd,  Rd \pm \#IMM \pm C \to Rd$                                                                                                                                                                                                  |  |  |  |  |  |

| SUBX        |                    | Performs addition or subtraction with carry on data in two general registers, or on immediate data and data in a general register.                                                                                                                    |  |  |  |  |  |

| INC         | B/W/L              | $Rd \pm 1 \rightarrow Rd, Rd \pm 2 \rightarrow Rd$                                                                                                                                                                                                    |  |  |  |  |  |

| DEC         |                    | Adds or subtracts the value 1 or 2 to or from data in a general register.<br>(Only the value 1 can be added to or subtracted from byte operands.)                                                                                                     |  |  |  |  |  |

| ADDS        | L                  | $Rd \pm 1 \to Rd,  Rd \pm 2 \to Rd,  Rd \pm 4 \to Rd$                                                                                                                                                                                                 |  |  |  |  |  |

| SUBS        |                    | Adds or subtracts the value 1, 2, or 4 to or from data in a 32-bit register.                                                                                                                                                                          |  |  |  |  |  |

| DAA         | В                  | Rd (decimal adjust) $\rightarrow$ Rd                                                                                                                                                                                                                  |  |  |  |  |  |

| DAS         |                    | Decimal-adjusts an addition or subtraction result in a general register by referring to CCR to produce 4-bit BCD data.                                                                                                                                |  |  |  |  |  |

| MULXU       | B/W                | $Rd \times Rs \to Rd$                                                                                                                                                                                                                                 |  |  |  |  |  |

|             |                    | Performs unsigned multiplication on data in two general registers: either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16 bits $\rightarrow$ 32 bits.                                                                             |  |  |  |  |  |

| MULXS       | B/W                | $Rd \times Rs \to Rd$                                                                                                                                                                                                                                 |  |  |  |  |  |

|             |                    | Performs signed multiplication on data in two general registers: either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16 bits $\rightarrow$ 32 bits.                                                                               |  |  |  |  |  |

| DIVXU       | B/W                | $Rd \div Rs \to Rd$                                                                                                                                                                                                                                   |  |  |  |  |  |

|             |                    | Performs unsigned division on data in two general registers: either 16 bits $\div$ 8 bits $\rightarrow$ 8-bit quotient and 8-bit remainder or 32 bits $\div$ 16 bits $\rightarrow$ 16-bit quotient and 16-bit remainder.                              |  |  |  |  |  |

Section 2 CPU

| Size* | Function                                                                                                                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В     | $C \oplus (<\!bit-No.\!> of <\!\mathsf{EAd\!\!>) \to C}$                                                                                                                                                               |

|       | Logically exclusive-ORs the carry flag with a specified bit in a general register or memory operand and stores the result in the carry flag.                                                                           |

| В     | $C \oplus \sim (<\!bit\!-\!No.\!> of <\!\mathsf{EAd\!\!>}) \to C$                                                                                                                                                      |

|       | Logically exclusive-ORs the carry flag with the inverse of a specified bit<br>in a general register or memory operand and stores the result in the<br>carry flag. The bit number is specified by 3-bit immediate data. |

| В     | $(\text{sti-No.} \text{ of } \text{}) \rightarrow C$                                                                                                                                                                   |

|       | Transfers a specified bit in a general register or memory operand to the carry flag.                                                                                                                                   |

| В     | ~ ( <bit-no.> of <ead>) <math>\rightarrow</math> C</ead></bit-no.>                                                                                                                                                     |

|       | Transfers the inverse of a specified bit in a general register or memory operand to the carry flag. The bit number is specified by 3-bit immediate data.                                                               |

| В     | $C \rightarrow (\text{-bit-No.> of -EAd>})$                                                                                                                                                                            |

|       | Transfers the carry flag value to a specified bit in a general register or memory operand.                                                                                                                             |

| В     | $\sim C \rightarrow (\langle bit-No. \rangle. of \langle EAd \rangle)$                                                                                                                                                 |

|       | Transfers the inverse of the carry flag value to a specified bit in a general register or memory operand. The bit number is specified by 3-bit immediate data.                                                         |

|       | B<br>B<br>B<br>B                                                                                                                                                                                                       |

B: Byte

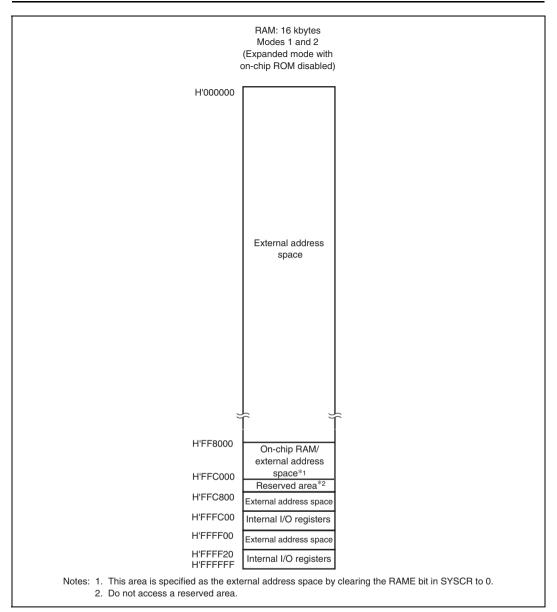

Figure 3.15 H8S/2363 Memory Map

## 6.3.5 CS Assertion Period Control Registers H, L (CSACRH, CSACRL)

CSACRH and CSACRL select whether or not the assertion period of the basic bus interface chip select signals ( $\overline{\text{CSn}}$ ) and address signals is to be extended. Extending the assertion period of the  $\overline{\text{CSn}}$  and address signals allows flexible interfacing to external I/O devices.

#### • CSACRH

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                        |

|-----|----------|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CSXH7    | 0             | R/W | CS and Address Signal Assertion Period Control                                                                                     |

| 6   | CSXH6    | 0             | R/W | 1                                                                                                                                  |

| 5   | CSXH5    | 0             | R/W | These bits specify whether or not the T, cycle is                                                                                  |

| 4   | CSXH4    | 0             | R/W | to be inserted (see figure 6.3). When an area for                                                                                  |

| 3   | CSXH3    | 0             | R/W | which the CSXHn bit is set to 1 is accessed, a                                                                                     |

| 2   | CSXH2    | 0             | R/W | one-state $T_{\rm b}$ cycle, in which only the $\overline{\rm CSn}$ and                                                            |

| 1   | CSXH1    | 0             | R/W | address signals are asserted, is inserted before                                                                                   |

| 0   | CSXH0    | 0             | R/W | the normal access cycle.                                                                                                           |

|     |          |               |     | 0: In area n basic bus interface access, the $\overline{\text{CSn}}$ and address assertion period $(T_{\text{h}})$ is not extended |

|     |          |               |     | 1: In area n basic bus interface access, the $\overline{\text{CSn}}$ and address assertion period $(T_{_h})$ is extended           |

|     |          |               |     | (n = 7 to 0)                                                                                                                       |

CSACRL

| Bit | Bit Name | Initial Value | R/W | Description                                                                                              |

|-----|----------|---------------|-----|----------------------------------------------------------------------------------------------------------|

| 7   | CSXT7    | 0             | R/W | CS and Address Signal Assertion Period Control                                                           |

| 6   | CSXT6    | 0             | R/W | 2                                                                                                        |

| 5   | CSXT5    | 0             | R/W | These bits specify whether or not the T, cycle                                                           |

| 4   | CSXT4    | 0             | R/W | shown in figure 6.3 is to be inserted. When an                                                           |

| 3   | CSXT3    | 0             | R/W | area for which the CSXTn bit is set to 1 is                                                              |

| 2   | CSXT2    | 0             | R/W | accessed, a one-state T, cycle, in which only the                                                        |

| 1   | CSXT1    | 0             | R/W | CSn and address signals are asserted, is                                                                 |

| 0   | CSXT0    | 0             | R/W | inserted after the normal access cycle.                                                                  |

|     |          |               |     | 0: In area n basic bus interface access, the CSn<br>and address assertion period (T,) is not<br>extended |

|     |          |               |     | 1: In area n basic bus interface access, the CSn and address assertion period (T,) is extended           |

|     |          |               |     | (n = 7 to 0)                                                                                             |

## 6.4.2 Bus Specifications

The external space bus specifications consist of five elements: bus width, number of access states, number of program wait states, read strobe timing, and chip select ( $\overline{CS}$ ) assertion period extension states. The bus width and number of access states for on-chip memory and internal I/O registers are fixed, and are not affected by the bus controller.

**Bus Width:** A bus width of 8 or 16 bits can be selected with ABWCR. An area for which an 8-bit bus is selected functions as an 8-bit access space, and an area for which a 16-bit bus is selected functions as a 16-bit access space. If all areas are designated as 8-bit access space, 8-bit bus mode is set; if any area is designated as 16-bit access space, 16-bit bus mode is set.

**Number of Access States:** Two or three access states can be selected with ASTCR. An area for which 2-state access is selected functions as a 2-state access space, and an area for which 3-state access is selected functions as a 3-state access space. With the DRAM interface and burst ROM interface, the number of access states may be determined without regard to the setting of ASTCR.

When 2-state access space is designated, wait insertion is disabled. When 3-state access space is designated, it is possible to insert program waits by means of the WTCRA and WTCRB, and external waits by means of the  $\overline{WAIT}$  pin.

**Number of Program Wait States:** When 3-state access space is designated by ASTCR, the number of program wait states to be inserted automatically is selected with WTCRA and WTCRB. From 0 to 7 program wait states can be selected. Table 6.2 shows the bus specifications (bus width, and number of access states and program wait states) for each basic bus interface area.

#### 7.3.4 DMA Control Registers (DMACRA and DMACRB)

DMACR controls the operation of each DMAC channel.

The DMA has four DMACR registers: DMACR\_0A in channel 0 (channel 0A), DMACR\_0B in channel 0 (channel 0B), DMACR\_1A in channel 1 (channel 1A), and DMACR\_1B in channel 1 (channel 1B).

In short address mode, channels A and B operate independently, and in full address mode, channels A and B operate together. The bit functions in the DMACR registers differ according to the transfer mode.

#### **Short Address Mode:**

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DTSZ     | 0             | R/W | Data Transfer Size<br>Selects the size of data to be transferred at one<br>time.<br>0: Byte-size transfer<br>1: Word-size transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | DTID     | 0             | R/W | <ul> <li>Data Transfer Increment/Decrement</li> <li>Selects incrementing or decrementing of MAR after every data transfer in sequential mode or repeat mode. In idle mode, MAR is neither incremented nor decremented.</li> <li>0: MAR is incremented after a data transfer</li> <li>When DTSZ = 0, MAR is incremented by 1</li> <li>When DTSZ = 1, MAR is incremented by 2</li> <li>1: MAR is decremented after a data transfer</li> <li>When DTSZ = 0, MAR is decremented by 1</li> <li>When DTSZ = 1, MAR is decremented by 1</li> <li>When DTSZ = 1, MAR is decremented by 1</li> <li>When DTSZ = 1, MAR is decremented by 1</li> </ul> |

| 5   | RPE      | 0             | R/W | <ul> <li>Repeat Enable</li> <li>Used in combination with the DTIE bit in</li> <li>DMABCR to select the mode (sequential, idle, or repeat) in which transfer is to be performed.</li> <li>When DTIE = 0 (no transfer end interrupt)</li> <li>0: Transfer in sequential mode</li> <li>1: Transfer in repeat mode</li> <li>When DTIE = 1 (with transfer end interrupt)</li> <li>0: Transfer in sequential mode</li> <li>1: Transfer in sequential mode</li> <li>1: Transfer in sequential mode</li> <li>1: Transfer in sequential mode</li> </ul>                                                                                              |

• DMACR\_0A, DMACR\_0B, DMACR\_1A, and DMARC\_1B

#### Rev.6.00 Mar. 18, 2009 Page 219 of 980 REJ09B0050-0600

| Bit | Bit Name | Initial Value | R/W | Description                                                                                                                                                                                                                                                                   |

|-----|----------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12  | SAE0     | 0             | R/W | Single Address Enable 0                                                                                                                                                                                                                                                       |

|     |          |               |     | Specifies whether channel 0B is to be used for<br>transfer in dual address mode or single address<br>mode. This bit is invalid in full address mode.                                                                                                                          |

|     |          |               |     | 0: Dual address mode                                                                                                                                                                                                                                                          |

|     |          |               |     | 1: Single address mode                                                                                                                                                                                                                                                        |

| 11  | DTA1B    | 0             | R/W | Data Transfer Acknowledge 1B                                                                                                                                                                                                                                                  |

| 10  | DTA1A    | 0             | R/W | Data Transfer Acknowledge 1A                                                                                                                                                                                                                                                  |

| 9   | DTA0B    | 0             | R/W | Data Transfer Acknowledge 0B                                                                                                                                                                                                                                                  |

| 8   | DTA0A    | 0             | R/W | Data Transfer Acknowledge 0A                                                                                                                                                                                                                                                  |

|     |          |               |     | These bits enable or disable clearing when DMA transfer is performed for the internal interrupt source selected by the DTF3 to DTF0 bits in DMACR.                                                                                                                            |

|     |          |               |     | It the DTA bit is set to 1 when DTE = 1, the internal interrupt source is cleared automatically by DMA transfer. When DTE = 1 and DTA = 1, the internal interrupt source does not issue an interrupt request to the CPU or DTC.                                               |

|     |          |               |     | If the DTA bit is cleared to 0 when $DTE = 1$ , the internal interrupt source is not cleared when a transfer is performed, and can issue an interrupt request to the CPU or DTC in parallel. In this case, the interrupt source should be cleared by the CPU or DTC transfer. |

|     |          |               |     | When DTE = 0, the internal interrupt source issues an interrupt request to the CPU or DTC regardless of the DTA bit setting.                                                                                                                                                  |

## 8.3 Activation Sources

The DTC operates when activated by an interrupt or by a write to DTVECR by software. An interrupt request can be directed to the CPU or DTC, as designated by the corresponding DTCER bit. At the end of a data transfer (or the last consecutive transfer in the case of chain transfer), the activation source or corresponding DTCER bit is cleared. The activation source flag, in the case of RXI0, for example, is the RDRF flag of SCI\_0.

When an interrupt has been designated a DTC activation source, existing CPU mask level and interrupt controller priorities have no effect. If there is more than one activation source at the same time, the DTC operates in accordance with the default priorities.

Table 8.1 shows the relationship between the activation sources and DTCER clearing, and figure 8.2 shows a block diagram of activation source control. For details see section 5, Interrupt Controller.

| Activation Source          | DISEL = 0 and Specified<br>Number of Transfers Has<br>Not Ended                                                        | DISEL = 1 or Specified Number<br>of Transfers Has Ended                                                                                                                                      |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Activation by software     | SWDTE bit is cleared to 0                                                                                              | <ul><li>SWDTE bit remains set to 1</li><li>Interrupt request to CPU</li></ul>                                                                                                                |

| Activation by an interrupt | <ul> <li>Corresponding DTCER bit<br/>remains set to 1.</li> <li>Activation source flag is<br/>cleared to 0.</li> </ul> | <ul> <li>Corresponding DTCER bit is cleared to 0.</li> <li>Activation source flag remains set to 1.</li> <li>Interrupt that became the activation source is requested to the CPU.</li> </ul> |

| Table 8.1 | <b>Relationship between</b> | Activation Sources and DTCER Clearing |

|-----------|-----------------------------|---------------------------------------|

|-----------|-----------------------------|---------------------------------------|

## 9.3.2 Port 3 Data Register (P3DR)

P3DR stores output data for the port 3 pins.

| Bit  | Bit Name | Initial Value | R/W | Description                                             |

|------|----------|---------------|-----|---------------------------------------------------------|

| 7, 6 | _        | All 0         |     | Reserved                                                |

|      |          |               |     | These bits are always read as 0 and cannot be modified. |

| 5    | P35DR    | 0             | R/W | Output data for a pin is stored when the pin function   |

| 4    | P34DR    | 0             | R/W | is specified to a general purpose I/O.                  |

| 3    | P33DR    | 0             | R/W |                                                         |

| 2    | P32DR    | 0             | R/W |                                                         |

| 1    | P31DR    | 0             | R/W |                                                         |

| 0    | P30DR    | 0             | R/W |                                                         |

#### 9.3.3 Port 3 Register (PORT3)

PORT3 shows the pin states.

PORT3 cannot be modified.

| Bit  | Bit Name | Initial Value | R/W | Description                                                                                              |

|------|----------|---------------|-----|----------------------------------------------------------------------------------------------------------|

| 7, 6 | _        | All 0         | _   | Reserved                                                                                                 |

|      |          |               |     | These bits are always read as 0 and cannot be modified.                                                  |

| 5    | P35      | *             | R   | If a port 3 read is performed while P3DDR bits are                                                       |

| 4    | P34      | *             | R   | set to 1, the P3DR values are read. If a port 1 read is performed while P3DDR bits are cleared to 0, the |

| 3    | P33      | *             | R   | pin states are read.                                                                                     |

| 2    | P32      | *             | R   |                                                                                                          |

| 1    | P31      | *             | R   |                                                                                                          |

| 0    | P30      | *             | R   |                                                                                                          |

Note: \* Determined by the states of pins P35 to P30.

## 9.7 Port 9

Port 9 is a 2-bit input-only port. Port 9 has the following register.

• Port 9 register (PORT9)

#### 9.7.1 Port 9 Register (PORT9)

PORT9 is an 8-bit read-only register that shows port 4 pin states.

PORT9 cannot be modified.

| Bit  | Bit Name | Initial Value | R/W | Description                                       |  |  |  |  |

|------|----------|---------------|-----|---------------------------------------------------|--|--|--|--|

| 7, 6 | _        | Undefined     | R   | Reserved                                          |  |  |  |  |

|      |          |               |     | If read they will return an undefined value.      |  |  |  |  |

| 5    | P95      | *             | R   | The pin states are always read when a port 9 read |  |  |  |  |

| 4    | P94      | *             | R   | is performed.                                     |  |  |  |  |

| 3    | _        | Undefined     | R   | Reserved                                          |  |  |  |  |

| 2    | _        | Undefined     | R   | If read they will return an undefined value.      |  |  |  |  |

| 1    | _        | Undefined     | R   |                                                   |  |  |  |  |

| 0    | _        | Undefined     | R   |                                                   |  |  |  |  |

Note: \* Determined by the states of pins P95 and P94.

#### 9.7.2 Pin Functions

Port 9 also functions as the pins for A/D converter analog input and D/A converter analog output. The correspondence between pins are as follows.

#### P95/AN13/DA3

| Pin function | AN13 input |

|--------------|------------|

|              | DA3 output |

#### P94/AN12/DA2

| Pin function | AN12 input |

|--------------|------------|

|              | DA2 output |

#### 10.3.6 Timer Counter (TCNT)

The TCNT registers are 16-bit readable/writable counters. The TPU has six TCNT counters, one for each channel.

The TCNT counters are initialized to H'0000 by a reset, or in hardware standby mode.

The TCNT counters cannot be accessed in 8-bit units; they must always be accessed as a 16-bit unit.

## 10.3.7 Timer General Register (TGR)

The TGR registers are 16-bit readable/writable registers with a dual function as output compare and input capture registers. The TPU has 16 TGR registers, four each for channels 0 and 3 and two each for channels 1, 2, 4, and 5. TGRC and TGRD for channels 0 and 3 can also be designated for operation as buffer registers. The TGR registers cannot be accessed in 8-bit units; they must always be accessed as a 16-bit unit. TGR buffer register combinations are TGRA–TGRC and TGRB–TGRD.

### 10.3.8 Timer Start Register (TSTR)

TSTR selects operation/stoppage for channels 0 to 5. When setting the operating mode in TMDR or setting the count clock in TCR, first stop the TCNT counter.

| Bit              | Bit Name                     | Initial value      | R/W        | Description                                                                                                                                                                                                                                                                                                       |

|------------------|------------------------------|--------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6             | _                            | All 0              | _          | Reserved                                                                                                                                                                                                                                                                                                          |

|                  |                              |                    |            | The write value should always be 0.                                                                                                                                                                                                                                                                               |

| 5                | CST5                         | 0                  | R/W        | Counter Start 5 to 0                                                                                                                                                                                                                                                                                              |

| 4                | CST4                         | 0                  | R/W        | These bits select operation or stoppage for TCNT.                                                                                                                                                                                                                                                                 |

| 3<br>2<br>1<br>0 | CST3<br>CST2<br>CST1<br>CST0 | 2 0 R/W<br>1 0 R/W | R/W<br>R/W | If 0 is written to the CST bit during operation with<br>the TIOC pin designated for output, the counter<br>stops but the TIOC pin output compare output level<br>is retained. If TIOR is written to when the CST bit is<br>cleared to 0, the pin output level will be changed to<br>the set initial output value. |

|                  |                              |                    |            | 0: TCNT_5 to TCNT_0 count operation is stopped<br>1: TCNT_5 to TCNT_0 performs count operation                                                                                                                                                                                                                    |

## 11.4.3 Example of Normal Pulse Output (Example of Five-Phase Pulse Output)

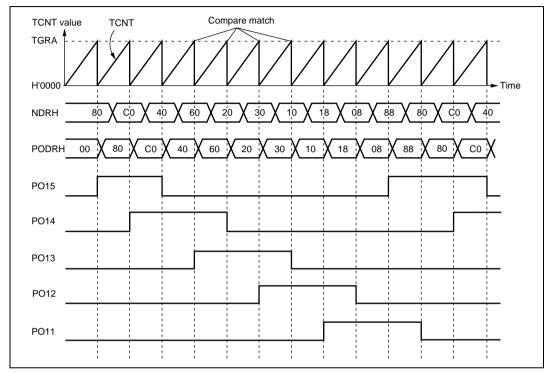

Figure 11.5 shows an example in which pulse output is used for cyclic five-phase pulse output.

Figure 11.5 Normal Pulse Output Example (Five-Phase Pulse Output)

- 1. Set up TGRA in TPU which is used as the output trigger to be an output compare register. Set a cycle in TGRA so the counter will be cleared by compare match A. Set the TGIEA bit in TIER to 1 to enable the compare match/input capture A (TGIA) interrupt.

- 2. Write H'F8 in P1DDR and NDERH, and set the G3CMS1, G3CMS0, G2CMS1, and G2CMS0 bits in PCR to select compare match in the TPU channel set up in the previous step to be the output trigger. Write output data H'80 in NDRH.

- 3. The timer counter in the TPU channel starts. When compare match A occurs, the NDRH contents are transferred to PODRH and output. The TGIA interrupt handling routine writes the next output data (H'C0) in NDRH.

- 4. Five-phase pulse output (one or two phases active at a time) can be obtained subsequently by writing H'40, H'60, H'20, H'30, H'10, H'18, H'08, H'88... at successive TGIA interrupts.

# 14.9 SCI Interrupts

## 14.9.1 Interrupts in Normal Serial Communication Interface Mode

Table 14.13 shows the interrupt sources in normal serial communication interface mode. A different interrupt vector is assigned to each interrupt source, and individual interrupt sources can be enabled or disabled using the enable bits in SCR.

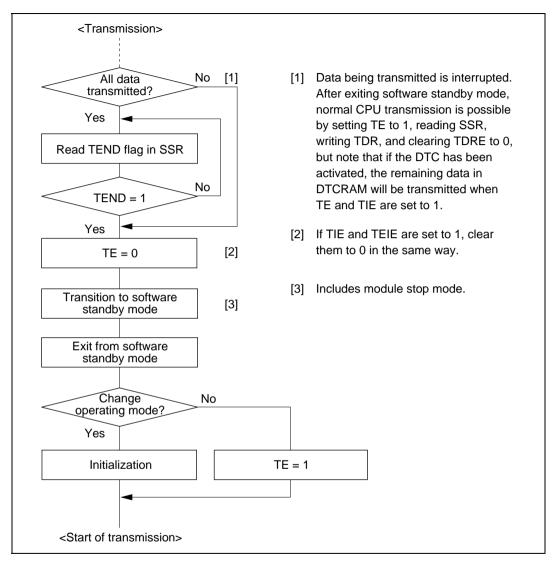

When the TDRE flag in SSR is set to 1, a TXI interrupt request is generated. When the TEND flag in SSR is set to 1, a TEI interrupt request is generated. A TXI interrupt can activate the DTC or DMAC to perform data transfer. The TDRE flag is cleared to 0 automatically when data transfer is performed by the DTC or DMAC.

When the RDRF flag in SSR is set to 1, an RXI interrupt request is generated. When the ORER, PER, or FER flag in SSR is set to 1, an ERI interrupt request is generated. An RXI interrupt request can activate the DTC or DMAC to perform data transfer. The RDRF flag is cleared to 0 automatically when data transfer is performed by the DTC or DMAC.

A TEI interrupt is generated when the TEND flag is set to 1 while the TEIE bit is set to 1. If a TEI interrupt and a TXI interrupt are generated simultaneously, the TXI interrupt has priority for acceptance. However, note that if the TDRE and TEND flags are cleared simultaneously by the TXI interrupt routine, the SCI cannot branch to the TEI interrupt routine later.

## Table 19.5Boot Mode Operation

| Item                                                       | Host Operation                                                                                                                                        | Communication Contents                                   | LSI Operation                                                                                                                                                                                                                                               |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ite                                                        | Processing Contents                                                                                                                                   |                                                          | Processing Contents                                                                                                                                                                                                                                         |

| Boot mode initiation                                       |                                                                                                                                                       |                                                          | Branches to boot program at reset-start.                                                                                                                                                                                                                    |

| Bit rate adjustment                                        | Continuously transmits data H'00<br>at specified bit rate.                                                                                            | H'00, H'00 · · · H'00<br>H'00<br>H'55<br>H'AA            | <ul> <li>Measures low-level period of receive data H'00.</li> <li>Calculates bit rate and sets BRR in SCI_1.</li> <li>Transmits data H'00 to host as adjustment end indication.</li> <li>Transmits data H'AA to host when data H'55 is received.</li> </ul> |

| Transfer of number of bytes of programming control program | Transmits number of bytes (N) of<br>programming control program to be<br>transferred as 2-byte data<br>(low-order byte following high-order<br>byte). | Upper bytes, lower bytes<br>Echoback<br>H'XX<br>Echoback | Echobacks the 2-byte data<br>received to host.<br>Echobacks received data to host and also<br>transfers it to RAM.<br>(repeated for N times)                                                                                                                |

| Flash memory erase                                         | Boot program<br>erase error<br>H'AA reception.                                                                                                        | H'FF<br>H'AA                                             | <ul> <li>Checks flash memory data, erases all flash memory blocks in case of written data existing, and transmits data H'AA to host. (If erase could not be done, transmits data H'FF to host and aborts operation.)</li> </ul>                             |

|                                                            |                                                                                                                                                       |                                                          | Branches to programming control program transferred to on-chip RAM and starts execution.                                                                                                                                                                    |

• Flash Transfer Destination Address Register (FTDAR)

FTDAR is a register that specify the address to download an on-chip program. This register must be specified before setting the SCO bit in FCCS to 1.

| Bit              | Bit<br>Name                                                                                                                               | Initial<br>Value | R/W        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7                | TDER                                                                                                                                      | 0                | R/W        | Transfer Destination Address Setting Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                  |                                                                                                                                           |                  |            | This bit is set to 1 when the address specified by bits<br>TDA6 to TDA0, which is the start address to download a<br>on-chip program, is over the range. Whether or not the<br>range specified by bits TDA6 to TDA0 is within the range<br>of H'00 to H'03 is determined when an on-chip program<br>downloaded by setting the SCO bit in FCCS. Make sure<br>that this bit is cleared to 0 before setting the SCO bit to<br>and the value specified by TDA6 to TDA0 is within the<br>range of H'00 to H'03. |  |  |  |  |

|                  |                                                                                                                                           |                  |            | 0: The value specified by bits TDA6 to TDA0 is within the range.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                  |                                                                                                                                           |                  |            | <ol> <li>The value specified by is TDA6 to TDA0 is over the<br/>range (H'04 to H'FF) and the download is stopped.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 6 TDA6 0 R/W     |                                                                                                                                           |                  |            | Transfer Destination Address<br>Specifies the start address to download an on-chip<br>program. H'00 to H'03 can be specified meaning that the<br>start address in the on-chip RAM space can be specified<br>in units of 4 kbytes.                                                                                                                                                                                                                                                                          |  |  |  |  |

| 5<br>4<br>3<br>2 | TDA5         0         R/W           TDA4         0         R/W           TDA3         0         R/W           TDA2         0         R/W |                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 1<br>0           | TDA1<br>TDA0                                                                                                                              | -                | R/W<br>R/W | H'00: H'FF9000 is specified as a start address to<br>download an on-chip program.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  |                                                                                                                                           |                  |            | H'01: H'FFA000 is specified as a start address to<br>download an on-chip program.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  |                                                                                                                                           |                  |            | H'02: H'FFB000 is specified as a start address to<br>download an on-chip program.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  |                                                                                                                                           |                  |            | H'03: H'FF8000 is specified as a start address to<br>download an on-chip program.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  |                                                                                                                                           |                  |            | H'04 to H'07: Setting prohibited. Specifying this value sets the TDRE bit to 1 and stops the download.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

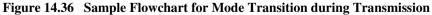

Figure 20.14 Procedure for Erasing User MAT in User Boot Mode

The difference between the erasing procedures in user program mode and user boot mode depends on whether the MAT is switched or not as shown in figure 20.14.

MAT switching is enabled by writing a specific value to FMATS. However note that while the MATs are being switched, the LSI is in an unstable state, e.g. access to a MAT is not allowed until MAT switching is completed, and if an interrupt occurs, from which MAT the interrupt vector is read is undetermined. Perform MAT switching in accordance with the description in section 20.6, Switching between User MAT and User Boot MAT.

Except for MAT switching, the erasing procedure is the same as that in user program mode.

| Instruction                | 1           | 2                                   | 3                     | 4                                   | 5                | 6      | 7 | 8 | 9 |

|----------------------------|-------------|-------------------------------------|-----------------------|-------------------------------------|------------------|--------|---|---|---|

| EXTS.W Rd                  | R:W<br>NEXT |                                     |                       | Repeated<br>times <sup>*1</sup>     | d for n          |        |   |   |   |

| EXTS.L ERd                 | R:W<br>NEXT |                                     |                       | _                                   |                  |        |   |   |   |

| EXTU.W Rd                  | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |

| EXTU.L ERd                 | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |

| INC.B Rd                   | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |

| INC.W<br>#1/2,Rd           | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |

| INC.L<br>#1/2,ERd          | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |

| JMP @ERn                   | R:W<br>NEXT | R:W EA                              |                       |                                     |                  |        |   |   |   |

| JMP @aa:24                 | R:W 2nd     | 1 state of<br>internal<br>operation | R:W EA                |                                     |                  |        |   |   |   |

| JMP Advanced<br>@@aa<br>:8 | R:W<br>NEXT | R:W:M<br>aa:8                       | R:W<br>aa:8           | 1 state of<br>internal<br>operation | R:W EA           |        |   |   |   |

| JSR Advanced<br>@ERn       | R:W<br>NEXT | R:W EA                              | W:W:M<br>Stack<br>(H) | W:W<br>Stack (L)                    |                  |        |   |   |   |

| JSR Advanced<br>@aa:2<br>4 | R:W 2nd     | 1 state of<br>internal<br>operation | R:W EA                | W:W:M<br>Stack<br>(H)               | W:W<br>Stack (L) |        |   |   |   |

| JSR Advanced<br>@@aa<br>:8 | R:W<br>NEXT | R:W:M<br>aa:8                       | R:W<br>aa:8           | W:W:M<br>Stack<br>(H)               | W:W<br>Stack (L) | R:W EA |   |   |   |

| LDC<br>#xx:8,CCR           | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |

| LDC<br>#xx:8,EXR           | R:W 2nd     | R:W<br>NEXT                         |                       |                                     |                  |        |   |   |   |

| LDC Rs,CCR                 | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |

| LDC Rs,EXR                 | R:W<br>NEXT |                                     |                       |                                     |                  |        |   |   |   |