Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 3                                                                        |

| Program Memory Size        | 448B (256 x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 3x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f320-e-mc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### PIC10(L)F320/322 Family Types

| Device       | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High Endurance Flash (bytes) | I/O'S <sup>(2)</sup> | 8-Bit ADC (ch) | Timers<br>(8-Bit) | PWM | Complementary Wave<br>Generator (CWG) | Configurable Logic<br>Cell (CLC) | Fixed Voltage<br>Reference (FVR) | Numerically Controlled<br>Oscillator (NCO) | Debug <sup>(1)</sup> | XLP |

|--------------|------------------|---------------------------------|----------------------|------------------------------|----------------------|----------------|-------------------|-----|---------------------------------------|----------------------------------|----------------------------------|--------------------------------------------|----------------------|-----|

| PIC10(L)F320 | (1)              | 256                             | 64                   | 128                          | 4                    | 3              | 2                 | 2   | 1                                     | 1                                | 1                                | 1                                          | Н                    | Υ   |

| PIC10(L)F322 | (1)              | 512                             | 64                   | 128                          | 4                    | 3              | 2                 | 2   | 1                                     | 1                                | 1                                | 1                                          | Н                    | Υ   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, Available using Debug Header;

E - Emulation, Available using Emulation Header.

2: One pin is input-only.

### **Data Sheet Index:**

1: DS40001585 PIC10(L)F320/322 Data Sheet, 6/8 Pin High Performance, Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

**TABLE 1-2:** PIC10(L)F320/322 PINOUT DESCRIPTION

| Name                        | Function | Input<br>Type | Output<br>Type | Description                                            |

|-----------------------------|----------|---------------|----------------|--------------------------------------------------------|

| RA0/PWM1/CLC1IN0/CWG1A/     | RA0      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                  |

| AN0/ICSPDAT                 | PWM1     | _             | CMOS           | PWM output.                                            |

|                             | CLC1IN0  | ST            | _              | CLC input.                                             |

|                             | CWG1A    | _             | CMOS           | CWG primary output.                                    |

|                             | AN0      | AN            | _              | A/D Channel input.                                     |

|                             | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                                        |

| RA1/PWM2/CLC1/CWG1B/AN1/    | RA1      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                  |

| CLKIN/ICSPCLK/NCO1CLK       | PWM2     | _             | CMOS           | PWM output.                                            |

|                             | CLC1     | _             | CMOS           | CLC output.                                            |

|                             | CWG1B    | _             | CMOS           | CWG complementary output.                              |

|                             | AN1      | AN            | _              | A/D Channel input.                                     |

|                             | CLKIN    | ST            | _              | External Clock input (EC mode).                        |

|                             | ICSPCLK  | ST            | _              | ICSP™ Programming Clock.                               |

|                             | NCO1CLK  | ST            |                | Numerical Controlled Oscillator external clock input.  |

| RA2/INT/T0CKI/NCO1/CLC1IN1/ | RA2      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                  |

| CLKR/AN2/CWG1FLT            | INT      | ST            |                | External interrupt.                                    |

|                             | T0CKI    | ST            |                | Timer0 clock input.                                    |

|                             | NCO1     |               | CMOS           | Numerically Controlled Oscillator output.              |

|                             | CLC1IN1  | ST            | _              | CLC input.                                             |

|                             | CLKR     |               | CMOS           | Clock Reference output.                                |

|                             | AN2      | AN            | _              | A/D Channel input.                                     |

|                             | CWG1FLT  | ST            | _              | Complementary Waveform Generator Fault 1 source input. |

| RA3/MCLR/VPP                | RA3      | TTL           | _              | General purpose input.                                 |

|                             | MCLR     | ST            | _              | Master Clear with internal pull-up.                    |

|                             | VPP      | HV            | _              | Programming voltage.                                   |

| VDD                         | VDD      | Power         | _              | Positive supply.                                       |

| Vss                         | Vss      | Power         | _              | Ground reference.                                      |

**Legend:** AN = Analog input or output

CMOS = CMOS compatible input or output TTL = CMOS input with TTL levels = CMOS input with Schmitt Trigger levels

HV = High Voltage

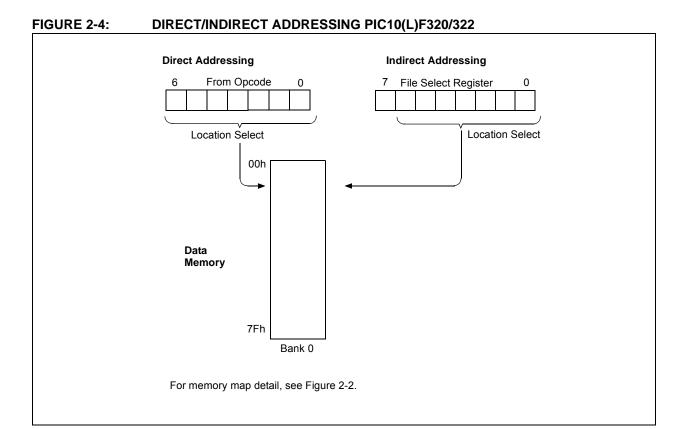

### 2.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- · Program Memory

- Configuration Word

- Device ID

- User ID

- Flash Program Memory

- · Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- · Indirect Addressing

### 2.1 Program Memory Organization

The mid-range core has a 13-bit program counter capable of addressing  $8K \times 14$  program memory space. This device family only implements up to 512 words of the 8K program memory space. Table 2-1 shows the memory sizes implemented for the PIC10(L)F320/322 family. Accessing a location above these boundaries will cause a wrap-around within the implemented memory space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figures 2-1, and 2-2).

TABLE 2-1: DEVICE SIZES AND ADDRESSES

| Device       | Program Memory<br>Space (Words) | Last Program Memory<br>Address | High-Endurance Flash<br>Memory Address Range <sup>(1)</sup> |

|--------------|---------------------------------|--------------------------------|-------------------------------------------------------------|

| PIC10(L)F320 | 256                             | 00FFh                          | 0080h-00FFh                                                 |

| PIC10(L)F322 | 512                             | 01FFh                          | 0180h-01FFh                                                 |

**Note 1:** High-endurance Flash applies to low byte of each address in the range.

### REGISTER 3-1: CONFIG: CONFIGURATION WORD (CONTINUED)

bit 5 **PWRTE**: Power-up Timer Enable bit<sup>(1)</sup>

1 = PWRT disabled0 = PWRT enabled

bit 4-3 WDTE<1:0>: Watchdog Timer Enable bit

11 = WDT enabled

10 = WDT enabled while running and disabled in Sleep

01 = WDT controlled by the SWDTEN bit in the WDTCON register

00 = WDT disabled

bit 2-1 BOREN<1:0>: Brown-out Reset Enable bits

11 = Brown-out Reset enabled; SBOREN bit is ignored

10 = Brown-out Reset enabled while running, disabled in Sleep; SBOREN bit is ignored

01 = Brown-out Reset controlled by the SBOREN bit in the BORCON register

00 = Brown-out Reset disabled; SBOREN bit is ignored

bit 0 FOSC: Oscillator Selection bit

1 = EC on CLKIN pin

0 = INTOSC oscillator I/O function available on CLKIN pin

**Note 1:** Enabling Brown-out Reset does not automatically enable Power-up Timer.

**2:** Once enabled, code-protect can only be disabled by bulk erasing the device.

3: See VBOR parameter for specific trip point voltages.

### 3.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data memory protection are controlled independently. Internal access to the program memory and data memory are unaffected by any code protection setting.

### 3.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word. When  $\overline{CP}=0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See Section 3.4 "Write Protection" for more information.

#### 3.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as boot loader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word define the size of the program memory block that is protected.

### 3.5 User ID

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 3.6 "Device ID and Revision ID"** for more information on accessing these memory locations. For more information on checksum calculation, see the "PIC10(L)F320/322 Flash Memory Programming Specification" (DS41572).

### 4.2 Clock Source Modes

Clock source modes can be classified as external or internal.

- Internal clock source (INTOSC) is contained within the oscillator module, which has eight selectable output frequencies, with a maximum internal frequency of 16 MHz.

- The External Clock mode (EC) relies on an external signal for the clock source.

The system clock can be selected between external or internal clock sources via the FOSC bit of the Configuration Word.

#### 4.3 Internal Clock Modes

The internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate all internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz (LFINTOSC).

The HFINTOSC consists of a primary and secondary clock. The secondary clock starts first with rapid start-up time, but low accuracy. The secondary clock ready signal is indicated with the HFIOFR bit of the OSCCON register. The primary clock follows with slower start-up time and higher accuracy. The primary clock is stable when the HFIOFS bit of the OSCCON register bit goes high.

### 4.3.1 INTOSC MODE

When the FOSC bit of the Configuration Word is cleared, the INTOSC mode is selected. When INTOSC is selected, CLKIN pin is available for general purpose I/O. See **Section 3.0** "**Device Configuration**" for more information.

### 4.3.2 FREQUENCY SELECT BITS (IRCF)

The output of the 16 MHz HFINTOSC is connected to a divider and multiplexer (see Figure 4-1). The Internal Oscillator Frequency Select bits (IRCF) of the OSCCON register select the frequency output of the internal oscillator:

- HFINTOSC

- 16 MHz

- 8 MHz (default after Reset)

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- LFINTOSC

- 31 kHz

**Note:** Following any Reset, the IRCF<2:0> bits of the OSCCON register are set to '110' and the frequency selection is set to 8 MHz. The user can modify the IRCF bits to select a different frequency.

There is no delay when switching between HFINTOSC frequencies with the IRCF bits. This is because the switch involves only a change to the frequency output divider.

Start-up delay specifications are located in **Section 24.0 "Electrical Specifications"**.

### 4.6 External Clock Mode

### 4.6.1 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the CLKIN input.

TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name    | Bit 7 | Bit 6  | Bit 5     | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0  | Register on Page |

|---------|-------|--------|-----------|-------|--------|-------|--------|--------|------------------|

| CLKRCON | _     | CLKROE | _         | _     | _      | _     | _      | _      | 26               |

| OSCCON  | _     |        | IRCF<2:0> |       | HFIOFR | _     | LFIOFR | HFIOFS | 26               |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by ECWG.

#### TABLE 4-2: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name   | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register on Page |

|--------|------|---------|---------|----------|----------|----------|----------|---------|---------|------------------|

| CONFIG | 13:8 | _       | _       | _        | WRT      | <1:0>    | BORV     | LPBOR   | LVP     | 20               |

| CONFIG | 7:0  | CP      | MCLRE   | PWRTE    | WDTE     | <1:0>    | BOREI    | N<1:0>  | FOSC    | 20               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register on Page |

|------------|-------|--------|--------|--------|--------|--------|---------|--------|------------------|

| INTCON     | GIE   | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 40               |

| IOCAF      | _     | _      | _      | _      | IOCAF3 | IOCAF2 | IOCAF1  | IOCAF0 | 76               |

| IOCAN      | _     | _      | _      | _      | IOCAN3 | IOCAN2 | IOCAN1  | IOCAN0 | 75               |

| IOCAP      | -     | _      |        | _      | IOCAP3 | IOCAP2 | IOCAP1  | IOCAP0 | 75               |

| OPTION_REG | WPUEN | INTEDG | T0CS   | T0SE   | PSA    |        | PS<2:0> |        | 95               |

| PIE1       | _     | ADIE   | _      | NCO1IE | CLC1IE | _      | TMR2IE  | _      | 41               |

| PIR1       | _     | ADIF   | _      | NCO1IF | CLC1IF | _      | TMR2IF  | _      | 42               |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupts.

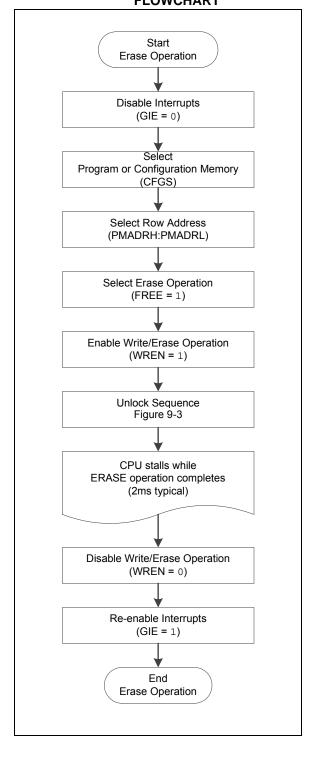

### 9.2.3 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the PMADRH:PMADRL register pair with any address within the row to be erased.

- 2. Clear the CFGS bit of the PMCON1 register.

- Set the FREE and WREN bits of the PMCON1 register.

- 4. Write 55h, then AAh, to PMCON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the PMCON1 register to begin the erase operation.

### See Example 9-2.

After the "BSF PMCON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the PMCON1 write instruction.

FIGURE 9-4: FLASH PROGRAM MEMORY ERASE FLOWCHART

### 10.1 PORTA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 10-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 10-1 shows how to initialize PORTA.

Reading the PORTA register (Register 10-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 10-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### 10.1.1 WEAK PULL-UPS

Each of the PORTA pins has an individually configurable internal weak pull-up. Control bits WPUA<3:0> enable or disable each pull-up (see Register 10-5). Each weak pull-up is automatically turned off when the port pin is configured as an output. All pull-ups are disabled on a Power-on Reset by the WPUEN bit of the OPTION\_REG register.

### 10.1.2 ANSELA REGISTER

The ANSELA register (Register 10-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

### 10.1.3 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 10-1.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 10-1.

TABLE 10-1: PORTA OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RA0      | ICSPDAT                          |

|          | CWG1A                            |

|          | PWM1                             |

|          | RA0                              |

| RA1      | CWG1B                            |

|          | PWM2                             |

|          | CLC1                             |

|          | RA1                              |

| RA2      | NCO1                             |

|          | CLKR                             |

|          | RA2                              |

| RA3      | None                             |

Note 1: Priority listed from highest to lowest.

### 11.6 Interrupt-On-Change Registers

### REGISTER 11-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | _   | IOCAP3  | IOCAP2  | IOCAP1  | IOCAP0  |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 **Unimplemented**: Read as '0'.

bit 3-0 IOCAP<3:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge. (1)

0 = Interrupt-on-Change disabled for the associated pin.

Note 1: Interrupt-on-change also requires that the IOCIE bit of the INTCON register be set (Register 6-1).

### REGISTER 11-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | _   | _   | _   | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |     |     |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-4 **Unimplemented**: Read as '0'.

bit 3-0 IOCAN<3:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge. (1)

0 = Interrupt-on-Change disabled for the associated pin.

Note 1: Interrupt-on-change also requires that the IOCIE bit of the INTCON register be set (Register 6-1).

INPUT DATA SELECTION AND GATING **FIGURE 19-2: Data Selection** CLCxIN[0]-000 CLCxIN[1]-Data GATE 1 CLCxIN[2] CLCxIN[3]lcxd1T LCxD1G1T CLCxIN[4] | CLCxIN[5]lcxd1N LCxD1G1N CLCxIN[6] CLCxIN[7]-111 LCxD2G1T LCxD1S<2:0> LCxD2G1N lcxg1 CLCxIN[0] 000 | CLCxIN[1]-LCxD3G1T CLCxIN[2]-LCxG1POL CLCxIN[3]lcxd2T<sub>1</sub> LCxD3G1N CLCxIN[4]lcxd2N CLCxIN[5]-CLCxIN[6]-LCxD4G1T CLCxIN[7]-LCxD2S<2:0> .CxD4G1N CLCxIN[0]-000 Data GATE 2 CLCxIN[1] CLCxIN[2] -lcxg2 | CLCxIN[3] lcxd3T (Same as Data GATE 1) CLCxIN[4] lcxd3N CLCxIN[5]-CLCxIN[6]-Data GATE 3 CLCxIN[7]--lcxg3 LCxD3S<2:0> (Same as Data GATE 1) CLCxIN[0]-Data GATE 4 000 CLCxIN[1]--lcxg4 CLCxIN[2]-(Same as Data GATE 1) Icxd4T CLCxIN[3]-CLCxIN[4]-Icxd4N CLCxIN[5] CLCxIN[6] CLCxIN[7]-LCxD4S<2:0> Note: All controls are undefined at power-up.

# 21.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces a complementary waveform with dead-band delay from a selection of input sources.

The CWG module has the following features:

- · Selectable dead-band clock source control

- · Selectable input sources

- · Output enable control

- Output polarity control

- Dead-band control with Independent 6-bit rising and falling edge dead-band counters

- · Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart enable

- Auto-shutdown pin override control

### 21.1 Fundamental Operation

The CWG generates a two output complementary waveform from one of four selectable input sources.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby, creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 21.5 "Dead-Band Control"**. A typical operating waveform, with dead band, generated from a single input signal is shown in Figure 21-2.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in **Section 21.9 "Auto-shutdown Control"**.

### 21.2 Clock Source

The CWG module allows the following clock sources to be selected:

- · Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the G1CS0 bit of the CWGxCON0 register (Register 21-1).

### 21.3 Selectable Input Sources

The CWG can generate the complementary waveform for the following input sources:

- PWM1

- PWM2

- N1OUT

- LC1OUT

The input sources are selected using the GxIS<1:0> bits in the CWGxCON1 register (Register 21-2).

### 21.4 Output Control

Immediately after the CWG module is enabled, the complementary drive is configured with both CWGxA and CWGxB drives cleared.

### 21.4.1 OUTPUT ENABLES

Each CWG output pin has individual output enable control. Output enables are selected with the GxOEA and GxOEB bits of the CWGxCON0 register. When an output enable control is cleared, the module asserts no control over the pin. When an output enable is set, the override value or active PWM waveform is applied to the pin per the port priority selection. The output pin enables are dependent on the module enable bit, GxEN. When GxEN is cleared, CWG output enables and CWG drive levels have no effect.

#### 21.4.2 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the GxPOLA and GxPOLB bits of the CWGxCON0 register.

### 21.5 Dead-Band Control

Dead-band control provides for non-overlapping output signals to prevent shoot-through current in power switches. The CWG contains two 6-bit dead-band counters. One dead-band counter is used for the rising edge of the input source control. The other is used for the falling edge of the input source control.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWGxDBR and CWGxDBF registers (Register 21-4 and Register 21-5, respectively).

### 21.6 Rising Edge Dead Band

The rising edge dead band delays the turn-on of the CWGxA output from when the CWGxB output is turned off. The rising edge dead-band time starts when the rising edge of the input source signal goes true. When this happens, the CWGxB output is immediately turned off and the rising edge dead-band delay time starts. When the rising edge dead-band delay time is reached, the CWGxA output is turned on.

The CWGxDBR register sets the duration of the deadband interval on the rising edge of the input source signal. This duration is from 0 to 64 counts of dead band.

Dead band is always counted off the edge on the input source signal. A count of 0 (zero), indicates that no dead band is present.

If the input source signal is not present for enough time for the count to be completed, no output will be seen on the respective output.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                         |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                        |

| Operation:       | (f) + 1 → (destination),<br>skip if result = 0                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                      |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.  If the result is '1', the next instruction is executed. If the result is '0', a NOP is executed instead, making it a 2-cycle instruction. |

| GОТО             | Unconditional Branch                                                                                                                                                        |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] GOTO k                                                                                                                                                              |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                        |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                             |  |  |

| Status Affected: | None                                                                                                                                                                        |  |  |

| Description:     | GOTO is an unconditional branch. The 11-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a 2-cycle instruction. |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] IORLW k                                                                                            |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                          |  |  |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                 |  |  |

| Status Affected: | Z                                                                                                            |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |

| INCF             | Increment f                                                                                                                                                    |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] INCF f,d                                                                                                                                             |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                             |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                            |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                           |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                             |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                        |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |

### 24.4 Thermal Considerations

Standard Operating Conditions (unless otherwise stated)

| Param<br>No. | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |

|--------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|

| TH01         | θЈА       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 6-pin SOT-23 package                                     |

|              |           |                                        | 80   | °C/W  | 8-pin PDIP package                                       |

|              |           |                                        | 90   | °C/W  | 8-pin DFN package                                        |

| TH02         | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 6-pin SOT-23 package                                     |

|              |           |                                        | 24   | °C/W  | 8-pin PDIP package                                       |

|              |           |                                        | 24   | °C/W  | 8-pin DFN package                                        |

| TH03         | ТЈМАХ     | Maximum Junction Temperature           | 150  | °C    |                                                          |

| TH04         | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |

| TH05         | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06         | Pı/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | PDER      | Derated Power                          | _    | W     | PDER = PDMAX (TJ - TA)/θJA <sup>(2)</sup>                |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

- 2: TA = Ambient Temperature

- 3: TJ = Junction Temperature

#### 24.5 **AC Characteristics**

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т                                          |   |      |

|--------------------------------------------|---|------|

| F Frequency                                | Т | Time |

| Lowercase letters (pp) and their meanings: |   |      |

| рр |               |     |          |

|----|---------------|-----|----------|

| СС | CCP1          | osc | CLKIN    |

| ck | CLKR          | rd  | RD       |

| cs | <del>CS</del> | rw  | RD or WR |

| di | SDI           | sc  | SCK      |

| do | SDO           | SS  | SS       |

| dt | Data in       | t0  | T0CKI    |

| io | I/O PORT      | t1  | T1CKI    |

| mc | MCLR          | wr  | WR       |

Uppercase letters and their meanings:

| S |                          |   |                |

|---|--------------------------|---|----------------|

| F | Fall                     | Р | Period         |

| Н | High                     | R | Rise           |

| 1 | Invalid (High-impedance) | V | Valid          |

| L | Low                      | Z | High-impedance |

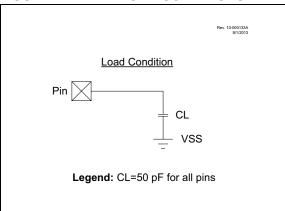

#### FIGURE 24-4: **LOAD CONDITIONS**

# 25.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

Graphs and charts are not available at this time.

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device       | [X] <sup>(</sup><br>Tape and<br>Option | ⊤<br>d Reel Temperatu                                  | re Package       | XXX<br> <br>Pattern |

|--------------------------|----------------------------------------|--------------------------------------------------------|------------------|---------------------|

| Device:                  | PIC10                                  | F320, PIC10LF320, PI                                   | C10F322, PIC10LF | 322                 |

| Tape and Reel<br>Option: | Blank<br>T                             | = Standard packaging<br>= Tape and Reel <sup>(1)</sup> | g (tube or tray) |                     |

| Temperature<br>Range:    | I<br>E                                 | = -40°C to +85°C<br>= -40°C to +125°C                  |                  |                     |

| Package:                 | OT<br>P<br>MC                          | = SOT-23<br>= PDIP<br>= DFN                            |                  |                     |

| Pattern:                 |                                        | SQTP, Code or Special otherwise)                       | Requirements     |                     |

### Examples:

- a) PIC10LF320T I/OT Tape and Reel, Industrial temperature, SOT-23 package p) PIC10F322 - I/P

- b) PIC10F322 I/P Industrial temperature PDIP package

- c) PIC10F322 E/MC Extended temperature, DFN package

Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.