# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 3                                                                        |

| Program Memory Size        | 448B (256 x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 3x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | SOT-23-6                                                                 |

| Supplier Device Package    | SOT-23-6                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f320-i-ot |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC10(L)F320/322 Family Types

| Device       | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High Endurance Flash (bytes) | I/O'S <sup>(2)</sup> | 8-Bit ADC (ch) | Timers<br>(8-Bit) | PWM | Complementary Wave<br>Generator (CWG) | Configurable Logic<br>Cell (CLC) | Fixed Voltage<br>Reference (FVR) | Numerically Controlled<br>Oscillator (NCO) | Debug <sup>(1)</sup> | XLP |

|--------------|------------------|---------------------------------|----------------------|------------------------------|----------------------|----------------|-------------------|-----|---------------------------------------|----------------------------------|----------------------------------|--------------------------------------------|----------------------|-----|

| PIC10(L)F320 | (1)              | 256                             | 64                   | 128                          | 4                    | 3              | 2                 | 2   | 1                                     | 1                                | 1                                | 1                                          | Н                    | Y   |

| PIC10(L)F322 | (1)              | 512                             | 64                   | 128                          | 4                    | 3              | 2                 | 2   | 1                                     | 1                                | 1                                | 1                                          | Н                    | Y   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, Available using Debug Header; E - Emulation, Available using Emulation Header.

**2:** One pin is input-only.

#### Data Sheet Index:

1: DS40001585 PIC10(L)F320/322 Data Sheet, 6/8 Pin High Performance, Flash Microcontrollers.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

# 6.6 Interrupt Control Registers

#### **REGISTER 6-1:** INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0          | R/W-0/0                            | R/W-0/0                               | R/W-0/0        | R/W-0/0            | R/W-0/0          | R/W-0/0           | R-0/0                |

|------------------|------------------------------------|---------------------------------------|----------------|--------------------|------------------|-------------------|----------------------|

| GIE              | PEIE                               | TMR0IE                                | INTE           | IOCIE              | TMR0IF           | INTF              | IOCIF <sup>(1)</sup> |

| bit 7            |                                    |                                       |                |                    |                  |                   | bit 0                |

|                  |                                    |                                       |                |                    |                  |                   |                      |

| Legend:          |                                    |                                       |                |                    |                  |                   |                      |

| R = Readable     | e bit                              | W = Writable                          | bit            | U = Unimpler       | mented bit, read | l as '0'          |                      |

| u = Bit is uncl  | hanged                             | x = Bit is unkr                       | iown           | -n/n = Value a     | at POR and BO    | R/Value at all o  | ther Resets          |

| '1' = Bit is set |                                    | '0' = Bit is clea                     | ared           |                    |                  |                   |                      |

|                  |                                    |                                       |                |                    |                  |                   |                      |

| bit 7            |                                    | nterrupt Enable                       |                |                    |                  |                   |                      |

|                  |                                    | all active interru                    | pts            |                    |                  |                   |                      |

| L:1 0            | 0 = Disables                       | •                                     |                |                    |                  |                   |                      |

| bit 6            | •                                  | eral Interrupt E<br>all active periph |                | 2                  |                  |                   |                      |

|                  |                                    | all peripheral in                     |                | ,                  |                  |                   |                      |

| bit 5            | TMROIE: Tim                        | er0 Overflow Ir                       | terrupt Enabl  | e bit              |                  |                   |                      |

|                  |                                    | he Timer0 inter                       |                |                    |                  |                   |                      |

|                  |                                    | the Timer0 inte                       | •              |                    |                  |                   |                      |

| bit 4            |                                    | ternal Interrupt                      |                |                    |                  |                   |                      |

|                  |                                    | he INT externa the INT externa        |                |                    |                  |                   |                      |

| bit 3            |                                    | upt-on-Change                         | -              | ble bit            |                  |                   |                      |

|                  |                                    | the interrupt-on-                     |                |                    |                  |                   |                      |

|                  | 0 = Disables                       | the interrupt-on                      | -change inter  | rupt               |                  |                   |                      |

| bit 2            |                                    | er0 Overflow In                       |                | bit                |                  |                   |                      |

|                  |                                    | gister has overf<br>gister did not ov |                |                    |                  |                   |                      |

| bit 1            | -                                  | ternal Interrupt                      |                |                    |                  |                   |                      |

|                  |                                    | external interrupt                    |                |                    |                  |                   |                      |

|                  |                                    | external interru                      |                | Jr                 |                  |                   |                      |

| bit 0            | IOCIF: Interru                     | upt-on-Change                         | Interrupt Flag | bit <sup>(1)</sup> |                  |                   |                      |

|                  |                                    | least one of the                      |                |                    |                  |                   |                      |

|                  | 0 = None of t                      | he interrupt-on-                      | change pins l  | have changed       | state            |                   |                      |

|                  | e IOCIF Flag bi<br>ve been cleared |                                       | nd cleared wh  | en all the Inter   | rupt-on-Change   | e flags in the IO | CAF register         |

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

| Name   | Bit 7 | Bit 6 Bit 5 Bit 4 |           | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|--------|-------|-------------------|-----------|-------|------------|-------|--------|--------|---------------------|

| OSCCON | —     |                   | IRCF<2:0> |       |            | —     | LFIOFR | HFIOFS | 26                  |

| STATUS | IRP   | RP1               | RP0       | TO    | PD         | Z     | DC     | С      | 13                  |

| WDTCON |       |                   |           | ١     | WDTPS<4:0> |       |        | SWDTEN | 48                  |

## TABLE 8-3: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

| TABLE 8-4: | SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER |

|------------|---------------------------------------------------|

|            |                                                   |

| Name   | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2  | Bit 9/1 | Bit 8/0              | Register<br>on Page |      |    |

|--------|------|---------|---------|----------|-----------|----------|-----------|---------|----------------------|---------------------|------|----|

| CONFIG | 13:8 |         | _       | _        | WRT       | WRT<1:0> |           | LPBOR   | LVP                  | 20                  |      |    |

| CONFIG | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          | WDTE<1:0> |         | WDTE<1:0> BOREN<1:0> |                     | FOSC | 20 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

# 12.3 FVR Control Registers

#### REGISTER 12-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0          | R-q/q                             | R/W-0/0                                       | R/W-0/0              | U-0                        | U-0                        | R/W-0/0          | R/W-0/0      |  |

|------------------|-----------------------------------|-----------------------------------------------|----------------------|----------------------------|----------------------------|------------------|--------------|--|

| FVREN            | FVRRDY <sup>(1)</sup>             | TSEN <sup>(3)</sup>                           | TSRNG <sup>(3)</sup> | —                          | —                          | ADFVR<1:0>       |              |  |

| bit 7            | •                                 |                                               |                      |                            | •                          |                  | bit C        |  |

|                  |                                   |                                               |                      |                            |                            |                  |              |  |

| Legend:          |                                   |                                               |                      |                            |                            |                  |              |  |

| R = Readable     | R = Readable bit W = Writable bit |                                               |                      |                            | mented bit, read           | as '0'           |              |  |

| u = Bit is uncl  | hanged                            | x = Bit is unk                                | nown                 | -n/n = Value               | at POR and BOI             | R/Value at all c | other Resets |  |

| '1' = Bit is set |                                   | '0' = Bit is cle                              | ared                 | q = Value de               | pends on condit            | ion              |              |  |

| bit 7            |                                   | d Voltage Refe                                |                      | bit                        |                            |                  |              |  |

|                  |                                   | Itage Reference<br>Itage Reference            |                      |                            |                            |                  |              |  |

| bit 6            |                                   | ed Voltage Re                                 | -                    | -                          |                            |                  |              |  |

|                  |                                   | Itage Referenc<br>Itage Referenc              |                      |                            | enabled                    |                  |              |  |

| bit 5            |                                   | erature Indicato<br>ture Indicator i          |                      | )                          |                            |                  |              |  |

|                  |                                   | ture Indicator i                              |                      |                            |                            |                  |              |  |

| bit 4            | TSRNG: Tem                        | perature Indica                               | ator Range Se        | lection bit <sup>(3)</sup> |                            |                  |              |  |

|                  |                                   | ′оо - 4Vт (High                               | υ,                   |                            |                            |                  |              |  |

|                  |                                   | ′DD - 2V⊤ (Low                                | •                    |                            |                            |                  |              |  |

| bit 3-2          | •                                 | ted: Read as '                                |                      |                            |                            |                  |              |  |

| bit 1-0          | 11 = ADC Fix                      | ADC Fixed V<br>ed Voltage Re                  | ference Peripl       | neral output is            | 4x (4.096V) <sup>(2)</sup> |                  |              |  |

|                  | 01 = ADC Fix                      | ed Voltage Re<br>d Voltage Re<br>d Voltage Re | ference Peripl       | neral output is            | 1x (1.024V)                |                  |              |  |

|                  | RRDY indicates                    |                                               |                      |                            |                            |                  |              |  |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 14.0 "Temperature Indicator Module" for additional information.

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit 0 | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|------------|-------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG |       |       | ADFVR<1:0> |       | 78                  |

**Legend:** Shaded cells are not used with the Fixed Voltage Reference.

| R/W-1/u              | R/W-1/u                                                                                                       | R/W-1/u                                                                                                                                                                                              | R/W-1/u                | R/W-1/u        | R/W-1/u          | R/W-1/u          | R/W-1/u     |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|------------------|------------------|-------------|--|--|--|--|

| WPUEN <sup>(1)</sup> | INTEDG                                                                                                        | TOCS                                                                                                                                                                                                 | T0SE                   | PSA            |                  | PS<2:0>          |             |  |  |  |  |

| bit 7                |                                                                                                               |                                                                                                                                                                                                      |                        |                |                  |                  | bit C       |  |  |  |  |

|                      |                                                                                                               |                                                                                                                                                                                                      |                        |                |                  |                  |             |  |  |  |  |

| Legend:              |                                                                                                               |                                                                                                                                                                                                      |                        |                |                  |                  |             |  |  |  |  |

| R = Readable         | bit                                                                                                           | W = Writable                                                                                                                                                                                         | bit                    |                | mented bit, read |                  |             |  |  |  |  |

| u = Bit is uncha     | anged                                                                                                         | x = Bit is unkr                                                                                                                                                                                      |                        | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is set     |                                                                                                               | '0' = Bit is cle                                                                                                                                                                                     | ared                   |                |                  |                  |             |  |  |  |  |

| bit 7                | WPUEN: Wea                                                                                                    | ak Pull-up Enal                                                                                                                                                                                      | ble bit <sup>(1)</sup> |                |                  |                  |             |  |  |  |  |

|                      |                                                                                                               | l-ups are disab<br>l-ups are enabl                                                                                                                                                                   |                        | al PORT latch  | values           |                  |             |  |  |  |  |

| bit 6                | INTEDG: Interrupt Edge Select bit                                                                             |                                                                                                                                                                                                      |                        |                |                  |                  |             |  |  |  |  |

|                      | <ul> <li>1 = Interrupt on rising edge of INT pin</li> <li>0 = Interrupt on falling edge of INT pin</li> </ul> |                                                                                                                                                                                                      |                        |                |                  |                  |             |  |  |  |  |

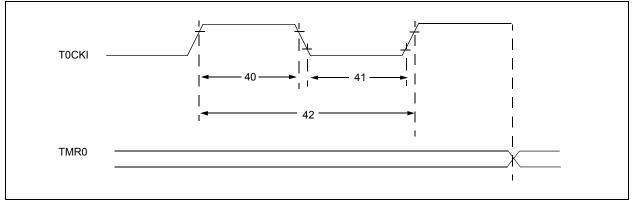

| bit 5                | TOCS: TMR0                                                                                                    | : TMR0 Clock Source Select bit                                                                                                                                                                       |                        |                |                  |                  |             |  |  |  |  |

|                      |                                                                                                               | on T0CKI pin<br>struction cycle                                                                                                                                                                      | clock (Fosc/4          | 4)             |                  |                  |             |  |  |  |  |

| bit 4                | TOSE: TMR0                                                                                                    | TMR0 Source Edge Select bit                                                                                                                                                                          |                        |                |                  |                  |             |  |  |  |  |

|                      |                                                                                                               | t on high-to-lov<br>t on low-to-higł                                                                                                                                                                 |                        |                |                  |                  |             |  |  |  |  |

| bit 3                | PSA: Prescaler Assignment bit                                                                                 |                                                                                                                                                                                                      |                        |                |                  |                  |             |  |  |  |  |

|                      |                                                                                                               | is inactive and is assigned to                                                                                                                                                                       |                        |                | ) module         |                  |             |  |  |  |  |

| bit 2-0              | <b>PS&lt;2:0&gt;:</b> Pre                                                                                     | escaler Rate Se                                                                                                                                                                                      | elect bits             |                |                  |                  |             |  |  |  |  |

|                      | Bit                                                                                                           | Value TMR0 F                                                                                                                                                                                         | Rate                   |                |                  |                  |             |  |  |  |  |

|                      | 0<br>0<br>1<br>1<br>1                                                                                         | 000         1:2           001         1:4           010         1:8           011         1:1           000         1:3           001         1:6           100         1:1           11         1:2 | 6<br>2<br>4<br>28      |                |                  |                  |             |  |  |  |  |

# REGISTER 16-1: OPTION\_REG: OPTION REGISTER

**Note 1:**  $\overline{\text{WPUEN}}$  does not disable the pull-up for the  $\overline{\text{MCLR}}$  input when  $\overline{\text{MCLR}} = 1$ .

#### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7                  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|------------|------------------------|--------|--------|-------|-------|--------|--------|--------|---------------------|

| INTCON     | GIE                    | PEIE   | TMR0IE | INTE  | IOCIE | TMR0IF | INTF   | IOCIF  | 40                  |

| OPTION_REG | WPUEN                  | INTEDG | TOCS   | T0SE  | PSA   |        |        | 95     |                     |

| TMR0       | Timer0 module Register |        |        |       |       |        |        |        | 40                  |

| TRISA      | —                      | —      | —      | —     | —     | TRISA2 | TRISA1 | TRISA0 | 69                  |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

#### 18.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 18-4.

## EQUATION 18-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

Note: If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 64) | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

| TABLE 18-2: | <b>EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (</b> | Fosc = 8 MHz) | ) |

|-------------|--------------------------------------------------|---------------|---|

|-------------|--------------------------------------------------|---------------|---|

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 64) | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 18.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 18.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to **Section 4.0** "**Oscillator Module**" for additional details.

## 18.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

# 19.5 CLC Control Registers

# REGISTER 19-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

| R/W-0/0                                                                                                                                                                                                   | R/W-0/0                                                                                                                                                                                                                                               | R-0/0                 | R/W-0/0                                   | R/W-0/0        | R/W-0/0         | R/W-0/0           | R/W-0/0     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------|----------------|-----------------|-------------------|-------------|

| LCxEN                                                                                                                                                                                                     | LCxOE                                                                                                                                                                                                                                                 | LCxOUT                | LCxINTP                                   | LCxINTN        |                 | LCxMODE<2:0       | >           |

| bit 7                                                                                                                                                                                                     |                                                                                                                                                                                                                                                       |                       |                                           |                |                 |                   | bit 0       |

| <b></b>                                                                                                                                                                                                   |                                                                                                                                                                                                                                                       |                       |                                           |                |                 |                   |             |

| Legend:                                                                                                                                                                                                   |                                                                                                                                                                                                                                                       |                       |                                           |                |                 |                   |             |

| R = Readable                                                                                                                                                                                              | bit                                                                                                                                                                                                                                                   | W = Writable          | bit                                       | U = Unimpler   | nented bit, rea | d as '0'          |             |

| u = Bit is unch                                                                                                                                                                                           | anged                                                                                                                                                                                                                                                 | x = Bit is unkr       | nown                                      | -n/n = Value a | at POR and BO   | OR/Value at all o | other Reset |

| '1' = Bit is set                                                                                                                                                                                          |                                                                                                                                                                                                                                                       | '0' = Bit is cle      | ared                                      |                |                 |                   |             |

| bit 7                                                                                                                                                                                                     | LCxEN: Conf                                                                                                                                                                                                                                           | figurable Logic       | Cell Enable b                             | it             |                 |                   |             |

| <ul> <li>1 = Configurable Logic Cell is enabled and mixing input signals</li> <li>0 = Configurable Logic Cell is disabled and has logic zero output</li> </ul>                                            |                                                                                                                                                                                                                                                       |                       |                                           |                |                 |                   |             |

| bit 6                                                                                                                                                                                                     | 1 = Configurable Logic Cell port pin output enabled                                                                                                                                                                                                   |                       |                                           |                |                 |                   |             |

| 0 = Configurable Logic Cell port pin output disabled         bit 5       LCxOUT: Configurable Logic Cell Data Output bit         Dead only logic cell output data affect CyDOL completed from law outputs |                                                                                                                                                                                                                                                       |                       |                                           |                |                 |                   |             |

| bit 4                                                                                                                                                                                                     | Read-only: logic cell output data, after LCxPOL; sampled from lcx_out wire.<br>LCxINTP: Configurable Logic Cell Positive Edge Going Interrupt Enable bit<br>1 = CLCxIF will be set when a rising edge occurs on lcx_out<br>0 = CLCxIF will not be set |                       |                                           |                |                 |                   |             |

| bit 3                                                                                                                                                                                                     | <ul> <li>LCxINTN: Configurable Logic Cell Negative Edge Going Interrupt Enable bit</li> <li>1 = CLCxIF will be set when a falling edge occurs on lcx_out</li> <li>0 = CLCxIF will not be set</li> </ul>                                               |                       |                                           |                |                 |                   |             |

| bit 2-0                                                                                                                                                                                                   | 111 = Cell is<br>110 = Cell is<br>101 = Cell is                                                                                                                                                                                                       | 4-input AND<br>OR-XOR | arent latch with<br>vith R<br>Flop with R | h S and R      | de bits         |                   |             |

| R/W-x/u          | U-0                                                                                                                                       | U-0                                     | U-0             | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxPOL           | —                                                                                                                                         | —                                       | —               | LCxG4POL       | LCxG3POL         | LCxG2POL         | LCxG1POL    |

| bit 7            |                                                                                                                                           |                                         |                 |                |                  |                  | bit 0       |

|                  |                                                                                                                                           |                                         |                 |                |                  |                  |             |

| Legend:          |                                                                                                                                           |                                         |                 |                |                  |                  |             |

| R = Readable I   | oit                                                                                                                                       | W = Writable I                          | bit             | U = Unimpler   | mented bit, read | l as '0'         |             |

| u = Bit is uncha | anged                                                                                                                                     | x = Bit is unkn                         | own             | -n/n = Value a | at POR and BO    | R/Value at all o | other Reset |

| '1' = Bit is set |                                                                                                                                           | '0' = Bit is clea                       | ared            |                |                  |                  |             |

|                  |                                                                                                                                           |                                         |                 |                |                  |                  |             |

| bit 7            | LCxPOL: LCO                                                                                                                               | OUT Polarity C                          | ontrol bit      |                |                  |                  |             |

|                  |                                                                                                                                           | ut of the logic c                       |                 |                |                  |                  |             |

|                  | 0 = The outp                                                                                                                              | ut of the logic c                       | ell is not inve | rted           |                  |                  |             |

| bit 6-4          | Unimplemen                                                                                                                                | ted: Read as 'o                         | )'              |                |                  |                  |             |

| bit 3            | LCxG4POL:                                                                                                                                 | Gate 4 Output I                         | Polarity Contr  | ol bit         |                  |                  |             |

|                  |                                                                                                                                           | ut of gate 4 is i                       |                 | applied to the | logic cell       |                  |             |

|                  | •                                                                                                                                         | ut of gate 4 is r                       |                 |                |                  |                  |             |

| bit 2            |                                                                                                                                           | Gate 3 Output I                         | •               |                |                  |                  |             |

|                  | •                                                                                                                                         | ut of gate 3 is iı<br>ut of gate 3 is r |                 | applied to the | logic cell       |                  |             |

| bit 1            | •                                                                                                                                         | •                                       |                 | ol bit         |                  |                  |             |

| DIL              | LCxG2POL: Gate 2 Output Polarity Control bit                                                                                              |                                         |                 |                |                  |                  |             |

|                  | <ul> <li>1 = The output of gate 2 is inverted when applied to the logic cell</li> <li>0 = The output of gate 2 is not inverted</li> </ul> |                                         |                 |                |                  |                  |             |

| bit 0            | <b>LCxG1POL:</b> Gate 1 Output Polarity Control bit                                                                                       |                                         |                 |                |                  |                  |             |

|                  |                                                                                                                                           | ut of gate 1 is i                       | •               |                | logic cell       |                  |             |

|                  |                                                                                                                                           | ut of gate 1 is r                       |                 |                | -                |                  |             |

## REGISTER 19-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

| R/W-x/u          | R/W-x/u                                        | R/W-x/u                           | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|------------------------------------------------|-----------------------------------|----------------|----------------|------------------|------------------|--------------|

| LCxG4D4T         | LCxG4D4N                                       | LCxG4D3T                          | LCxG4D3N       | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N     |

| bit 7            |                                                |                                   |                |                |                  | •                | bit 0        |

|                  |                                                |                                   |                |                |                  |                  |              |

| Legend:          |                                                |                                   |                |                |                  |                  |              |

| R = Readable     |                                                | W = Writable                      |                | •              | nented bit, read |                  |              |

| u = Bit is uncha | anged                                          | x = Bit is unkn                   |                | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |                                                | '0' = Bit is clea                 | ared           |                |                  |                  |              |

| bit 7            |                                                | Gate 4 Data 4 T                   | rue (non-inver | rted) bit      |                  |                  |              |

|                  |                                                | gated into lcxg                   |                | ned) bit       |                  |                  |              |

|                  |                                                | not gated into                    |                |                |                  |                  |              |

| bit 6            | LCxG4D4N:                                      | Gate 4 Data 4 M                   | Vegated (inver | rted) bit      |                  |                  |              |

|                  | 1 = lcxd4N is gated into lcxg4                 |                                   |                |                |                  |                  |              |

|                  | 0 = Icxd4N is                                  | not gated into                    | lcxg4          |                |                  |                  |              |

| bit 5            | LCxG4D3T: G                                    | Gate 4 Data 3 T                   | rue (non-inver | rted) bit      |                  |                  |              |

|                  |                                                | gated into lcxg                   |                |                |                  |                  |              |

|                  |                                                | not gated into                    | •              |                |                  |                  |              |

| bit 4            |                                                | Gate 4 Data 3 M                   | •              | rted) bit      |                  |                  |              |

|                  |                                                | gated into loxo                   |                |                |                  |                  |              |

| 1.1.0            |                                                | not gated into                    | •              |                |                  |                  |              |

| bit 3            |                                                | Sate 4 Data 2 T                   |                | rted) bit      |                  |                  |              |

|                  |                                                | gated into lcxg<br>not gated into |                |                |                  |                  |              |

| bit 2            |                                                | Gate 4 Data 2 M                   | •              | rted) bit      |                  |                  |              |

| SR 2             |                                                | gated into lcxc                   |                |                |                  |                  |              |

|                  |                                                | not gated into                    |                |                |                  |                  |              |

| bit 1            | LCxG4D1T: G                                    | Gate 4 Data 1 T                   | rue (non-inver | rted) bit      |                  |                  |              |

|                  | 1 = lcxd1T is                                  | gated into lcxg                   | 4              |                |                  |                  |              |

|                  | 0 = lcxd1T is not gated into lcxg4             |                                   |                |                |                  |                  |              |

| bit 0            | LCxG4D1N: Gate 4 Data 1 Negated (inverted) bit |                                   |                |                |                  |                  |              |

|                  | 1 = Icxd1N is gated into Icxg4                 |                                   |                |                |                  |                  |              |

|                  | 0 = Icxd1N is                                  | not gated into                    | lova/          |                |                  |                  |              |

# REGISTER 19-8: CLCxGLS3: GATE 4 LOGIC SELECT REGISTER

| Name     | Bit7     | Bit6     | Bit5        | Bit4     | Blt3     | Bit2     | Bit1        | Bit0     | Register<br>on Page |

|----------|----------|----------|-------------|----------|----------|----------|-------------|----------|---------------------|

| CLC1CON  | LC1EN    | LC10E    | LC10UT      | LC1INTP  | LC1INTN  | L        | C1MODE<2:0  | >        | 110                 |

| CLC1GLS0 | LC1G1D4T | LC1G1D4N | LC1G1D3T    | LC1G1D3N | LC1G1D2T | LC1G1D2N | LC1G1D1T    | LC1G1D1N | 114                 |

| CLC1GLS1 | LC1G2D4T | LC1G2D4N | LC1G2D3T    | LC1G2D3N | LC1G2D2T | LC1G2D2N | LC1G2D1T    | LC1G2D1N | 115                 |

| CLC1GLS2 | LC1G3D4T | LC1G3D4N | LC1G3D3T    | LC1G3D3N | LC1G3D2T | LC1G3D2N | LC1G3D1T    | LC1G3D1N | 116                 |

| CLC1GLS3 | LC1G4D4T | LC1G4D4N | LC1G4D3T    | LC1G4D3N | LC1G4D2T | LC1G4D2N | LC1G4D1T    | LC1G4D1N | 117                 |

| CLC1POL  | LC1POL   | _        | _           | _        | LC1G4POL | LC1G3POL | LC1G2POL    | LC1G1POL | 111                 |

| CLC1SEL0 | —        |          | LC1D2S<2:0> |          | _        |          | LC1D1S<2:0> |          | 112                 |

| CLC1SEL1 | —        |          | LC1D4S<2:0> |          | _        |          | LC1D3S<2:0> |          | 113                 |

| INTCON   | GIE      | PEIE     | TMR0IE      | INTE     | IOCIE    | TMR0IF   | INTF        | IOCIF    | 40                  |

| PIE1     | _        | ADIE     |             | NCO1IE   | CLC1IE   | _        | TMR2IE      | _        | 41                  |

| PIR1     | _        | ADIF     | _           | NCO1IF   | CLC1IF   | _        | TMR2IF      | _        | 42                  |

| TRISA    | _        | _        | _           | _        | _        | TRISA2   | TRISA1      | TRISA0   | 69                  |

### TABLE 19-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

Legend: — = unimplemented read as '0'. Shaded cells are not used for CLC module.

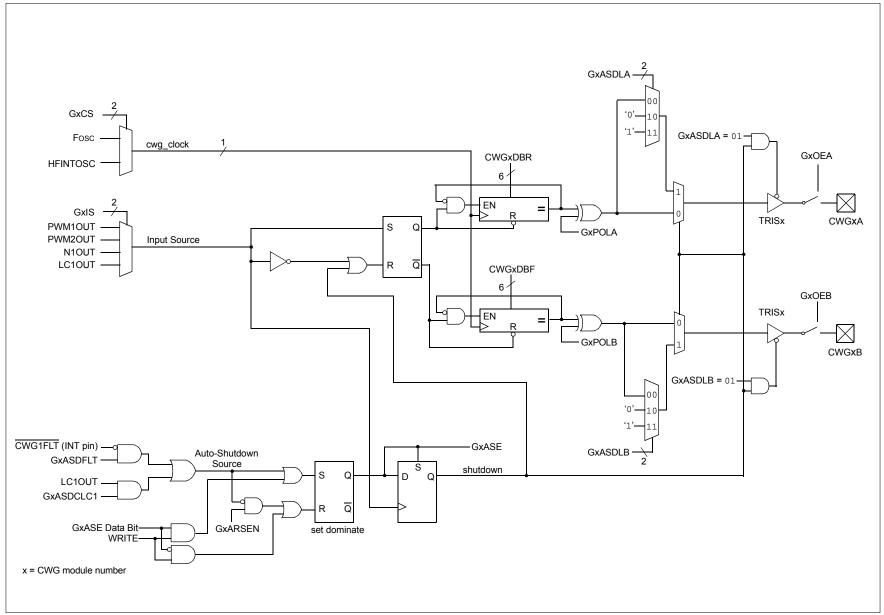

#### FIGURE 21-1: CWG BLOCK DIAGRAM

# 21.11 Configuring the CWG

The following steps illustrate how to properly configure the CWG to ensure a synchronous start:

- 1. Ensure that the TRIS control bits corresponding to CWGxA and CWGxB are set so that both are configured as inputs.

- 2. Clear the GxEN bit, if not already cleared.

- 3. Set desired dead-band times with the CWGxDBR and CWGxDBF registers.

- 4. Setup the following controls in CWGxCON2 auto-shutdown register:

- Select desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the GxASE bit and clear the GxARSEN bit.

- 5. Select the desired input source using the CWGxCON1 register.

- 6. Configure the following controls in CWGxCON0 register:

- · Select desired clock source.

- · Select the desired output polarities.

- Set the output enables for the outputs to be used.

- 7. Set the GxEN bit.

- Clear TRIS control bits corresponding to CWGxA and CWGxB to be used to configure those pins as outputs.

- If auto-restart is to be used, set the GxARSEN bit and the GxASE bit will be cleared automatically. Otherwise, clear the GxASE bit to start the CWG.

# 21.11.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the GxASDLA and GxASDLB bits of the CWGxCON1 register (Register 21-2). GxASDLA controls the CWG1A override level and GxASDLB controls the CWG1B override level. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not apply to the override level.

## 21.11.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to have resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the CWGxCON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 21-5 and Figure 21-6.

# 21.11.2.1 Software controlled restart

When the GxARSEN bit of the CWGxCON2 register is cleared, the CWG must be restarted after an auto-shut-down event by software.

The CWG will resume operation on the first rising edge event after the GxASE bit is cleared. Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the GxASE bit will remain set.

### 21.11.2.2 Auto-Restart

When the GxARSEN bit of the CWGxCON2 register is set, the CWG will restart from the auto-shutdown state automatically.

After the shutdown event clears, the GxASE bit will clear automatically and the CWG will resume operation on the first rising edge event.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSS f,b                                                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                                             |

| Operands:        | None                                                                                                                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT} \\ \text{0} \rightarrow \text{WDT prescaler,} \\ 1 \rightarrow \overline{\text{TO}} \\ 1 \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                     |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set.                                                             |

| CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                 |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The 11-bit immediate<br>address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                              |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |

| Status Affected: | Z                                                                                                                                                              |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |

| CLRF             | Clear f                                                                                    |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [label]CLRF f                                                                              |

| Operands:        | $0 \leq f \leq 127$                                                                        |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{f}) \\ 1 \rightarrow \text{Z} \end{array}$ |

| Status Affected: | Z                                                                                          |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.                          |

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                               |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                        |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                       |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |

| Status Affected: | Z                                                                                                                     |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the<br>W register. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |