# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 3                                                                       |

| Program Memory Size        | 896B (512 x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                             |

| Data Converters            | A/D 3x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

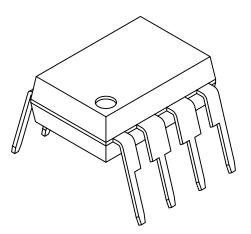

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f322-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 5.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 5.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

#### 5.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word. The four operating modes are:

- BOR is always on

- BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 5-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Register 3-1.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 5-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device Operation upon:<br>Release of POR/Wake- up from Sleep |

|------------|--------|-------------|----------|--------------------------------------------------------------|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)              |

| 1.0        |        | Awake       | Active   | Weite for POP ready (POPPDY = 1)                             |

| 10         | Х      | Sleep       | Disabled | Waits for BOR ready (BORRDY = 1)                             |

| 0.1        | 1      | Х           | Active   | Waits for BOR ready <sup>(1)</sup> (BORRDY = 1)              |

| 01         | 0      | х           | Disabled | Baging immediately (BOBBDY =)                                |

| 00         | Х      | х           | Disabled | Begins immediately (BORRDY = $x$ )                           |

TABLE 5-1: BOR OPERATING MODES

**Note 1:** In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 5.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 5.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 5.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 6.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 7.0 "Power-Down Mode (Sleep)" for more details.

#### 6.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

#### 6.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Temporary holding registers W\_TEMP and STATUS\_TEMP should be placed in the last 16 bytes of GPR (see Table 1-2). This makes context save and restore operations simpler. The code shown in Example 6-1 can be used to:

- Store the W register

- · Store the STATUS register

- · Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- · Restore the W register

- Note: These devices do not require saving the PCLATH. However, if computed GOTOS are used in both the ISR and the main code, the PCLATH must be saved and restored in the ISR.

#### EXAMPLE 6-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W |

|----------------|--------------------|-------------------------------------------------------------|

| MOLTHE         |                    | ;Swaps are used because they do not affect the status bits  |

| MOVWF<br>:     | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register              |

| :(ISR)         |                    | ;Insert user code here                                      |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W                           |

|                |                    | ;(sets bank to original state)                              |

| MOVWF          | STATUS             | ;Move W into STATUS register                                |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                         |

|                |                    |                                                             |

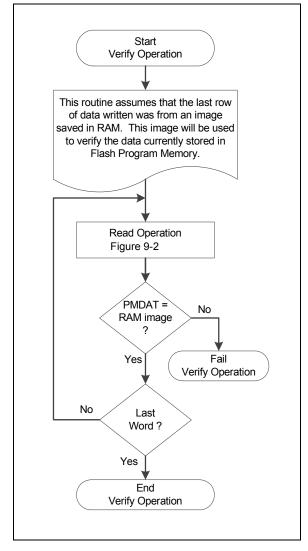

#### 9.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 9-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

| U-1 <sup>(1</sup>           | ) R/W-0/0                  | R/W-0/0                                                                                                                                                           | R/W/HC-0/0     | R/W/HC-0/q <sup>(2)</sup>             | R/W-0/0          | R/S/HC-0/0       | R/S/HC-0/0       |  |  |  |  |

|-----------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------|------------------|------------------|------------------|--|--|--|--|

| _                           | CFGS                       | LWLO                                                                                                                                                              | FREE           | WRERR                                 | WREN             | WR               | RD               |  |  |  |  |

| bit 7                       |                            |                                                                                                                                                                   |                |                                       |                  |                  | bit C            |  |  |  |  |

| logondi                     |                            |                                                                                                                                                                   |                |                                       |                  |                  |                  |  |  |  |  |

| L <b>egend:</b><br>R = Read | able bit                   | W = Writable                                                                                                                                                      | bit            | U = Unimplemer                        | nted bit. read a | as '0'           |                  |  |  |  |  |

|                             | in only be set             | x = Bit is unk                                                                                                                                                    |                | -n/n = Value at P                     | -                |                  | er Resets        |  |  |  |  |

| '1' = Bit is                | •                          | '0' = Bit is cle                                                                                                                                                  |                | HC = Bit is clear                     |                  |                  |                  |  |  |  |  |

|                             |                            |                                                                                                                                                                   |                |                                       |                  |                  |                  |  |  |  |  |

| bit 7                       | Unimpleme                  | nted: Read as                                                                                                                                                     | '1'            |                                       |                  |                  |                  |  |  |  |  |

| bit 6                       |                            | iguration Selec                                                                                                                                                   |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            |                                                                                                                                                                   |                | evice ID Registers                    | 5                |                  |                  |  |  |  |  |

| hit E                       |                            | Flash program                                                                                                                                                     | -              |                                       |                  |                  |                  |  |  |  |  |

| bit 5                       |                            | Write Latches                                                                                                                                                     |                | write latch is load                   | led/undated o    | n the next WR (  | ommand           |  |  |  |  |

|                             |                            |                                                                                                                                                                   |                | e latch is loaded/                    |                  |                  |                  |  |  |  |  |

|                             |                            |                                                                                                                                                                   | •              | ext WR command                        |                  | •                | 0                |  |  |  |  |

| bit 4                       | FREE: Progr                | FREE: Program Flash Erase Enable bit                                                                                                                              |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            | 1 = Performs an erase operation on the next WR command (hardware cleared upon completion)                                                                         |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            | 0 = Performs an write operation on the next WR command                                                                                                            |                |                                       |                  |                  |                  |  |  |  |  |

| bit 3                       |                            | WRERR: Program/Erase Error Flag bit                                                                                                                               |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            | 1 = Condition indicates an improper program or erase sequence attempt or termination (bit is se<br>automatically on any set attempt (write $(1)$ ) of the WP bit) |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            | automatically on any set attempt (write '1') of the WR bit).<br>0 = The program or erase operation completed normally.                                            |                |                                       |                  |                  |                  |  |  |  |  |

| bit 2                       |                            |                                                                                                                                                                   |                |                                       |                  |                  |                  |  |  |  |  |

|                             | -                          | WREN: Program/Erase Enable bit<br>1 = Allows program/erase cycles                                                                                                 |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            | 0 = Inhibits programming/erasing of program Flash                                                                                                                 |                |                                       |                  |                  |                  |  |  |  |  |

| bit 1                       | WR: Write C                | WR: Write Control bit                                                                                                                                             |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            | 1 = Initiates a program Flash program/erase operation.                                                                                                            |                |                                       |                  |                  |                  |  |  |  |  |

|                             |                            |                                                                                                                                                                   |                | is cleared by har                     | dware once o     | peration is com  | olete.           |  |  |  |  |

|                             |                            |                                                                                                                                                                   |                | ed) in software.<br>is complete and i | nactive          |                  |                  |  |  |  |  |

| bit 0                       | RD: Read Co                | •                                                                                                                                                                 |                |                                       | naouvo.          |                  |                  |  |  |  |  |

|                             |                            |                                                                                                                                                                   | sh read. Read  | takes one cycle.                      | RD is cleared    | in hardware. T   | he RD bit ca     |  |  |  |  |

|                             |                            | set (not cleared                                                                                                                                                  |                |                                       |                  |                  |                  |  |  |  |  |

|                             | 0 = Does no                | ot initiate a prog                                                                                                                                                | ram Flash read | d.                                    |                  |                  |                  |  |  |  |  |

| Note 1:                     | Unimplemented b            |                                                                                                                                                                   |                |                                       |                  |                  |                  |  |  |  |  |

| 2:                          | The WRERR bit is (WR = 1). | automatically                                                                                                                                                     | set by hardwar | e when a program                      | n memory write   | e or erase opera | ition is started |  |  |  |  |

| э.                          |                            | nored during a                                                                                                                                                    |                | on oraca anarati                      |                  | ١                |                  |  |  |  |  |

#### REGISTER 9-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

**3:** The LWLO bit is ignored during a program memory erase operation (FREE = 1).

### 10.2 Register Definitions: PORTA

### **REGISTER 10-1: PORTA: PORTA REGISTER**

| U-0   | U-0 | U-0 | U-0 | R-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------|-----|-----|-----|-------|---------|---------|---------|

| —     | —   | —   | —   | RA3   | RA2     | RA1     | RA0     |

| bit 7 |     |     |     |       |         |         | bit 0   |

|       |     |     |     |       |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 RA<3:0>: PORTA I/O Value bits (RA3 is read-only)

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

#### REGISTER 10-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | U-1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | (1) | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'.                                                               |

|---------|-------------------------------------------------------------------------------------------|

| bit 3   | Unimplemented: Read as '1'.                                                               |

| bit 2-0 | TRISA<2:0>: RA<2:0> Port I/O Tri-State Control bits                                       |

|         | <ol> <li>Port output driver is disabled</li> <li>Port output driver is enabled</li> </ol> |

Note 1: Unimplemented, read as '1'.

### 15.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- ADC conversion clock source

- · Interrupt control

#### 15.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 10.0 "I/O Port"** for more information.

| Note: | Analog voltages on any pin that is defined  |

|-------|---------------------------------------------|

|       | as a digital input may cause the input buf- |

|       | fer to conduct excess current.              |

#### 15.1.2 CHANNEL SELECTION

There are up to five channel selections available:

- AN<2:0> pins

- Temperature Indicator

- FVR (Fixed Voltage Reference) Output

Refer to Section 12.0 "Fixed Voltage Reference (FVR)" and Section 14.0 "Temperature Indicator Module" for more information on these channel selections.

The CHS bits of the ADCON register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 15.2 "ADC Operation"** for more information.

#### 15.1.3 ADC VOLTAGE REFERENCE

There is no external voltage reference connections to the ADC. Only VDD can be used as a reference source. The FVR is only available as an input channel and not a VREF+ input to the ADC.

#### 15.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON register (Register 15-1). There are seven possible clock options:

- · Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 9.5 TAD periods as shown in Figure 15-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in **Section 24.0 "Electrical Specifications"** for more information. Table 15-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

#### TABLE 15-2: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

| Name   | Bit 7      | Bit 6  | Bit 5  | Bit 4    | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|--------|------------|--------|--------|----------|--------|--------|---------|--------|---------------------|

| ADCON  | ADCS<2:0>  |        |        | CHS<2:0> |        |        | GO/DONE | ADON   | 88                  |

| ADRES  | ADRES<7:0> |        |        |          |        | 89     |         |        |                     |

| ANSELA | —          | _      | _      | —        | —      | ANSA2  | ANSA1   | ANSA0  | 70                  |

| FVRCON | FVREN      | FVRRDY | TSEN   | TSRNG    | _      | _      | ADFVF   | ۲<1:0> | 78                  |

| INTCON | GIE        | PEIE   | TMR0IE | INTE     | IOCIE  | TMR0IF | INTF    | IOCIF  | 40                  |

| PIE1   | —          | ADIE   | _      | NCO1IE   | CLC1IE | -      | TMR2IE  | —      | 41                  |

| PIR1   | —          | ADIF   | —      | NCO1IF   | CLC1IF | —      | TMR2IF  | _      | 42                  |

| TRISA  | _          | —      | _      | —        | _      | TRISA2 | TRISA1  | TRISA0 | 69                  |

Legend: x = unknown, u = unchanged, — = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

| U-0            | R/W-0/0            | R/W-0/0                                                                             | R/W-0/0       | R/W-0/0       | R/W-0/0          | R/W-0/0 | R/W-0/0      |  |  |  |

|----------------|--------------------|-------------------------------------------------------------------------------------|---------------|---------------|------------------|---------|--------------|--|--|--|

| _              |                    | TOUTF                                                                               | °S<3:0>       |               | TMR2ON           | T2CKF   | °S<1:0>      |  |  |  |

| bit 7          |                    |                                                                                     |               |               |                  |         | bit          |  |  |  |

| Legend:        |                    |                                                                                     |               |               |                  |         |              |  |  |  |

| R = Readat     | ole bit            | W = Writable                                                                        | bit           | U = Unimpler  | mented bit, read | as '0'  |              |  |  |  |

| u = Bit is ur  | changed            | x = Bit is unkr                                                                     | nown          |               | at POR and BO    |         | other Resets |  |  |  |

| '1' = Bit is s | -                  | '0' = Bit is cle                                                                    |               |               |                  |         |              |  |  |  |

|                |                    |                                                                                     | _             |               |                  |         |              |  |  |  |

| bit 7          | -                  | nted: Read as '                                                                     |               |               |                  |         |              |  |  |  |

| bit 6-3        |                    | 0>: Timer2 Out                                                                      | put Postscale | r Select bits |                  |         |              |  |  |  |

|                |                    | 1111 = 1:16 Postscaler                                                              |               |               |                  |         |              |  |  |  |

|                |                    | 1110 = 1:15 Postscaler                                                              |               |               |                  |         |              |  |  |  |

|                |                    | 1101 = 1:14 Postscaler<br>1100 = 1:13 Postscaler                                    |               |               |                  |         |              |  |  |  |

|                |                    | 100 = 1.13  Postscaler $1011 = 1.12  Postscaler$                                    |               |               |                  |         |              |  |  |  |

|                |                    | 1011 - 1.12  Postscaler $1010 = 1.11  Postscaler$                                   |               |               |                  |         |              |  |  |  |

|                |                    | 1001 = 1:10 Postscaler                                                              |               |               |                  |         |              |  |  |  |

|                | 1000 = <b>1</b> :9 | 1000 = 1:9 Postscaler                                                               |               |               |                  |         |              |  |  |  |

|                | 0111 = <b>1</b> :8 | Postscaler                                                                          |               |               |                  |         |              |  |  |  |

|                |                    | 0110 = 1:7 Postscaler                                                               |               |               |                  |         |              |  |  |  |

|                |                    | 0101 = 1:6 Postscaler                                                               |               |               |                  |         |              |  |  |  |

|                | 0100 = 1:5         |                                                                                     |               |               |                  |         |              |  |  |  |

|                | 0011 = 1:4         |                                                                                     |               |               |                  |         |              |  |  |  |

|                | 0010 = 1:3         |                                                                                     |               |               |                  |         |              |  |  |  |

|                |                    | 0001 = 1:2 Postscaler<br>0000 = 1:1 Postscaler                                      |               |               |                  |         |              |  |  |  |

| bit 2          | TMR2ON: T          |                                                                                     |               |               |                  |         |              |  |  |  |

|                | 1 = Timer2 i       |                                                                                     |               |               |                  |         |              |  |  |  |

|                | 0 = Timer2 i       | is off                                                                              |               |               |                  |         |              |  |  |  |

| bit 1-0        | T2CKPS<1:          | 0>: Timer2 Cloc                                                                     | k Prescale Se | elect bits    |                  |         |              |  |  |  |

|                | 11 = Presc         | <b>T2CKPS&lt;1:0&gt;:</b> Timer2 Clock Prescale Select bits<br>11 = Prescaler is 64 |               |               |                  |         |              |  |  |  |

|                |                    | 10 = Prescaler is  16                                                               |               |               |                  |         |              |  |  |  |

|                | 01 = Presc         | aler is 4                                                                           |               |               |                  |         |              |  |  |  |

|                | 00 = Presc         | aler is 1                                                                           |               |               |                  |         |              |  |  |  |

|                |                    |                                                                                     |               |               |                  |         |              |  |  |  |

| TABLE 17-      | 1: SUMMAR          | RY OF REGIS                                                                         | TERS ASSO     | CIATED WIT    | H TIMER2         |         |              |  |  |  |

#### REGISTER 17-1: T2CON: TIMER2 CONTROL REGISTER

| TABLE ' | 17-1: \$ | SUMMAR | Y OF REG | ISTERS A | ASSOCIATED | ) WITH TI | MER2 |

|---------|----------|--------|----------|----------|------------|-----------|------|

|         |          |        |          |          |            |           |      |

| Name   | Bit 7                  | Bit 6                          | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Register on<br>Page |

|--------|------------------------|--------------------------------|--------|--------|--------|--------|--------|-------|---------------------|

| INTCON | GIE                    | PEIE                           | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF | 40                  |

| PIE1   | _                      | ADIE                           |        | NCO1IE | CLC1IE |        | TMR2IE |       | 41                  |

| PIR1   | -                      | ADIF                           | _      | NCO1IF | CLC1IF | _      | TMR2IF |       | 42                  |

| PR2    |                        | Timer2 module Period Register  |        |        |        |        | 96     |       |                     |

| TMR2   | Timer2 module Register |                                |        |        |        | 96     |        |       |                     |

| T2CON  | _                      | TOUTPS<3:0> TMR2ON T2CKPS<1:0> |        |        | 97     |        |        |       |                     |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

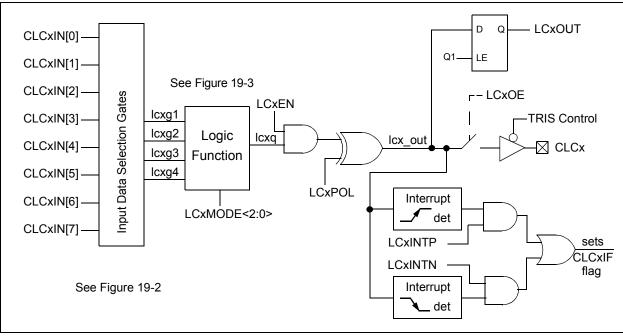

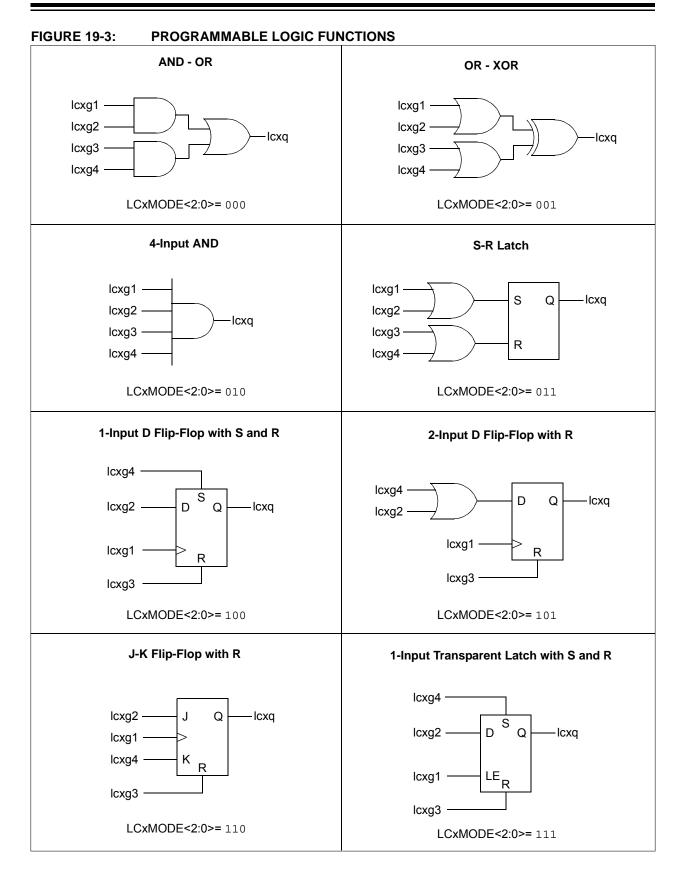

## 19.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell selects any combination of the eight input signals and through the use of configurable gates reduces the selected inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- Two I/O pins

- Internal clocks

- · Peripherals

- Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 19-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

### FIGURE 19-1: CLCx SIMPLIFIED BLOCK DIAGRAM

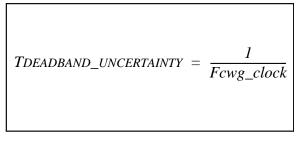

# EQUATION 21-1: DEAD-BAND DELAY TIME UNCERTAINTY

# EXAMPLE 21-1: DEAD-BAND DELAY TIME UNCERTAINTY

$$Fcwg\_clock = 16 MHz$$

Therefore:

$$TDEADBAND\_UNCERTAINTY = \frac{1}{Fcwg\_clock}$$

$$= \frac{1}{16 MHz}$$

$$= 625 ns$$

## 21.12 CWG Control Registers

| R/W-0/0                                        | R/W-0/0       | R/W-0/0                                                                        | R/W-0/0            | R/W-0/0       | U-0              | U-0            | R/W-0/0      |

|------------------------------------------------|---------------|--------------------------------------------------------------------------------|--------------------|---------------|------------------|----------------|--------------|

| GxEN                                           | GxOEB         | GxOEA                                                                          | GxPOLB             | GxPOLA        | _                | _              | GxCS0        |

| bit 7                                          |               |                                                                                |                    |               |                  |                | bit 0        |

|                                                |               |                                                                                |                    |               |                  |                |              |

| Legend:                                        |               |                                                                                |                    |               |                  |                |              |

| R = Readab                                     | le bit        | W = Writable                                                                   | bit                | U = Unimplen  | nented bit, read | as '0'         |              |

| u = Bit is un                                  | changed       | x = Bit is unk                                                                 | x = Bit is unknown |               | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is se                                | et            | '0' = Bit is cle                                                               | ared               | q = Value dep | ends on condit   | ion            |              |

|                                                |               |                                                                                |                    |               |                  |                |              |

| bit 7                                          | GxEN: CWG     | x Enable bit                                                                   |                    |               |                  |                |              |

|                                                | 1 = Module i  |                                                                                |                    |               |                  |                |              |

|                                                | 0 = Module i  |                                                                                |                    |               |                  |                |              |

| bit 6                                          |               |                                                                                |                    | <b>a</b> .    |                  |                |              |

|                                                |               | is available on<br>is not available                                            |                    |               |                  |                |              |

| bit 5                                          |               |                                                                                |                    | le l/O pin    |                  |                |              |

| DIL 5                                          |               | <b>GxOEA:</b> CWGxA Output Enable bit<br>1 = CWGxA is available on appropriate |                    |               |                  |                |              |

|                                                |               | is not available                                                               |                    | •             |                  |                |              |

| bit 4                                          |               | NGxB Output F                                                                  |                    |               |                  |                |              |

|                                                |               | s inverted polar                                                               | •                  |               |                  |                |              |

|                                                | 0 = Output is | s normal polarit                                                               | y                  |               |                  |                |              |

| bit 3 <b>GxPOLA:</b> CWGxA Output Polarity bit |               | olarity bit                                                                    |                    |               |                  |                |              |

|                                                |               | s inverted polar                                                               |                    |               |                  |                |              |

|                                                |               | s normal polarit                                                               | •                  |               |                  |                |              |

| bit 2-1                                        | Unimplemer    | nted: Read as '                                                                | 0'                 |               |                  |                |              |

| bit 0                                          |               | Gx Clock Source                                                                | e Select bit       |               |                  |                |              |

|                                                | 1 = HFINTO    | SC                                                                             |                    |               |                  |                |              |

#### REGISTER 21-1: CWGxCON0: CWG CONTROL REGISTER 0

| ADDLW            | Add literal and W                                                                                                      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] ADDLW k                                                                                                        |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                      |  |  |

| Status Affected: | C, DC, Z                                                                                                               |  |  |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |

| BCF              | Bit Clear f                                                         |  |  |  |  |

|------------------|---------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BCF f,b                                                   |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |  |  |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |  |  |  |  |

| Status Affected: | None                                                                |  |  |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                           |

| Operands:        | $0 \le k \le 255$                                                                                                  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                    |

| Status Affected: | Z                                                                                                                  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W<br>register. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                             |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                             |  |  |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                              |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                              |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                               |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2-cycle instruction. |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                         |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                          |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |  |  |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                           |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the<br>W register. |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |  | Inclusive OR W with f |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|-----------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |  |  |                       |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |  |                       |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |  |                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |  |                       |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |  |                       |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                          |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since Status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |

| MOVWF            | Move W to f                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                      |

| Operands:        | $0 \leq f \leq 127$                                                                                           |

| Operation:       | $(W) \rightarrow (f)$                                                                                         |

| Status Affected: | None                                                                                                          |

| Description:     | Move data from W register to<br>register 'f'.                                                                 |

| Words:           | 1                                                                                                             |

| Cycles:          | 1                                                                                                             |

| Example:         | MOVW OPTION_REG<br>F                                                                                          |

|                  | Before Instruction<br>$OPTION_REG = 0xFF$<br>W = 0x4F<br>After Instruction<br>$OPTION_REG = 0x4F$<br>W = 0x4F |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                       |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |  |

| NOP              | No Operation  |  |  |  |  |

|------------------|---------------|--|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |  |

| Operands:        | None          |  |  |  |  |

| Operation:       | No operation  |  |  |  |  |

| Status Affected: | None          |  |  |  |  |

| Description:     | No operation. |  |  |  |  |

| Words:           | 1             |  |  |  |  |

| Cycles:          | 1             |  |  |  |  |

| Example:         | NOP           |  |  |  |  |

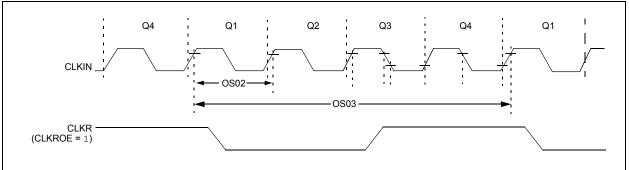

#### FIGURE 24-5: CLOCK TIMING

#### TABLE 24-6: CLOCK OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                                                  |                                         |       |     |          |     |                    |  |

|---------------------------------------------------------|--------------------------------------------------|-----------------------------------------|-------|-----|----------|-----|--------------------|--|

| Param<br>No.                                            | Sym Characteristic Min Typt Max Units Conditions |                                         |       |     |          |     |                    |  |

| OS01                                                    | Fosc                                             | External CLKIN Frequency <sup>(1)</sup> | DC    |     | 20       | MHz | EC mode            |  |

| OS02                                                    | Tosc                                             | External CLKIN Period <sup>(1)</sup>    | 31.25 | -   | $\infty$ | ns  | EC Oscillator mode |  |

| OS03                                                    | TCY                                              | Instruction Cycle Time <sup>(1)</sup>   | 200   | Тсү | DC       | ns  | Tcy = 4/Fosc       |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to CLKIN pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

#### TABLE 24-7: OSCILLATOR PARAMETERS

| Standar                          | Standard Operating Conditions (unless otherwise stated) |                                                          |                  |      |              |       |            |                                                                                                                                |

|----------------------------------|---------------------------------------------------------|----------------------------------------------------------|------------------|------|--------------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. Sym. Characteristic |                                                         | Freq.<br>Tolerance                                       | Min.             | Тур† | Max.         | Units | Conditions |                                                                                                                                |

| OS08                             | HFosc                                                   | Internal Calibrated HFINTOSC<br>Frequency <sup>(1)</sup> | ±3%<br>-8 to +4% | _    | 16.0<br>16.0 | —     | MHz<br>MHz | $\begin{array}{l} 0^{\circ}C \leq TA \leq +85^{\circ}C, \ VDD \geq 2.3V \\ -40^{\circ}C \leq TA \leq 125^{\circ}C \end{array}$ |

| OS09                             | LFosc                                                   | Internal LFINTOSC Frequency                              | ±25%             | _    | 31           | -     | kHz        |                                                                                                                                |

| OS10*                            | TWARM                                                   | HFINTOSC<br>Wake-up from Sleep Start-up Time             | —                | _    | 5            | 8     | μS         |                                                                                                                                |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

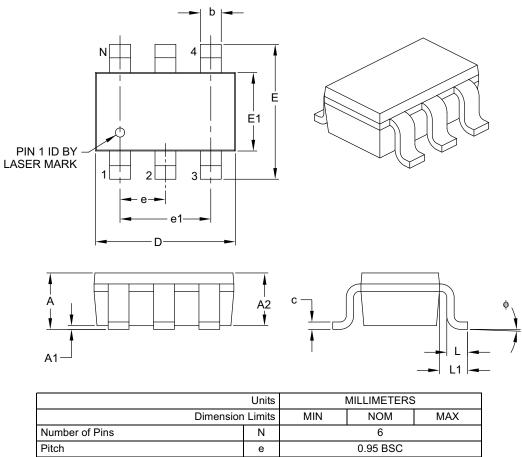

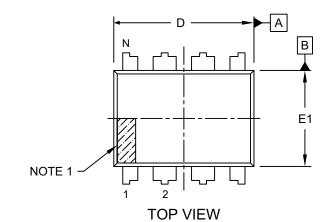

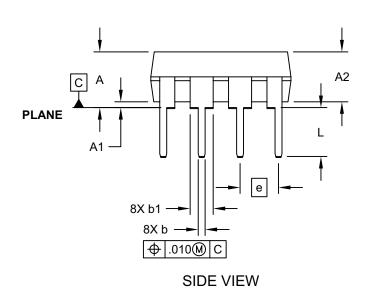

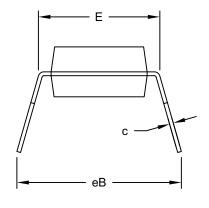

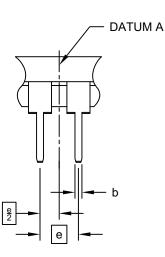

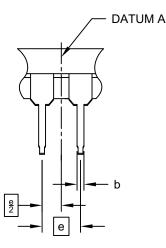

### 27.2 Package Details

The following sections give the technical details of the packages.

### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Offita           |             |             |      |  |  |

|--------------------------|------------------|-------------|-------------|------|--|--|

|                          | Dimension Limits | MIN         | NOM         | MAX  |  |  |

| Number of Pins           | N                |             | 6           |      |  |  |

| Pitch                    | е                |             | 0.95 BSC    |      |  |  |

| Outside Lead Pitch       | e1               |             | 1.90 BSC    |      |  |  |

| Overall Height           | А                | 0.90        | -           | 1.45 |  |  |

| Molded Package Thickness | A2               | 0.89        | -           | 1.30 |  |  |

| Standoff                 | A1               | 0.00        | -           | 0.15 |  |  |