Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 3                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 3x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f322t-e-ot |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC10(L)F320/322 PINOUT DESCRIPTION

| Name                        | Function | Input<br>Type | Output<br>Type | Description                                            |

|-----------------------------|----------|---------------|----------------|--------------------------------------------------------|

| RA0/PWM1/CLC1IN0/CWG1A/     | RA0      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                  |

| AN0/ICSPDAT                 | PWM1     | _             | CMOS           | PWM output.                                            |

|                             | CLC1IN0  | ST            | _              | CLC input.                                             |

|                             | CWG1A    | _             | CMOS           | CWG primary output.                                    |

|                             | AN0      | AN            | —              | A/D Channel input.                                     |

|                             | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                                        |

| RA1/PWM2/CLC1/CWG1B/AN1/    | RA1      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                  |

| CLKIN/ICSPCLK/NCO1CLK       | PWM2     | —             | CMOS           | PWM output.                                            |

|                             | CLC1     | —             | CMOS           | CLC output.                                            |

|                             | CWG1B    | —             | CMOS           | CWG complementary output.                              |

|                             | AN1      | AN            | _              | A/D Channel input.                                     |

|                             | CLKIN    | ST            | —              | External Clock input (EC mode).                        |

|                             | ICSPCLK  | ST            | —              | ICSP™ Programming Clock.                               |

|                             | NCO1CLK  | ST            | _              | Numerical Controlled Oscillator external clock input.  |

| RA2/INT/T0CKI/NCO1/CLC1IN1/ | RA2      | TTL           | CMOS           | General purpose I/O with IOC and WPU.                  |

| CLKR/AN2/CWG1FLT            | INT      | ST            | —              | External interrupt.                                    |

|                             | TOCKI    | ST            | —              | Timer0 clock input.                                    |

|                             | NCO1     | —             | CMOS           | Numerically Controlled Oscillator output.              |

|                             | CLC1IN1  | ST            | _              | CLC input.                                             |

|                             | CLKR     | —             | CMOS           | Clock Reference output.                                |

|                             | AN2      | AN            | _              | A/D Channel input.                                     |

|                             | CWG1FLT  | ST            | _              | Complementary Waveform Generator Fault 1 source input. |

| RA3/MCLR/VPP                | RA3      | TTL           | _              | General purpose input.                                 |

|                             | MCLR     | ST            | _              | Master Clear with internal pull-up.                    |

|                             | Vpp      | HV            | _              | Programming voltage.                                   |

| Vdd                         | Vdd      | Power         |                | Positive supply.                                       |

| Vss                         | Vss      | Power         | —              | Ground reference.                                      |

**Legend:** AN = Analog input or output

CMOS = CMOS compatible input or output

TTL = CMOS input with TTL levels ST = CMOS input with Schmitt Trigger levels

HV = High Voltage

#### 2.3 PCL and PCLATH

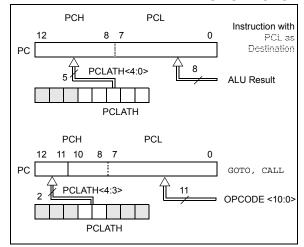

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper five bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower eight bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| Note 1: | There are no Status bits to indicate Stack<br>Overflow or Stack Underflow conditions.                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:      | There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address. |

#### 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-4.

A simple program to clear RAM location 40h-7Fh using indirect addressing is shown in Example 2-1.

| EXAMPLE 2-1: | INDIRECT ADDRESSING |

|--------------|---------------------|

|--------------|---------------------|

|          | MOVLW | 0x40  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | ;clear INDF register |

|          | INCF  | FSR   | ;inc pointer         |

|          | BTFSS | FSR,7 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       | ;yes continue        |

|          |       |       |                      |

# PIC10(L)F320/322

# PIC10(L)F320/322

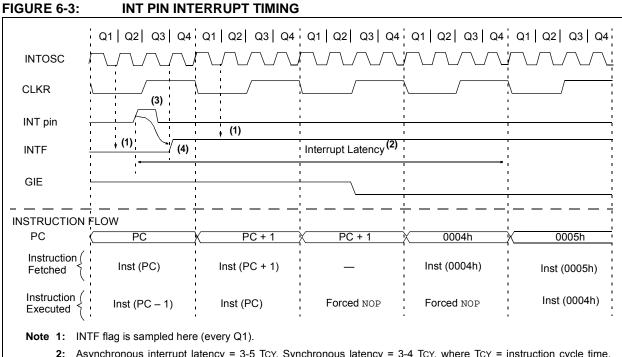

- 2: Asynchronous interrupt latency = 3-5 TCY. Synchronous latency = 3-4 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: For minimum width of INT pulse, refer to AC specifications in Section 24.0 "Electrical Specifications".

- 4: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### 9.6 Flash Program Memory Control Registers

#### REGISTER 9-1: PMDATL: PROGRAM MEMORY DATA LOW

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | PMDA    | AT<7:0>        |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable b    | oit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is uncha | anged   | x = Bit is unkn   | own     | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

### bit 7-0 **PMDAT<7:0>**: The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

#### REGISTER 9-2: PMDATH: PROGRAM MEMORY DATA HIGH

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | PMDA    | T<13:8> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMDAT<13:8>**: The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

#### REGISTER 10-3: LATA: PORTA DATA LATCH REGISTER

| U-0              | U-0   | U-0               | U-0  | U-0            | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|-------|-------------------|------|----------------|------------------|------------------|-------------|

| —                | —     | _                 | _    | —              | LATA2            | LATA1            | LATA0       |

| bit 7            |       |                   |      | •              |                  | •                | bit 0       |

|                  |       |                   |      |                |                  |                  |             |

| Legend:          |       |                   |      |                |                  |                  |             |

| R = Readable     | bit   | W = Writable      | bit  | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unch  | anged | x = Bit is unkn   | Iown | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                |                  |                  |             |

bit 7-3 Unimplemented: Read as '0'.

bit 2-0 LATA<2:0>: RA<2:0> Output Latch Value bits

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from LATx register return register values, not I/O pin values.

#### REGISTER 10-4: ANSELA: PORTA ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | —   | —   | ANSA2   | ANSA1   | ANSA0   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'.

bit 2-0 ANSA<2:0>: Analog Select between Analog or Digital Function on Pins RA<2:0>, respectively

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital Input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or Digital special function.

- **Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry. Weak pull-ups, if available, are unaffected. The corresponding TRIS bit must be set to Input mode by the user in order to allow external control of the voltage on the pin.

#### 12.3 FVR Control Registers

#### REGISTER 12-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0          | R-q/q                                                         | R/W-0/0                                       | R/W-0/0              | U-0                        | U-0                        | R/W-0/0          | R/W-0/0      |

|------------------|---------------------------------------------------------------|-----------------------------------------------|----------------------|----------------------------|----------------------------|------------------|--------------|

| FVREN            | FVRRDY <sup>(1)</sup>                                         | TSEN <sup>(3)</sup>                           | TSRNG <sup>(3)</sup> | —                          | —                          | ADFVI            | R<1:0>       |

| bit 7            | •                                                             |                                               |                      |                            | •                          |                  | bit C        |

|                  |                                                               |                                               |                      |                            |                            |                  |              |

| Legend:          |                                                               |                                               |                      |                            |                            |                  |              |

| R = Readable     | e bit                                                         | W = Writable                                  | bit                  | U = Unimpler               | mented bit, read           | as '0'           |              |

| u = Bit is uncl  | hanged                                                        | x = Bit is unk                                | nown                 | -n/n = Value               | at POR and BOI             | R/Value at all c | other Resets |

| '1' = Bit is set |                                                               | '0' = Bit is cle                              | ared                 | q = Value de               | pends on condit            | ion              |              |

| bit 7            |                                                               | d Voltage Refe                                |                      | bit                        |                            |                  |              |

|                  |                                                               | Itage Reference<br>Itage Reference            |                      |                            |                            |                  |              |

| bit 6            | FVRRDY: Fixed Voltage Reference Ready Flag bit <sup>(1)</sup> |                                               |                      |                            |                            |                  |              |

|                  |                                                               | Itage Referenc<br>Itage Referenc              |                      |                            | enabled                    |                  |              |

| bit 5            |                                                               | erature Indicato<br>ture Indicator i          |                      | )                          |                            |                  |              |

|                  |                                                               | ture Indicator i                              |                      |                            |                            |                  |              |

| bit 4            | TSRNG: Tem                                                    | perature Indica                               | ator Range Se        | lection bit <sup>(3)</sup> |                            |                  |              |

|                  |                                                               | ′оо - 4Vт (High                               | υ,                   |                            |                            |                  |              |

|                  |                                                               | ′DD - 2V⊤ (Low                                | •                    |                            |                            |                  |              |

| bit 3-2          | •                                                             | ted: Read as '                                |                      |                            |                            |                  |              |

| bit 1-0          | 11 = ADC Fix                                                  | ADC Fixed V<br>ed Voltage Re                  | ference Peripl       | neral output is            | 4x (4.096V) <sup>(2)</sup> |                  |              |

|                  | 01 = ADC Fix                                                  | ed Voltage Re<br>d Voltage Re<br>d Voltage Re | ference Peripl       | neral output is            | 1x (1.024V)                |                  |              |

|                  | RRDY indicates                                                |                                               |                      |                            |                            |                  |              |

- 2: Fixed Voltage Reference output cannot exceed VDD.

- 3: See Section 14.0 "Temperature Indicator Module" for additional information.

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG |       |       | ADFV  | R<1:0> | 78                  |

**Legend:** Shaded cells are not used with the Fixed Voltage Reference.

#### 15.2.5 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- Disable weak pull-ups either globally (Refer to the OPTION\_REG register) or individually (Refer to the appropriate WPUX register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

Note 1: The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

2: Refer to Section 15.4 "A/D Acquisition Requirements".

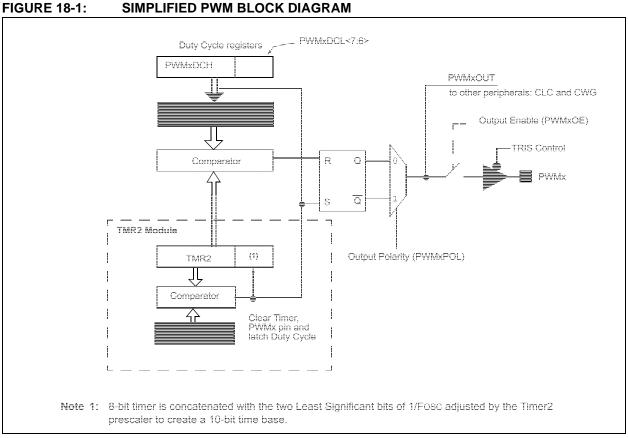

#### 18.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

Figure 18-1 shows a simplified block diagram of PWM operation.

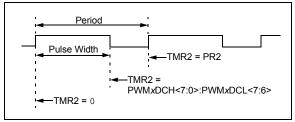

Figure 18-2 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up this module for PWM operation, refer to **Section 18.1.9** "Setup for PWM Operation using PWMx Pins".

#### FIGURE 18-2: PWM OUTPUT

| U-0                                    | R/W-x/u                                                         | R/W-x/u                                | R/W-x/u      | U-0                       | R/W-x/u         | R/W-x/u          | R/W-x/u     |  |  |

|----------------------------------------|-----------------------------------------------------------------|----------------------------------------|--------------|---------------------------|-----------------|------------------|-------------|--|--|

| _                                      | LCxD2S<2:0>(1)                                                  |                                        |              | _                         | -               | _CxD1S<2:0>(1)   | -           |  |  |

| bit 7                                  |                                                                 |                                        |              |                           |                 |                  | bit 0       |  |  |

|                                        |                                                                 |                                        |              |                           |                 |                  |             |  |  |

| Legend:                                |                                                                 |                                        |              |                           |                 |                  |             |  |  |

| R = Readable                           | e bit                                                           | W = Writable b                         | bit          | U = Unimplei              | mented bit, rea | d as '0'         |             |  |  |

| u = Bit is unch                        | nanged                                                          | x = Bit is unkn                        | own          | -n/n = Value              | at POR and BC   | R/Value at all o | ther Resets |  |  |

| '1' = Bit is set                       |                                                                 | '0' = Bit is clea                      | ired         |                           |                 |                  |             |  |  |

|                                        |                                                                 |                                        |              |                           |                 |                  |             |  |  |

| bit 7                                  | Unimpleme                                                       | nted: Read as '0                       | )'           |                           |                 |                  |             |  |  |

| bit 6-4                                | LCxD2S<2:0                                                      | 0>: Input Data 2                       | Selection Co | ntrol bits <sup>(1)</sup> |                 |                  |             |  |  |

|                                        | 111 = CLCx                                                      | (IN[7] is selected                     | for lcxd2.   |                           |                 |                  |             |  |  |

|                                        | 110 = CLC×                                                      | (IN[6] is selected                     | for lcxd2.   |                           |                 |                  |             |  |  |

|                                        |                                                                 | 101 = CLCxIN[5] is selected for lcxd2. |              |                           |                 |                  |             |  |  |

|                                        |                                                                 | (IN[4] is selected                     |              |                           |                 |                  |             |  |  |

|                                        |                                                                 | (IN[3] is selected                     |              |                           |                 |                  |             |  |  |

|                                        |                                                                 | (IN[2] is selected                     |              |                           |                 |                  |             |  |  |

|                                        |                                                                 | (IN[1] is selected                     |              |                           |                 |                  |             |  |  |

|                                        | 000 = CLCx                                                      | (IN[0] is selected                     | for lcxd2.   |                           |                 |                  |             |  |  |

| bit 3                                  | Unimpleme                                                       | nted: Read as '0                       | )'           |                           |                 |                  |             |  |  |

| bit 2-0                                | LCxD1S<2:0>: Input Data 1 Selection Control bits <sup>(1)</sup> |                                        |              |                           |                 |                  |             |  |  |

| 111 = CLCxIN[7] is selected for lcxd1. |                                                                 |                                        |              |                           |                 |                  |             |  |  |

| 110 = CLCxIN[6] is selected for lcxd1. |                                                                 |                                        |              |                           |                 |                  |             |  |  |

|                                        | 101 = CLCx                                                      | (IN[5] is selected                     | for lcxd1.   |                           |                 |                  |             |  |  |

|                                        | 100 = CLCx                                                      | (IN[4] is selected                     | for lcxd1.   |                           |                 |                  |             |  |  |

|                                        |                                                                 | (IN[3] is selected                     |              |                           |                 |                  |             |  |  |

|                                        |                                                                 | (IN[2] is selected                     |              |                           |                 |                  |             |  |  |

|                                        |                                                                 | (IN[1] is selected                     |              |                           |                 |                  |             |  |  |

|                                        | 000 = CLCx                                                      | (IN[0] is selected                     | for lcxd1.   |                           |                 |                  |             |  |  |

#### REGISTER 19-3: CLCxSEL0: MULTIPLEXER DATA 1 AND 2 SELECT REGISTER

**Note 1:** See Table 19-1 for signal names associated with inputs.

| R/W-x/u          | R/W-x/u                        | R/W-x/u                                                      | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |

|------------------|--------------------------------|--------------------------------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|--|

| LCxG3D4T         | LCxG3D4N                       | LCxG3D3T                                                     | LCxG3D3N        | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |  |  |

| bit 7            |                                |                                                              |                 |                |                  |                  | bit (       |  |  |

| Lonondi          |                                |                                                              |                 |                |                  |                  |             |  |  |

| Legend:          | h:t                            |                                                              | hit             |                | nonted hit road  |                  |             |  |  |

| R = Readable     |                                | W = Writable                                                 |                 | •              | nented bit, read |                  | ther Decete |  |  |

| u = Bit is uncha | angeo                          | x = Bit is unkr                                              |                 | -n/n = value a | at POR and BO    | R/value at all C | iner Reseis |  |  |

| '1' = Bit is set |                                | '0' = Bit is cle                                             | areo            |                |                  |                  |             |  |  |

| bit 7            | LCxG3D4T: (                    | Gate 3 Data 4 1                                              | Frue (non-invei | rted) bit      |                  |                  |             |  |  |

|                  |                                | gated into lcxg                                              |                 | ,              |                  |                  |             |  |  |

|                  | 0 = Icxd4T is                  | not gated into                                               | lcxg3           |                |                  |                  |             |  |  |

| bit 6            | LCxG3D4N:                      | Gate 3 Data 4                                                | Negated (inver  | rted) bit      |                  |                  |             |  |  |

|                  |                                | gated into Icx                                               |                 |                |                  |                  |             |  |  |

|                  |                                | not gated into                                               | 0               |                |                  |                  |             |  |  |

| bit 5            |                                | Gate 3 Data 3                                                |                 | rted) bit      |                  |                  |             |  |  |

|                  |                                | Icxd3T is gated into Icxg3<br>Icxd3T is not gated into Icxg3 |                 |                |                  |                  |             |  |  |

| bit 4            |                                | Gate 3 Data 3                                                | •               | tod) bit       |                  |                  |             |  |  |

| DIL 4            |                                | gated into lcx                                               | •               | leu) bit       |                  |                  |             |  |  |

|                  |                                | not gated into                                               |                 |                |                  |                  |             |  |  |

| bit 3            |                                | Gate 3 Data 2                                                | •               | rted) bit      |                  |                  |             |  |  |

|                  |                                | gated into Icxo                                              | •               | ,              |                  |                  |             |  |  |

|                  |                                | not gated into                                               |                 |                |                  |                  |             |  |  |

| bit 2            | LCxG3D2N:                      | Gate 3 Data 2                                                | Negated (inver  | rted) bit      |                  |                  |             |  |  |

|                  | 1 = Icxd2N is gated into Icxg3 |                                                              |                 |                |                  |                  |             |  |  |

|                  |                                | not gated into                                               |                 |                |                  |                  |             |  |  |

| bit 1            | LCxG3D1T: (                    | LCxG3D1T: Gate 3 Data 1 True (non-inverted) bit              |                 |                |                  |                  |             |  |  |

|                  | 1 = lcxd1T is gated into lcxg3 |                                                              |                 |                |                  |                  |             |  |  |

|                  |                                | not gated into                                               | 0               |                |                  |                  |             |  |  |

| bit 0            |                                | Gate 3 Data 1                                                | 0 (             | rted) bit      |                  |                  |             |  |  |

|                  |                                | gated into Icx<br>not gated into                             |                 |                |                  |                  |             |  |  |

|                  | 0 = 10x0  IN IS                | not gated into                                               | icxys           |                |                  |                  |             |  |  |

#### REGISTER 19-7: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

#### 21.11 Configuring the CWG

The following steps illustrate how to properly configure the CWG to ensure a synchronous start:

- 1. Ensure that the TRIS control bits corresponding to CWGxA and CWGxB are set so that both are configured as inputs.

- 2. Clear the GxEN bit, if not already cleared.

- 3. Set desired dead-band times with the CWGxDBR and CWGxDBF registers.

- 4. Setup the following controls in CWGxCON2 auto-shutdown register:

- Select desired shutdown source.

- Select both output overrides to the desired levels (this is necessary even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the GxASE bit and clear the GxARSEN bit.

- 5. Select the desired input source using the CWGxCON1 register.

- 6. Configure the following controls in CWGxCON0 register:

- · Select desired clock source.

- · Select the desired output polarities.

- Set the output enables for the outputs to be used.

- 7. Set the GxEN bit.

- Clear TRIS control bits corresponding to CWGxA and CWGxB to be used to configure those pins as outputs.

- If auto-restart is to be used, set the GxARSEN bit and the GxASE bit will be cleared automatically. Otherwise, clear the GxASE bit to start the CWG.

#### 21.11.1 PIN OVERRIDE LEVELS

The levels driven to the output pins, while the shutdown input is true, are controlled by the GxASDLA and GxASDLB bits of the CWGxCON1 register (Register 21-2). GxASDLA controls the CWG1A override level and GxASDLB controls the CWG1B override level. The control bit logic level corresponds to the output logic drive level while in the shutdown state. The polarity control does not apply to the override level.

#### 21.11.2 AUTO-SHUTDOWN RESTART

After an auto-shutdown event has occurred, there are two ways to have resume operation:

- Software controlled

- Auto-restart

The restart method is selected with the GxARSEN bit of the CWGxCON2 register. Waveforms of software controlled and automatic restarts are shown in Figure 21-5 and Figure 21-6.

#### 21.11.2.1 Software controlled restart

When the GxARSEN bit of the CWGxCON2 register is cleared, the CWG must be restarted after an auto-shut-down event by software.

The CWG will resume operation on the first rising edge event after the GxASE bit is cleared. Clearing the shutdown state requires all selected shutdown inputs to be low, otherwise the GxASE bit will remain set.

#### 21.11.2.2 Auto-Restart

When the GxARSEN bit of the CWGxCON2 register is set, the CWG will restart from the auto-shutdown state automatically.

After the shutdown event clears, the GxASE bit will clear automatically and the CWG will resume operation on the first rising edge event.

#### 21.12 CWG Control Registers

| R/W-0/0         | R/W-0/0                           | R/W-0/0                                                                                                                      | R/W-0/0      | R/W-0/0        | U-0              | U-0            | R/W-0/0      |  |  |

|-----------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|------------------|----------------|--------------|--|--|

| GxEN            | GxOEB                             | GxOEA                                                                                                                        | GxPOLB       | GxPOLA         | _                | _              | GxCS0        |  |  |

| bit 7           |                                   |                                                                                                                              |              |                |                  |                | bit 0        |  |  |

|                 |                                   |                                                                                                                              |              |                |                  |                |              |  |  |

| Legend:         |                                   |                                                                                                                              |              |                |                  |                |              |  |  |

| R = Readab      | le bit                            | W = Writable                                                                                                                 | bit          | U = Unimplen   | nented bit, read | as '0'         |              |  |  |

| u = Bit is un   | changed                           | x = Bit is unk                                                                                                               | nown         | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |  |  |

| '1' = Bit is se | et                                | '0' = Bit is cle                                                                                                             | ared         | q = Value dep  | ends on condit   | ion            |              |  |  |

|                 |                                   |                                                                                                                              |              |                |                  |                |              |  |  |

| bit 7           | GxEN: CWG                         | x Enable bit                                                                                                                 |              |                |                  |                |              |  |  |

|                 | 1 = Module i                      |                                                                                                                              |              |                |                  |                |              |  |  |

|                 | 0 = Module i                      |                                                                                                                              |              |                |                  |                |              |  |  |

| bit 6           |                                   | GxB Output Er                                                                                                                |              | <b>a</b> .     |                  |                |              |  |  |

|                 |                                   | <ul> <li>1 = CWGxB is available on appropriate I/O pin</li> <li>0 = CWGxB is not available on appropriate I/O pin</li> </ul> |              |                |                  |                |              |  |  |

| bit 5           |                                   |                                                                                                                              |              | le l/O pin     |                  |                |              |  |  |

| DIL 5           |                                   | GxA Output Er<br>is available on                                                                                             |              | 0 nin          |                  |                |              |  |  |

|                 |                                   | is not available                                                                                                             |              | •              |                  |                |              |  |  |

| bit 4           |                                   | NGxB Output F                                                                                                                |              |                |                  |                |              |  |  |

|                 |                                   | s inverted polar                                                                                                             | •            |                |                  |                |              |  |  |

|                 | 0 = Output is                     | s normal polarit                                                                                                             | y            |                |                  |                |              |  |  |

| bit 3           | GxPOLA: CWGxA Output Polarity bit |                                                                                                                              |              |                |                  |                |              |  |  |

|                 |                                   | s inverted polar                                                                                                             |              |                |                  |                |              |  |  |

|                 |                                   | s normal polarit                                                                                                             | •            |                |                  |                |              |  |  |

| bit 2-1         | Unimplemer                        | nted: Read as '                                                                                                              | 0'           |                |                  |                |              |  |  |

| bit 0           |                                   | Gx Clock Source                                                                                                              | e Select bit |                |                  |                |              |  |  |

|                 | 1 = HFINTO                        | SC                                                                                                                           |              |                |                  |                |              |  |  |

#### REGISTER 21-1: CWGxCON0: CWG CONTROL REGISTER 0

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                        |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC < 10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                          |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 11-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>2-cycle instruction. |  |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                           |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                   |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the<br>W register. |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

#### 24.3 DC Characteristics

#### TABLE 24-1: SUPPLY VOLTAGE

| PIC10LF320/322<br>PIC10F320/322 |        |                                                                                  | Standard Operating Conditions (unless otherwise stated) |      |            |        |                                                                                                                                                                                                                                                                                         |  |  |

|---------------------------------|--------|----------------------------------------------------------------------------------|---------------------------------------------------------|------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                 |        |                                                                                  |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |  |

| Param.<br>No.                   | Sym.   | Characteristic                                                                   | Min.                                                    | Тур† | Max.       | Units  | Conditions                                                                                                                                                                                                                                                                              |  |  |

| D001                            | Vdd    | Supply Voltage                                                                   |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |  |

|                                 |        |                                                                                  | 1.8<br>2.5                                              |      | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                         |  |  |

| D001                            |        |                                                                                  | 2.3<br>2.5                                              | _    | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 20 MHz                                                                                                                                                                                                                                                         |  |  |

| D002*                           | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                                        |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |  |

|                                 |        |                                                                                  | 1.5                                                     | —    | —          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |  |

| D002*                           |        |                                                                                  | 1.7                                                     | —    | _          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |  |

|                                 | VPOR*  | Power-on Reset Release Voltage                                                   | —                                                       | 1.6  | _          | V      |                                                                                                                                                                                                                                                                                         |  |  |

|                                 | VPORR* | Power-on Reset Rearm Voltage                                                     | —                                                       | 0.8  | _          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |  |

|                                 |        |                                                                                  | —                                                       | 1.7  | _          | V      | Device in Sleep mode                                                                                                                                                                                                                                                                    |  |  |

| D003                            | VFVR   | Fixed Voltage Reference Voltage                                                  |                                                         |      |            |        |                                                                                                                                                                                                                                                                                         |  |  |

|                                 |        | 1x gain (1.024V nominal)<br>2x gain (2.048V nominal)<br>4x gain (4.096V nominal) | -8                                                      | _    | +6         | %      | $ \begin{array}{l} V{\rm DD} \geq 2.5V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \\ V{\rm DD} \geq 2.5V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \\ V{\rm DD} \geq 4.75V, \ -40^{\circ}{\rm C} \leq {\rm TA} \leq +85^{\circ}{\rm C} \end{array} $ |  |  |

| D004*                           | SVDD   | VDD Rise Rate to ensure internal<br>Power-on Reset signal                        | 0.05                                                    | —    | —          | V/ms   | See Section 5.1 "Power-On Reset (POR)" for details.                                                                                                                                                                                                                                     |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

#### 24.4 Thermal Considerations

| Standard Operating Conditions (unless otherwise stated) |           |                                        |      |       |                                                          |  |  |  |

|---------------------------------------------------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|--|

| Param<br>No.                                            | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |  |  |  |

| TH01                                                    | θJA       | Thermal Resistance Junction to Ambient | 60   | °C/W  | 6-pin SOT-23 package                                     |  |  |  |

|                                                         |           |                                        | 80   | °C/W  | 8-pin PDIP package                                       |  |  |  |

|                                                         |           |                                        | 90   | °C/W  | 8-pin DFN package                                        |  |  |  |

| TH02                                                    | θJC       | Thermal Resistance Junction to Case    | 31.4 | °C/W  | 6-pin SOT-23 package                                     |  |  |  |

|                                                         |           |                                        | 24   | °C/W  | 8-pin PDIP package                                       |  |  |  |

|                                                         |           |                                        | 24   | °C/W  | 8-pin DFN package                                        |  |  |  |

| TH03                                                    | TJMAX     | Maximum Junction Temperature           | 150  | °C    |                                                          |  |  |  |

| TH04                                                    | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |  |

| TH05                                                    | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |  |

| TH06                                                    | Pi/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |  |

| TH07                                                    | Pder      | Derated Power                          | —    | W     | Pder = PDmax (Τj - Τa)/θja <sup>(2)</sup>                |  |  |  |

Standard Operating Conditions (unless otherwise stated)

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

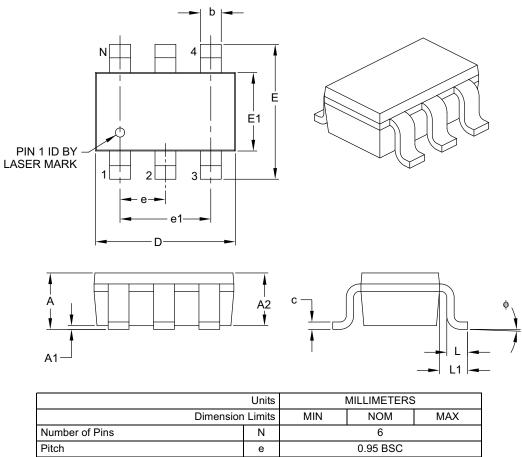

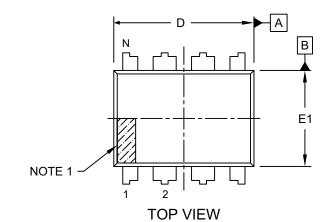

#### 27.2 Package Details

The following sections give the technical details of the packages.

#### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Dimension Limits | MIN      | NOM | MAX  |

|--------------------------|------------------|----------|-----|------|

| Number of Pins           | N                |          | 6   |      |

| Pitch                    | е                | 0.95 BSC |     |      |

| Outside Lead Pitch       | e1               | 1.90 BSC |     |      |

| Overall Height           | А                | 0.90     | -   | 1.45 |

| Molded Package Thickness | A2               | 0.89     | -   | 1.30 |

| Standoff                 | A1               | 0.00     | -   | 0.15 |

| Overall Width            | E                | 2.20     | -   | 3.20 |

| Molded Package Width     | E1               | 1.30     | -   | 1.80 |

| Overall Length           | D                | 2.70     | -   | 3.10 |

| Foot Length              | L                | 0.10     | -   | 0.60 |

| Footprint                | L1               | 0.35     | -   | 0.80 |

| Foot Angle               | ф                | 0°       | -   | 30°  |

| Lead Thickness           |                  | 0.08     | -   | 0.26 |

| Lead Width               | b                | 0.20     | -   | 0.51 |

#### Notes:

1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-028B

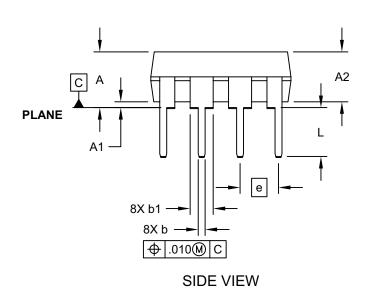

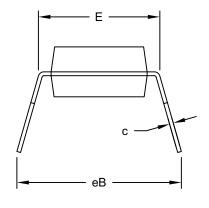

#### 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**END VIEW**

Microchip Technology Drawing No. C04-018D Sheet 1 of 2

### THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.